# (11) EP 2 413 305 A1

(12)

# **EUROPEAN PATENT APPLICATION** published in accordance with Art. 153(4) EPC

(43) Date of publication: 01.02.2012 Bulletin 2012/05

(21) Application number: 09842134.0

(22) Date of filing: 23.03.2009

(51) Int Cl.:

G09C 1/00 (2006.01)

G06F 21/24 (2006.01)

(86) International application number:

PCT/JP2009/001276

(87) International publication number:

WO 2010/109516 (30.09.2010 Gazette 2010/39)

(84) Designated Contracting States:

AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HR HU IE IS IT LI LT LU LV MC MK MT NL NO PL PT RO SE SI SK TR

(71) Applicant: Fujitsu Limited

Kawasaki-shi, Kanagawa 211-8588 (JP)

(72) Inventors:

FURUKAWA, Kazuyoshi Kawasaki-shi Kanagawa 211-8588 (JP)  SHIMOYAMA, Takeshi Kawasaki-shi Kanagawa 211-8588 (JP)

TAKENAKA, Masahiko Kawasaki-shi Kanagawa 211-8588 (JP)

(74) Representative: Wilding, Frances Ward

Haseltine Lake LLP Lincoln House, 5th Floor 300 High Holborn London WC1V 7JH (GB)

#### (54) DATA PROCESSING DEVICE AND DATA PROCESSING METHOD

A data processing apparatus includes an address bus, a scramble unit, and a data bus. The address bus outputs address data to be given to a memory apparatus. The scramble unit scrambles write-in data into a storage position in the memory apparatus identified by the address data to obtain confidential data. The data bus outputs the confidential data. The scramble unit includes a first scramble unit, a first conversion unit and a second scramble unit. The first scramble unit XORs first mask data corresponding to the address data and the write-in data for each bit and makes it first scrambled data. The first conversion unit performs one-to-one substitution conversion of the first scrambled data. The second scramble unit XORs second mask data corresponding to the address data and data after the conversion of the first scrambled data by the first conversion unit and outputs obtained second scrambled data as the confidential data.

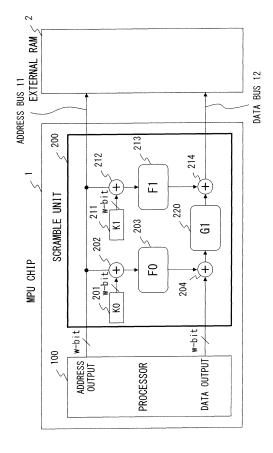

FIG. 4

# TECHNICAL FIELD

**[0001]** The present invention relates to a technique to protect data stored in a memory apparatus.

1

#### **BACKGROUND ART**

**[0002]** Since an embedded device such as a mobile phone has valuable asset such as paid contents, it has become a target of attacks to obtain it fraudulently. One way of such attacks is data probing. The data probing is an attack to read out data electrically from an exposed data bus wiring between an MPU (Micro Processor Unit) chip and an external RAM (Random Access Memory).

**[0003]** Data scrambling is a method of preventing information leaking due to the data probing. The data scrambling is to convert data into scrambled data before it is released from the MPU chip, to keep the contents of the data confidential from the attacker.

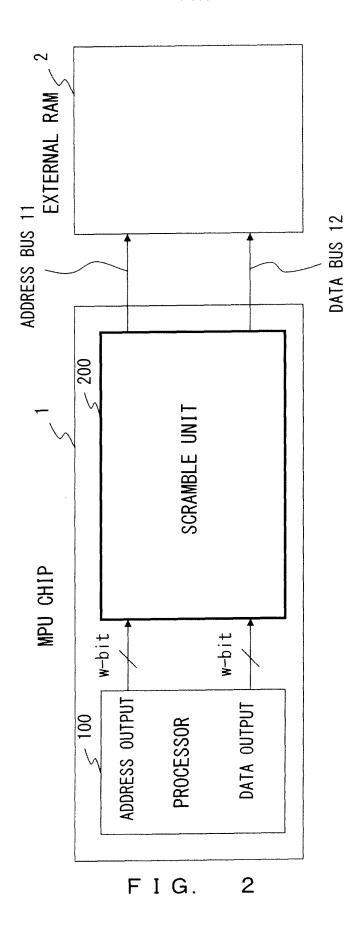

**[0004]** Here, FIG. 1 is explained. FIG. 1 illustrates an example of conventional data scrambling.

In FIG. 1, an MPU chip 1 being a data processing apparatus has an address bus 11 and a data bus 12 both having a bit width of w-bit and are respectively connected to an external RAM 2 being a memory apparatus. Furthermore, the MPU chip 1 has a processor 100 and a scramble unit 200 inside.

**[0005]** The address bus 11 outputs address data to give to the external RAM 2 output by the processor 100. The scramble unit 200 obtains confidential data by scrambling write-in data, output by the processor 100, to the storage position of the external RAM 2 specified by an address data output by the address bus 11.

**[0006]** The data bus 12 outputs the confidential data that the scramble unit 200 has obtained.

The configuration of the scramble unit 200 presented in FIG. 1 is further explained.

The scramble unit 200 is configured to have a key register 201, an exclusive OR circuit (hereinafter, referred to as an "XOR circuit") 202, a substitution function processing unit 203, and an XOR circuit 204.

**[0007]** The key register 201 is a register in which scramble key data K of w-bit is stored.

The XOR circuit 202 XORs the same address data as that output by the address bus 11 and the scramble key data stored in the key register 201 for each bit.

**[0008]** The substitution function processing unit 203 performs a substitution conversion process to associate w-bit data output from the XOR circuit 202 uniquely with any data expressed in w-bit and to output the uniquely associated data.

**[0009]** The XOR circuit 204 XORs, during the scrambling operation, the write-in data output by the processor 100 and data (mask value) corresponding to the address data output from the substitution function process unit 203 for each bit. The data output from the XOR circuit

204 is the confidential data in which the write-in data is scrambled, which is output from the data bus 12 to the external RAM 2. The confidential data is stored in a storage position in the external RAM 2 specified by an address data output by the address bus 11.

**[0010]** When the MPU chip 1 reads out the confidential data from the external RAM 2, the scramble unit 200 performs a descrambling operation.

The address data being output from the address bus 11 when the MPU chip 1 reads out the confidential data from the external RAM 2 is the same as that when the confidential data is written in. Therefore, if the scramble key data K in the key register 201 and substitution conversion F in the substitution function processing unit 203 are both the same as those at the time of the scrambling operation, the mask value output from the substitution function processing unit 203 at the time of reading out of the confidential data becomes the same as that at the time of written in the confidential data.

**[0011]** The XOR circuit 204 XORs, during the descrambling operation, the confidential data read out from the eternal RAM 2 and the mask value output from the substitution function processing unit 203 for each bit. Here, since the mask value is the same at the time of writing in and reading out of the confidential data, the XOR results in the original write-in data. The descrambling of the confidential data is completed as described above, and the obtained original write-in data is read in the processor 100.

[0012] As described above, in the configuration presented in FIG. 1, the scramble unit 200 inside the MPU chip 1 performs scrambling of write-in data to the external RAM 2. That is, since the wiring for the processor 100 and the scrambling unit 200 is not exposed outside the MPU chip 1, write-in data cannot by read out by data probing before it is subjected to scrambling.

**[0013]** In addition, in the configuration presented in FIG. 1, generally, the processor 100 performing the data processing performs calculation of the mask value in advance using the characteristic that address data can be prepared in the address bus 11 before write-in data is prepared. By reducing processing for write-in data as much as possible as described above, the high-speed response performance to complete the scrambling process within the delay time that is allowed between the processor 100 and the external RAM 2.

**[0014]** Generally, in the scrambling of write-in data to the memory apparatus, safety can be improved by generating the mask value with the shared key block cipher and the like, and the safety is maintained even if the processing scheme is revealed. However, since the processing of the shared key block cipher is complicated generally, it becomes impossible when using the shared key block cipher to satisfy the high-speed response performance that is required for the data bus 12 transmitting the write-in data.

**[0015]** Meanwhile, the scrambling adopting the configuration presented in FIG. 1 ensures, by embedding the

scramble unit 200 into the MPU chip 1, security with the difficulty for the attacker to know the algorithm for generating the mask value. The scrambling adopting this configuration has a feature that since the calculation volume is smaller than the case in which a cryptographic processing that is still safe even if the algorithm of the scrambling is revealed, the processing can be performed at a high speed.

[0016] In addition, the data scramble unit 200 in the configuration presented in FIG. 1 generates scramble data (confidential data) using both information write-in data and address data output from the processor 100. With the data scramble algorithm that is dependent also on the address data, even with for the same write-in data, the scrambled data written into the external RAM 2 becomes different by the address data, improving the resistance for analysis.

**[0017]** Meanwhile, as other backgrounds arts, a technique to perform scrambling of data also at the memory unit side and a technique of double encryption to further encrypt encrypted data have been known.

#### Patent Literature 1:

Japanese Laid-open Patent Publication No. 2001-109667

#### Patent Literature 2:

Japanese Laid-open Patent Publication No. 2002-328844

#### Patent Literature 3:

Japanese Laid-open Patent Publication No. 2004-110408

#### SUMMARY OF INVENTION

#### **TECHNICAL PROBLEM**

[0018] As described earlier, by providing the scramble unit 200 within the MPU chip 1, it has become possible to make data confidential from data probing. However, there still remains the risk that the attacker analyses the scramble algorithm. In order to ensure the security of the scrambling, the security of the scramble algorithm needs to be evaluated.

**[0019]** One of items to evaluate the security of a keyed scramble algorithm being an algorithm to perform data scrambling using scramble key data as adopted in the scramble unit 200 in FIG. 1 is resistance to brute force key attacks based on a known plaintext attack.

**[0020]** In the brute force key attacks, among the combination of scramble key data, write-in data, scramble data and address data and hardware implementing the scramble key algorithm, those except for the scramble key data are given to the attacker. The attacker executes,

in this case, scrambling while setting scramble key data arbitrarily. Then, the execution is repeated until the scramble key data used in the given combination is identified.

**[0021]** The resistance to the brute force key attack in creases as the key length of the scramble key data becomes longer. In addition, the security is ensured by making the calculation volume required for the brute force key attack a value that cannot be calculated within a practical period of time.

**[0022]** For the keyed scramble algorithm adopted in the scramble unit 200 in FIG. 1, the key length (bit length) of the scramble key data cannot be longer than the word length of the processor 100.

**[0023]** For example, the word length of the processor for a number of embedded devices is currently below 32 bits. Here, the brute force key attack to the scramble unit 200 in the case in which the word length is assumed as 32 bits is considered. Supposing that the execution of scrambling can be performed 1000 times per second, the scramble key data could be found in 50 days.

**[0024]** In addition, as an attacking method to a keyed scramble algorithm, chosen plaintext attacks have been known. In this attack, a case is assumed in which the attacker cannot see the scramble key data is not to be known by the attacker but can obtain scramble data while setting data and address data freely. In other words, this attack assumes a higher ability of the attacker than that for the brute force key attack.

**[0025]** In the scramble unit 200 in FIG. 1, the attacker first create a pair of write-in data and scrambled data for all address data. Then, the mask value for all the scrambled data can be found by XORing the scrambled data and write-in data. Then, it becomes possible for the attacker to descramble the scrambled data of a given address into data using the obtained mask value, without finding the scramble key data.

**[0026]** The present invention has been made in view of the problem described above, and a problem to be solved by it is to provide a data scrambling method having resistance to chosen plaintext attacks.

#### SOLUTION TO PROBLEM

[0027] A data processing apparatus disclosed herein has an address bus, a scramble unit and a data bus. Among these, the address bus outputs address data to be given to a memory apparatus. The scramble unit scrambles write-in data into a storage position in the memory apparatus identified by address data output by the address bus to obtain confidential data. The data bus outputs the confidential data obtained by the scramble unit.

**[0028]** Meanwhile, the scramble unit has first scramble means, first conversion means and second scramble means. Among these, the first scramble means scrambles write-in data by XORing with first mask data corresponding to the address data for each bit to obtain first

scrambled data. The first conversion means performs one-to-one substation conversion of the first scrambled data. The second scramble means scrambles data after the conversion of the first mask data by the first conversion means by XORing with second mask data corresponding to the address data to obtain second scrambled data. Meanwhile, the scramble unit makes the second scrambled data the confidential data.

**[0029]** In the apparatus, after the first conversion means performs substitution conversion of write-in data scrambled by the first scramble means, the second scramble means further performs scrambling. By the first conversion means, the processing for write-in data being simple XOR with a mask value is avoided. That is, according to the configuration of the apparatus, the relationship between write-in data and confidential data in input/output of the scramble unit depends not only on the address data but also on the write-in data. Therefore, data scrambling performed in the apparatus has resistance to chosen plaintext attacks.

[0030] In addition, the apparatus has, as means to obtain a mask value for write-in data, two scramble means, i.e., first scramble means and second scramble means. Here, by configuring to obtain the first mask data from address data and first scramble key data and to obtain the second mask data from the address data and second scramble key data, the key length for the scramble key data as a whole can be made longer than conventional one. By doing so, the resistance to the brute force key attack improves compared with the conventional one described earlier.

**[0031]** In addition, in the first scramble means and the second scramble means in the apparatus, the calculation to obtain the mask value from address data may be performed in advance. Therefore, in the apparatus, by giving the conversion means a high speed, a high-speed response performance may be realized for the scrambling operation.

[0032] Meanwhile, a descramble apparatus to descramble confidential data stored in the memory apparatus by the data processing apparatus to obtain original write-in data is also disclosed herein. The descramble apparatus has an address bus, first descramble means, inverse conversion means and second descramble means.

[0033] Among these, the address bus outputs address data to be given to the memory apparatus. The first descramble means descrambles confidential data read out from a storage position in the memory apparatus identified by address data by XORing with the second mask data described earlier to obtain intermediate descrambled data. The inverse conversion means performs inversion conversion of substitution conversion by the first conversion means described earlier for the intermediate descrambled means. The second descramble means descramble data after inverse conversion of the intermediate descrambled data by the inverse conversion means by XORing with the first mask data to obtain original write-

in data.

[0034] According to the descramble unit, original writein data may be obtained by reading out and descrambling

confidential data stored in the memory apparatus by the

data processing apparatus described earlier. In addition,

as a matter of course, it is possible to configure the data

processing apparatus described above to include the

constituent elements of the descramble apparatus in order to obtain the original write-in data from the descrambled data by itself.

**[0035]** In addition, a scrambling method performed by the data processing apparatus described above, and a descrambling method performed by the descramble apparatus described above are also disclosed herein.

#### ADVANTAGEOUS EFFECTS OF INVENTION

[0036] According to the apparatus and method disclosed herein, an effect is obtained that a data scrambling

method having resistance to chosen plaintext attacks can be provided.

#### BRIEF DESCRIPTION OF DRAWINGS

# <sup>25</sup> [0037]

35

40

FIG. 1 is a diagram illustrating an example of conventional data scrambling.

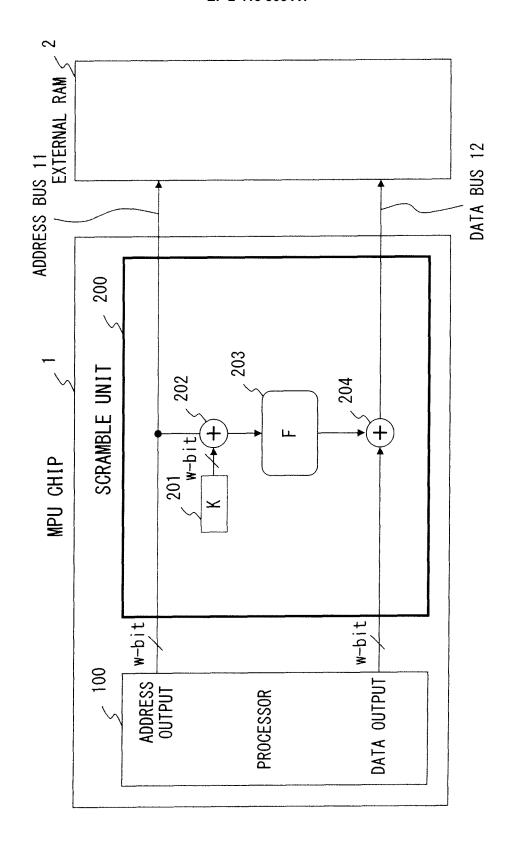

FIG. 2 is an overall configuration diagram of a data processing apparatus.

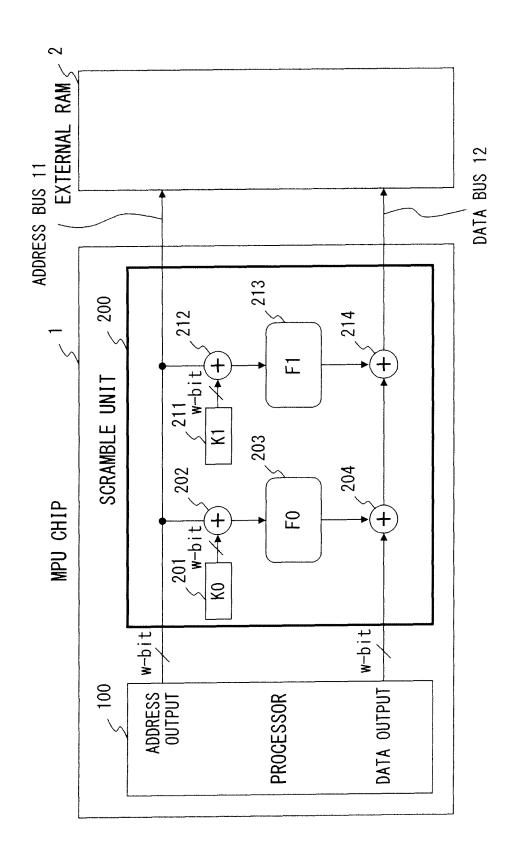

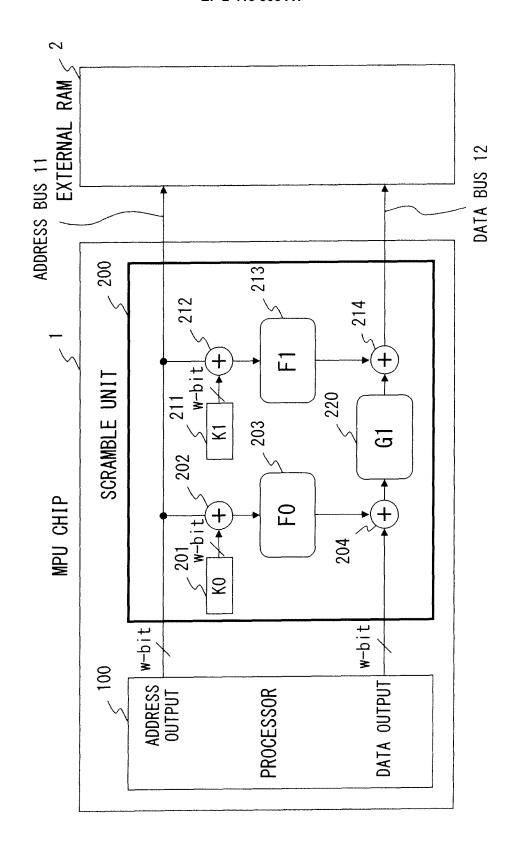

FIG. 3 is a diagram illustrating a first example of a scramble unit presented in FIG. 2.

FIG. 4 is a diagram illustrating a first example of a scramble unit presented in FIG. 2.

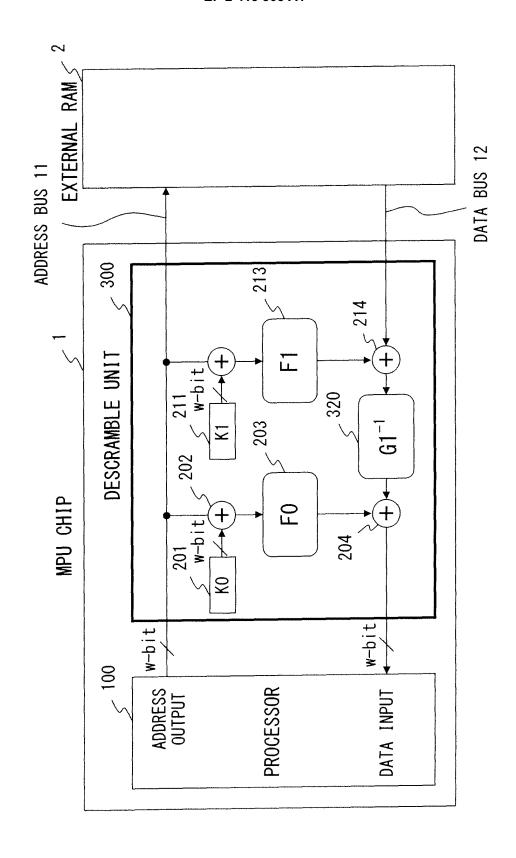

FIG. 5 is a configuration diagram of a descramble unit

FIG. 6A is a first example of a substitution function and its inverse function.

FIG. 6B is a second example of a substitution function and its inverse function.

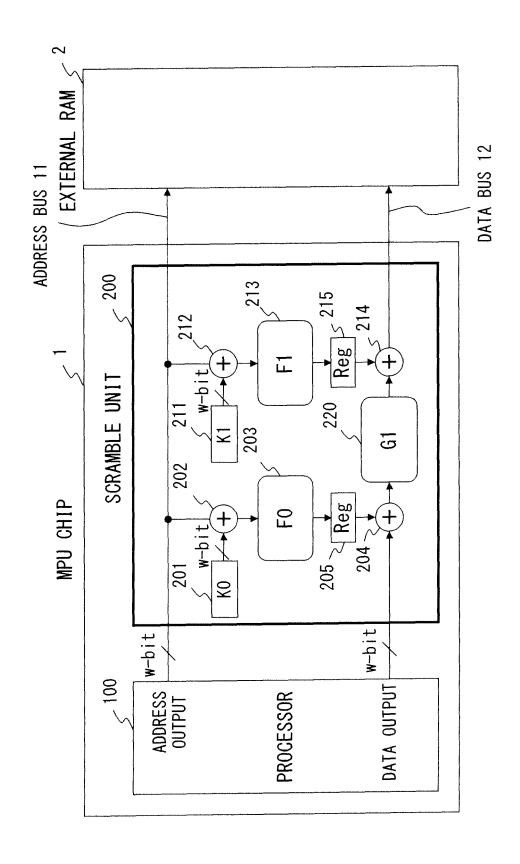

FIG. 7 is a diagram illustrating a third example of a scramble unit presented in FIG. 2.

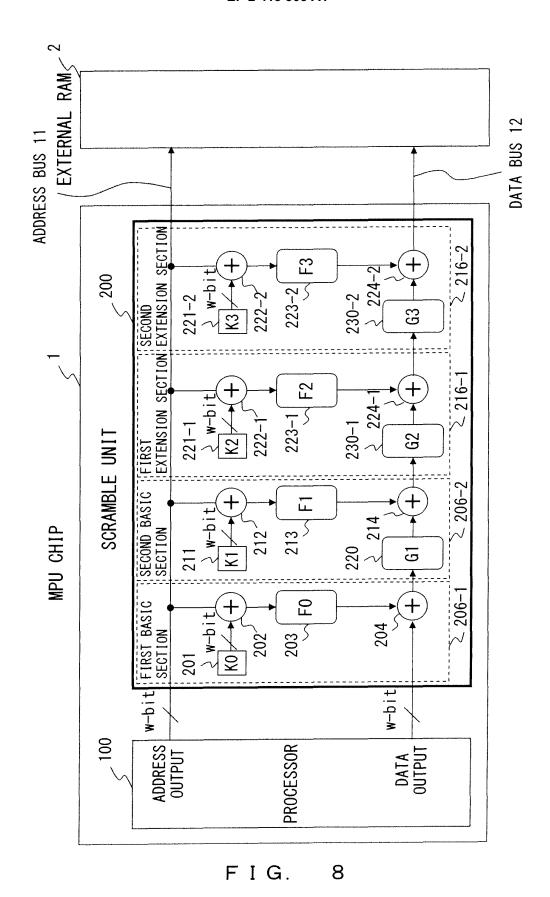

FIG. 8 is a diagram illustrating a fourth example of a scramble unit presented in FIG. 2.

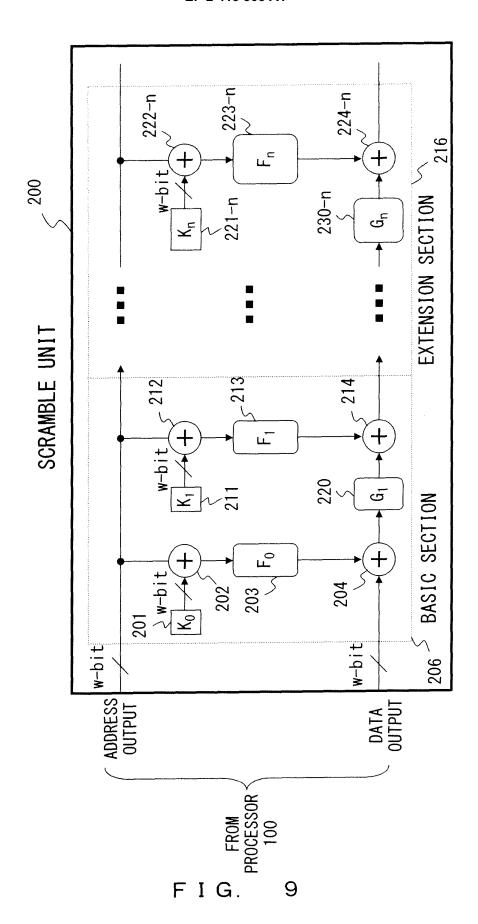

FIG. 9 is diagram illustrating a fifth example of a scramble unit presented in FIG. 2.

#### REFERENCE SIGNS LIST

#### <sup>50</sup> [0038]

1 MPU chip

2 External RAM

11 Address bus

12 Data bus

100 Processor

200 Scramble unit

201, 211, 221-1, 221-2, 221-n Key register

40

202, 204, 212, 214, 221-1, 221-2, 224-1, 224-2, 222-n, 224-n XOR circuit

203, 213, 220, 223-1, 223-2, 230-1, 230-2, 320, 223-n, 230-n Substitution function processing unit

205, 215 Register

206 Basic section

206-1 First basic section

206-2 Second basic section

216 Extension section

216-1 First extension section

216-2 Second extension section

300 Descramble unit

#### **DESCRIPTION OF EMBODIMENTS**

**[0039]** Hereinafter, embodiments of the present invention are described according to the drawings.

FIG. 2 illustrates the overall configuration of an MPU chip 1 being a data processing apparatus.

In FIG. 2, the MPU chip 1 has an address bus 11 and a data bus 12 whose bit width is both w-bit and being respectively connected to an external RAM 2 being a memory apparatus. Furthermore, the MPU chip 1 has a processor 100 and a scramble unit 200 inside.

**[0040]** The address bus 11 outputs address data output by the processor 100 and given to the external RAM 2. The scramble unit 200 scrambles write-in data output by the processor 100 that is for the storage position in the external RAM 2 identified by address data output by the address bus 11 to obtain confidential data.

**[0041]** The data bus 12 outputs the confidential data obtained by the scramble unit 200.

The configuration unit 200 presented in FIG. 2 is further described. FIG. 3 illustrates the first example of the configuration of the scramble unit.

**[0042]** In FIG. 3, the scramble unit 200 is configured to have key registers 201 and 211, XOR circuits 202, 204, 212 and 214, and substitution function processing units 203 and 213.

**[0043]** The key register 201 is a register in which scramble key data K0 of w-bit is stored. The scramble key data K0 (hereinafter, the key data K0 may be referred to as "first scramble key data") to be stored in the register 201 is changeable.

[0044] The XOR circuit 202 XORs address data that is the same as the one output by the address bus 11 and the first scramble key data stored in the key register 201. [0045] The substitution function processing unit 203 performs a substitution conversion process to associate w-bit output from the XOR circuit 202 uniquely with any of the data expressed by w-bit and to output the uniquely associated data. For substitution conversion F0 performed in the substitution function processing unit 203, relationship of input and output is generally nonlinear. Meanwhile, the substitution function processing unit 203 is configured by combining basic logic elements (AND circuit, OR circuit, NOT circuit etc.). However, if the processing speed allows, for example, the substitution

conversion may be performed by referring to a table stored in a storage apparatus in which correspondence relationship of input and output has been determined in advance. Meanwhile, in the description below, the data corresponding to the address data being data output from the substitution function processing unit 203 is referred to the "first mask data".

**[0046]** The XOR circuit 204 XORs write-in data output by the processor 100 and the first mask data output from the substitution function processing unit 203 for each bit, to perform scrambling of the write-in data.

[0047] In the following description, the scrambling performed by the key register 201, the XOR circuits 202 and 204, and the substitution function processing unit 203 is referred to as "first scrambling". In addition, data obtained by the first scrambling is referred to as "first scrambled data".

**[0048]** The key register 211 is a register in which scramble key data K1 of w-bit is stored. The scramble key data K1 (in the following description, the key data K1 may be referred to as "second scramble key data") to be stored in the register 211 is also changeable.

**[0049]** The XOR circuit 212 XORs address data that is the same as the one output by the address bus 11 and the second scramble key data stored in the key register 211.

[0050] The substitution function processing unit 213 performs a substitution conversion process to associate w-bit data output from the XOR circuit 212 uniquely with any of the data expressed by w-bit and to output the uniquely associated data. For substitution conversion F1 performed in the substitution function processing unit 213, relationship of input and output is also generally nonlinear in the same manner as in the substitution conversion F0. The substitution function processing unit 213 is also configured by combining basic logic elements, and if the processing speed allows, for example, the substitution conversion may be performed by referring to a table stored in a storage apparatus in which correspondence relationship of input and output has been determined in advance. Meanwhile, in the description below, the data corresponding to the address data being data output from the substitution function processing unit 213 is referred to the "second mask data".

5 [0051] The XOR unit 214 XORs the first scrambled data obtained by the first scrambling and the second mask data output from the substitution function processing unit 213 for each bit, to perform scrambling of the first scrambled data.

[0052] In the following description, the scrambling performed by the key register 211, the XOR circuits 212 and 214, and the substitution function processing unit 213 is referred to as "second scrambling". In addition, data obtained by the second scrambling is referred to as "second scrambled data".

**[0053]** In the configuration in FIG. 3, the second scrambled data obtained by the second scrambling is the confidential data in which write-in data output by the proces-

20

30

40

50

sor 100 is scrambled, which is output from the data bus 12 to the external RAM 2. The confidential data is stored in the storage position in the external RAM 2 identified by an address data output by the address bus 11.

**[0054]** As described above, the configuration of the scramble unit 200 presented in FIG. 3 is the one in which the conventional configuration presented in FIG. 1 is connected in tandem in two stages. Therefore, in order to obtain the original data by descrambling the confidential data obtained by the configuration, the descrambling in the conventional configuration presented in FIG. 1 may be performed in inverse order as in FIG. 3.

**[0055]** In the configuration in FIG. 3, the scrambling of write-in data is performed using the first scramble key data and the second scramble key data both having a key length of w-bit. Therefore, in the scramble unit 200 as a whole, the key length of the scramble key data used for the scrambling of write-in data seemingly becomes double (2w-bit), but since the configuration of FIG. 3 can be converted into the configuration in FIG. 1 that is equivalent to it, the security is unchanged from FIG. 1.

**[0056]** Next, FIG. 4 is described. FIG. 4 illustrates the second example of the configuration of scramble unit 200 presented in FIG. 2.

In FIG. 4, the same numerals are assigned to the same constituent elements as those presented in FIG. 3. The description is partly omitted for these constituent elements.

[0057] The configuration presented in FIG. 4 differs from the first example of the configuration presented in FIG. 3 in that a substitution function processing unit 220 that performs one-to-one substitution conversion of the first scrambled data obtained by the first scrambling is added. In addition, in the second scrambling in the configuration presented in FIG. 4, the XOR circuit 214 XORs data after conversion of the first scrambled data by the substitution function processing unit 220 and the second mask data for each bit to obtained the second scrambled data. Then, the second scrambled data becomes the confidential data in which write-in data output by the processor 100 is scrambled.

[0058] The substitution function processing unit 220 performs a substitution conversion process to associate first scrambled data of w-bit with any of the data expressed by w-bit one-to-one and to output the one-toone associated data. For substitution conversion G performed in the substitution function processing unit 220, relationship of input and output is also generally nonlinear in the same manner as in the substitution conversion F0 and F1. The substitution function processing unit 220 is also configured by combining basic logic elements, and if the processing speed allows, for example, the substitution conversion may be performed by referring to a table stored in a storage apparatus in which correspondence relationship of input and output has been determined in advance. However, since the substitution conversion processing unit 220 performs substitution conversion of data to be written into the external RAM 2, it is preferable

that the conversion process is performed at a high speed. [0059] In the configuration presented in FIG. 4, after the substitution function processing unit 220 performs substitution conversion of write-in data scrambled by the first scramble (that is, the first scrambled data), the second scrambling further performs scrambling. By doing so, the processing for write-in data being simple XOR with the mask value is avoided. In other words, according to the configuration presented in FIG. 4, the relationship between write-in data and confidential data in input/output of the scramble unit 200 depends not only on the address data but also on the write-in data. Therefore, the data scrambling performed by the scramble unit 200 having the configuration presented in FIG. 4 has resistance to chosen plaintext attacks. In addition, since the input/ output of the substitution function processing unit 220 does is not exposed outside of the scramble unit, attacks to the substitution function processing unit 220 are prevented. That is, if the substitution function processing unit 220 is placed to the left of 204 or right of 214, the configuration becomes vulnerable to simple differential attacks to the substitution function processing unit 220. Therefore, in the configuration presented in FIG. 4, it is necessary that the substitution function processing unit 220 is placed between 204 and 214.

**[0060]** Furthermore, in the configuration presented in FIG. 4, in the scramble unit 200 as a whole, the key length of the scramble key data used for the scrambling of writein data is doubled (2w-bit). Therefore, resistance to brute force key attacks is improved compared to the conventional configuration in FIG. 1.

[0061] Next, descrambling of confidential data stored in the external RAM 2 by the MPU chip 1 having the scramble unit 200 configured as presented in FIG. 4 is described. FIG. 5 is a configuration diagram of a descramble unit that descrambles the confidential data.

[0062] In the configuration in FIG. 5, a descramble unit 300 is provided within the MPU chip 1 in FIG. 2 being a data processing apparatus. Instead of configuring in such a way, it is of course possible to provide the descramble unit 300 in a descramble unit being a separate body from the MPU chip 1.

**[0063]** In FIG. 5, the same numerals are assigned to the same constituent elements as those presented in FIG. 4. The description is partly omitted for these constituent elements.

The descramble unit 300 presented in FIG. 5 is configured to have the key registers 201 and 211, the XOR circuits 202, 204, 212 and 214, and the substitution function processing units 203, 213 and 320. Meanwhile, the address bus 11 outputs an address data output by the processor 100 and given to the external RAM 2 in the same manner as that presented in FIG. 4.

**[0064]** The XOR circuit 214 descrambles confidential data read out from the storage position of the external RAM 2 identified by an address data (that is, the second scrambled data described earlier) by XORing it with the second mask data described earlier for each bit. Then,

25

the first scrambled data after the conversion by the substitution function processing unit 220 described earlier is obtained. Here, the descrambling is referred to as "first descrambling", and data obtained by the first descrambling is referred to as "intermediate descrambled data". [0065] The substitution function processing unit 320 performs inverse conversion G-1 of the substitution conversion G by the substitution function processing unit 220 for the intermediate descrambled data obtained by the XOR circuit 214.

**[0066]** Here, FIG. 6A is described. FIG. 6A is the first example of substitution conversion G and its inverse conversion G<sup>-1</sup>. Meanwhile, the example of the substitution function G in FIG. 6A is for the word length of input/output of 4-bit (16 values of "0" ('0000' in binary digits) - "f" ('1111' in binary digits)).

**[0067]** According to FIG. 6A, it is expressed that when "8" for example is input in the substitution function G, "0" is output. Meanwhile, it is expressed that "0" being the output of the substitution function G is input to the inverse conversion G-1, "8" that was the input to the substitution function G is output. In FIG. 6A, it is obvious that the relationship between the input of the substitution function G and its inverse conversion G-1 is established for all the values of "0"-"f". In addition, it is also obvious that the input/output relationship of the substitution function G is one-to-one correspondence.

**[0068]** Meanwhile, the substitution function processing unit 320 is also configured by combining basic logic elements. Here, if the processing speed allows, for example, the substitution conversion may be performed by referring to a table stored in a storage apparatus in which correspondence relationship of input and output has been determined in advance. However, since the substitution conversion processing unit 320 performs substitution conversion of data to be written into the external RAM 2, also in the same manner as the substitution function processing unit 220, it is preferable that the conversion process is performed at a high speed.

[0069] The description returns to FIG. 5.

The XOR circuit 204 descrambles data after the inverse conversion of the intermediate descrambled data by the substitution function processing unit 320 by XORing it and the first mask data described earlier. Then, the original write-in data that was output by the processor 100 at the time of scrambling operation by the scramble unit 200 is obtained. Here, the descrambling is referred to as "second descrambling".

**[0070]** The descrambling operation by the descramble unit 300 whose configuration is presented in FIG. 5 is performed as described above.

Here, the configuration of the scramble unit 200 in FIG. 4 and the configuration of the descramble unit 300 in FIG. 5 are compared. Then, the XOR circuit 204 XORs input data (write-in data in the scramble unit 200 and data after the inverse conversion of the intermediate descrambled data in the descramble unit 300) and the first mask data described earlier in both configurations. Therefore, the

XOR circuit 204 may be shared to the first scrambling in the scramble unit 200 and the second descrambling by the descramble unit 300. In addition, the XOR circuit 214 XORs input data (first scrambled data in the scramble unit 200 and confidential data read out from the external RAM 2 for the descramble unit 300) in both configurations. Therefore, the XOR circuit 204 may be shared for the second scrambling in the scramble unit 200 and the first descrambling in the descramble unit 300. By sharing the XOR circuits 204 and 214 for the scrambling operations by the scramble unit 200 and the descramble operations by the descramble unit 300, the circuit scale of the MPU chip 1 may be reduced.

[0071] Furthermore, the configuration for obtaining the first mask data composed of the key register 201, the XOR circuit 202 and the substitution function processing unit 203 is the same for the scramble unit 200 and the descramble unit 200. In addition, the configuration for obtaining the second mask data composed of the key register 211, the XOR circuit 212 and the substitution function processing unit 213 is also the same for the scramble unit 200 and the descramble unit 300. Therefore, when the scramble unit 200 and the descramble unit 300 exist together within a single MPU chip 1, the key registers 201 and 211, the XOR circuits 202 and 212, and the substitution function processing unit 203 and 213 may be shared. The circuit scale of the MPU chip 1 may be reduced also by sharing these constituent elements for the scrambling operations by the scramble unit 200 and the descrambling operations by the descramble unit 300.

**[0072]** In addition, between the substitution function processing unit 220 and the substitution function processing unit 320, one-to-one substitution conversion of input data may be performed, and the one with the forward conversion of the substitution conversion and its inverse conversion being identical (referred to as "identical substitution conversion") may be shared.

**[0073]** Here, FIG. 6B is described. FIG. 6B is the second example of substitution conversion G and its inverse conversion G<sup>-1</sup>. Meanwhile, the example of the substitution function G in FIG. 6B is also for the word length of input/output of 4-bit (16 values of "0" ('0000' in binary digits) - "f" ('1111' in binary digits)).

[0074] According to FIG. 6B, it expressed that when "0" for example is input in the substitution function G, "3" is output. Meanwhile, it is expressed that "3" being the output of the substitution function G is input to the inverse conversion G-1, "0" that was the input to the substitution function G is output. In FIG. 6B, it is obvious that the relationship between the input of the substitution function G and its inverse conversion G-1 is established for all the values of "0"-"f". In addition, it is also obvious that the input/output relationship of the substitution function G is one-to-one correspondence.

[0075] Furthermore, in the example in FIG. 6B, it is also obvious that the correspondence relationship between input and output in the substitution function G is

the same as the correspondence relationship in its inverse conversion G<sup>-1</sup>. Therefore, for the substitution conversion in FIG. 6B, the forward conversion G and its inverse conversion C<sup>-1</sup> are identical.

**[0076]** By configuring a function processing unit that performs identical substitution conversion as described above, it may be shared between the substitution function processing unit 220 and the substitution function processing unit 320. In other words, by sharing the function processing unit that performs identical substitution conversion between the substitution function processing unit 220 in the scramble unit 200 and the substitution function processing unit 320 in the descramble unit 300, the circuit scale of the MPU chip 1 may be reduced.

**[0077]** Next, the security of scrambling by the scramble unit 200 presented in FIG. 4 is reviewed.

For example, a case in which the word length of the processor (that is, the bit widths of address data and write-in data) is 32-bit is considered. At this time, the first scramble key data and the second scramble key data may both be 32-bit. At this time the key length of the entire scramble key data is 64-bit. In this case, a brute force key attack to the keyed scramble algorithm described earlier would require 584,942,417 years supposing that the scrambling operation can be performed 1000 times per second. In addition, even if the scrambling operation can be performed 1,000,000,000 times per second, 584 years would be required. Therefore, it is very difficult to find the scramble key data within a practical period of time.

**[0078]** Meanwhile, for the processor 100, it is preferable that the access to the external RAM 2 is at a high speed. Therefore, it is preferable that the amount of time required for the scrambling operation by the scramble unit 200 and the descrambling operation by the descramble unit 300 is small. Here, the time may be reduced by configuring the substitution function processing units 203, 213, 220 and 320 that performs the substitution conversion or its inverse conversion as follows.

[0079] That is, when the word length is 32-bit, instead of configuring the substitution function processing units 203, 213, 220 and 320 simply as 32-bit substitution functions for example, they are replaced with the combination of a 32-bit replace function and eight 4-bit substitution functions. Generally, for the substitution function, the complexity of the configuration increases exponentially as the word length becomes longer, and the time required for conversion also becomes longer. Therefore, by replacing a substitution function with a long word length with a combination of a replace function with a very simple configuration and a short conversion time since only rearrangement of bits is to be performed, and a substitution function with a short word length, the time required for substitution conversion can be reduced. Meanwhile, the substitution function used as the replacement is not limited to the one with the 4-bit word length, and for example, two 6-bit substitution functions and four 5-bit substitution functions may be used, or four 8-bit substitution functions may be used.

**[0080]** Meanwhile, the substitution function processing units 203 and 213 do not need to be the ones that perform identical substitution conversion, and may be non-identical. A circuit that performs non-identical substitution conversion may perform processing faster than identical one.

**[0081]** Next, FIG. 7 is described. FIG. 7 illustrates the third example of the configuration of the scramble unit 200 presented in FIG. 2.

In FIG. 7, the same numerals are assigned to the same constituent elements as those presented in FIG. 4. The description is partly omitted for these constituent elements.

**[0082]** The configuration of the scramble unit 200 presented in FIG. 7 is preferable to make the scramble unit 200 performs a synchronized operation, and differs from the first example of the configuration presented in FIG. 3 that registers 205 and 215 are added.

**[0083]** In the register 205, the first mask data output from the substitution function processing unit 203 is stored and held. In addition, in the register 215, the second mask data output from the substitution function processing unit 213 is stored and held.

**[0084]** The configuration presented in FIG. 7 utilizes the general characteristic that the processor 100 performing the data processing can prepare address data in the address bus 11 before preparing write-in data.

[0085] That is, first, the XOR operations of the address data and the first scramble key data and the second scramble key data by the XOR circuits 202 and 204 and substitution conversion of the operation results by the substitution function processing units 203 and 213 are performed. Then, the first mask data and the second mask data obtained by the performance are stored in the registers 205 and 215 respectively. After that, when writein data is output from the processor 100, the XOR operations by the XOR circuit 204, the substitution conversion of its operation result by the substitution function processing unit 220, and the XOR operation by the XOR circuit 214 are performed. Then, the confidential data obtained as the result of the performance is output to the RAM 2. [0086] Meanwhile, descrambling of the confidential data obtained by the scrambling by the scramble unit 200 configured as presented in FIG. 7 may be performed, for example, using the descramble unit 300 configured as presented in FIG. 5.

**[0087]** Next, FIG. 8 is described. FIG. 8 illustrates the fourth example of the configuration of the scramble unit 200 presented in FIG. 2.

In FIG. 8, the same numerals are assigned to the same constituent elements as those presented in FIG. 4. The description is partly omitted for these constituent elements. Meanwhile, the configuration of the scramble unit 200 presented in FIG. 4, that is, the configuration composed of the key registers 201 and 211, the XOR circuits 202, 204, 212 and 214, and the substitution function processing units 203, 213 and 220 is referred as the basic section here. That is, in the configuration of the scramble

35

unit 200 presented in FIG, 8, the configuration composed of the key register 201, the XOR circuits 202 and 204, and the substitution function processing unit 203 is referred to as a first basic section 206-1. Meanwhile, in FIG. 8, the configuration composed of the key register 211, the XOR circuits 212 and 214, and the substitution function processing units 213 and 220 is referred to as a second basic section 206-2.

**[0088]** Meanwhile, in FIG. 8, the configuration composed of the key register 221-1, the XOR circuits 222-1 and 224-1, and the substitution function processing unit 223-1 and 230-1 is referred to a first extension section 216-1. Then, in FIG. 8, the same configuration as the first extension section 216-1 composed of the key register 221-2, XOR circuit 222-2 and 224-2, and the substitution function processing units 223-2 and 230-2 is referred to as a second extension section 216-2.

[0089] That is, the scramble unit 200 presented in FIG. 8 is configured to have the first basic section 206-1 and the second basic section 206-2, and the first extension section 216-1 and the second extension section 216-2 that both scramble target data and output scrambled data

**[0090]** Here, to the second basic section 206-2, data obtained by the first scrambling described earlier performed by the first basic section 206-1 (that is, the first scrambled data) is input as the target data. Then, the second basic section 206-2 performs the second scrambling described earlier, and outputs the second scrambled data.

**[0091]** To the first extension section 216-1, as the target data, data output by the second basic section 206-2 (second scrambled data) is input. In the first extension section 216-1, the substitution function processing unit 230-1 performs one-to-one substitution conversion of the target data, and the key register 221-1, the XOR circuit 222-1, and the substitution function processing unit 223-1 generates mask data corresponding to the address data. Then, the XOR circuit 224-1 XORs the data after the substitution conversion by the substitution function processing unit 230-1 and the mask data for each bit. The first extension section 216-1 performs the further scrambling of the scrambled data output by the second basic section 206-2 as described above.

**[0092]** To the second extension section 216-2, as the target data, the scrambled data output by the first extension section 216-1 is input. In the second extension section 216-2, the substitution function processing unit 230-2 performs one-to-one substitution conversion of the target data, and the key register 221-2, the XOR circuit 222-2, and the substitution function processing unit 223-2 generates mask data corresponding to the address data. Then, the XOR circuit 224-2 XORs the data after the substitution conversion by the substitution function processing unit 230-2 and the mask data for each bit. The second extension section 216-2 performs the further scrambling of the scrambled data output by the first extension section 216-1 as described above.

**[0093]** The scramble unit 200 presented in FIG. 8 outputs the scrambled data output by the second extension section 216-2 from the data but 12 to the external RAM 2 as confidential data.

As descried above, the configuration of the scramble unit 200 presented in FIG. 8 is the one in which, in the second configuration presented in FIG. 4, the extension sections following the basic sections are connected in tandem in two stages. Therefore, in order to obtain original data by descrambling confidential data obtained by the configuration, descrambling for the extension section may be performed in inverse order twice, and descrambling for the basic section may be performed after that.

[0094] In the scramble unit 200 presented in FIG. 8, scrambling of write-in data is performed using four pieces of scramble key data stored in the four key registers 201 and 211, and 221-1 and 221-2. Therefore, in the scramble unit 200 as a whole, the key length of the scramble key data used for scrambling of write-in data becomes quadruple (4w-bit). Therefore, by adopting the configuration in FIG. 8, the resistance to the brute force key attack further improves compared with the configuration in FIG. 4.

**[0095]** Next, FIG. 9 is described. FIG. 9 illustrates the fifth example of the configuration of the scramble unit 200 presented in FIG. 2. The fifth example is the one in which the number of connection in tandem of the extension section in the fourth example presented in FIG. 8 is extended to n stages.

30 [0096] In FIG. 9, the scramble unit 200 has the basic section 206 and an extension section 216 having n (here, n is an integer at least equal to or above 1) units of extension scramble units that scramble target data and output scrambled data.

[0097] Here, the n-th extension scramble unit is configured to have a key register 221-n, the XOR circuits 222-n and 224-n, and substitution function processing units 223-n and 230-n. Here, the substitution function processing unit 230-n performs one-to-one substitution conversion of target data to be the target of scrambling in the n-th scramble unit. Meanwhile, the key register 221-n, the XOR circuit 222-n, and the substitution function processing unit 223-n obtain mask data (additional mask data) corresponding to the address data output by the processor 100. Then, the XOR circuit 224-n scrambles the data after the substitution conversion of the target data by the substitution function processing unit 230n by XORing it and the additional mask data for each bit and outputs scrambled data (additional scrambled data). Meanwhile, the target data at this time is additional scrambled data output by the (n-1)th extension scramble

**[0098]** The scramble unit 200 in FIG. 9 is configured as described above, and outputs the additional scrambled data obtained by the n-th extension scramble unit from the data bus 12 to the external RAM 2 as confidential data.

unit (however, scramble data output by the basic unit

when n=1).

20

25

30

35

40

45

**[0099]** As described above, the configuration of the scramble unit 200 presented in FIG. 9 in the one in which, in the second configuration presented in FIG. 4, the extension scramble unit following the basic section is connected in tandem in n stages. Therefore, in order to obtain original data by descrambling confidential data obtained by the configuration, descrambling for the extension scramble unit may be performed in inverse order n times, and descrambling for the basic section may be performed after that.

**[0100]** In the scramble unit 200 presented in FIG. 9, scrambling of write-in data is performed using n+2 scramble key data stored in n+2 key registers 201, 211,, 221-1, ..., 221-n. Therefore, in the scramble unit 200 as a whole, the key length of the scramble key data used for the scrambling of write-in data becomes (n+2) times ((n+2)\*w-bit). Therefore, by adopting the configuration in FIG. 9, the resistance to the brute force key attack further improved compared with the configuration in FIG. 4.

**[0101]** Meanwhile, in the configuration in FIG. 9, within the range of the allowable security, the substitution conversion processing units 230-n may be reduced to less than n units in order for a faster speed.

In addition, the present invention is not limited to the embodiments described above, and various modifications may be made at the implementation stage within the range that does not change its gist.

Claims

**1.** A data processing apparatus comprising:

an address bus configured to output address data to be given to a memory apparatus; a scramble unit configured to scramble write-in data into a storage position in the memory apparatus identified by the address data output by the address bus to obtain confidential data; and a data bus configured to output the confidential data obtained by the scramble unit,

wherein

the scramble unit comprises:

first scramble means configured to scramble the write-in data by XORing with first mask data corresponding to the address data for each bit to obtain first scrambled data;

first conversion means configured to perform one-to-one substitution conversion of the first scrambled data; and

second scramble means configured to scramble the first scrambled data after conversion by the first conversion means by XORing with second mask data corresponding to the address data for each bit to obtain second scrambled data, and

the scramble unit makes the second scramble data the confidential data.

2. The data processing apparatus according to claim 1, wherein

the first scramble means obtains the first mask data by performing substitution conversion of XOR of the address data and first scramble key data for each bit, and

the second scramble means obtains the second mask data by performing substitution conversion of XOR of the address data and second scramble key data for each bit.

15 3. The data processing apparatus according to claim1, further comprising:

first descramble means configured to descramble the confidential data read out from a storage position in the memory apparatus identified by the address data by XORing with the second mask data for each bit to obtain intermediate descrambled data;

inverse conversion means configured to perform inverse conversion of substitution conversion by the first conversion means for the intermediate descrambled data; and

second descramble means configured to descramble data after inverse conversion of the intermediate descrambled data by the inverse conversion means by XORing with the first mask data for each bit to obtain the write-in data.

**4.** The data processing apparatus according to claim 3, further comprising:

a first logic circuit configured to XOR input data and the first mask data for each bit; and a second logic circuit configured to XOR input data and the second mask data for each bit,

wherein

the first logic circuit is shared for scrambling in the first scramble means and descrambling in the second descramble means, and

the second logic circuit is shared for scrambling in the second scramble means and descrambling in the first descramble means.

50 **5.** The data processing apparatus according to claim 3, wherein

an identical substitution conversion which performs one-to-one substitution conversion of input data and in which forward conversion and inverse conversion are identical is shared for substitution conversion in the first conversion means and inverse conversion in the inverse conversion means.

20

30

35

40

45

50

55

The data processing apparatus according to claimwherein

the scramble unit further comprises at least an extension scramble unit configured to scramble target data, and

the extension scramble unit comprises:

additional conversion means configured to perform one-to-one substitution conversion of the target data; and

additional scramble means configured to scramble data after conversion of the target data by the additional conversion means by XORing with additional mask data corresponding to the address for each bit to obtain additional scrambled data, and

to the extension scramble unit, the second scrambled data is input as target data, and the scramble unit makes additional scrambled data obtained by the extension scramble unit instead of the second scrambled data.

7. A descramble apparatus configured to descramble confidential data stored in the memory apparatus by the data processing apparatus according to claim 1 to obtain the write-in data, comprising:

an address bus configured to output address data to be given to a memory apparatus;

first descramble means configured to descramble the confidential data read out from a storage position in the memory apparatus identified by the address data by XORing with the second mask data for each bit to obtain intermediate descrambled data;

inverse conversion means configured to perform inverse conversion of substitution conversion by the first conversion means for the intermediate descrambled data: and

second descramble means configured to descramble data after inverse conversion of the intermediate descrambled data by the inverse conversion means by XORing with the first mask data for each bit to obtain the write-in data.

**8.** A data processing method comprising:

an address data output step to output address data to be given to a memory apparatus from an address bus:

a scramble step to scramble write-in data into a storage position in the memory apparatus identified by the address data output by the address bus to obtain confidential data; and

a confidential data output step to output the confidential data obtained by the scramble step from a data bus, wherein

the scramble step comprises:

a first scramble step to scramble the writein data by XORing with first mask data corresponding to the address data for each bit to obtain first scrambled data;

a first conversion step to perform one-toone substitution conversion of the first scrambled data; and

a second scramble step to scramble data after conversion of the first scrambled data by the first conversion step by XORing with second mask data corresponding to the second address data to obtain second scrambled data.

and

the scramble step makes the second scrambled data the confidential data.

The data processing method according to claim 8, wherein

the first scramble step obtains the first mask data by performing substitution conversion of XOR of the address data and first scramble key data for each bit, and

the second scramble step obtains the second mask data by performing substitution conversion of XOR of the address data and second scramble key data for each bit.

**10.** The data processing method according to claim 8, further comprising:

a first descramble step to descramble the confidential data read out from a storage position in the memory apparatus identified by the address data by XORing with the second mask data for each bit to obtain intermediate scrambled data; an inverse conversion step to perform inverse conversion of substitution conversion by the first conversion step for the intermediate scrambled data; and

a second descramble step to descramble data after inverse conversion of the intermediate descrambled data by the inverse conversion step by XORing with the first mask data for each bit to obtain the write-in data.

The data processing method according to claim 10, wherein

a first logic circuit configured to XOR input data and the first mask data for each bit is shared for scrambling in the first scramble step and descrambling in the second descramble step, and

a second logic circuit configured to XOR input data and the second mask data for each bit is shared for scrambling in the second scramble step and descrambling in the first descramble step.

12. The data processing method according to claim 10,

wherein

a substitution function unit which performs one-toone substitution conversion of input data and in which forward conversion and inverse conversion are identical is shared for substitution conversion by the first conversion step and inverse conversion in the inverse conversion step.

**13.** The data processing method according to claim 8, wherein

the scramble step comprises at least an extension scramble step to scramble target data, and the extension scramble step comprises:

additional conversion step to perform one-toone substitution conversion of the target data; and

additional scramble step to scramble data after conversion of the target data in the additional conversion step by XORing with additional mask data corresponding to the address for each bit to obtain additional scrambled data,

the extension scramble step scrambles the second scrambled data as the target data, and the scramble step makes additional scrambled data obtained by the extension scramble step the confidential data instead of the second scrambled data.

**14.** A descrambling method to descramble confidential data stored in the memory apparatus by the data processing method according to claim 8 to obtain the write-in data, comprising:

an address data output step to output address data to be given to a memory apparatus from an address bus:

first descramble step to descramble the confidential data read out from a storage position in the memory apparatus identified by the address data by XORing with the second mask data for each bit to obtain intermediate descrambled data;

inverse conversion step to perform inverse conversion of substitution conversion by the first conversion means for the intermediate scrambled data; and

second descramble step to descramble data after inverse conversion of the intermediate descrambled data by the inverse conversion means by XORing with the first mask data for each bit to obtain the write-in data.

10

15

20

25

30

35

40

45

50

FIG. 1

FIG. 3

FIG. 4

FIG. 5

|            | 4-       | ته     |

|------------|----------|--------|

|            | -        | C      |

|            | 9        |        |

| '          | Р        | q      |

|            | ပ        | _      |

|            | _0       | 4      |

|            | a        | 9      |

|            | δ        | 6      |

| 7          | $\infty$ | 4      |

| <b>G</b> 1 | 7        | 3      |

|            | 9        | a      |

|            | 2        | 5      |

|            | 4        | ъ      |

|            | 3        | -      |

|            | 2        | 2      |

|            | -        | 0      |

|            | 0        | 8      |

|            | 4-       | 8      |

|            | е        | Ŧ      |

|            | Ð        | 4      |

|            | ပ        | e      |

|            | q        | р      |

|            | В        | 9      |

|            | 6        | 6      |

|            | 8        | 0      |

| <b>G</b> 1 | 7        | C      |

|            | 9        | а      |

|            | 5        | 5      |

|            | 4        | q      |

|            | 3,       | 7      |

|            | 2 (      | 7      |

|            |          | 1 3 2  |

|            | 0 1      |        |

|            |          |        |

|            | INPUT    | OUTPUT |

FIG. 6A

| G1 <sup>-1</sup> | b c d e f | b c 9 e f |

|------------------|-----------|-----------|

|                  | <u>a</u>  | 7         |

|                  | 6         | 0         |

|                  | $\infty$  | 9         |

|                  | 7         | 5         |

|                  | 9         | $\infty$  |

|                  | 5         | _         |

|                  | 4         | 117       |

|                  | 3         | 10        |

|                  | 0 1 2     | a         |

| ŀ                | _         | 4         |

|                  |           | f 3       |

|                  | 4         | 4         |

|                  | 9         | e         |

|                  | ਰ         | 9         |

|                  | ၁         | o<br>q    |

|                  | 9         | 9         |

|                  | a         | 2         |

|                  | 6         | 9 p       |

| <b>G1</b>        | ∞         |           |

|                  | 19        | 5         |

|                  | 9         | ∞         |

|                  | 5         | 1 7       |

|                  | 4         |           |

|                  | က         | 0         |

|                  | 2         | ·a        |

|                  |           | 4         |

|                  | 0         | 3         |

|                  | INPUT     | OUTPUT 3  |

FIG. 6B

FIG. 7

# EP 2 413 305 A1

# INTERNATIONAL SEARCH REPORT

International application No.

PCT/JP2009/001276

|                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                 | PCT/JE                                                                                                                                                                                                               | 2009/001276                               |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|--|

|                                                                                                                                                                                                                                                                                             | ATION OF SUBJECT MATTER<br>2006.01)i, <i>G06F21/24</i> (2006.01)i                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                      |                                           |  |

| According to Inte                                                                                                                                                                                                                                                                           | ernational Patent Classification (IPC) or to both national                                                                                                                                                                                                                                                                                                                                      | l classification and IPC                                                                                                                                                                                             |                                           |  |

| B. FIELDS SE                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                      |                                           |  |

|                                                                                                                                                                                                                                                                                             | nentation searched (classification system followed by cl $$ G $$ G $$ F $$ 2 $$ 4 $$                                                                                                                                                                                                                                                                                                            | assification symbols)                                                                                                                                                                                                |                                           |  |

| Jitsuyo<br>Kokai J:                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                 | tsuyo Shinan Toroku Koho<br>roku Jitsuyo Shinan Koho                                                                                                                                                                 | 1996-2009<br>1994-2009                    |  |

| Electronic data c                                                                                                                                                                                                                                                                           | and consumed during the international section (maine of                                                                                                                                                                                                                                                                                                                                         | data base and, where practicable, search                                                                                                                                                                             | in terms used)                            |  |

| C. DOCUMEN                                                                                                                                                                                                                                                                                  | ITS CONSIDERED TO BE RELEVANT                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                      |                                           |  |

| Category*                                                                                                                                                                                                                                                                                   | Citation of document, with indication, where ap                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                      | Relevant to claim No.                     |  |

| X<br>Y<br>Y                                                                                                                                                                                                                                                                                 | JP 2007-328789 A (Samsung Electronics Co.,<br>Ltd.),<br>20 December, 2007 (20.12.07),<br>Par. Nos. [0062] to [0076]; Figs. 2 to 4<br>& US 2007/0286413 A1 & GB 2438972 A<br>& GB 710989 D0 & DE 102007026977 A<br>& FR 2902252 A & FR 2906665 A<br>& KR 10-2007-0117172 A & CN 101086769 A<br>JP 2008-58829 A (Sony Corp.),<br>13 March, 2008 (13.03.08),<br>Par. Nos. [0031] to [0034]; Fig. 2 |                                                                                                                                                                                                                      | 1,3,6-8,10,<br>13-14<br>2,4-5,9,<br>11-12 |  |

| × Further do                                                                                                                                                                                                                                                                                | & WO 2008/026623 A1                                                                                                                                                                                                                                                                                                                                                                             | See patent family annex.                                                                                                                                                                                             |                                           |  |

| * Special categories of cited documents: "T" later document published after the international filing date or priority                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                      |                                           |  |

| "A" document defining the general state of the art which is not considered to be of particular relevance date and not in conflict with the application but cited to understand the principle or theory underlying the invention                                                             |                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                      |                                           |  |

| "E" earlier application or patent but published on or after the international filing date "X" document of particular relevance; the claimed invention care considered novel or cannot be considered to involve an                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                 | dered to involve an inventive                                                                                                                                                                                        |                                           |  |

| "L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)  step when the document is taken along the document of particular relevance; the considered to involve an inventive |                                                                                                                                                                                                                                                                                                                                                                                                 | claimed invention cannot be                                                                                                                                                                                          |                                           |  |

| "O" document referring to an oral disclosure, use, exhibition or other means "P" document published prior to the international filing date but later than the priority date claimed                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                 | considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art document member of the same patent family |                                           |  |