11) Veröffentlichungsnummer:

**0 000 863** A1

12

## EUROPÄISCHE PATENTANMELDUNG

(1) Anmeldenummer: 78100173.0

(5) Int. Cl.2: **H 01 L 23/56**, H 01 L 27/08

2 Anmeldetag: 15.06.78

@ Priorität: 18.08.77 US 825759

(1) Anmelder: International Business Machines Corporation, Armonk, N.Y. 10504 (US)

Veröffentlichungstag der Anmeldung: 07.03.79 Patentblatt 79/5 Erfinder: Bergeron, David Leo, 7606 Wedgewood Drive, Manassas, Virginia 22110 (US)

Erfinder: Stephens, Geoffrey Brownell, 10 Mercer Court, Catlett, Virginia 22019 (US)

84 Benannte Vertragsstaaten: DE FR GB

(4) Vertreter: Jost, Otto Karl, Dipl.-Ing., Schönalcher Strasse 220, D-7030 Böblingen (DE)

## 3 Temperaturkompensierter integrierter Halbieiterwiderstand.

Zur Kompensation des Temperaturganges von integrierten Halbleiterwiderständen wird die Erkenntnis angewandt, dass der Wert eines Widerstandes auch eine Funktion der Potentialdifferenz zwischen dem Widerstand (8) selbst und der diesen umgebenden Epitaxieschicht 4 ist. Die Temperaturkompensation wird dadurch bewirkt, dass ein Temperaturfühler an die Epitaxieschicht angeschlossen wird und eine Kompensationsspannung liefert, welche die Potentialdifferenz gegenläufig zu dem Widerstandstemperaturkoeffizienten des Widerstands beeinflusst. Auf diese Weise wird der Widerstand (8) über einen weiten Temperaturbereich konstant gehalten.

Anmelderin:

International Business Machine Corporation, Armonk, N.Y.10504 jo/bm-se

Temperaturkompensierter integrierter Halbleiterwiderstand

Die Erfindung bezieht sich auf einen temperaturkompensierten integrierten Halbleiterwiderstand nach dem Oberbegriff des Anspruchs 1.

Bekannte integrierte Halbleiterwiderstände weisen ein Widerstands-/Temperaturverhalten auf, das durch ihren Widerstandstemperaturkoeffizienten (TCR) bestimmt ist. Es wurden bisher zahlreiche Versuche unternommen, den Widerstandstemperaturkoeffizienten zu verringern.

Es wurden auch schon Schaltungsvorschläge gemacht und verwendet, um die Widerstandsänderungen hinsichtlich der Temperatur dadurch zu kompensieren, daß eine PN-Sperrschicht mit einem entgegengesetzten Widerstandstemperaturkoeffizienten in Reihe mit dem Widerstand geschaltet wurde.

Diese bekannten Maßnahmen zur Lösung des Problems des Temperaturgangs von integrierten Halbleiterwiderständen waren begrenzt hinsichtlich des zu kompensierenden Widerstandsbereichs, des linearen Verlaufs des Serienwiderstands, des Temperaturbereichs, über den der Widerstandstemperaturkoeffizient kompensiert werden konnte und in den Anforderungen, die sich aus den Kompensationsschaltungen selbst ergaben.

In der US-PS 3 683 306 ist beispielsweise ein Verfahren beschrieben, mit dem der Widerstandstemperaturkoeffi-

10

15

20

zient auf Null gebracht werden soll, indem das Mittel der Ionenimplantation eingesetzt wird, um Gefügeschäden in dem Gebiet zu verursachen, in das der integrierte Halbleiterwiderstand eingebracht werden soll.

5

10

Dann ist in der US-PS 3 947 866 ein integrierter Halbleiterwiderstand beschrieben, der in seinem mittleren Teil dicker ist, als an seinen äußeren Enden, so daß der dickere Mittelteil einen negativen Widerstandstemperaturkoeffizienten und die äußeren Teile einen positiven Widerstandstemperaturkoeffizienten haben. Es wird in der Beschreibung dieser US-PS angegeben, daß der Widerstand insgesamt einen Widerstandstemperaturkoeffizienten Null erreicht.

15

20

25

Alle diese bekannten Lösungen des Problems, die Widerstandsänderung eines Widerstandes in Abhängigkeit von seiner Betriebstemperatur zu kompensieren, haben zwar dieses Ziel erreicht, aber andere Probleme geschaffen, die insgesamt nachteilig sind. So ist beispielsweise eine Zunahme der Komplexität der Herstellungsprozesse ebenso von Nachteil, wie die Tatsache, daß der Bereich der Widerstandswerte, die erzielbar sind, begrenzt ist, sowie daß auch der Temperaturbereich begrenzt ist, über den eine gewünschte Widerstands-/Temperaturkompensation möglich ist.

Hier will die Erfindung Abhilfe schaffen, indem sie eine verbesserte Widerstands-/Temperaturkompensation angibt,

die die genannten Nachteile, d.h. Komplexität des Herstellungsprozesses, Begrenzung des Widerstandsbereichs, sowie Begrenzung des Widerstands-/Temperaturkompensationsbereichs, vermeidet.

Gelöst wird diese Aufgabe der Erfindung durch die im Hauptanspruch angegebenen Merkmale.

Vorteilhafte Ausgestaltungen und Weiterbildungen des 5 Gegenstandes der Erfindung sind den Unteransprüchen zu entnehmen.

Durch die Erfindung wird also der Vorteil erzielt, daß zur Herstellung eines integrierten, temperaturkompensierten Halbleiterwiderstandes normale, unkomplizierte Prozesse verwendet werden können. Außerdem können Widerstandswerte über einen großen Bereich erzeugt werden, die zudem noch in weiten Temperaturbereichen kompensierbar sind.

15

Im folgenden wird ein Ausführungsbeispiel der Erfindung anhand der Fign. erläutert.

Es zeigen:

20

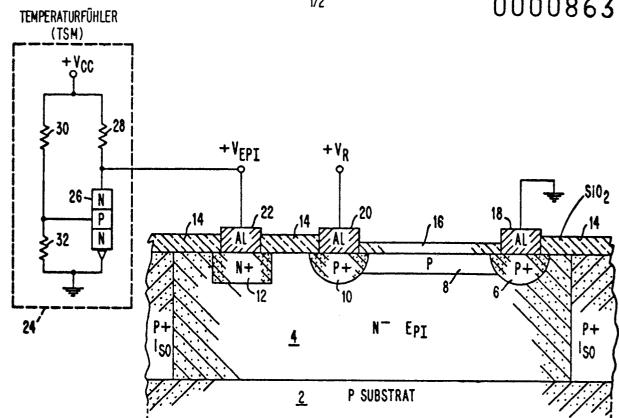

- Fig. 1 eine schematische Querschnittsdarstellung eines durch Ionenimplantation in eine Epitaxieschicht eingebauten Widerstands und das Blockschaltbild einer Temperaturkompensationsschaltung,

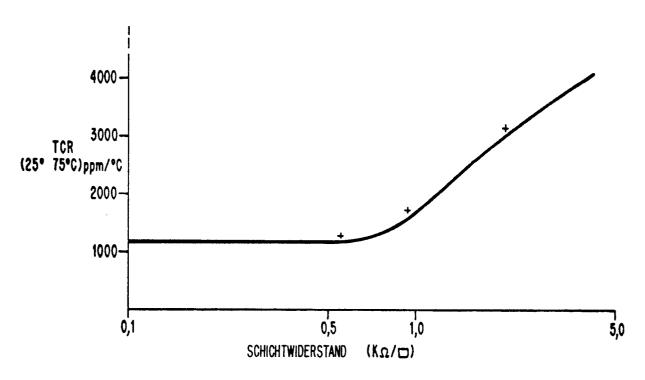

- Fig. 2 eine graphische Darstellung des Verlaufs des Widerstandstemperaturkoeffizienten (TCR) eines durch Ionenimplantation hergestellten Widerstandes als Funktion des Schichtwiderstandes und

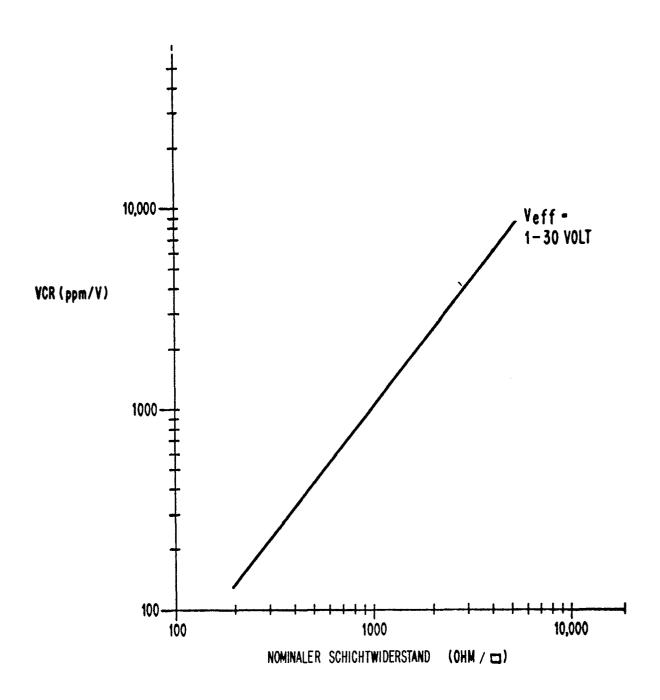

- Fig. 3 eine graphische Darstellung des Verlaufs des Widerstandsspannungskoeffizienten (VCR) als Funktion des nominellen Schichtwiderstands

für einen Widerstand, der aus den gleichen Prozeßbedingungen und der gleichen Implantationsdosis entstanden ist, wie der in Fig. 2 zugrundegelegte.

5

10

15

20

25

30

35

Der Widerstand eines durch Ionenimplantation oder Diffusion hergestellten Widerstands, ist eine Funktion der Temperatur, bei der er betrieben wird. Die hier dargestellte Temperaturkompensationsschaltung basiert auf der Erkenntnis, daß der Widerstand eines solchen Widerstandes auch eine Funktion der Potentialdifferenz zwischen dem Anschluß des Widerstands, der das höchste positive Potential führt und der Epitaxieschicht selbst ist. Eine Temperaturkompensation wird dadurch bewirkt, daß ein Temperaturfühler mit der Epitaxieschicht verbunden ist, die eine Ausgangsspannung führt, die sich gegenläufig zum Widerstandstemperaturkoeffizienten des Widerstandes verändert. Daher nähert sich die Gesamtwiderstandsänderung des betrachteten durch Ionenimplantation oder Diffusion hergestellten Widerstandes über einen weiten Bereich von Temperaturschwankungen dem Wert Null.

In Fig. 1 ist eine N-leitende epitaktische Halbleiterschicht 4 dargestellt, die auf einem P-leitenden Substrat 2 aufgebracht ist. Die P-dotierten Kontaktbereiche sind bei 6 und 10 dargestellt, wobei sich zwischen ihnen in der Epitaxieschicht der Widerstand 8 aus P-dotiertem Material befindet. Der Widerstand 8 ist als ein durch Ionenimplantation hergestellter Widerstand dargestellt, obwohl das Prinzip der Erfindung auch auf nach anderen Prinzipien hergestellte Widerstände anwendbar ist, für die eine Widerstandstemperaturkompensation gewünscht wird; d.h. es kann auch ein in die Epitaxieschicht  ${\rm E}_{\rm PI}$  hineindiffundierter Widerstand anstelle des durch Ionenimplantation hergestellten Widerstandes verwendet werden.

Der Widerstand des mittels Ionenimplantation hergestellten Widerstands 8 nimmt mit steigender Temperatur zu. Um diesen Widerstandszuwachs zu kompensieren, muß dafür gesorgt werden, daß der Widerstandsspan-5 nungskoeffizient der Potentialdifferenz zwischen der Epitaxieschicht 4 und dem Widerstand 8 eine gleiche und entgegengerichtete Widerstandsänderung des Widerstandes 8 bewirkt. Die PN-Sperrschicht, die den Widerstand 8 in der Epitaxieschicht 4 umgibt, hat eine Verarmungszone, 10 deren Dicke mit abnehmender Potentialdifferenz zwischen dem Widerstand 8 und der Epitaxieschicht 4 abnimmt. Wenn die Temperatur der Anordnung ansteigt, wodurch auch der Wert des Widerstandes 8 zunimmt, wird zur Kompensation dieses Temperaturganges die Potentialdifferenz zwischen 15 der Epitaxieschicht 4 und dem Widerstand 8 abgesenkt, was zur Folge hat, daß die den Widerstand 8 umgebende Verarmungszone den Querschnitt des Widerstandes 8 weniger einschnürt, wodurch wiederum durch den so vergrößerten Querschnitt der Wert des Widerstandes 8 kleiner wird. Um dieses durchzuführen, ist eine Schaltungsanordnung 24 20 über einen Kontakt 12 und einen Aluminiumkontakt 22 an die Epitaxieschicht 4 angeschlossen, wobei die genannte Schaltung ihre Ausgangsspannung  $\mathbf{V}_{\text{EPT}}$  in dem Maße absenkt, wie die Temperatur ihrer Umgebung ansteigt. Wie an sich 25 bekannt ist, sind auch an den Positionen 18 und 20 Kontakte angebracht. Durch ein Absenken des Potentials  $\mathbf{V}_{\mathtt{EPT}}$  mit zunehmender Temperatur, wird daher die gewünschte Widerstandskompensation für den Widerstand 8 bewirkt.

Die Schaltungsanordnung 24 besteht aus zwei parallel geschalteten Spannungsteilern, die zwischen einer Spannung +V<sub>CC</sub> und Erde angeschlossen sind. In dem ersten Spannungsteiler bilden die Widerstände 30 und 32 einen

Spannungsteiler mit einem Abgriff, der an die Basis eines NPN-Transistors 26 angeschlossen ist. Der zweite Spannungsteiler besteht aus einem Widerstand 28 und dem NPN-Transistor 26, deren gemeinsamer Verbindungspunkt auch der Ausgangsknoten der Schaltung für die Erzeugug der Spannung  $V_{epi}$  ist. Der Spannungsabfall zwischen  $V_{CR}$ und der Basis des Transistors 26, wird mit Hilfe der konstanten Größe von  $\mathbf{V}_{\mathbf{CC}}$  und dem konstanten Verhältnis der Widerstände 30 und 32 konstant gehalten. Auf diese Weise wird auch die Basis- Emitterspannung des NPN-Transistors 26 konstant gehalten. Die PN-Sperrschicht am Emitter-Basis-Übergang des NPN-Transistors 26 verändert jedoch ihre Stromflußcharakteristik mit der Änderung der Umgebungstemperatur.

15

20

10

5

Wie oben bereits erwähnt wurde, wird die Potentialdifferenz zwischen dem Widerstand 8 und der Epitaxieschicht 4 gesenkt, um eine Widerstandsverringerung entsprechend des Widerstandsspannungskoeffizienten des Transistors zu erreichen. Da sowohl der Widerstand, als auch die Epitaxieschicht positiv bezüglich des Widerstandes vorgespannt sind, muß der Epitaxieschicht 4 eine ins Negative driftende Spannungsänderung aufgezwungen werden, um den Widerstandswert des Widerstandes 8 zu 25 verringern ( $V_{EPI} > V_{R}$  in Fig. 1). Um eine ins Negative driftende Spannung zu erzeugen, muß die Schaltungsanordnung 24 mit steigender Temperatur eine ins Negative gehende Änderung der Spannung  $V_{EDT}$  generieren. Dieses wird durch den Transistor 26 erreicht, der mit 30 steigender Temperatur einen größer werdenden Stromfluß zur Folge hat, wodurch auch ein größerer Strom durch den mit ihm in Serie geschalteten Widerstand 28 fließt und somit dessen Spannungsabfall größer und das Potential an seinem Ausgangsknoten kleiner wird, so daß auch die Spannung  $V_{\text{EPT}}$  mit steigender Temperatur

abnimmt. Durch geeignete Auswahl der Größen der Widerstände 28, 30 und 32, kann die Größe der Veränderung von  $V_{\rm EPI}$  erreicht werden, die eine Verringerung des Widerstands 8 gemäß seinem Widerstandsspannungskoeffizienten bewirkt, die exakt dem Ansteigen des Widerstandswertes des Widerstands 8 entsprechend seines Temperaturzuwachses entgegenwirkt.

Durch Einhaltung eines konstanten Basis- Emitterpotentials längs des Widerstandes 32 und durch das Anheben der Leitfähigkeit des Widerstands 6 mit der Temperatur, kann ein größerer Strom durch den Serienwiderstand 28 getrieben werden, der die Größe der Spannung V<sub>EPI</sub> an seinem Ausgangsknoten in der gewünschten Weise verringert.

15

10

5

Fig. 2 zeigt eine graphische Darstellung des Widerstandstemperaturkoeffizienten über dem Widerstand der Schicht für durch Ionenimplantation hergestellte Widerstände, bei einer bestimmten Gruppe von Prozeßbedingungen über 20 einem weiten Bereich der Ionenimplantationsdosis, die Schichtwiderstände von 100 Ohm je Flächenelement bis 5000 Ohm je Flächenelement ergeben. Der Widerstandstemperaturkoeffizient erstreckt sich dabei über einen Bereich von etwa 1100 Teile je Million und je Grad Celsius (ppm/OC) bis über 4000 ppm/OC für diesen Bereich 25 des Schichtwiderstands. Andere Kurven mit höherem oder niedrigerem Widerstandstemperaturkoeffizienten können dadurch erreicht werden, daß der Satz von Prozeßbedingungen verändert wird, insbesondere die Implantations-30 energie, die Oxyddicke, die Hintergrundkonzentration (Epitaxie) und Erhitzungsdauer und -temperatur des der Implantation nachgeschalteten Wärmeschrittes.

Aus Fig. 2 ist beispielsweise zu sehen, daß ein Widerstand bei einem Schichtwiderstand von 5000 Ohm je Flächenelement einen Widerstandstemperaturkoeffizienten von etwa 4000 ppm/°C hat. Daher wird ein Widerstand, dessen Widerstandswert 10 000 Ohm bei 25 °C ist, einen Widerstand von 10 000 + 10 000 x 4 000 x 10 6 x (75-25) oder 12 000 Ohm bei 75 °C haben.

Fig. 3 zeigt eine graphische Darstellung des Wider-10 standsspannungskoeffizienten (VCR) über dem nominellen Schichtwiderstand, für einen nach den gleichen Prozeßbedingungen hergestellten Widerstand, wie der im Zusammanhang mit Fig. 2 erläuterte. Die Widerstandsänderung mit der Spannung ist von der Ladungsträgerverarmung 15 längs der PN-Sperrschicht abhängig, die zwischen dem Widerstandsbereich und der entgegengesetzt dotierten Epitaxieschicht gebildet ist. Die Dicke des an Ladungsträgern verarmten Bereichs ist eine Funktion der Dotierungskonzentration auf beiden Seiten der Sperrschicht, 20 sowie der Potentialdifferenz (elektrisches Feld) zwischen beiden Seiten der Sperrschicht.

Das Potential (Vorspannung) über der Sperrschicht, ist sowohl eine Funktion des an die Epitaxieschicht angelegten Potential relativ zu dem positiven Ende des Widerstandes und dem Potential, das an beide Enden des Widerstandes angelegt wird. Die Gesamtwirkung dieser beiden Potentiale kann ausgedrückt werden als eine kombinierte effektive Spannung (Veff), die in folgendem algebraischen Ausdruck erfaßbar ist:

$$v_{\text{eff}} = v_{\text{EPI}} - (+v_{\text{R}}) + \frac{v_{\text{R}}}{2}$$

5

25

Diese Spannung kann als mittlere Potentialdifferenz über der Widerstands-Epitaxiesperrschicht angesehen werden.

Aus den in den Fign. 2 und 3 dargestellten Beziehungen ist zu sehen, daß ein Anwachsen des Widerstandes infolge steigender Temperatur durch ein Absenken der effektiven Spannung über der PN-Sperrschicht ausgeglichen werden kann.

10

1

Wenn beispielsweise ein Widerstand von 5000 Ohm je Flächenelement bei 25 °C ein TCR von 4000 ppm/°C und ein VCR von 10 000 ppm/V hat, dann hat er annähernd einen konstanten Wert von 25 °C bis 75 °C, wenn die Vorspannung der Epitaxieschicht gegenüber dem positiven Ende des Widerstandes von 30 Volt bei 25 °C bis 10 Volt bei 75 °C eingestellt wird. Die Einstellung der Vorspannung an der Epitaxieschicht wird von der in Fig. 1 dargestellten Schaltungsanordnung vorgenommen, deren Temperaturfühler in unmittelbarer Nähe des Widerstandes, dessen Temperatur dann zu kompensieren ist, angebracht ist, so daß die Temperatur des Widerstands die gleiche oder fast die gleiche ist, wie die Temperatur des Fühlers TSM.

Beispiele anderer möglicher Realisierungen der Kompensation des Temperaturganges können darin gesehen werden, daß eine P-Zone innerhalb einer N-Epitaxieschicht und die Epitaxieschicht verwendet wird, um einen Widerstand zu bilden, dessen Temperaturänderung durch Änderungen der Verarmungszone kompensiert wird, die durch die umgekehrt vorgespannte P-Zone gebildet wird.

Gemäß einem anderen Ausführungsbeispiel wird ein Widerstand dadurch gebildet, daß eine P-Zone in einer N-Epitaxieschicht, beispielsweise einer solchen, die zur Herstellung einer Transistorbasis-Zone verwendet wird, die von einer schmaleren N+-Zone überlappt wird, wie es bei einer solchen der Fall ist, die dazu verwendet wird, um eine Transistoremitterzone zu bilden. Es handelt sich hierbei also um einen sogenannten Pinch-Widerstand. Die Kompensation des Temperaturganges des P-Widerstands wird dadurch erreicht, daß die entgegengesetzte Vorspannung an der N+-Zone und der Epitaxieschicht bezüglich der P-Widerstandszone variiert wird. Das ausführlich erläuterte Ausführungsbeispiel kann erweitert werden, indem mehrere Widerstände in einer gemeinsamen Epitaxieschicht kompensiert werden, wobei nur dieser eine Temperaturfühler mit der Kompensationsschaltung nach Fig. 1 verwendet wird.

5

## PATENTANSPRÜCHE

- 1. Temperaturkompensierter integrierter Halbleiterwiderstand mit einem Widerstandsgebiet des einen 5 Leitfähigkeitstyps in einer Epitaxieschicht des entgegengesetzten Leitfähigkeitstyps, das einen Abstand von einanderaufweisende elektrische Kontakte besitzt. dadurch gekennzeichnet, daß einer der elektrischen Kontakte (18; Fig. 1) auf einem Referenzpotential 10 liegt, der Widerstand (8) einen positiven Widerstandsspannungskoeffizienten (VCR) und einen gegebenen Widerstandstemperaturkoeffizienten (TCR) hat, ein Temperaturfühler (24) vorgesehen ist, der auf der integrierten Schaltung dicht am Widerstand liegt und 15 dessen Ausgangsspannungsanschluß an die Epitaxieschicht (4) angeschlossen ist und dessen Spannungsbezugsanschluß auf Referenzpotential liegt, wobei die Ausgangsspannungscharakteristik des Temperaturfühlers bezüglich der Temperatur an seinem Ausgangs-20 anschluß einen zum Widerstandsspannungskoeffizienten des Widerstandes entgegengesetzten Verlauf hat und die Widerstandsänderungen des Widerstandes bezüglich der Temperatur durch diese Spannungsänderungen des Temperaturfühlers an der Epitaxieschicht kompensiert 25 werden.

- 2. Temperaturkompensierter integrierter Halbleiterwiderstand nach Anspruch 1, dadurch gekennzeichnet, daß der mit seinem Ausgangsanschluß über einen ersten Kontakt (22, 12) an die Epitaxieschicht (4) und mit seinem Spannungsbezugsanschluß an die Referenzspannung (Erde) angeschlossene Temperaturfühler (24) aus zwei parallel geschalteten Spannungsteilern (26, 28; 30, 32) besteht, von denen der eine Teilwiderstand aus einem einen negativen Temperaturgang auf-

weisenden steuerbaren Widerstand (26) besteht, dessen Steuerelektrode mit dem Abgriff des einen Spannungsteilers zwischen seinen Teilwiderständen (30, 32) verbunden ist und wobei der Ausgangsspannungsanschluß mit dem Abgriff des zweiten Spannungsteilers zwischen dessen Teilwiderständen (26, 28) identisch ist und die Versorgungsspannung (V<sub>CR</sub>) zwischen der Verbindung zwischen den beiden festen Widerständen (28, 30) und der Verbindung zwischen dem anderen festen (32) und dem steuerbaren Widerstand (26) angeschlossen ist.

- 3. Temperaturkompensierter integrierter Halbleiterwiderstand nach Anspruch 2, dadurch gekennzeichnet, daß der steuerbare Widerstand (26) aus einem NPN-Transi-15 stor gebildet ist, dessen Emitter-Basisspannung durch einen konstanten Spannungsabfall zwischen der Versorgungsspannung ( $V_{CR}$ ) und der Basis des Transistors, bewirkt durch eine konstante Versorgungsspannung und das feste Verhältnis der Widerstände (30, 32) des einen 20 Spannungsteilers, konstant gehalten wird, wodurch sich aber der Stromfluß durch die PN-Sperrschicht zwischen Emitter und Basis mit der Temperatur und somit auch durch den Serienwiderstand (28) des anderen Spannungsteilers und damit die Höhe der Epitaxieschichtspan-25 nung (V<sub>epi</sub>) ändert.

- Temperaturkomensierter integrierter Halbleiterwiderstand nach Anspruch 3, dadurch gekennzeichnet, daß

die mittlere Potentialdifferenz (V<sub>eff</sub>) zwischen dem Widerstandsgebiet (8) und der Epitaxieschicht (4) nach folgender Beziehung gewählt ist:

$$v_{eff} = v_{epi} - (+v_R) + \frac{v_R}{2}$$

wobei  $+V_R$  die an dem einen Kontakt (20) des Widerstands (11) anliegende Spannung und  $V_{\rm epi}$  die an einem Kontakt (22) der Epitaxieschicht anliegende Spannung ist.

5

10

5. Temperaturkompensierter integrierter Halbleiterwiderstand nach einem oder mehreren der Ansprüche 1 bis 4, dadurch gekennzeichnet, daß gleichzeitig mehrere nach Anspruch 1 gebildete integrierte Halbleiterwiderstände (11) von einem Temperaturfühler (24), der in der nach Anspruch 2 angeführten Weise angeschlossen ist, in ihrem jeweiligen Widerstandswert temperaturkompensierbar sind.

FIG.

FIG.

FIG. 3

## **EUROPEAN SEARCH REPORT**

$0 \text{ pp } 99863_{73}$

|             | DOCUMENTS CONS                                               | CLASSIFICATION OF THE APPLICATION (Int. Ci. <sup>2</sup> ) |                      |                                                                                                                                                                                                                                                                                   |

|-------------|--------------------------------------------------------------|------------------------------------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Category    | Citation of document with ind passages                       | lication, where appropriate, of relevant                   | Relevant<br>to claim |                                                                                                                                                                                                                                                                                   |

|             | US - A - 3 700<br>* Figure 1;                                | 977 (MOTOROLA)<br>claim 1 *                                | 1                    | H 01 L 23/56<br>H 01 L 27/08                                                                                                                                                                                                                                                      |

| A           | US - A - 3 484<br>GRAPH AND TELE:<br>* Claim 1 *             | 658 (NIPPON TELE-<br>PHONE)                                | 1                    |                                                                                                                                                                                                                                                                                   |

| A           | ELECTRONICS, vo                                              | <br>ol. 48, 23-1-1975,<br>olithic converter                | , 1 , 3              | TECHNICAL FIELDS<br>SEARCHED (Int.Cl.²)                                                                                                                                                                                                                                           |

|             |                                                              | asurement capabili-                                        |                      | H 01 L 23/56<br>H 01 L 27/08<br>H 01 L 27/02                                                                                                                                                                                                                                      |

| P           | FR - A - 2 351  * Claims 1,2  & DE 2 720 653  & GB 1 517 266 |                                                            | 1-4                  |                                                                                                                                                                                                                                                                                   |

|             |                                                              |                                                            |                      | CATEGORY OF CITED DOCUMENTS  X: particularly relevant A: technological background O: non-written disclosure P: intermediate document T: theory or principle underlyin the invention E: conflicting application D: document cited in the application L: citation for other reasons |

| d           | The present search report has been drawn up for all claims   |                                                            |                      | &: member of the same patent family, corresponding document                                                                                                                                                                                                                       |

| lace of sea | The Hague                                                    | Date of completion of the search 15–11–1978                | Examiner             | DE RAEVE                                                                                                                                                                                                                                                                          |