1) Veröffentlichungsnummer:

0 012 863

**A2**

(12)

## **EUROPÄISCHE PATENTANMELDUNG**

(21) Anmeldenummer: 79104724.4

(22) Anmeldetag: 27.11.79

(5) Int. Cl.<sup>3</sup>: **H 01 L 21/31** H 01 L 27/04, G 11 C 11/24

(30) Priorität: 26.12.78 US 973219

(43) Veröffentlichungstag der Anmeldung: 09.07.80 Patentblatt 80/14

Benannte Vertragsstaaten:

DE FR GB

71 Anmelder: International Business Machines Corporation

Armonk, N.Y. 10504(US)

(72) Erfinder: Noble Jr., Wendell Phillips RFD Nr. 3 Milton, Vermont 05468(US)

(2) Erfinder: Unis, Richard Alan 4 Old Mill Drive Poughkeepsie, New York 12603 (US)

(74) Vertreter: Mönig, Anton, Dipl.-Ing. Schönsicher Strasse 220 D-7030 Böblingen(DE)

(54) Verfahren zur Herstellung von Halbleiteranordnungen mit herabgesetzter parasitärer Kapazität.

(57) Zur Herabsetzung einer parasitären Kopplung zwischen mindestens einem in einem Halbleitersubstrat (10) angeordneten Dotierungsgebiet (20) und einer darüber vorgesehenen elektrisch leitfähigen Schicht (28), die über dem Dotierungsgebiet (20) einen größeren Abstand von der Substratoberfläche als außerhalb davon und somit eine unebene Oberfläche aufweist, wird auf die unebene Oberfläche der leitfähigen Schicht (28) eine diese vollständig bedeckende Maskierungsschicht (30), vorzugsweise aus einem Photolack, aufgebracht, so daß eine nunmehr eingeebnete Oberfläche (32) gebildet wird. Anschließend wird von der Maskierungsschicht (30) ein einheitlicher Schichtdickenanteil (L) abgetragen, bis die Oberfläche des Bereiches der elektrisch leitfähigen Schicht (28) mit der höchsten Erhebung freigelegt ist. Daraufhin wird die leitfähige Schicht (28) in dem derart freigelegten Bereich entfernt. Mit dem angegebenen Verfahren lassen sich vorteilhaft kapazitive Eine-FET-Speicheranordnungen mit geringer Bitleitungskapazität aufbauen, wenn die Bitleitung als streifenförmiges Dotierungsgebiet (20) im Substrat (10) ausgeführt ist und die, vorzugsweise aus polykristallinem Silicium bestehande, leitfähige Schicht (28) als Abschirmschicht bzw. als eine Elektrode der Speicherkondensatoren ausgefürt ist.

EP 0 012 863 A2

FIG. 9

Verfahren zur Herstellung von Halbleiteranordnungen mit herabgesetzter parasitärer Kapazität

Die Erfindung betrifft ein Verfahren zur Herstellung von Halbleiteranordnungen mit herabgesetzter kapazitiver Kopplung zwischen mindestens einem in einem Halbleitersubstrat angeordneten Dotierungsgebiet und einer isoliert auf dem Sub5 strat vorgesehenen elektrisch leitfähigen Schicht, die über dem Dotierungsgebiet einen größeren Abstand von der Substratoberfläche als außerhalb des Dotierungsgebiets und somit eine unebene Oberfläche aufweist. Sie bezieht sich insbesondere auf Maßnahmen zur Herabsetzung parasitärer Bitleitungskapa10 zitäten in Speicheranordnungen, bei denen die Bitleitungen in Form von Dotierungsgebieten im betreffenden Halbleitersubstrat ausgeführt sind, wobei über dem Substrat mindestens eine elektrisch leitende Schicht vorgesehen ist.

15 Zum Stand der Technik bezüglich der Herstellung und des Aufbaus von dynamischen MOSFET-Speicheranordnungen unter Einsatz einer aus einem dotierten Oxid bestehenden Diffusionsquellschicht sowie einer leitfähigen Abschirmschicht aus polykrstallinem Silicium kann auf die US-Patentschriften 20 3 811 076 und 3 841 926 in Verbindung mit der weiteren US-Patentsschrift 3 387 286 Bezug genommen werden. Dort wird der Aufbau einer Speicherzellenstruktur beschrieben, die mit einem einzigen Transistor sowie einem Kondensator auskommt, wobei eine aus polykristallinem Silicium bestehende 25 Abschirmschicht von der darunter angeordneten diffundierten Bitleitung durch eine relativ dünne dielektrische Schicht aus Siliciumdioxid und Siliciumnitrid beabstandet ist, die das Gate-Dielektrikum des Transistors bildet. Allen Bemühungen zu größeren Packungsdichten solcher Speicheranordnungen 30 liegt dabei zugrunde, daß eine möglichst kleinflächige Speicherzelle bereitzustellen ist, die ein brauchbares Lesesignal gewisser Mindestgröße zu liefern in der Lage ist, das durch

die Abfühlschaltkreise zuverlässig erkannt und zugeordnet werden kann. Die Größe eines solchen Lesesignals ist abhängig von der Größe des Speicherkondensators, den angelegten Spannungen und der Kapazität der Bit-Abfühlleitungen. 5 Auf dem Gebiet solcher Speicheranordnungen kommt dem sog. Übertragungsverhältnis (transfer ratio) als dem Verhältnis der effektiven Kapazität einer Bitleitung zur Kapazität einer einzelnen Speicherzelle im Hinblick auf die Leistungsfähigkeit des Speicherentwurfs besondere Bedeutung zu. Ob-10 wohl man vorzugsweise ein geringes Übertragungsverhältnis vorliegen haben möchte, ist es schwierig, die Kapazität der Bit-Abfühlleitung wirksam zu reduzieren. Bei Speicherentwürfen mit einer diffundierten bzw. dotierten Bitleitung beinhaltet die parasitäre Bitleitungskapazität einmål die 15 Kapazität des Halbleiterübergangs des die Bitleitung darstellenden Dotierungsgebietes sowie die (Koppel-)Kapazität zwischen der diffundierten Bitleitung und benachbarten isolierten leitfähigen Elektroden. Zur Verringerung dieser parasitären Koppelkapazität zwischen Bitleitung und ande-20 ren leitfähigen Schichten oder Schichtbereichen wurden bereits zahlreiche Maßnahmen vorgeschlagen. Eine Möglichkeit sieht vor, daß man über solchen diffundierten Bitleitungen relativ dicke (dotierte) Oxidschichten stehen läßt, um so durch Vergrößerung des Abstandes zwischen den Elektroden der 25 wirksamen Kapazität den Kapazitätswert zu verringern. Bei einer anderen Methode wird sorgfältig auf die jeweilige Ätzcharakteristik beim Ätzen der als Diffusionsquellschicht benutzten dotierten Oxidschicht geachtet, um die Überlappungskapazität an den Rändern der diffundierten Bitleitung möglichst gering zu halten, vgl. US-Patentschrift 3 975 220. Hin-30 sichtlich dieser Methode ist jedoch anzumerken, daß davon alle Diffusionen auf dem jeweiligen Halbleiterplättchen betroffen sind und die effektive Reduzierung der Überlappungskapazitäten nur einen kleinen Anteil der bezüglich 35 der Dotierungsbereiche wirksamen gesamten Kapazität aus-

macht. Andere Wege zur Verringerung solcher Kapazitäten sehen vor, die leitfähigen Bereiche über solchen Dotierungsgebieten thermisch zu oxidieren (vgl. z. B. IBM Technical Disclosure Bulletin, Juni 1974, Seite 18) oder eine elek-5 trisch nicht leitfähige intrinsische polykristalline Siliciumschicht aufzubringen, die lediglich in bezüglich der Koppelkapazität unkritischen Bereichen durch Hinzufügen von Dotierungsatomen leitfähig gemacht wird (vgl. IBM Technical Disclosure Bulletin, Juni 1974, Seite 17). Diese 10 Verfahren weisen den Nachteil auf, daß ein zusätzlicher Maskierungs- und Ausrichtungsschritt in einem ohnehin bezüglich der Ausrichtung kritischen Verfahren hinzukommt. Wünschenswert wäre demgegenüber eine Lösung, bei der keine besonderen Anforderungen an die Ausrichtung von Masken gestellt sind, 15 um das Vorkommen größerer Bereiche einer leitfähigen Schicht, insbesondere über Dotierungsgebieten, auszuschließen.

Als weitere Stand der Technik seien ferner die Veröffentlichungen im IBM Technical Disclosure Bulletin, Dezember 1976,

Seiten 2471/2472 sowie vom April 1978, Seiten 4842/4843 genannt. In beiden Veröffentlichungen wird eine unregelmäßige

Oberfläche mit einer Photolackschicht belegt und durch Anwendung einer Ionenimplantation behandelt. Dadurch werden

unterschiedliche Ätzraten der so behandelten unregelmäßigen

Schicht bewirkt, so daß stärker dotierte Bereiche der unregelmäßigen Schicht schneller abgetragen werden als die

übrigen Bereiche und letztlich eine Planarisierung erzielt

wird. Nachteilig bei diesen Verfahren ist, daß das Ätzende

solcher auf unterschiedliche Ätzraten angelegten Verfahren

prozeßmäßig schlecht zu kontrollieren ist.

Weiterhin gibt die US-Patentschrift 3 976 524 ein Verfahren zum Herstellen ebener Oberflächen bei integrierten Schaltungen an, bei dem die einzuebnende Oberfläche zunächst mit einer Photolackschicht überzogen wird, die zur Bildung

eines Photolackmusters in den vertieften Bereichen nach entsprechender Belichtung und Entwicklung in den erhabenen Bereichen von diesen vollständig und aus den vertieften Bereichen an am Rande belichteten und entwickelten Bereichen entfernt wird. Anschließend wird das unbelichtete Photolackmuster zum Zerfließen gebracht, so daß die vertieften Bereiche vollständig maskiert werden. Die erhabenen Bereiche können danach bis auf die Tiefe der vertieften Bereiche abgetragen werden. Schließlich ist noch die US-Patentschrift 4 070 501 von Interesse, die ein Verfahren zur selbstausrichtenden Herstellung von Mehrlagen-Leitungssystemen mit Querverbindungen betrifft. Dabei wird auf ein erstes Leitungsmuster tragendes Substrat eine Isolationsschicht aufgebracht, die der Oberfläche der Topologie des Leitungs-15 musters entspricht, also entsprechende Erhebungen aufweist. Auf die Isolationsschicht wird eine zweite Schicht aufgebracht, deren Dicke über den Leitungszügen geringer ist als neben diesen. Mittels einer Maske wird im Bereich der zu bildenden Verbindungslöcher über den Leitungszügen das Mate-20 rial der zweiten Schicht über den Erhebungen entfernt. Schließlich werden die Verbindungslöcher in der Isolationsschicht durch Ätzen gebildet, wobei die Maske und die zweite Schicht als Ätzmaske dienen.

- Die Erfindung, wie sie in den Patentansprüchen gekennzeichnet ist, löst die Aufgabe, ein verbessertes Herstellungsverfahren für Halbleiteranordnungen mit verringerten parasitären Kapazitäten anzugeben, die aus dem Zusammenwirken von Dotierungsgebieten in einem Substrat mit darüber angeordneten leitfähigen Schichten bzw. Schichtbereichen resultieren können. Insbesondere soll mit dem Verfahren die Herstellung von kapazitiven Ein-FET-Speicheranordnungen mit reduzierter Bitleitungskapazität möglich sein.

- 35 Zusammengefaßt sieht die Erfindung zur Herabsetzung der kapazitiven Kopplung zwischen mindestens einem in einem

Halbleitersubstrat angeordneten Dotierungsgebiet und einer isoliert auf dem Substrat vorgesehenen elektrisch leitfähigen Schicht, die über dem Dotierungsgebiet einen größeren Abstand von der Substratoberfläche als außerhalb des Do-5 tierungsgebiets und somit eine unebene Oberfläche mit mindestens einem erhabenen Bereich aufweist, vor, auf die Oberfläche der leitfähigen Schicht eine relativ dicke Maskierungsschicht, vorzugsweise aus Photolack, derart aufzubringen, daß die leitfähige Schicht mit unregelmäßiger Ober-10 fläche vollständig bedeckt wird und sich eine praktisch ebene Oberfläche bildet. Anschließend wird ein subtraktiver Prozeß, z. B. ein Ätz- oder Entwicklungsprozeß, ausgeführt, um einen gleichmäßigen Schichtanteil der Maskierungsschicht soweit abzutragen, daß bereichsweise die erhabenen Bereiche 15 der Oberfläche der leitfähigen Schicht freigelegt werden. Die leitfähige Schicht kann dann mittels eines weiteren Abtragungsverfahrens, z. B. durch Ätzen, in dem Gebiet über dem Dotierungsgebiet im Halbleitersubstrat entfernt werden. Damit lassen sich insbesondere über diffundierten Bitleitungen die zugehörigen Bereiche einer eventuell vorgesehenen 20 leitfähigen Schicht entfernen und die Bitleitungskapazitäten wirksam herabsetzen. Der zusätzlich erforderliche photolithographische Schritt ist dabei völlig unkritisch hinsichtlich der letztlich möglichen Packungsdichte, da keine 25 besonderen Anforderungen an eine Ausrichtung oder eine selektive Belichtung gestellt sind.

Die Erfindung wird im folgenden anhand eines Ausführungsbeispiels unter Zuhilfenahme der Zeichnungen näher erläutert.

Es zeigen:

30

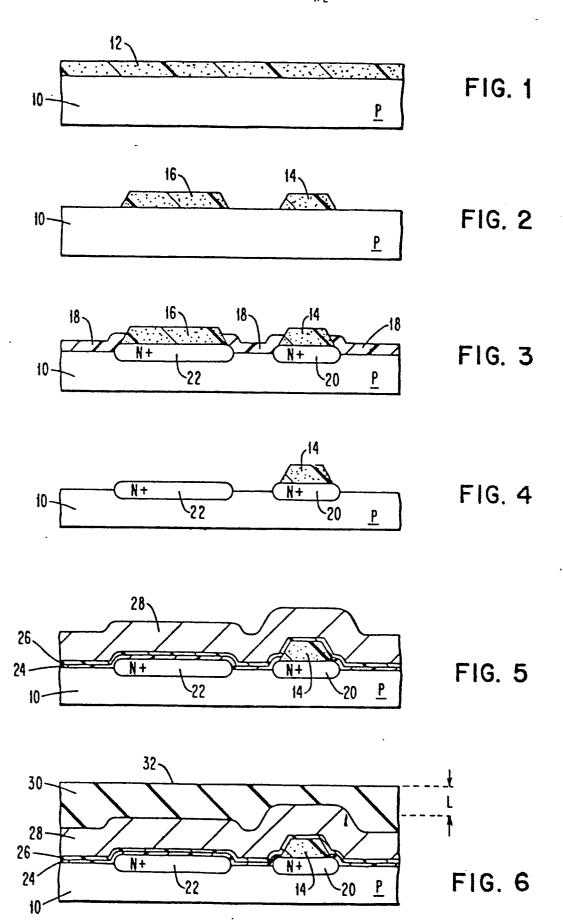

Fign. 1 Querschnitte durch eine Halbleiteranordnung bis 5 für ein dynamisches Speicherelement in verschiedenen anfänglichen Verfahrensstufen,

die als tpyisch für den Stand der Technik angesehen werden können und

۲.

Fign. 6 entsprechende Querschnittsdarstellungen zur

5 bis 11 Verdeutlichung nachfolgender Verfahrensschritte im Rahmen der vorliegenden Erfindung.

## Im einzelnen zeigen:

| 10 | Fig. 6             | das Aufbringen der ausgleichenden Photolack-<br>schicht auf die in Fig. 5 gezeigte Struktur;                                    |

|----|--------------------|---------------------------------------------------------------------------------------------------------------------------------|

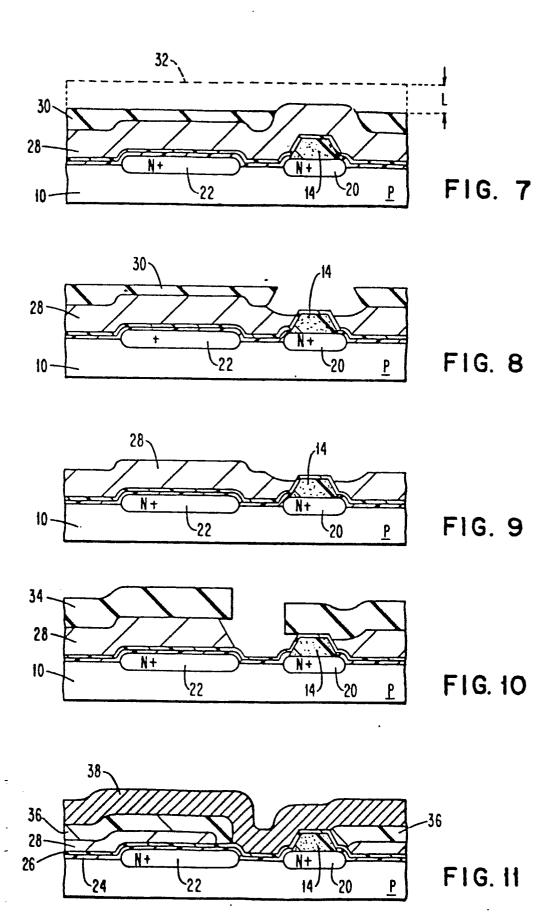

| 15 | Fig. 7             | die Struktur, in der der zu entfernende Teil<br>der leitfähigen Schicht freigelegt ist;                                         |

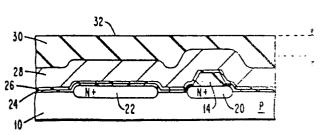

| 13 | Fign. 8 und 9      | die sich nach dem Ätzen der leitfähigen<br>Schicht bzw. nach der Entfernung der Photo-<br>lackschicht ergebenden Strukturen und |

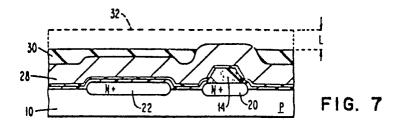

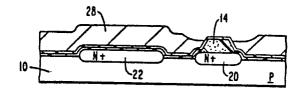

| 20 | Fign. 10<br>und 11 | die sich zum Abschluß des Verfahrens hin ergebenden Endstrukturen.                                                              |

Fig. 1 zeigt ein Halbleitersubstrat 10, das vorzugsweise aus P-leitendem Silicium mit einem spezifischen Widerstand von etwa 2 bis 12 Ω·cm besteht. Auf dem Substrat 10 ist eine mit 12 bezeichnete Schicht aus einem arsendotierten Oxid aufgebracht. Dazu wurde das Substrat 10 in eine zum chemischen Niederschlag durch Zersetzung aus der Gasphase (CVD) geeignete Atmosphäre aus gasförmigem Silan, Arsin, Sauerstoff und Stickstoff in geeigneten Mengen eingebracht, daß eine dotierte Oxidschicht 12 von etwa 300 bis 500 nm entsteht, die als Diffusionsquellschicht zur Bildung von PN-übergängen im Substrat dienen kann. Dieser CVD-Prozeß wird am besten bei etwa 500 °C in einer apparativen Einrichtung

35

ausgeführt, wie sie z. B. in der US-Patentschrift 3 805 736 beschrieben ist.

Ohne daß an dieser Stelle näher darauf einzugehen ist, soll 5 lediglich angemerkt werden, daß die verschiedensten Reinigungs-, Inspektions- und Prüfprozeduren vor bzw. nach den einzelnen, hier hauptsächlich beschriebenen Prozeßschritten üblich sind und demzufolge vorgesehen werden können. Solche Reinigungsschritte können dabei beispielsweise aus dem Ein-10 tauchen in Säurelösungen und dem Abwaschen unter deionisiertem Wasser mit anschließendem Reinigen in Gas- oder Luftströmen bestehen, wobei diese Schritte mehr oder weniger von der Produktempfindlichkeit bezüglich der verschiedensten Verunreinigungen abhängig sind. Zusätzlich können auch noch 15 verschiedene zusätzliche Verfahrensschritte in den Prozeßablauf eingefügt werden. Beispielsweise kann es bei der Herstellung der in diesem Ausführungsbeispiel beschriebenen dynamischen Speicherschaltungen durchaus wünschenswert sein, eine Getterung der im IBM Technical Disclosure Bulletin, 20 April 1977, Seite 4091, beschriebenen Art vorzusehen, um Leckstrompfade durch Störstellen im Halbleiterkristall zu reduzieren.

Nach dem Aufbringen der dotierten Oxidschicht 12 wird ein photolithographischer Maskierungsschritt durchgeführt, um alle die Bereiche auf der Oberfläche des Substrats 10 zu definieren, in denen diffundierte Übergänge erwünscht sind. Die dotierte Oxidschicht 12 wird dann in einem Naßätzverfahren, beispielsweise in mit Ammoniumfluorid gepufferter Flußsäure, (selektiv) entfernt. Nachdem die schützende Photolackmaskierung ebenfalls entfernt ist, bleiben die mit 14 und 16 bezeichneten Bereiche der dotierten Oxidschicht auf der Oberfläche des Substrats 10 in der in Fig. 2 gezeigten Weise übrig. Obwohl normalerweise eine sehr große Anzahl solcher dotierter Bereiche vorgesehen wird, sind zur Be-

schreibung der Erfindung in diesem Fall nur zwei derartige Bereiche dargestellt. Das mit 14 bezeichnete Gebiet ist in Wirklichkeit ein ausgedehnter Streifen, der sich senkrecht zur Darstellungsebene erstreckt und eine Bit-Abfühlleitung darstellt. Das mit 16 bezeichnete Gebiet ist dabei eines von vielen benachbart zum Gebiet 14 angeordneter Gebiete, die jeweils einen isolierten Kapazitätsbereich bilden.

Im Anschluß an die Abgrenzung der mit 14 und 16 bezeichneten 10 Gebiete wird das Substrat in eine Oxidations-/Eintreibatmosphäre eingebracht, wie sie einrichtungsmäßig beispielsweise in der US-Patentschrift 3 790 404 näher beschrieben ist. Dieser Verfahrensschritt wird vorzugsweise bei etwa 1100 °C in einer Sauerstoff und etwa 1 bis 3 % Wasserstoffchlorid 15 einhaltenden Atmosphäre durchgeführt, wobei sich eine thermische Siliciumdioxidschicht 18 auf der Substratoberfläche bildet, soweit sie nicht von dotierten Oxidschichtbereichen 14 und 16 bedeckt war. Bei diesem Verfahrensschritt erfolgt eine Ausdiffusion von Arsen aus den dotierten Oxidschicht-20 bereichen in das Substrat 10, so daß sich die N+ leitenden Dotierungsgebiete 20 und 22 bilden. Diese aus Fig. 3 ersichtlichen Dotierungsgebiete 20 und 22 repräsentieren dabei die diffundierte Bit-Abfühlleitungen sowie die Speicherknoten einer kapazitiven Ein-FET-Speicherzelle.

25

Im Anschluß an diesen geschilderten Eintreibschritt wird eine unkritische (nicht gezeigte) Grobmaskierungs aufgebracht, die so ausgelegt ist, daß die dotierten Oxidschichtbereiche selektiv über solchen Dotierungsgebieten entfernt werden können, auf die eine kapazitiv angekoppelte überdeckende Schicht aus leitfähigem Material aufgebracht werden muß. Nachdem die Grobmaskierung entfernt ist, wird ein kurzes Eintauchätzen durchgeführt, um jeglichen Rest der thermischen Oxidschicht 18 zu beseitigen, die vorher unter der Grobmaskierung und benachbart zu dem verbleibenden Oxidschichtbe-

reich 14 noch vorhanden war, vgl. insoweit auch die USPatentschrift 3 975 220. Fig. 4 verdeutlicht das Ergebnis

im Anschluß an diesen Verfahrensschritt. Um die effektive

Kapazität der Bit-Abfühlleitung gering zu halten, wird das

5 mit 14 bezeichnete Oxidgebiet über dem zugehörigen Dotierungsgebiet 20 für die (diffundierte) Bit-Abfühlleitung

aufrechterhalten.

Darauf wird, wie in Fig. 5 illustriert, in einer Sauerstoff/ 10 Wasserstoffchlorid enthaltenden Atmosphäre bei etwa 1000 <sup>O</sup>C eine dünne thermische Siliciumdioxidschicht 24 von etwa 30 nm Dicke aufgewachsen. Diese mit 24 bezeichnete Schicht bedeckt dabei die gesamte freigelegte Oberfläche mit Ausnahme der Stellen, an denen dotiertes Oxid vorhanden ist. 15 Dieser Verfahrensschritt kann ebenfalls in einer Einrichtung der in der US-Patentschrift 3 790 404 näher beschriebenen Art ausgeführt werden. Als nächstes wird eine etwa 20 nm dicke Siliciumnitridschicht 26 mittels einer Silan und Ammoniak enthaltenden Atmosphäre bei etwa 900 °C aufge-20 bracht. Daran anschließend erfolgt der Niederschlag einer etwa 300 nm dicken und mit Bor dotierten polykristallinen Siliciumschicht 28 aus einer Wasserstoff, Silan und Borhydrid enthaltenden Atmosphäre bei etwa 600 °C. Die beiden letztgenannten Verfahrensschritte können aufeinanderfolgend 25 in einer gemeinsamen Verfahrenskammer der in der US-Patentschrift 3 805 763 näher beschriebenen Art ausgeführt werden.

Wie aus Fig. 5 ersichtlich ist, erstreckt sich die Schicht

28 aus polykristallinem Silicium, die anschließend als sog.

Abschirmschicht abgegrenzt wird, über den dotierten Oxidbereich, der seinerseits die diffundierte Bitleitung 20

bedeckt, und ist kapazitiv damit gekoppelt. Bei den bekannten Verfahren in den US-Patentschriften 3 841 926 sowie

35 3 975 220 wurde der Aufbau einer Speicherzelle zu diesem

Verfahrenszeitpunkt damit abgeschlossen, daß man das polykristalline Silicium der Schicht 28 im Bereich zwischen den Dotierungsgebieten 20 und 22 entfernte, die Schicht 28 anschließend oxidierte und schließlich eine Aluminiummetallisierung als Wortleitung über der oxidierten Oberfläche aufbrachte. Die polykristalline Siliciumschicht 28 bleibt bereichsweise erhalten, nämlich über den Dotierungsgebieten 22 für die Speicherknoten, wo sie eine Elektrode des Speicherkondensators der betreffenden Speicherzelle darstellt, bzw. 10 als Abschirmschicht über dem Substrat um die Dotierungsgebiete 22 herum. Weiterhin verblieb die Schicht 28 aber auch über der gesamten Länge der die Bitabfühlleitungen darstellenden Dotierungsgebiete 20, was einen wesentlichen Betrag zur Erhöhung der insoweit wirksamen Koppelkapazität ausmachte. Dieser Effekt trat auf ungeachtet der effektiven Reduzierung der kapazitiven Auswirkungen, die dadurch erreicht wurde, daß man durch Beibehalten der dotierten Oxidbereiche 14 sowohl den Abstand zwischen den Kondensatorelektroden wie auch zwischen den Dotierungsgebieten 20 und der leitfähigen 20 Schicht 28 erhöht hatte.

Im Rahmen der vorliegenden Erfindung werden Bereiche der polykristallinen Siliciumschicht 28 in einem unkritischen Photolithographie- und Ätzverfahren in einer Weise entfernt, daß die effektive Bitleitungskapazität in Speicheranordnungen wesentlich herabgesetzt wird.

Nach dem Niederschlagen der polykristallinen Siliciumschicht 28 wird eine relativ dicke Photolack-Maskierungsschicht 30 auf das Substrat aufgetragen. Die Schicht 30 ist dabei so dick, daß sie alle Bereiche der mit 28 bezeichneten Schicht bedeckt und eine im wesentlichen ebene Oberfläche entsprechend Fig. 6 bildet. Als Photolack für die Schicht 30 kann ein üblicher Positivlack verwendet werden, der unter 35 dem Handelsnamen AZ1350J von der Firma Shipley Company,

Newton, Massachusetts vertrieben wird. AZ1350J ist ein lichtempfindliches Polymer, das aus einem m-Kresol-FormaldehydNovolak-Harz und einem Diazo-Keton-Sensibilisator, gelöst

in Äthylen-Glycol-Monoäthyläther-Azetat besteht. Der Photolack kann einen Zusatz zur Verbesserung der Haftungseigenschaften enthalten, wie z. B. in der US-Patentschrift

3 827 908 beschrieben ist. Das Aufbringen des Photolacks

kann in einer der konventionellen Techniken erfolgen, die

soviel Material aufzutragen gestattet, daß sich eine im

wesentliche ebene Oberfläche einstellen kann. Anschließend

wird der Photolack mittels einer Wärmebehandlung bei 95 °C

über eine zum Aushärten ausreichende Zeit behandelt.

Wie in Fig. 7 gezeigt ist, wird als nächstes die Photolackschicht 30 gleichmäßig bis zu einer einheitlichen Tiefe L 15 von der ursprünglichen Oberfläche 32 entfernt, um nur die Bereiche der polykristallinen Siliciumschicht 28 freizulegen, die über den beibehaltenen dotierten Oxidgebieten 14 liegen. Die dazu angewendeten Verfahren sind unkritisch, 20 solange die Abtragungsgeschwindigkeit eine Beendigung des Verfahrensschrittes nach Erreichen der Tiefe L gestattet. Auch wird kein Maskierungsschritt benötigt, da vorzugsweise die Photolackschicht von der gesamten Oberfläche einheitlich abgetragen wird, obwohl natürlich auch Grobmaskierungen ein-25 gesetzt werden können, um beispielsweise einige erhabene Bereiche der Schicht 28 an gewünschten Stellen stehenzulassen. Als geeignetes Abtragungsverfahren kommen beispielsweise die folgenden Möglichkeiten in Betracht: durchgehende Belichtung der Photolackschicht 30 bis zu einer Tiefe L, 30 so daß ein Standard-Entwickler zur Entfernung der belichteten Schichtbereiche angewendet werden kann. Durchgehende einheitliche Belichtung des Photolacks durch ein neutrales Dichtefilter, um die Entwicklungsrate ausreichend zur Steuerung der Entwicklungstiefe L herabzusetzen, vgl. z. B. US-Patentschrift 3 649 393. Gleichmäßiges Abtragen der nicht belichteten Photolackschicht 28 mittels eines aus einem Lösungsmittel bestehenden Entwicklers, z. B. einer Kaliumpermanganat enthaltenden Phosphorsäure, vgl. US-Patentschrift 4 089 766. Schließlich kommt noch ein Abtrag mittels reaktiven Ionenätzens bzw. mittels eines Sputterverfahrens in Betracht. Da eine gleichmäßige Photolackschicht abgetragen wird, ist dieser Verfahrensschritt selbstjustierend und legt selektiv lediglich die Bereiche des beschichteten Substrats frei, die in der in Fig. 7 gezeigten Weise durch die verbleibende Photolack-Maskierungsschicht reichen.

Nach dem Entfernen eines Teils der Photolackschicht 30 wird das dann freiliegende polykristalline Silicium selektiv mittels eines geeigneten Ätzmittels entfernt, z. B. mittels einer Lösung aus Salpetersäure, Wasser und gepufferter Flußsäure in einem Volumenverhältnis von 7:4:1, wobei die gepufferte Flußsäure 5 Volumenteile 40 %igen Ammoniumfluorids auf einen Volumenteil 48 %iger Flußsäure aufweist. Durch diesen Verfahrensschritt wird in wirksamer Weise im wesentlichen alles Material der polykristallinen Siliciumschicht 28 über den Dotierungsgebieten 20 für die Bit-Abfühlleitungen abgetragen. Die mögliche parasitäre Koppelkapazität zwischen den relativ langgestreckten Bit-Abfühlleitungen und den benachbart dazu liegenden Bereichen der leitfähigen Schicht 28 wird dadurch erheblich verringert.

Im Anschluß an das selbstausrichtende Ätzen der Schicht 28 werden die verbleibenden Bereiche der Photolackschicht 30 mittels konventioneller Ablöseverfahren entfernt, z. B. mit 30 N-Methylpyrolidon. Aus Fig. 9 ist ersichtlich, daß im Anschluß an den geschilderten Verfahrensschritt eine Anordnung verbleibt, die hinsichtlich des Verfahrenszustandes mit Fig. 5 vergleichbar ist. Demgegenüber besteht jedoch der Unterschied, daß die leitfähige Schicht 28 aus polykristallinem Silicium von selektiven Bereichen, insbesondere über

den Dotierungsgebieten 20 für die Bit-Abfühlleitungen mit den darüber belassenen dotierten Oxidgebieten 14, entfernt worden ist.

5 Für den weiteren Verfahrensablauf kann entsprechend der US-Patentschrift 3 841 926 in der folgenden Weise vorgegangen werden. Nach dem Ablösen der selbstausrichtenden Photolackschicht 30 wird ein weitere Photolithographie- und Ätzschritt angewandt, um die Bereiche der polykristallinen Siliciumschicht 28 zu ätzen, an denen Gate-Bereiche für die 10 jeweiligen Feldeffekttransistoren erforderlich sind, vgl. Fig. 10. Obwohl man aufgrund der Darstellung in den Figuren annehmen könnte, daß durch diesen Verfahrensschritt die zuvor geätzten Bereiche der Schicht 28 ausgedehnt würden, ist dieser Ätzschritt jedoch auf relativ kleine Gate-Bereiche beschränkt, wodurch jeder der zahlreichen isolierten Bereiche 22 der Speicherknoten mit dem langgestreckten Dotierungsgebiet 20 der zugehörigen Bitleitung gekoppelt wird. Eine geringe Fehljustierung der zum Ätzen der Gatebereiche 20 erforderlichen Photolackmaske 34 wird im wesentlichen nicht die Kapazität der Bit-Abfühlleitungen beeinflussen, während eine Fehljustierung bei der zur Entfernung des polykristallinem Siliciums 28 benutzten Maskierung für den dotierten Oxidbereichen 14 unannehmbar große Kapazitätsänderungen der 25 Bitleitungen von Chip zu Chip zur Folge haben würde, wobei die so hergestellten Speicheranordnungen entsprechend unterschiedliche Betriebseigenschaften zeigen würden.

Im Anschluß an die Abgrenzung der Gate-Bereiche werden die verbleibenden Bereiche der polykristallinen Siliciumschicht 28 in einer Sauerstoff/Wasserstoffchlorid-Atmosphäre bei etwa 1000 OC thermisch oxidiert, wobei die mit 36 bezeichnete Siliciumdioxidschicht entsteht. Durch diesen Oxidationsschritt wird das Ausmaß der kapazitiven Kopplung zwischen der Schicht 28 aus polykristallinem Silicium und dem Do-

tierungsgebiet 20 für die Bit-Abfühlleitung, wie aus Fig. 11 ersichtlich, weiter vermindert, da die Oxidation sowohl die Dicke als auch die seitliche Abmessung der Schicht 28 reduziert.

5

Zur Bildung der Gate-Elektroden und elektrisch leitfähigen Wortleitungen wird abschließend eine leitfähige Schicht 38, z. B. aus Kupfer-Aluminium im Rahmen eines sog. Lift-off-Prozesses aufgedampft. Obwohl im Rahmen der Herstellung solcher Speicheranordnungen noch zusätzliche Passivierungsund Leitschichten vorzusehen sein werden, sind nach dem Aufbringen der Aluminiumschicht 38 die eigentlichen Speicherzellen, die aus den Dotierungsgebieten 20 für die Bit-Abfühlleitungen, den Gate-Elektroden 38, und den Speicherknoten 22 so-15 wie Kondensatorelektroden (Bereiche der Schicht 28 über den Dotierungsgebieten 22) bestehen, voll funktionsfähig und testbar. Die elektrische Isolierung benachbarter Speicherknoten 22 ist möglich, indem man ein Referenzpotential an die polykristalline Siliciumschicht 28 anlegt, so daß die Ober-20 fläche des Substrats 10 benachbart zu den Gebieten 20 und 22, jedoch nicht unter den Elektroden 38 zwischen diesen Gebieten, dauernd in Sperrichtung vorgespannt ist. Dies kann erreicht werden, indem man das Substrat 10 und die Schicht 28 aus polykristallinem Silicium an eine negative Spannung an-25 legt.

Obwohl die Erfindung im Zusammenhang mit einem bevorzugten Ausführungsbeispiel erläutert wurde, ist festzuhalten, daß solche Oberflächenunregelmäßigkeiten, wie die erhabenen 30 Bereiche der Schicht 28 im vorliegenden Ausführungsbeispiel, durch die oben anhand der Fign. 6 bis 9 verdeutlichten Verfahrensschritte planarisiert werden können. Die hauptsächlichen Verfahrensschritte sind, daß die derart unebene Oberfläche mit einer Maskierungsschicht, z. B. aus Photolack, bedeckt wird, daß von der neuentstandenen ebenen Oberfläche ein gleichmäßiger Oberflächenanteil der Maskierungsschicht

so abgetragen wird, daß die Oberflächen der erhöhten Bereiche darunter freigelegt werden, und anschließend zunächst

diese freigelegten Bereiche sowie daraufhin die verbleibenden

Maskierungsschichtteile entfernt werden.

BU 978 002

## PATENTANSPRÜCHE

- Verfahren zur Herstellung von Halbleiteranordnungen 1. mit herabgesetzter kapazitiver Kopplung zwischen mindes-5 tens einem in einem Halbleitersubstrat (10) angeordneten Dotierungsgebiet (20) und einer isoliert auf dem Substrat vorgesehenen elektrisch leitfähigen Schicht (28), die über dem Dotierungsgebiet (20) einen größeren Abstand von der Substratoberfläche als außerhalb des Dotierungsgebiets und somit eine unebene Oberfläche 10 mit mindestens einem erhabenen Bereich aufweist (Fig. 5), dadurch gekennzeichnet, daß auf die Oberfläche der leitfähigen Schicht (28) eine diese vollständig bedeckende Maskierungsschicht 15 (30) aufgebracht wird, die ihrerseits eine praktisch ebene Oberfläche (32) bildet (Fig. 6), daß von der Maskierungsschicht (30) ein einheitlicher Schichtdickenanteil (L) abgetragen wird, bis die Oberfläche des mindestens einen erhabenen Bereichs der leitfähigen 20 Schicht (28) über dem (den) Dotierungsgebiet(en) (20) freigelegt ist (Fig. 7) und daß anschließend die leitfähige Schicht (28) in dem (den) derart freigelegten Bereich(en) abgetragen wird (Fig. 8).

- 25 2. Verfahren nach Anspruch 1, gekennzeichnet durch eine Maskierungsschicht (30) aus einem organischen Polymer, vorzugsweise einem strahlungsempfindlichen Polymer.

- Verfahren nach den Ansprüchen 1 oder 2,

dadurch gekennzeichnet,

daß zum Abtragen des einheitlichen Schichtdickenanteils

(L) der Maskierungsschicht (30) eine Tiefenbelichtung

bis zu einer Tiefe vorgenommen wird, die größer ist

als der Abstand zwischen der Oberfläche (32) der Mas kierungsschicht (28) und dem (den) obersten erhabenen

Oberflächenbereich(en) der leitfähigen Schicht (28) und daß anschließend zur bereichsweisen Freilegung der leitfähigen Schicht (28) die belichteten Schichtanteile der Maskierungsschicht (30) durch Anwendung eines chemischen Entwicklungsverfahrens entfernt werden.

- Verfahren nach den Ansprüchen 1 oder 2,

dadurch gekennzeichnet,

daß zum Abtragen des einheitlichen Schichtdickenanteils

(L) der Maskierungsschicht (30) ein Ätzverfahren, vorzugsweise in Form eines reaktiven Ionenätzverfahrens,

durchgeführt wird.

- 5. Verfahren nach mindestens einem der vorgehenden Ansprüche, dadurch gekennzeichnet,

daß die leitfähige Schicht (28) aus polykristallinem

Silicium besteht, unter dem sich im Bereich wenigstens

eines im Substrat (10) angeordneten Dotierungsgebiets

(20) ein Dielektrikum enthaltend ein dotiertes Oxidgebiet (14) befindet, aus dem als Quellschicht das

Dotierungsgebiet (20) durch Ausdiffusion hergestellt

wurde.

- 6. Verfahren nach Anspruch 5, dadurch gekennzeichnet,

daß im Substrat weitere Dotierungsgebiete (22) vorgesehen sind, die von der leitfähigen Schicht (28)

durch ein, verglichen mit der Dicke eines dotierten

Oxidgebiets (14), relativ dünnes Dielektrikum (24, 26)

getrennt sind.

30

35

5

7. Verfahren nach mindestens einem der vorhergehenden Ansprüche, dadurch gekennzeichnet,

daß damit Halbleiteranordnungen für Speicherbauelemente,

insbesondere für kapazitive Ein-FET-Speicherzellen,

hergestellt werden, bei denen jeweils ein im Substrat

(10) angeordnetes Dotierungsgebiet (20) die mit möglichst geringer kapazitiver Kopplung zur leitfähigen

Schicht (28) auszulegende Bit-Abfühlleitung und ein

weiteres dazu benachbartes Dotierungsgebiet (22) den

jeweiligen kapazitiven Speicherknotenbereich mit demgegenüber hoher Kopplungskapazität darstellt.

5

1: