(1) Numéro de publication:

**0 050 350**

12

## **DEMANDE DE BREVET EUROPEEN**

21 Numéro de dépôt: 81108503.4

(51) Int. Cl.3: G 04 G 13/02

2 Date de dépôt: 19.10.81

30 Priorité: 21.10.80 FR 8022889

71 Demandeur: SOCIETE SUISSE POUR L'INDUSTRIE HORLOGERE MANAGEMENT SERVICES S.A., Rue Stämpfli 96, CH-2500 Bienne (CH)

43 Date de publication de la demande: 28.04.82 Bulletin 82/17

Inventeur: Piguet, Christian, Vieux Châtel 21, CH-2000 Neuchâtel (CH) Inventeur: Perotto, Jean-Félix, Chemin Marnière 30, CH-2068 Hauterive (CH)

Etats contractants désignés: CH DE GB LI

Mandataire: Coutts, William Robert, SSIH Management Services S.A. Patent Service Rue Stämpfli 96, CH-2500 Blenne (CH)

64 Procédé pour comparer un état horaire et le contenu d'un registre dans une pièce d'horlogerie à rappel, circuit pour sa mise en oeuvre et utilisation de ce circuit.

⑤ Un registre programmable (2) déclenche un signal lorsque le contenu d'au moins un compteur (1) coïncide avec celui d'une partie du registre (2). Dans l'autre partie du registre (2) est programmé le code d'un état (—) que les compteurs correspondants (1) n'atteignent jamais en fonctionnement normal et la comparaison (3) entre l'état de ces compteurs (1) et celui de l'autre partie du registre (2) est validée quel que soit cet état.

L'invention s'applique particulièrement aux montres à rappel par son circuit comparateur (3) qui peut représenter une fonction d'unité arithmétique et logique de microprocesseur.

Procédé pour comparer un état horaire et le contenu d'un registre dans une pièce d'horlogerie à rappel, circuit pour sa mise en oeuvre et utilisation de ce circuit

L'invention est relative à un procédé pour la comparaison de l'état horaire d'une pièce d'horlogerie électronique pour déclencher un signal d'avertissement ou rappel à différentes périodicités programmables dans un registre par l'utilisateur, ce déclenchement intervenant lorsque l'état horaire de la pièce d'horlogerie arrive au moins partiellement en coïncidence avec le contenu du registre. Elle concerne également un circuit logique pour la mise en oeuvre de ce procédé et une utilisation de ce circuit dans un microprocesseur horloger.

Un circuit logique pour une montre-réveil est décrit dans le bre10 vet US 3,759,029. Dans ce cas, le registre doit nécessairement toujours contenir l'indication des heures, minutes et secondes et la périodicité du rappel est donc toujours nécessairement la même, c'est-àdire quotidienne. Des circuits du même type pour rappel à périodicité

fixe et pouvant comparer respectivement depuis les dizaines d'heures

15 jusqu'aux secondes et depuis les heures jusqu'aux dizaines de minutes

font également l'objet des brevets US 3,745,761 et CH 534 386.

Une périodicité de rappel hebdomadaire, mais hebdomadaire seulement, peut aussi être obtenue au moyen du circuit décrit dans la demande de brevet DE-A 26 43 993 qui compare depuis les jours jusqu'aux

20 minutes. Un comparateur pour les heures et les minutes dans une montre

comportant dix rappels est également exposé dans la demande de brevet

DE-A 21 17 756.

Dans aucun de ces cas l'utilisateur n'est maître de la périodicité, fixée une fois pour toute, du rappel qu'il programme. Aussi est-il apparu comme extrêmement utile que l'utilisateur puisse choisir luimême, selon ses besoins propres, la périodicité des rappels qu'il attend de sa montre - ou autre pièce d'horlogerie -. C'est cet objectif que l'invention vise à atteindre en proposant un procédé pour la comparaison et un circuit logique pour sa mise en oeuvre permettant l'activation d'un signal d'avertissement lorsque le contenu d'au moins un compteur horaire de la pièce d'horlogerie arrive en coïncidence avec le contenu de la partie correspondante du registre dans lequel a été programmée l'indication de rappel, l'autre partie du registre conte-

nant, au lieu d'informations horaires, un état que les compteurs horaires correspondants n'atteignent jamais en fonctionnement normal, par exemple le code d'un symbole non numérique tel que la comparaison entre l'état des compteurs horaires correspondants, quel que soit cet état, et le contenu de cette autre partie du registre soit toujours validée. Une telle disposition permet à l'utilisateur de programmer toute périodicité désirée à son rappel, par exemple quotidienne, hebdomadaire, mensuelle, annuelle.

L'invention va maintenant être exposée en détail à la lumière 10 d'un exemple. Pour l'intelligence de la description, on se référera aux dessins parmi lesquels:

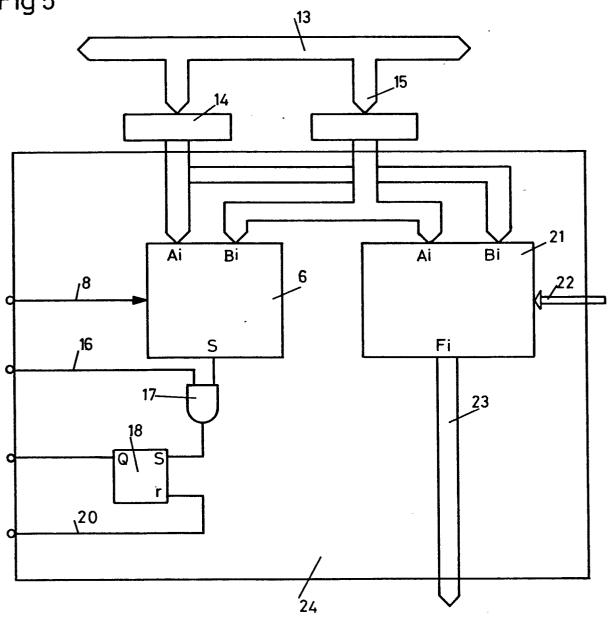

La figure l'est une représentation schématique d'un circuit comparateur selon l'invention.

La figure 2 illustre un code qui peut être utilisé pour la pro-5 grammation du registre du circuit de la figure 1.

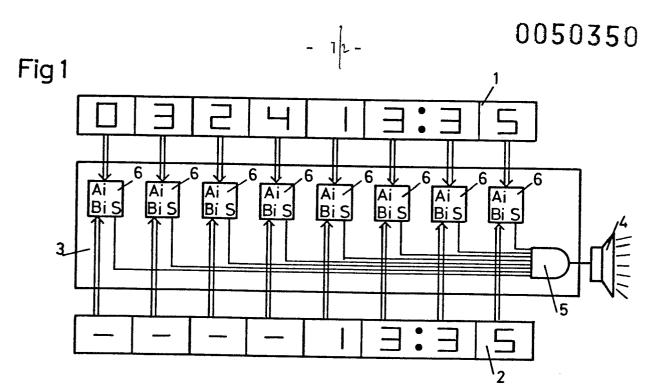

La figure 3 représente une cellule ou comparateur élémentaire du même circuit.

La figure 4 montre une disposition permettant, dans le cadre de l'invention, d'inhiber le rappel sonore au profit d'un rappel visuel lorsque les minutes ne sont pas spécifiées.

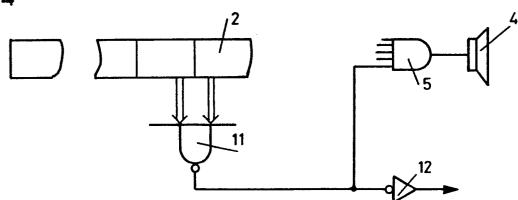

La figure 5 illustre une utilisation possible du comparateur élémentaire de la figure 3 dans une unité arithmétique et logique d'un microprocesseur horloger.

A la figure 1, l'état horaire d'une pièce d'horlogerie apparaît

25 dans des compteurs horaires 1 contenant l'information relative respectivement à la minute ("35"), à l'heure ("13"), au quantième ("24") et au mois ("03"). Un registre programmable 2 est constitué par des cellules correspondant chacune à une information élémentaire présente dans les compteurs 1. Les compteurs 1 et le registre 2 sont connectés à l'affichage permettant ainsi la visualisation de leurs contenus respectifs. Dans la partie de ce registre 2 correspondant à l'heure et à la minute ont, dans l'exemple représenté, été respectivement programmés treize heures ("13") et trente-cinq minutes ("35"). Dans chaque cellule de l'autre partie du registre 2 a été programmé un symbole non numérique correspondant, dans le cas présent, à un tiret ("-"). On aurait tout aussi bien pu programmer une autre information, l'essentiel étant que celle-ci représente un état que ne peuvent atteindre les

compteurs horaires correspondants 1 en fonctionnement normal de la pièce d'horlogerie. Un circuit logique comparateur 3 est constitué de cellules ou comparateurs élémentaires 6 en nombre correspondant à chacune des informations élémentaires précédentes, huit dans le cas pré-5 sent et d'une porte logique ET 5. Chaque comparateur élémentaire 6 reçoit en entrée les informations Ai et Bi relatives respectivement à chaque information élémentaire contenue dans les compteurs horaires l et dans le registre 2. Dans le cas où il y a identité entre l'information Ai et l'information Bi correspondante, ou bien où l'information 10 Bi représente le symbole tiret "-", le comparateur 6 concerné va délivrer à sa sortie un signal S au niveau logique "l" qui va parvenir à la porte ET 5. Dans l'exemple illustré, il en est ainsi en permanence pour tous les étages autres que ceux relatifs à l'heure et à la minute, et, lorsque les compteurs 1 des heures et des minutes correspon-15 dront à treize heures et trente-cinq minutes, les quatre comparateurs élémentaires 6 concernés fourniront également chacun un signal S au 🔝 niveau logique "l" et la porte ET 5 laissera passer un signal allant activer un avertisseur 4, par exemple un haut-parleur. Une minute plus tard, à treize heures et trente-six minutes, l'activation cessera et 20 la porte ET 5 ne transmettra plus aucun signal jusqu'à ce que l'état horaire de la pièce d'horlogerie aux compteurs 1 soit "03 25 13:35" et, à ce moment, l'avertisseur 4 sera à nouveau activé. On obtient donc un rappel quotidien, chaque fois qu'il est treize heures trente-cinq.

Si l'utilisateur programme dans le registre 2 "-- 24 13:35", le mois n'étant pas spécifié et représenté par les symboles "--", le rappel aura lieu mensuellement au quantième vingt-quatre et à treize heures trente-cinq. De même, si toutes les positions du registre 2 sont occupées par un symbole numérique correspondant à un état possible des compteurs 1, donc sans aucun symbole tiret "-" ou autre état impossible des compteurs 1, on aura une périodicidé annuelle pour le rappel : ainsi la programmation "05 21 13:35" provoquera un avertissement tous les vingt et un mai à treize heures trente-cinq.

On pourrait de même programmer une périodicité hebdomadaire en prévoyant une lecture pour la comparaison du compteur des dates et du compteur des jours. Ainsi la programmation "-- SA 10:30" donnerait un rappel tous les samedis à dix heures trente. Bien que cet exemple ne soit pas illustré, il est clair qu'il découle, pour l'homme de métier,

de façon évidente de ce qui vient d'être exposé.

La figure 3 représente une exécution particulière d'un comparateur élémentaire 6 pour des compteurs horaires 1 dont le code comprend quatre bits, tel le code BCD présenté à la figure 2, et où un état im-5 possible des compteurs l'est représenté par le symbole non numérique tiret "-" est par exemple codé par "llll". Les bits  $A_1$ ,  $A_2$ ,  $A_3$ ,  $A_4$  représentent l'information Ai venant d'un des compteurs 1, et les bits B<sub>1</sub>, B<sub>2</sub>, B<sub>3</sub>, B<sub>4</sub> l'information Bi en provenance de la partie correspondante du registre 2 où est programmée l'indication de rappel. Le cir-10 cuit 7 est un comparateur à quatre bits tel par exemple que le circuit 7485 bien connu en technologie TTL (Transistor-Transistor-Logic). Si Ai = Bi quel que soit i égal à 1, 2, 3 ou 4, la sortie du circuit 7 est au niveau logique "1" et ce signal va passer la porte OU 10 pour donner à la sortie S du comparateur élémentaire 6 un niveau logique "l" également, et ce quel que soit le niveau à la sortie de la porte ET 9. Cette porte ET 9 reçoit les bits B1, B2, B3, B4 et une entrée supplémentaire 8. Si l'entrée 8 est au niveau "O", la sortie de la porte ET 9 sera toujours au même niveau "O", et le comparateur élémentaire 6 fonctionne alors comme un simple comparateur à quatre bits, la 20 porte OU 10 ne pouvant envoyer un signal "1" à la porte ET 5 que quand Ai = Bi. Si, par contre, l'entrée 8 est au niveau "l", le comparateur élémentaire 6 sera un comparateur à quatre bits où la comparaison sera validée dès qu'on aura  $B_1 = B_2 = B_3 = B_4 = 1$ , c'est-à-dire le symbole tiret "-" dans la cellule correspondante du registre 2, et ce quelles que soient les valeurs A<sub>1</sub>, A<sub>2</sub>, A<sub>3</sub>, A<sub>4</sub> fournies par le compteur 1 correspondant. En effet, la sortie ET 9 sera toujours au niveau logique "1" et par conséquent celle de la porte OU 10 également.

La figure 4 illustre le cas particulier où, dans le registre 2, ce sont les minutes qui ne sont pas spécifiées. Les cellules concer-30 nées comportent donc, par exemple, le code llll correspondant au symbole tiret "-".

Dans cette hypothèse, il est utile que le rappel prévu ne soit pas sonore, car de durée trop longue, et de lui substituer un avertissement visuel. Aussi une porte NON-ET ll est-elle prévue à la sortie du registre 2, celle-ci produit alors le niveau logique "O" qui va inhiber l'avertisseur sonore 4 en bloquant la porte ET 5, mais par ailleurs activer un indicateur visuel (non représenté) par l'intermédiai-

re d'un inverseur 12. Cette disposition peut être utilisée pour un rappel quotidien en programmant uniquement l'information de l'heure, le reste du registre 2 comportant partout ailleurs le code du symbole tiret "-" ou autre état impossible des compteurs 1. De même, en ne spécifiant que la date, c'est-à-dire le quantième et le mois, on pour-ra programmer des anniversaires, par exemple "07 21 --:--", le 21 juillet de chaque année.

Une variante d'utilisation du circuit comparateur élémentaire 6 est illustrée à la figure 5. Il est appliqué comme fonction spéciale 10 d'une unité arithmétique et logique (ALU) 24 dans un microprocesseur horloger. Un bus 13 permet de charger deux registres 14, 15 avec le contenu de deux compteurs ou registres horaires à comparer. Si les deux contenus sont identiques ou si le code contenu dans le registre de rappel est celui du symbole tiret "-", le signal de sortie S du 15 comparateur 6 est au niveau logique "l". Ce signal sert d'entrée à une porte ET 17 et un signal 16 en seconde entrée de cette porte ET 17 permet, par une instruction du microprocesseur, de sélectionner cette opération de comparaison. Dans ce cas, la sortie de la porte ET 17 au niveau "l" met au même niveau "l" l'indicateur ou bascule-drapeau 18 20 lorsque la comparaison est effective. Ce signal de sortie Q de l'indicateur 18 est testé par le microprocesseur pour déterminer si la comparaison a été effective et un signal 20 permet de remettre à zéro l'indicateur 18. Par ailleurs, un signal 8 permet, par une instruction du microprocesseur, de sélectionner au choix, comme dans le cas précé-25 dent, une comparaison simple et le signal 8 est niveau "0", ou une comparaison validée auquel cas le signal 8 est au niveau "1".

L'unité arithmétique et logique 24 peut comporter en outre un circuit 21 tel que le type TTL-74 181 bien connu recevant en entrée les sorties des deux registres 14 et 15 et dont la sortie est le bus 23, des variables de commande 22 permettant de sélectionner l'opération à effectuer.

Pour la programmation du registre programmable 2 de la figure l ou l'équivalent de la figure 5, on peut faire appel à un système tel que montré dans le brevet CH 610 712 dans lequel on utilise deux com-35 mutateurs dont un fonctionne comme sélecteur et l'autre comme correcteur. Le sélecteur est actionné afin d'envoyer un signal à un compteur électronique dont le contenu, qui dépend du nombre de fois que le commutateur de sélection a été actionné, est envoyé à un aiguillage de correction. Le commutateur de correction peut à tour de rôle être actionné afin d'envoyer des signaux à la cellule sélectionnée du registre 2 pour changer son contenu. Pour chaque impulsion, le contenu peut être augmenté par une unité et il est bien entendu que le comptage prévu permettra l'introduction du symbole tiret "-" ou autre état impossible des compteurs l. Il est également possible que le correcteur puisse transmettre un train d'impulsions au lieu d'une seule impulsion lors de son actionnement.

## Revendications

- Procédé pour la comparaison de l'état horaire d'une pièce d'horlogerie électronique et du contenu d'un registre programmable pour déclencher un signal d'avertissement lorsque le contenu d'au moins un compteur horaire de la pièce d'horlogerie arrive en coïnci- dence avec le contenu de la partie correspondante du registre, caractérisé par le fait qu'il consiste à programmer dans l'autre partie du registre (2), au lieu d'une information horaire, le code d'un état que les compteurs horaires correspondants (1) n'atteignent jamais en fonctionnement normal (-) et à valider la comparaison entre l'état des

compteurs horaires (1) correspondants, quel que soit cet état, et le contenu de cette autre partie du registre (2), cet étant ne pouvant donc inhiber l'avertissement (4).

- Circuit de déclenchement d'un avertisseur (4) dans une pièce d'horlogerie électronique lorsque certains compteurs (1), au moins,

d'une chaîne de division atteignent un état correspondant à un état de consigne, caractérisé par le fait qu'il comporte un registre programmable (2) dont les différentes cellules, qui correspondent chacune à un compteur (1) de ladite chaîne, peuvent être placées individuellement soit dans un état de consigne soit dans un état de validation,

une pluralité de circuits comparateurs (6) associés respectivement auxdites cellules (2) pour produire chacun un signal d'autorisation lorsqu'il y a coïncidence entre l'état de la cellule associée (2) et l'état du compteur (1) correspondant ou lorsque la cellule associée (2) se trouve dans l'état de validation, et un circuit porte (5) déclenchant l'avertisseur (4) lorsque tous les comparateurs (6) émettent simultanément un signal d'autorisation.

- 3. Circuit selon la revendication 2, caractérisé par le fait que ledit état de validation est un état que le compteur (1) n'atteint jamais en fonctionnement normal.

- 4. Circuit selon la revendication 2 ou la revendication 3, caractérisé par le fait que chaque comparateur élémentaire (6) comporte un circuit conventionnel (7) comparateur à quatre bits, recevant en entrée les quatre bits (Ai, Bi) respectivement en provenance du compteur horaire et de la cellule du registre correspondante (2), associé à une porte OU (10) dont la sortie (S) sert d'entrée à la porte ET (5),

et à laquelle porte OU (10) il envoie un signal d'activation lorsqu'il y a identité (A = B) entre les deux ensembles de quatre bits, et associé également à une porte ET (9) recevant en entrée les quatre bits (Bi) en provenance de la cellule du registre (2) ainsi qu'un signal (8) permettant l'activation de cette porte ET (9) lorsquel les quatre bits (Bi) représentent le code de l'état impossible (-), ladite porte ET (9) délivrant alors son signal à la porte OU (10).

- 5. Circuit selon l'une quelconque des revendications 2 à 4, caractérisé par le fait qu'aux cellules du registre (2) correspondant au moins, soit à la minute, soit à l'heure, soit au jour ou soit au mois, est associée une porte NON-ET (11) dont la sortie sert d'entrée à la porte ET (5) et à la commande par l'intermédiaire d'un inverseur (12) d'un second avertisseur de nature différente du premier (4), le code de l'état impossible (-) du compteur correspondant (1), s'il est contenu dans lesdites cellules (2) inhibant ainsi le premier avertisseur (4) au profit du second.

- 6. Circuit selon la revendication 5, caractérisé par le fait que le premier avertisseur (4) est sonore, et le second visuel.

- 7. Utilisation d'un circuit selon l'une quelconque des revendica-20 tions 2 à 6, caractérisée par le fait que ce circuit représente une fonction spéciale d'une unité arithmétique et logique (24) dans un microprocesseur pour pièce d'horlogerie.

Fig 2

| Code BCD | Symbole   |

|----------|-----------|

| 0000     | 0         |

| 0001     | 1         |

| 0010     | 2         |

| 0011     | 3         |

| 0100     | 4         |

| 0101     | 5         |

| 01 10    | 6         |

| 0111     | 7         |

| 1000     | 8         |

| 1 001    | 9         |

| 1 1 1 1  | 一 (tiret) |

Fig 4

Fig 5