(11) Publication number:

**0 071 752** A1

(12)

### **EUROPEAN PATENT APPLICATION**

21 Application number: 82105866.6

(f) Int. Cl.3: G 08 B 25/00

22 Date of filing: 01.07.82

30 Priority: 02.07.81 JP 102305/81

Applicant: Nohmi Bosai Kogyo Co., Ltd., No. 7 - 3 Kudan Minami 4-chome Chiyoda-ku, Tokyo 103 (JP)

- (3) Date of publication of application: 16.02.83 Builetin 83/7

- Inventor: Itoh, Hideo c/o Nohmi Bosai Kogyo Co., Ltd., 7-3, Kudan-Minami, 4-chome Chiyoda-ku (JP)

- Designated Contracting States: BE CH DE FR GB IT LI

SE

- Representative: Tiemann, Ulrich, Dr.-Ing., c/o Cerberus AG Patentbüro Alte Landstrasse 411, CH-8708 M\u00e4nnedorf (CH)

- (54) Fire alarm system.

- This invention relates to a fire alarm system in which fire detectors, when operated, send address signals for identification of the alarming detectors and their output changes to a control panel besides fire signals as given by conventional fire detectors, and the control panel indicates the fire zones, the alarming detectors and their output changes.

#### Fire alarm system

The present invention relates to a fire alarm system which is capable of detecting, through a receiver, the operation and the change in output of individual fire detectors among a plurality of fire sensors that are arrayed in parallel along the same lines in the same area.

In conventional fire alarm systems, a plurality of fire detectors are connected in parallel across a pair of lines for every area, and the lines are short-circuited when a physical phenomenon such as heat or smoke caused by fire has reached a predetermined value to transmit fire signals to the control panel. Therefore, the area where fire has broken out could be indicated only roughly by the control panel. In other words, it is not possible to indicate which fire detector has worked or the change of its output, and it is not possible to indicate the burning condition. Namely it is not possible to suitably control equipment for preventing or expelling the smoke, or to suitably control fire extinguishers.

In view of the above-mentioned situations, the object of the present invention is to provide a fire alarm system according to which, in case a fire detector has operated, fire signals are transmitted to the control panel like the conventional fire detector, and an address signal which indicates the operated fire detector and the change in output of the detector are transmitted to the control panel, such that the area where fire has broken out, the operated fire detector and the change of its output, are indicated by the control panel.

The fire alarm facility according to an embodiment of the present invention will now be described below in conjunction with Figs. 1 to 3.

7

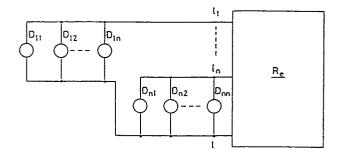

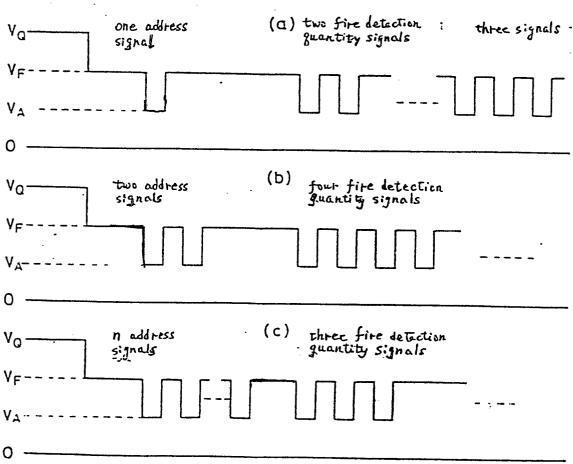

In Fig. 1, symbols  $D_{ll}$  to  $D_{ln}$  and  $D_{nl}$  to  $D_{nn}$  denote fire detectors that are connected in parallel across a pair of lines l<sub>1</sub> and l through up to a pair of lines l<sub>n</sub> to l covering every area, and Re denotes a control panel. The fire detectors connected in parallel in each area have been constructed in the same way except a decoder that is provided to generate an address signal specific to the detector. Therefore, the detector  $D_{11}$  only will be described below with reference to Figs. 2 and 3, in which reference numeral 1 denotes a fire detector circuit which consists of a fire detector portion 2, and a comparator 3 such as operational amplifier A that detects a predetermined output of the detector portion 2. The fire detector portion 2 has an inner ion chamber CH1 and an outer ion chamber  ${

m CH}_2$  connected in series, and an FET which detects the change in potential at a middle point between the inner ion chamber and the outer ion chamber. Reference numeral 4 denotes an inhibit circuit whose input is connected to the output of the comparator 3, and whose inhibit input is connected to a line voltage detector circuit 5 which detects a predetermined voltage drop across a pair of lines 11 and &. The detector circuit 5 consists of a transistor  $T_1$ , a Zener diode  $Z_1$ , and resistors  $R_1$ ,  $R_2$ . Under the supervisory condition, the Zener diode Z1 is rendered conductive, whereby the transistor T1 is rendered conductive. When other detectors connected in parallel across the lines  $\ell_1$  and  $\ell$ have worked to decrease the line voltage, the Zener diode Z<sub>1</sub> is rendered non-conductive, whereby the transistor T<sub>1</sub> becomes non-conductive. Reference numeral 6 denotes a latch circuit consisting of an RS flip-flop circuit, the set terminal being connected to the inhibit circuit 4, and the output terminal being connected to a switching circuit 7 and to a delay circuit 8. The switching circuit 7 is connected across the pair of lines l, l to produce fire signals, and

consists of a Zener diode Z2 having a Zener voltage smaller than that of the Zener diode  $Z_1$ , and a transistor  $T_2$ . The base of the transistor  $T_2$  which serves as an input terminal is connected to the output of the latch circuit 6. The delay circuit 8 so works that the output of the latch circuit 6 is produced being delayed by a predetermined period of time, and consists of a resistor R3 and a capacitor C1. The output of the delay circuit 8 is sent to a non-stable multivibrator ll via a Schmidt trigger inhibit circuit 9 and an OR circuit 10. Reference numeral 12 denotes a counter which counts pulse outputs produced by the multivibrator 11, and 13 denotes a decoder which produces an output at a predetermined counted value of the counter 12. In the case of this detector  $D_{11}$ , the output is produced when "1" is counted. As for other detectors (see Fig. 1) connected in parallel across the lines  $l_1$  and  $l_n$  for example, as for the detector  $D_{12}$ , the decoder produces an output when "2" is counted. As for the detector  $D_{ln}$ , the decoder produces an output when "n" is counted.

Reference numeral 14 denotes a latch circuit which consists of an RS flip-flop circuit, the set terminal thereof being connected to the output of the decoder 13, and the output terminal thereof being connected to the inhibit input of the inhibit circuit and to a clear terminal of the counter 12 via the OR circuit 15. Reference numeral 16 denotes a switching circuit which is connected across the lines  $\ell_1$  and  $\ell$ like the switching circuit 7, and which works to send the address and fire detection quantity signal of the detector  $D_{11}$ . The switching circuit 7 consists of a Zener diode  $Z_3$ having a Zener voltage smaller than that of the Zener diode  $Z_2$ , and a transistor  $T_3$ , the base of the transistor  $T_3$  which serves as an input terminal being connected to the output of the non-stable multivibrator 11. Reference numeral 17 denotes a delay circuit which is connected to the output of the latch circuit 14, which consists of a resistor  $R_4$ , a capacitor C2 and a Schmidt trigger circuit B, and which has

a delay time that is sufficiently longer than the time for sending address signals. Reference numeral 18 denotes a nonstable multivibrator which operates responsive to the output of the delay circuit 17, and which has a pulse width and a period longer than the time for sending the fire detection quantity signals to the control panel Re via the multivibrator 11. The output of the non-stable multivibrator 18 is connected to the non-stable multivibrator 11 via a flip-flop circuit 19 and the OR circuit 10. Reference numeral 20 denotes an analog-to-digital converter of which the analog input is connected to the source of the FET in the fire detector portion 2, of which the digital output is supplied to one input of a digital coincidence circuit 21, and of which the strobe input is connected to the output of the non-stable multivibrator 18. The digital coincidence circuit 21 consists of a magnitude comparator, wherein another input for comparison is connected to the output of the counter 12, and the coincidence output is supplied to the clear terminal of the counter 12 via the OR circuit 15, and is also supplied to the reset terminal of the flip-flop circuit 19 via OR circuit 22. Reference numeral 23 denotes a reset circuit which consists of resistors  $R_5$  to  $R_7$ , a capacitor  $C_3$ , and a transistor T4, that are provided on the output side of the constantvoltage circuit 24. The collector of the transistor  $T_{\Delta}$  which produces an output is connected to the clear terminal of the counter 12 and to the reset terminal of the flip-flop circuit 19 via the OR circuits 15 or 22, and to reset terminals of the latch circuits 6, 14.

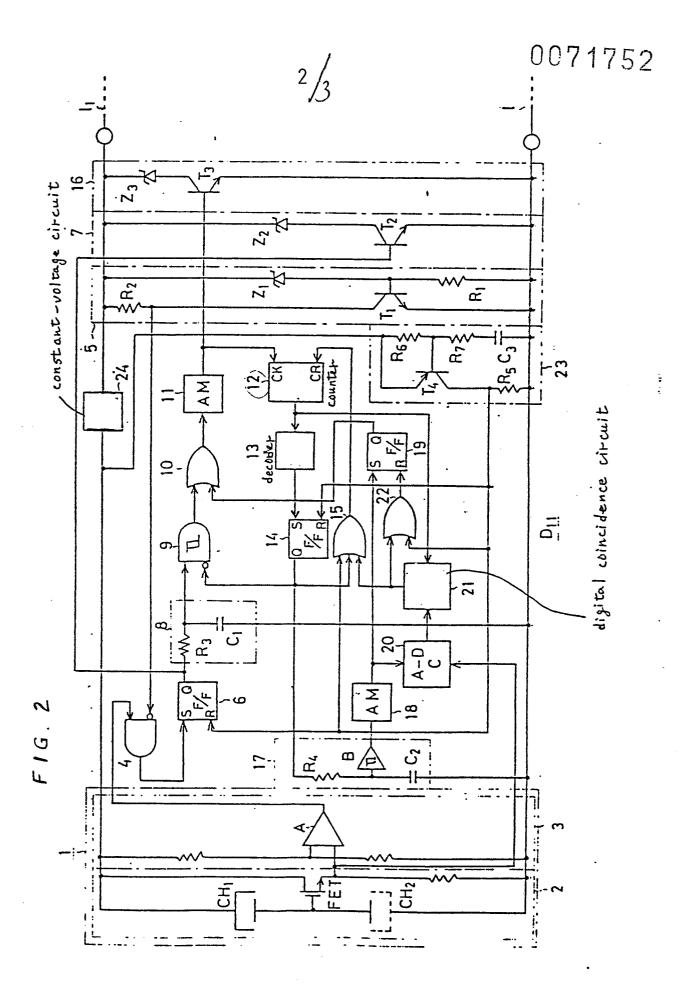

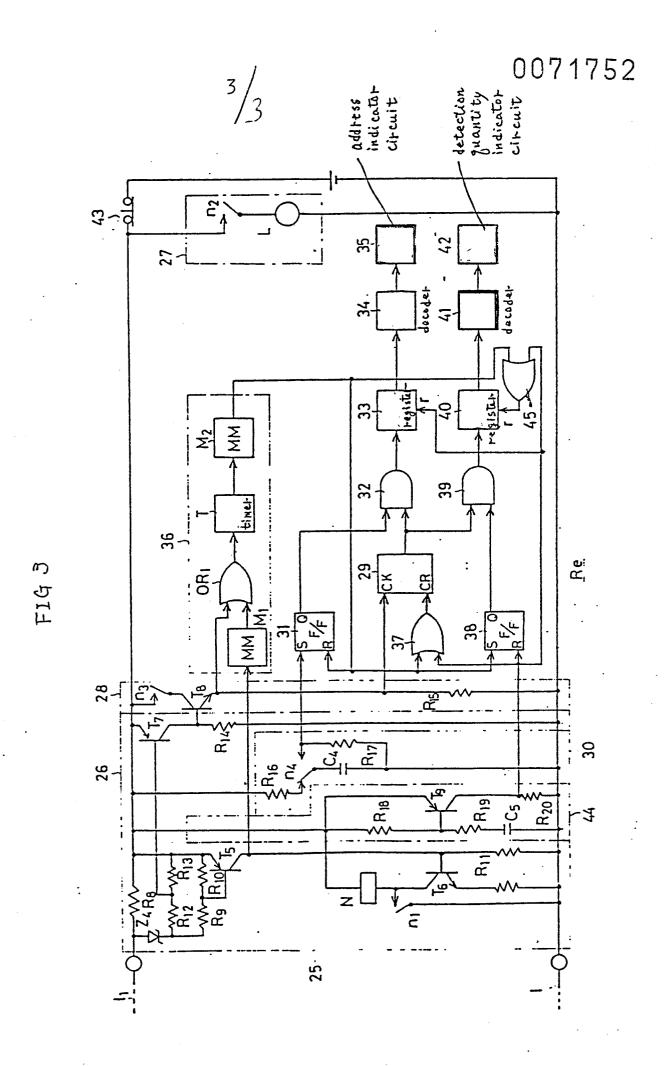

Reference numeral 25 denotes a fire signal receiver circuit in the control panel Re, which consists of resistors  $R_8$  to  $R_{11}$ , a Zener diode  $Z_4$ , a transistor  $T_5$  which becomes conductive upon receipt of a fire signal from the fire detector, and a self-holding circuit made up of a transistor  $T_6$ , a relay N, and a contact point  $n_1$ . Reference numeral 26 denotes a circuit which receives addresses and fire detection quantity signals, and which consists of resistors  $R_8$ ,  $R_{12}$  to  $R_{14}$ ,

a Zener diode Z4, and a transistor T7 which is rendered conductive responsive to a pulse such as an address signal from the fire detector. Reference numeral 27 denotes an alarm indicator circuit which indicates the section where fire has broken out, and which consists of a lamp L that will be turned on when a contact n2 of a relay N is closed. Reference numeral 28 denotes an AND circuit which consists of a contact n3 of a relay N, a transistor T8 of which the base is connected to the collector of the transistor  $T_7$ , and a resistor  $R_{15}$ , that are all connected in series, 29 denotes a counter which counts the number of pulses sent through the AND circuit 28 as address signals and fire detection quantity signals, and which assumes the form of a four-bit binary counter like the counter 12 in the detector, 30 denotes a pulse generator circuit which consists of resistors R<sub>16</sub>, R<sub>17</sub>, a capacitor  $C_4$  and a contact  $n_4$  of a relay N. The pulse generator circuit 30 is connected to inputs of the AND circuit 32 via a flip-flop circuit 31 together with the output of the counter 29, such that only the number of pulses in the form of address signals is stored in a register 33 of a subsequent stage. Further, reference numeral 34 denotes a decoder which converts binary values stored in the register 33 into different values, e.g., which converts binary numbers into decimal numbers. Reference numeral 35 denotes an address indicator circuit which indicates a detector that is operated by the output of the decoder 34, and which consists of numeral display tubes. Reference numeral 36 denotes a timer circuit which produces a single pulse after a predetermined period of time has passed from the reception of a fire signal, an address signal or a fire detection quantity signal produced by the fire detector. The timer circuit 36 consists of a monostable multivibrator M1 of which the input is connected to the collector of the transistor T5, an OR circuit OR<sub>1</sub> of which the inputs are connected to the emitter of the transistor  $T_8$  and to the output of the vibrator  $M_1$ , respectively, a timer T, and a monostable multivibrator  $M_2$ . The output of the timer circuit 36 is connected to the clear terminal of the counter 29 via OR circuit 37, connected to the reset terminal of the flip-flop circuit 31, and is connected to the set terminal of a flip-flop circuit 38. The output of the flip-flop circuit 38 is connected to the inputs of an AND circuit 39 together with the output of the counter 29, such that the number of pulses in the form of fire detection quantity signals is temporarily stored in a register 40 in a subsequent stage. Further, reference numeral 41 denotes a decoder which converts binary numbers stored in the registers 40 into different values, e.g., which converts binary numbers into decimal numbers, 42 denotes a fire detection quantity indicator circuit which indicates a fire detection quantity depending upon the output of the decoder 41, and which consists of numeral display tubes, 43 denotes a push-button switch for restoration, and 44 denotes a reset circuit which consits of resistor  $R_{18}$  to  $R_{20}$ , a capacitor  $C_5$ , and a transistor  $T_9$ . The collector of the transistor  $T_9$ which produces output is connected to the flip-flop circuit 38 and to the reset terminal of the register 33, and is further connected to the clear terminal of the counter 29 and to the reset terminal of the register 40, respectively, via OR circuits 37 and 45, and another input of the OR circuit 45 is connected to the output of the timer circuit 36.

Operation of the circuit will be described below. In Fig. 2, if smoke produced by fire enters into the ion chamber  ${\rm CH_2}$  in the fire detector portion 2 of a fire detector  ${\rm D_{11}}$  among a multiplicity of fire detectors  ${\rm D_{11}}$  to  ${\rm D_{1n}}$  connected in parallel across the lines  ${\rm \ell_1}$  and  ${\rm \ell_1}$ , the source potential of FET rises, whereby the comparator 3 operatives at a predetermined value, and the output is sent to the inhibit circuit 4. In this case, other sensors  ${\rm D_{12}}$  to  ${\rm D_{1n}}$  connected in parallel between the lines  ${\rm \ell_1}$  and  ${\rm \ell}$  do not operate, the line voltage detector circuit 5 is inoperative, and the inhibit input of the inhibit circuit 4 assumes the low level. Therefore, the output from the fire detector circuit 1 sets the

flip-flop circuit which works as a latch circuit 6 via inhibit circuit 4, and is further transmitted to the switching circuit 7 and to the delay circuit 8.

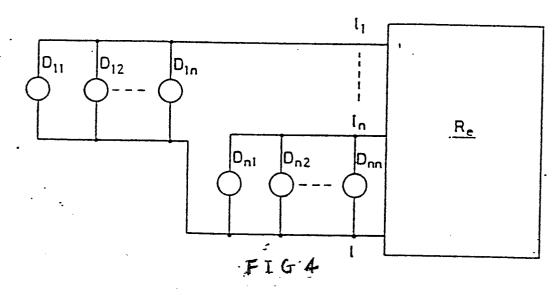

Responsive to this output, the switching circuit 7 renders the transistor  $\mathtt{T}_2$  conductive. Therefore, a voltage  $\mathtt{V}_\alpha$  across the lines  $l_1$  and l is dropped to a value  $V_F$  as determined by the Zener diode Z2, as shown in Fig. 4(a), and the thus obtained fire signal is sent to the control panel Re. Accordingly, the voltage drops across the resistor Rg in the fire signal receiver circuit 25 in the receiver Re, whereby the transistor T5 is rendered conductive, the monostable multivibrator  $M_1$  in the timer circuit 36 is operated to energize the timer T through OR circuit OR1 and to actuate the relay N so that its operation is maintained by the closure of its contact n<sub>1</sub>. Consequently, the contact n<sub>2</sub> in the alarm indicator circuit 27 is closed to turn the lamp L on. Thus, it is indicated that fire broke out in the area where the detectors  $D_{11}$ ,  $D_{12}$  to  $D_{1n}$  are connected in parallel between the lines  $\ell_1$  and  $\ell$ .

Further, while the fire signals are being received by the control panel Re, outputs of the latch circuit 6 delayed through the delay circuit 8 drive the non-stable multivibrator 11 via inhibit circuit 9 and OR circuit 10, such that pulse outputs are generated. The pulses are counted by the counter 12. When a pulse number "1" is counted, the decoder 13 operates, whereby the flip-flop circuit that works as latch circuit 14 is set, the inhibit input of the inhibit circuit 9 assumes the high level, the non-stable multivibrator 11 is stopped through the OR circuit 10, the counter 12 is cleared through the OR circuit 15, and the output is sent to the delay circuit 17. Furthermore, the transistor  $T_3$ in the switching circuit 16 operates for a short period of time responsive to a pulse output from the multivibrator 11, and the voltage across the lines  $\ell_1$  and  $\ell$  is dropped to  $V_A$ as shown in Fig. 4(a), such that the address signal in the

form of a pulse produced by the detector  $D_{11}$  is sent to the receiver Re. In the control panel Re, the transistor T7 in the circuit 26 which receives address signals and fire detection quantity signals, operates responsive to the pulse and is turned on through the contact n3 in the AND circuit 28 where the transistor Tg has already been closed, and a pulse number "1" is counted in the counter 29. In the pulse generator circuit 30, furthermore, the contact n4 in the relay N is switched and the flip-flop circuit 31 is set. The value counted by the counter 29 therefore is temporarily stored in the register 33 through AND circuit 32, and "1" is displayed on the numeral display tube of the address indicator circuit 35 through decoder 34, to indicate that the first detector has operated, i.e., to indicate that the fire detector D<sub>11</sub> has operated. Thereafter, the timer T which operates after a predetermined period of time has passed produces an output which causes the monostable multivibrator M<sub>2</sub> to operate, and the flip-flop circuit 31 is reset by the pulse, the counter 29 is cleared through the OR circuit 37, and the flip-flop circuit 38 is set. While the address signals are being received by the control panel Re, outputs of the latch circuit 14 delayed by the delay circuit 17 in the fire detector D<sub>11</sub> drive the non-stable multivibrator 18 so that it will periodically produce pulses having a long pulse width. Responsive to the pulses introduced through the flipflop circuit 19 and the OR circuit 10, the non-stable multivibrator 11 and the analog-to-digital converter 20 are intermittently actuated. The number of pulses generated by the multivibrator 11, i.e., the value counted by the counter 12, and the fire detection quantity of the fire detector portion 2, i.e., the output of the analog-to-digital converter 20, are compared in the digital coincidence circuit 21 which produces an output when the analog quantity produced by the fire detector portion 2 is in agreement with the value counted by the counter 12. This output resets the flip-flop circuit 19 through OR circuit 22, stops the non-stable multivibrator 11 through OR circuit 10, and clears the counter 12 through

OR circuit 15. Therefore, the non-stable multivibrator 11 produces pulses of a number corresponding to the fire detection quantity of the fire detection portion. The flip-flop circuit 19 is set responsive to pulses generated successively from the non-stable multivibrator 18, to actuate the nonstable multivibrator 11 and the analog-to-digital converter 20. Being controlled by the digital coincidence circuit 21, therefore, the pulses are continuously produced by the nonstable multivibrator ll in a number corresponding to the fire detection quantity of that time. Responsive to the thus produced pulses, the transistor T3 in the switching circuit 16 operates for short periods of time, such that the voltage across the lines  $\ell_1$  and  $\ell$  is dropped to  $V_A$  twice and then thrice as shown in Fig. 4(a). Thus, fire detection quantity signals are sent to the receiver to indicate that the output of the fire detection portion 2 is increasing, for example, to 2 volts and then 3 volts. In the control panel Re, the transistor T7 in the circuit 26 which receives address signals and fire detection quantity signals, operates responsive to the pulses, whereby the transistor Tg in the AND circuit 28 is intermittently rendered conductive twice, the timer circuit 36 is energized, the counter 29 counts the pulse number "2", the counted value is temporarily stored in the register 40 through AND circuit 39, and "2" is displayed on the numeral display tube of the detection quantity indicator circuit 42 via decoder 41, to indicate that the output of 2 volts is produced by the fire detection portion 2 in the fire detector  $D_{11}$ . The monostable multivibrator  $M_2$  is then operated by the output of the timer T which operates after a predetermined time has passed, the counter 29 is cleared through OR circuit 37, and the register 40 is reset through OR circuit 45. The fire detection quantity signals are then received by the receiver circuit 26, and "3" is displayed in the detection quantity indicator circuit 42, to indicate that the output produced by the fire detector D<sub>11</sub> has risen to 3 volts. The above operation is performed repetitively, and the fire detection quantity produced by the

detector  $\mathrm{D}_{11}$  is displayed on the control panel Re with the lapse of time. As for other detectors  $\mathrm{D}_{12}$  to  $\mathrm{D}_{1n}$  connected in parallel across the lines  $\ell_1$  and  $\ell$ , the transistor  $\mathrm{T}_1$  in their circuit 5 for detecting line voltage remains non-conductive, the inhibit input of the inhibit circuit 4 assumes the high level, and no output is transmitted from the fire detector circuit 1. Namely the detectors  $\mathrm{D}_{12}$  to  $\mathrm{D}_{1n}$  remain in the inoperative condition.

When the fire detector  $D_{12}$  has operated instead of the fire detector  $D_{11}$ , the non-stable multivibrator 11 of the detector is stopped by the output of the decoder 12 under the condition in which two pulses are sent. Therefore, two pulses are sent through the switching circuit 16 as shown in Fig. 4(b). When the fire detector D<sub>ln</sub> has operated, n pulses are sent as shown in Fig. 4(c). In the control panel Re, therefore, the pulses are counted by the counter 29, and the address indicator circuit 35 indicates that the second detector or the n-th detector has operated. When a fire detector  ${\tt D_{nl}}$  of other area has operated, a fire signal receiver circuit 25 (which is not shown) operates to indicate the area where fire has broken out, and the pulse number "1" produced by the detector as an address signal is detected by the circuit which receives address signals and fire detection quantity signals, whereby it is indicated that the first detector has operated. Moreover, the output of the detector is indicated relying upon the fire detection quantity signals that are introduced subsequently. When a button switch 43 for -restoring the control panel Re is depressed for a short period of time, the reset circuit 23 in the detector and the reset circuit 44 in the control panel Re operate; i.e., the detector and the control panel are restored to normal condition. Although ion chambers are employed as the fire detector portion 2 in the above-mentioned embodiment, it is of course allowable to employ a fire detector portion of the photoelectric type which detects the light scattered by the smoke or of the thermal type such as thermistors.

The invention is constructed and operates as mentioned above. Namely, the invention provides a fire alarm system which is capable of discriminating the operation of a fire detector in an area where a plurality of fire detectors are connected in parallel across the same lines, and which is also capable of detecting the change in the output produced by the detector as a result of the fire.

#### 4. Brief Description of the Drawings:

Fig. 1 is a circuit diagram illustrating connections of fire detectors and a control panel in a fire alarm system according to the present invention;

Fig. 2 is a circuit diagram of a fire detector of Fig. 1;

Fig. 3 is a circuit diagram of a control panel of Fig. 1; and

Fig. 4 is a diagram showing voltage waveforms for illustrating the present invention.

l Fire Detector Circuit, 2 Detector portion, 3 Comparator, 4,9 Inhibit Circuit, 5 Line Voltage Detector Circuit, 6,14 Latch Circuit, 7,16 Switching Circuit, 8,17 Delay Circuit, 11,18 Non-Stable Multivibrator, 12,29 Counter, 13,34,41 Decoder, 19 Flip-Flop Circuit, 20 Analog-To-Digital Converter, 21 Digital Coincidence Circuit, 25 Fire Signal Receiver Circuit, 26 Circuit Which Receives Addresses and Fire Detection Quantity Signals, 27 Alarm Indicator Circuit, 28 AND Circuit, 35 Address Indicator Circuit, 42 Fire Detection Quantity Indicator Circuit

# STATEMENT

In his letter dated October 29, 1982 which was received by the EPO on November 2, 1982 the Applicant requested that the following corrections of obvious errors made in the originally filed text of the description should be allowed:

| OLD DESCRIPTION |                | NEW DESCRIPTION |                   |  |

|-----------------|----------------|-----------------|-------------------|--|

| Page            | <u>line</u>    | <u>Page</u>     | <u>line</u>       |  |

| 5               | 21 : an        | . 5             | 17 : AND          |  |

| 6               | 26 : Fig. 1    | 6               | 25 : Fig. 2       |  |

| 7               | 4 : circuit    | 6               | 34 : circuit 5    |  |

| 7               | 5 : circuit    | 6               | 35 : circuit 4    |  |

| 7               | 6 : circuit    | 6               | 36 : circuit 1    |  |

| 8               | 28 : converter | 8               | 27 : converter 20 |  |

| 11              | 4 : panel      | 10              | 30 : panel Re     |  |

The request for correction is allowed under Rule 88 EPC.

The Hague, 15 DEC. 1982

RECEIVING SECTION

R. KRAANEN Ext.Nr.: 3040

## Patent Claims

A fire alarm system having:

fire detectors each of which comprising:

- a fire detector circuit which detects a predetermined fire detection quantity produced by a fire detector portion such as an ion chamber or a thermistor which detects burning related phenomenon such as smoke or heat;

- a first inhibit circuit which inhibits the transmission of output from said fire detector circuit when a line voltage of a pair of lines connected to the control panel is dropped;

- a first latch circuit which stores the output sent from the first inhibit circuit;

- a first switching circuit which works to decrease the voltage of said line responsive to the operation of the first latch circuit, in order to send a fire signal to the control panel;

- a first delay circuit which produces an output after a predetermined period of time has passed from the operation of the first latch circuit:

- a second inhibit circuit which inhibits the transmisssion of output of the first delay circuit responsive to the output of a second latch circuit that will be mentioned below;

- a first non-stable multivibrator which is operated by the second inhibit circuit;

a second switching circuit which is intermittently operated by the output of the first non-stable multivibrator, which is connected across the lines together with said first switching circuit, and which works to decrease the line voltage in order to send an address signal and a signal of fire detection quantity to the receivers;

a decoder which generates address signals to detect a predetermined value of a counter that counts the outputs of the first non-stable multivibrator;

a second latch circuit which stores the output of the decoder;

a second delay circuit which produces an output after a predetermined period of time has passed responsive to the operation of the second latch circuit;

a second non-stable multivibrator which operates responsive to the output of the second delay circuit;

an analog-to-digital converter which converts analog outputs into digital values, said analog outputs being produced by a flip-flop circuit which is set by the second non-stable multivibrator and which actuates said first non-stable multi-vibrator, and said analog outputs being further produced by the fire detection portion; and

a digital coincidence circuit which compares the output of the converter with the output of said counter, and stops said first non-stable multivibrator when said outputs are in agreement;

and a control panel comprising:

a fire signal receiving circuit which detects a predetermined line voltage dropped by the operation of the first switching circuit in the fire detector; a circuit for receiving addresses and fire detection quantity signals that are produced by the second switching circuit in the fire detector;

an AND circuit which permits the passage of the circuit that receives addresses and fire detection quantity signals, responsive to the operation of said fire signal receiving circuit;

a counter which counts the pulse outputs of said AND circuit; decoders which detect the counter values and which indicate addresses and fire detection quantities; and

a display circuit.

FIG 1

0071752

Application number

EP 82 10 5866

|                                                                                                                                                                 | DOCUMENTS CONS                                        | IDERED TO BE     | RELEVANT                                                                                                                                                                                        | •                    |                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------------------------------------------------------------|

| Category                                                                                                                                                        | Citation of document wi                               |                  |                                                                                                                                                                                                 | Relevant<br>to claim | CLASSIFICATION OF THE APPLICATION (Int. Cl. <sup>3</sup> ) |

| A                                                                                                                                                               | GB-A-2 030 336 *Abstract; from to page 3, line        |                  | line 87<br>s 1,2*                                                                                                                                                                               | 1                    | G 08 B 25/00                                               |

| A                                                                                                                                                               | DE-A-2 261 179 *Page 4, line 3 30; figure 1*          |                  | 5, line                                                                                                                                                                                         | 1                    |                                                            |

| А                                                                                                                                                               | US-A-4 162 483<br>*Column 2, line<br>lines 42-57; fig | s 3-64; co       | lumn 8,                                                                                                                                                                                         | 1                    |                                                            |

| A                                                                                                                                                               | FR-A-2 111 743 *Claims 1,2* & C                       |                  | 338 470                                                                                                                                                                                         | 1                    | ·                                                          |

|                                                                                                                                                                 |                                                       |                  |                                                                                                                                                                                                 |                      |                                                            |

|                                                                                                                                                                 |                                                       |                  |                                                                                                                                                                                                 | -                    | TECHNICAL FIELDS<br>SEARCHED (Int. Cl. 3)                  |

|                                                                                                                                                                 |                                                       |                  | -                                                                                                                                                                                               |                      | G 08 B                                                     |

| i                                                                                                                                                               |                                                       |                  |                                                                                                                                                                                                 |                      |                                                            |

|                                                                                                                                                                 |                                                       |                  |                                                                                                                                                                                                 |                      |                                                            |

|                                                                                                                                                                 |                                                       |                  |                                                                                                                                                                                                 |                      |                                                            |

|                                                                                                                                                                 |                                                       |                  |                                                                                                                                                                                                 |                      | -                                                          |

|                                                                                                                                                                 |                                                       |                  |                                                                                                                                                                                                 |                      |                                                            |

|                                                                                                                                                                 | -                                                     |                  |                                                                                                                                                                                                 |                      |                                                            |

|                                                                                                                                                                 |                                                       |                  |                                                                                                                                                                                                 |                      |                                                            |

|                                                                                                                                                                 |                                                       |                  |                                                                                                                                                                                                 |                      |                                                            |

| The present search report has been drawn up for all claims                                                                                                      |                                                       |                  |                                                                                                                                                                                                 |                      |                                                            |

| Place of search Date of completic OS-IO-                                                                                                                        |                                                       | on of the search | SGURA                                                                                                                                                                                           | Examiner S.          |                                                            |

| X: particularly relevant if taken alone     Y: particularly relevant if combined with another     document of the same category     A: technological background |                                                       |                  | T: theory or principle underlying the invention E: earlier patent document, but published on, or after the filing date D: document cited in the application L: document cited for other reasons |                      |                                                            |

|                                                                                                                                                                 |                                                       |                  | &: member of the same patent family, corresponding document                                                                                                                                     |                      |                                                            |