11) Veröffentlichungsnummer:

**0 075 122**

12

## **EUROPÄISCHE PATENTANMELDUNG**

(21) Anmeldenummer: 82107719.5

(51) Int. Cl.3: G 06 G 7/186

2 Anmeldetag: 23.08.82

(30) Priorität: 22.09.81 DE 3137708

Anmelder: SIEMENS AKTIENGESELLSCHAFT, Berlin und München Wittelsbacherplatz 2, D-8000 München 2 (DE)

Weröffentlichungstag der Anmeldung: 30.03.83 Patentblatt 83/13

84) Benannte Vertragsstaaten: DE FR GB

© Erfinder: Pfleiderer, Hans-Jörg, Dr., Franz-Krinninger-Weg 23, D-8011 Zorneding (DE)

Integratorschaltung mit einem Differenzverstärker.

Die Erfindung bezieht sich auf eine Integratorschaltung mit einem kapazitiv rückgekoppelten Differenzverstärker (2) und mit einer Kapazität (C2), deren erste Elektrode über einen ersten Schalttransistor (S1) mit dem Schaltungseingang (1) und über einen zweiten Schalttransistor (S3) mit dem invertierenden Verstärkereingang verbunden ist. Angestrebt wird, daß die Schaltung der bilinearen Übertragungsfunktion genügt. Erreicht wird dies dadurch, daß die zweite Elektrode der Kapazität (C2) über einen dritten, mit dem zweiten (S3) synchron betätigbaren Schalttransistor (S2) mit dem Schaltungseingang (1) und über einen vierten mit dem ersten synchron betätigbaren Schalttransistor (S4) mit dem nichtinvertierenden Verstärkereingang verbunden ist. Der Anwendungsbereich der Erfindung umfaßt monolithisch integrierte Filterschaltungen.

075 122

SIEMENS AKTIENGESELLSCHAFT Berlin und München

Unser Zeichen VPA 81P 7 121 E

### Integratorschaltung

5

10

Die Erfindung bezieht sich auf eine Integratorschaltung mit einem Differenzverstärker, dessen Ausgang mit dem invertierenden Verstärkereingang über einen Rückkopplungszweig verbunden ist, der eine erste Kapazität enthält, und mit einer zweiten Kapazität, deren erste Elektrode über einen ersten, mit einer ersten Taktimpulsspannung angesteuerten Schalttransistor mit dem Schaltungseingang und über einen zweiten, mit einer zweiten Taktimpulsspannung angesteuerten Schalttransistor mit dem invertierenden 15 Verstärkereingang verbunden ist. Eine derartige Integratorschaltung ist beispielsweise aus dem IEEE Journal of Solid-State Circuits, Vol. SC-12, No. 6, Dezember 1977, Seiten 600 bis 608, insb. Fig. 1 und Fig. 2, bekannt.

20 Aufgabe der Erfindung ist es, eine Integratorschaltung der eingangs genannten Art anzugeben, die der bilinearen Übertragungsfunktion

$$\frac{u_{A}}{u_{E}} = \frac{C2}{C1} \cdot \frac{1+z^{-1}}{1-z^{-1}}$$

(1)

genügt. Dabei bedeuten  $\mathbf{u}_{\mathrm{E}}$  die am Schaltungseingang anliegende Spannung,  $\mathbf{u}_{\mathrm{A}}$  die Ausgangsspannung, C1 die erste Kapazität, C2 die zweite Kapazität und  $z^{-1}$  den Verzöge-30 rungsoperator (delay time operator). Für den letzteren gilt weiterhin

$$z^{-1} = e^{-j \cdot 2} \mathcal{K} f T$$

(2)

wenn f die Frequenz der Taktimpulsspannungen und T die Periodendauer derselben, d.h. die Taktperiode, darstellen. Die Aufgabe wird erfindungsgemäß durch eine Ausbildung

der Integratorschaltung entsprechend dem kennzeichnenden Teil des Patentanspruchs 1 gelöst.

Die zur Realisierung der bilinearen Übertragungsfunktion (1)

5 dienende Integratorschaltung nach der Erfindung zeichnet sich insbesondere dadurch aus, daß sie in einfacher und flächensparender Weise auf einem dotierten Halbleiterkörper monolithisch integriert werden kann.

10 Die Ansprüche 2 bis 4 sind auf bevorzugte Ausgestaltungen und Weiterbildungen der Integratorschaltung nach Anspruch 1 gerichtet.

Die Erfindung wird nachfolgend anhand der Zeichnung näher 15 erläutert. Dabei zeigt:

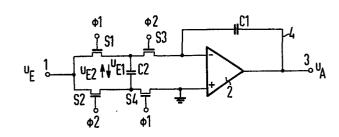

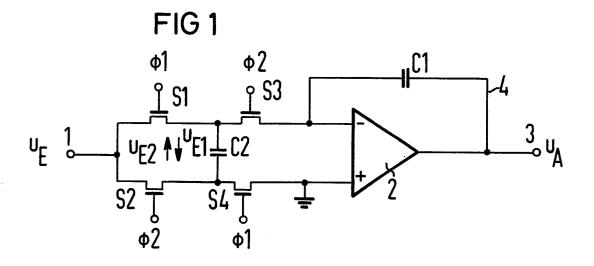

- Fig. 1 das Prinzipschaltbild eines bevorzugten Ausführungsbeispiels der Erfindung,

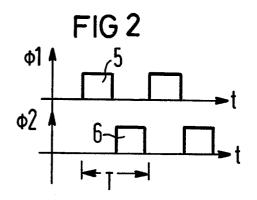

- Fig. 2 Spannungs-Zeit-Diagramme zur Erläuterung von Fig. 1,

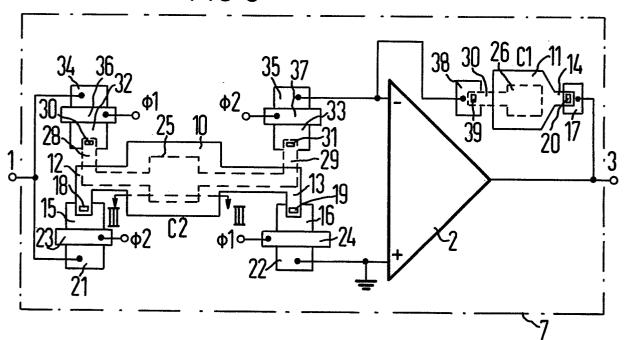

- 20 Fig. 3 eine zweckmäßige Ausgestaltung der Integratorschaltung nach Fig. 1 in integrierter Schaltungstechnik,

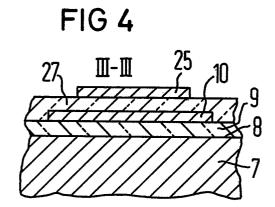

- Fig. 4 einen Querschnitt durch die Anordnung von Fig. 3 längs der Linie III-III.

- 25 In Fig. 1 ist ein Schaltungseingang über einen Schalttransistor S1 mit der oberen Elektrode einer Kapazität C2

verbunden, wobei das Gate von S1 mit einer Taktimpulsspannung Ø 1 beschaltet ist. Die untere Elektrode von C2 ist

über einen Schalttransistor S2, an dessen Gate eine Takt-

- impulsspannung Ø 2 liegt, an den Schaltungseingang 1 geführt. Die obere Elektrode von C2 ist andererseits über

einen mit Ø 2 angesteuerten Schalttransistor S3 mit dem

invertierenden Eingang eines Differenzverstärkers 2 verbunden, dessen nichtinvertierender Eingang auf Bezugspo-

- 35 tential liegt. Die untere Elektrode von C2 ist über

einen Schalttransistor S4 auf Bezugspotential gelegt. Dabei ist das Gate von S4 mit der Taktimpulsspannung Ø 1 beaufschlagt. Der Ausgang 3 des Differenzverstärkers 2, der gleichzeitig den Schaltungsausgang darstellt, ist über einen Rückkopplungszweig 4, der eine Kapazität C1 enthält, mit dem invertierenden Verstärkereingang verbunden.

u<sub>E</sub> bezeichnet eine bei 1 anliegende, zu integrierende Eingangsspannung, die kontinuierlich oder auch getastet, d.h. von einem kontinuierlichen Eingangssignal z.B. über ein Abtast-Halteglied abgeleitet sein kann. Auch eine zeitabhängige Vorzeichenumkehr von  $\mathbf{u}_{_{\mathbf{F}}}$  ist durchaus möglich. Beim Auftreten eines Taktimpulses 5 von Ø1 (Fig. 2) wird C2 über die dann leitend geschalteten Transistoren S1 und S4 auf einen Spannungswert  $u_{E1}$  aufgeladen, der in Fig. 1 durch einen nach unten zeigenden Pfeil angedeutet ist. Durch den nächstfolgenden Taktimpuls 6 von Ø 2 werden die Transistoren S2 und S3 leitend geschaltet, so daß C2 mit entge-20 gengesetzter Polung an den zu diesem Zeitpunkt anliegenden Spannungswert  $u_{\rm E,0}$  gelegt wird, der durch einen nach oben gerichteten Pfeil gekennzeichnet ist. Voraussetzung hierfür ist eine große Spannungsverstärkung des Verstärkers 2, die bewirkt, daß an dem invertierenden Verstärkereingang 25 praktisch dasselbe Potential liegt wie an dem nichtinvertierenden Eingang, d.h. also Bezugspotential. Innerhalb einer durch die einander nicht überlappenden Taktimpulse 5 und 6 gegebenen Taktperiode T lädt sichalso C2 auf eine Differenzspannung  $u_{E1} - u_{E2}$  auf, die beim Anliegen von 6 über S3 auf die Kapazität C1 übertragen wird. Die Taktperiode T muß dabei so kurz sein, daß für die Abtastung von  $u_{\rm F}$  das Abtasttheorem (sampling theorem) gilt.

In aufeinanderfolgenden Taktperioden T werden jeweils Um

ladevorgänge von C1 bewirkt, die nach Betrag und Vorzeichen den sich in den einzelnen Taktperioden T jeweils er-

## -4- VPA 81P.7.1.21 E

gebenden Differenzspannungen  $u_{E1}$  -  $u_{E2}$  entsprechen. Damit ist an C1 bzw. am Schaltungsausgang 3 eine Ausgangsspannung  $u_A$  abgreifbar, die als Integrationsergebnis, d.h. als die Integralspannung von  $u_E$ , aufzufassen ist. Der Quotient aus  $u_A$  und  $u_E$  entspricht der bilinearen Übertragungsfunktion (1).

Fig. 3 zeigt eine monolithisch integrierte Ausführungsform der Integratorschaltung nach Fig. 1, bei der parasitäre Kapazitäten zwischen der oberen Elektrode von C2 und den auf Bezugspotential liegenden Schaltungsteilen sowie zwischen der linken Elektrode von C1 und diesen Schaltungsteilen weitgehend vermieden sind. Die Integratorschaltung ist auf einem Körper 7 aus dotiertem Halbleitermaterial z.B. p-dotiertem Silizium, aufgebaut. Der Fig. 4 ist ent-15 nehmbar, daß der Körper 7 eine obere Grenzfläche 8 aufweist, die mit einer dünnen Schicht 9 aus elektrisch isolierendem Material, z.B. SiO2, bedeckt ist. Die untere Elektrode von C2 und die rechte Elektrode von C1 sind als Belegungen 10 und 11 aus elektrisch leitendem Material, 20 z.B. hochdotiertem polykristallinen: Silizium, ausgeführt, die auf der Schicht 9 angeordnet sind. Sie weisen Anschlußstreifen 12, 13 und 14 auf, die zu n-dotierten Halbleitergebieten 15, 16 und 17 hin verlaufen. Oberhalb derselben sind in der Isolierschicht 9 Kontaktlöcher 18 bis 20 vorgesehen, in denen diese Anschlußstreifen die Halbleitergebiete 15 bis 17 kontaktieren.

Es sind weiterhin n-leitende Gebiete 21 und 22 vorgesehen, die zu den Gebieten 15 und 16 im Abstand angeordnet sind. Die Halbleiterbereiche, die jeweils zwischen den Gebieten 15 und 21 sowie 16 und 22 liegen und die Kanalbereiche der Schalttransistoren S2 und S4 darstellen, werden von Gates 23 und 24 überdeckt, die mit Ø 2 und Ø 1 beschaltet sind. Das Gebiet 21 ist mit dem Schaltungseingang 1 und das Gebiet 22 ist mit dem nichtinvertierenden Verstärker-

eingang leitend verbunden. Das n-leitende Halbleitergebiet 17 ist mit dem Schaltungsausgang 3 verbunden.

Die obere Eelektrode von C2 (Fig. 1) und die linke Elektrode sind als leitende Belegungen 25, 26 einer zweiten, 5 oberhalb der Belegungen 10 und 11 liegenden Ebene dargestellt. Sie bestehen beispielsweise aus hochdotiertem, polykristallinen Silizium, sind oberhalb der Belegungen 10 und 11 angeordnet und durch eine Zwischenschicht 27 (Fig.4) aus elektrisch isolierendem Material von diesen getrennt. Sie weisen ferner Anschlußstreifen 28 bis 30 auf, von denen die Anschlußstreifen 28 und 29 oberhalb der Anschlußstreifen 12 und 13 verlaufen und wesentlich schmaler ausgebildet sind als diese. Die Belegungen 25 und 26 sind 15 kleinflächiger als die Belegungen 10 und 11 und relativ zu diesen so angeordnet, daß deren Ränder in lateraler Richtung weit unter den Rändern der Belegungen 25 und 26 hervorragen. Hierdurch werden die oben genannten parasitären Kapazitäten so klein, daß sie praktisch vernach-20 lässigbar sind. Die Anschlußstreifen 28 und 29 kontaktieren im Bereich von Kontaktlöchern 30 und 31 jeweils nleitende Halbleitergebiete 32 und 33, die zusammen mit n-leitenden Halbleitergebieten 34 und 35 und den dazwischen liegenden Halbleiterbereichen; die von gegen die 25 Grenzfläche 8 isolierten und mit Ø 1 und Ø 2 beschalteten Gates 36, 37 überdeckt sind, die Schalttransistoren S1 und S3 darstellen. Das Gebiet 34 ist dabei mit dem Schaltungseingang 1 leitend verbunden, das Gebiet 35 mit dem invertierenden Verstärkereingang. Der Anschlußstreifen 30 30 kontaktiert ein n-leitendes Gebiet 38 im Bereich eines weiteren Kontaktloches 39 der isolierenden Schicht 9. Das Gebiet 38 ist mit dem invertierenden Eingang des Differenzverstärkers 2 verbunden.

<sup>4</sup> Patentansprüche

<sup>35 4</sup> Figuren

#### Patentansprüche

1. Integratorschaltung mit einem Differenzverstärker, dessen Ausgang mit dem invertierenden Verstärkereingang über 5 einen Rückkopplungszweig verbunden ist, der eine erste Kapazität enthält, und mit einer zweiten Kapazität, deren erste Elektrode über einen ersten, mit einer ersten Taktimpulsspannung angesteuerten Schalttransistor mit. dem Schaltungseingang und über einen zweiten, mit einer zwei-10 ten Taktimpulsspannung angesteuerten Schalttransistor mit dem invertierenden Verstärkereingang verbunden ist, dagekennzeichnet, daß die zweite Elektrode der zweiten Kapazität (C2) über einen dritten, mit dem zweiten synchron betätigbaren Schalttransistor (S2) 15 mit dem Schaltungseingang (1) und über einen vierten, mit dem ersten synchron betätigbaren Schalttransistor (S4) mit dem auf Bezugspotential liegenden, nichtinvertierenden Verstärkereingang verbunden ist.

-6-

20 2. Integratorschaltung nach Anspruch 1, dadurch k e n n z e i c h n e t , daß sie auf einem dotierten Halbleiterkörper (7) aufgebaut ist, daß die Elektroden der ersten und zweiten Kapazität (C1 und C2) jeweils aus zwei übereinander liegenden und durch eine elektrisch isolierende Zwischenschicht (27) voneinander getrennten leiten-25 den Belegungen (10,25; 11,26) bestehen, daß die unteren Belegungen (10, 11) jeweils durch eine dünne elektrisch isolierende Schicht (9) von einer Grenzfläche (8) des Halbleiterkörpers (7) getrennt sind und daß die oberen Bele-30 gungen (25, 26) kleinflächiger ausgebildet sind als die unteren (10, 11) und so angeordnet sind, daß die Ränder der unteren in lateraler Richtung wesentlich unter den Rändern der oberen Belgungen (25, 26) hervorragen.

# -7- VPA 81P 7 121 E

- 3. Integratorschaltung nach Anspruch 2, dadurch ge k e n n z e i c h n e t , daß die Belegungen (10, 25)

der zweiten Kapazität (C2) mit Anschlußstreifen (12, 13,

28, 29) versehen sind, die mit den Schalttransistoren verbunden sind, und daß die Anschlußstreifen (28, 29) der

oberen Elektrode oberhalb der Anschlußstreifen (12, 13)

der unteren angeordnet sind und wesentlich schmaler als

die letzteren ausgebildet sind, sodaß die Ränder der

unteren in lateraler Richtung wesentlich unter den Rändern

der oberen Anschlußstreifen (28, 29) hervorragen.

- 4. Integratorschaltung nach Anspruch 2 oder 3, dadurch gekennzeich net , daß der Halbleiterkörper (7) aus dotiertem monokristallinen Silizium und die Elektroden (10,25, 11,26) der ersten und zweiten Kapazität (C1 und C2) aus hochdotiertem polykristallinen Silizium bestehen.

FIG 3