11 Publication number:

0 097 772

**A2**

(12)

## **EUROPEAN PATENT APPLICATION**

(21) Application number: 83103163.8

(5) Int. Cl.<sup>3</sup>: **H 01 L 29/06** H 01 L 21/20

(22) Date of filing: 30.03.83

(30) Priority: 30.06.82 US 393951

(43) Date of publication of application: 11.01.84 Bulletin 84/2

(84) Designated Contracting States: DE FR GB

(71) Applicant: International Business Machines Corporation **Old Orchard Road** Armonk, N.Y. 10504(US)

72 Inventor: Hovel, Harold John **Diane Court** Katonah New York 10536(US)

(72) Inventor: Rosenberg, Robert 101 Lakeview Avenue West Peekskill New York 10566(US)

(74) Representative: Hobbs, Francis John IBM United Kingdom Patent Operations Hursley Park Winchester Hants, SO21 2JN(GB)

- (54) Structure comprising a monocrystalline substrate supporting a device layer of semiconductor material.

- (57) An intermediate, lattice accommodating epitaxial layer (4) of GaAlAs is positioned between a monocrystalline substrate (2), eg of Al<sub>2</sub>O<sub>3</sub>, and a device layer (6) of semiconductor material (eg of GaAs) in which semiconductor devices can be formed. A thin layer (5) of Ge may be included between the substrate (2) and the GaAlAs layer (4) to permit a wider lattice spacing tolerance for the substrate (2).

## STRUCTURE COMPRISING A MONOCRYSTALLINE SUBSTRATE SUPPORTING A DEVICE LAYER OF SEMICONDUCTOR MATERIAL

This invention relates to structures comprising a monocrystalline substrate supporting a device layer of semiconductor material. Intermetallic semiconductor material crystals of more than one element such as GaAs and GaAlAs have a number of properties useful in integrated circuit structures but to take full advantage of those properties it is necessary to build the integrated circuit structure in a thin layer with properties that produce device advantages supported by a substrate with different properties. It is desirable that the properties of the substrate have minimal effect on the properties of the device layer.

One integrated circuit structure in use in the art involves making the integrated circuit in a layer of GaAs on a substrate of high resistivity or semi-insulating GaAs. In this structure impurities in the doping that renders the substrate semi-insulating have a detrimental effect on device performance.

Another integrated circuit structure developed in the art involves the making and the isolating of integrated circuits in a layer of GaAs on a substrate of Al<sub>2</sub>O<sub>3</sub> as described in Metallurgical Transactions Vol. 1, March 1970, pages 623-628 and in Journal of Applied Physics Vol. 42, No. 6, May 1971, pages 2519-2527. In this type of structure, problems are encountered with crystal defects at the GaAs-Al<sub>2</sub>O<sub>3</sub> interface.

Still another semiconductor structure involves selectively doped very thin layers of different semiconductor materials. This structure is known as a high electron mobility transistor (HEMT) and is described in the Japanese Journal of Applied Physics, Vol. 19, No. 5, May 1980, pp. L225 to L227. This structure places very stringent requirements on the quality of the substrate and the semiconductor material adjacent the device.

A structure comprising a monocrystalline substrate supporting a device layer of semiconductor material in which semiconductor devices can be formed, is characterised, according to the invention, by the inclusion of an intermediate, lattice accommodating epitaxial layer of GaAlAs positioned between the monocrystalline substrate and said device layer.

2

The invention may be viewed as an intermediate manufacturing product which may be employed in a variety of ways to achieve integrated circuit structure benefits.

The invention will now be described by way of example, with reference to the accompanying drawings, in which:-

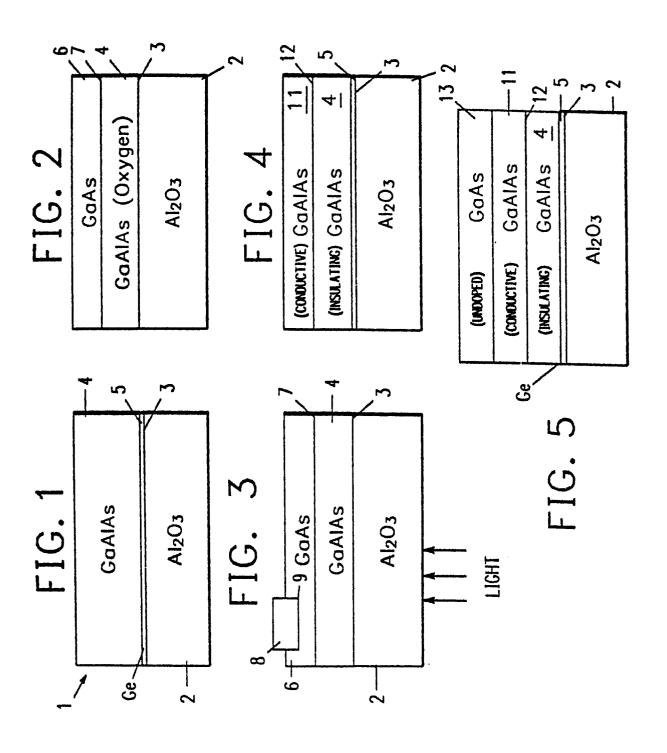

FIG. 1 represents a structure embodying the invention; and

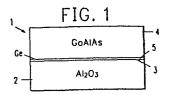

FIGS. 2, 3, 4 and 5 represent various applications of the invention.

Referring to FIG. 1, the structure 1 has a monocrystalline insulating substrate 2 which is joined at a line of demarcation 3 with an epitaxial layer 4 of GaAlAs. The GaAlAs layer 4 is generally undoped but may contain conductivity type determining impurities in accordance with the properties desired to be imparted to the ultimate integrated circuit structure. Since GaAlAs may have varying quantities of Ga and Al usually described as Ga<sub>x</sub>Al<sub>1-x</sub>As where x varies from about 0.1 to 0.9 and the electrical and optical properties vary with x, much flexibility can be achieved. The GaAlAs intermediate layer 4 is epitaxial with the crystalline substrate 2 and provides a barrier to electrons, in a device layer which will be formed over the exposed surface of at least portions of the layer 4, from interacting with interface defects at the interface 3. The GaAlAs intermediate layer 4 also permits wide differences in resistance properties in the material chosen for the substrate 2 from affecting the properties of the integrated circuit devices. A thin

Y09-81-070

layer 5 of Ge may be included in order to improve the lattice spacing transition from the spacing of the substrate 2 to that of the GaAlAs layer 4.

The substrate 2 is of a crystalline material with crystal structure and lattice spacing compatible with epitaxial growth of the GaAlAs layer 4. The substrate may be of insulating material such as sapphire, spinel, ZnSe or conducting GaAs. The substrate may be chosen to impart a variety of properties such as resistance, optical transparency and thermal conductance. Where the substrate 2 is optically transparent and light transmission is employed as part of the application of the invention, the Ge layer 5 would not be used since it is optically opaque to the frequencies of most device materials such as GaAs and GaAlAs.

The structure 1 may be employed in various types of integrated circuit structures as illustrated in FIGS. 2, 3, 4 and 5.

Referring next to FIG. 2, the intermediate structure of FIG. 1 is provided with an epitaxial device layer 6 of GaAs in which an integrated circuit is to be formed. The layer 6 joins the GaAlAs layer 4 epitaxially at an interface 7. In FIG. 2, the region 4 and the region 6 may be provided with oxygen in the few parts per million range. This causes the GaAlAs layer 4 to be highly insulating. The oxygen will also give the GaAs layer 6 high resistivity so that processing operations such as ion implantation to produce arrays of field effect transistors may be employed.

In FIG. 2, while the Ge lattice accommodation layer 5 is not shown, the addition of a 5 micron thickness layer 5 of Ge would permit a wider lattice spacing tolerance in the selection of the material for the substrate 2. Where the substrate 2 is made of the material  ${\rm Al}_2{\rm O}_3$ , the defects at the interface 3 may not, however, be a sufficient problem to justify adding the Ge layer 5 with the added processing complexity.

Referring next to FIG. 3, an optically active device 8 such as a region of GaAs with a p-n junction 9 or a Schottky barrier is positioned in at least a portion of the surface of the region 6. When the structure of FIG. 3 is used, a device actuating light signal can be introduced through a transparent substrate 2 of  $Al_2O_3$  and the intermediate region 4 to produce carriers in the device layer 6 to be collected through an external ohmic contact (not shown) to the device 8. Optical performance can be improved by providing a low recombination velocity condition well known in the photovoltaic cell art at the interface 7. It will be apparent that the Ge layer 5 would not be used in this structure since the Ge would operate to attenuate light of the wavelengths employed with GaAs.

Referring next to FIG. 4, the GaAlAs region 4 is made insulating and is equipped with a conductive GaAlAs layer 11 epitaxially joined to the region 4 at an interface 12. The layer 11 may be formed by the techniques of ion implantation, diffusion or vapor growth.

Referring next to FIG. 5, a layer 13 of undoped GaAs is added to the structure of FIG. 4 where the GaAs layer 13 and the conductive GaAlAs layer 11 are at least 0.06 micrometers thick to provide an improved structure for the high electron mobility transistor (HEMT) device currently receiving attention in the art. In this type of device the layers are so thin that advantage can be taken of the spatial separation between electrons and their parent donor impurities.

Additional advantages occur with the practice of the invention. Misfit dislocations at the interface 3 will be passive in structures employing the invention as opposed to the conditions present in the "silicon on sapphire" type structures common in the silicon industry. Further imperfections originating at the interface 3 will propagate in the intermediate layer 4 but will not grow perpendicular to the interfaces 7 and 12 between the intermediate and device layers and when they

\$100 m

reach the device layers 6 and 11 they will propagate parallel to the interfaces 7 and 12 resulting in a higher quality device layer.

A preferred embodiment of the invention is a structure similar to FIG. 2 with a substrate 2 of Al<sub>2</sub>O<sub>3</sub> of sufficient thickness for handling. A 2 to 20 micron thick layer 4 of Ga<sub>0.5x</sub>Al<sub>1-0.5x</sub>As is epitaxially grown thereon, through the technique of the decomposition of vapors of trimethyl aluminum, trimethyl gallium and arsine. This is followed by a layer of GaAs of at least 0.1 microns thickness in which no Alcontaining vapor is provided in the growth with the Ga source and the As source. In order for the GaAs layer 6 to be useful for active devices, it should have an average carrier mobility of the order of 5,000 centimetres<sup>2</sup> per volt second and have a doping concentration between 10<sup>15</sup> and 10<sup>16</sup> atoms per cc. Where the Ge layer 5 is employed, it would be grown first on the Al<sub>2</sub>O<sub>3</sub> to a depth of around 5 microns followed by the GaAlAs described.

Alternatively, the GaAs layer 6 could be 2 to 20 microns thick and oxygen doped to give it high resistivity and a technique such as ion implantation used to form the active device region.

What has been described is a structure for the fabrication of integrated circuits wherein an intermediate layer of GaAlAs or of GaAlAs and Ge is provided between the substrate and the device layer.

## CLAIMS

- 1. A structure comprising a monocrystalline substrate (2) supporting a device layer (6) of semiconductor material in which semiconductor devices can be formed, the structure being characterised by the inclusion of an intermediate, lattice accommodating epitaxial layer (4) of GaAlAs positioned between the monocrystalline substrate (2) and said device layer (6).

- 2. A structure as claimed in claim 1, in which the substrate consists of sapphire, spinel, ZnSe or GaAs.

- 3. A structure of claim 1 as claimed in claim 1 or claim 2, in which said device layer consists of GaAs.

- 4. A structure as claimed in claim 1 or claim 2, in which said device layer comprises a layer of conductive GaAlAs.

- 5. A structure as claimed in claim 4, in which said device layer further comprises a layer of undoped GaAs overlying the layer of conductive GaAlAs.

- 6. A structure as claimed in any preceding claim, in which both said device layer and the intermediate layer are doped with oxygen.

- 7. A structure as claimed in any preceding claim, further comprising a thin layer of Ge positioned between the monocrystalline substrate and the intermediate layer of GaAlAs..

- 8. A structure as claimed in claim 3, including an electro-optical device formed in said device layer.

- 9. A structure as claimed in claim 8, in which the substrate and the intermediate layer are transparent to light to which said device layer is responsive.

- 10. A structure as claimed in claim 9, in which the substrate consists of  ${\rm Al}_2{\rm O}_3$ .