# Europäisches Patentamt

(19) European Patent Office

Office européen des brevets

⑪ Numéro de publication:

**0115737**

**A1**

**⑫ DEMANDE DE BREVET EUROPEEN**

②1 Numéro de dépôt: 83460006.6

⑤1 Int. Cl.<sup>3</sup>: G 09 G 1/16

② Date de dépôt: 22.12.83

③〇 Priorité: 29.12.82 FR 8222225

(71) Demandeur: Etablissement Public de Diffusion dit "Télédiffusion de France", 21-27 rue Barbès, F-92120 Montrouge (FR)

Demandeur: Leger, Alain André, La Gentilhommière, F-35830 Betton (FR)

(43) Date de publication de la demande: 15.08.84

Bulletin 84/33

(72) Inventeur: Leger, Alain André, La Gentilhommière,

F-35830 Betton (FR)

84 Etats contractants désignés: CH DE GB IT LI NL SE

⑦4 Mandataire: Le Guen, Louis François, 13, rue Emile Barde

BP 91, F-35802 Dinard Cedex (FR)

#### 54 Système de transcodage de matrices pour vidéographie à alphabet dynamiquement redéfinissable.

57 La conversion d'une matrice  $12 \times 10$  points en matrice  $8 \times 10$  points, comporte deux phases, une première où les pixels de chaque ligne sont groupés par trois et chaque groupe est traité logiquement pour obtenir un groupe de deux pixels transformés, une seconde où la configuration de l'ensemble initial des quatre pixels qui est à cheval sur la limite entre deux groupes est examiné.

Quand il est différent de 0110, l'ensemble transformé formé des deux pixels transformés de la première phase, qui sont de part et d'autre de la limite, est conservé et, dans le cas contraire, la configuration de l'ensemble initial correspondant de la ligne antérieure est examiné et:

- s'il vaut 0110, les pixels sont remplacés par les pixels correspondants de la ligne précédente,

- s'il n'est ni égal à 0110, ni à 0000, les pixels sont remplacés par des pixels calculés dans la seconde phase à partir des pixels initiaux, voisins de la ligne courante et de la ligne antérieure,

- s'il est égal à 0000, l'ensemble initial correspondant de la ligne postérieure est examiné et:

- s'il est égal à 0000 ou à 0110, les pixels sont remplacés par 1 et 1,

- s'il est différent de 0000 et de 0110, les pixels sont remplacés par des pixels calculés dans la seconde phase.

Système de transcodage de matrices pour vidéographie

à alphabet dynamiquement redéfinissable

La présente invention concerne un système de transcodage entre matrices élémentaires à 12x10 points et à 8x10 points respectivement dans des systèmes de vidéographie à matrices et à alphabets dynamiquement redéfinissables.

- 5 Des systèmes de vidéographie à matrices ou à graphisme alphamosaïque connus sont, par exemple, les systèmes français Télétel et Antiope ou les systèmes britanniques Prestel et Ceefax. Par opposition, le système canadien Télidon est un système à graphisme alphagéométrique qui n'est pas concerné par la présente invention.

- 10 Des systèmes de vidéographie à matrices et à alphabets dynamiquement redéfinissables sont connus. A titre d'exemple, un tel système est décrit dans le brevet français 2 419 623. Dans le générateur de caractères des terminaux de ces systèmes, une mémoire vive de formes de caractères est associée aux mémoires mortes habituelles et

- 15 peut recevoir des formes particulières de caractères qui lui sont couramment transmises par le canal de transmission des informations de vidéographie, ces formes particulières de caractères complétant les jeux de formes existant déjà dans les mémoires mortes. Dans la terminologie anglo-saxonne, de tels systèmes sont appelés systèmes

DRCS (Dynamically redefinable character set). Il existe actuellement deux types de structures DRCS: dans l'une, les matrices élémentaires comportent 8x10 points et, dans l'autre, 12x10 points. D'une manière générale, en ce qui concerne les systèmes DRCS, on pourra se reporter à l'article de O. Lambert et autres, paru dans la revue IEEE Transactions on Consumer Electronics, Vol. CE 26, août 1980, pages 600 à 604, et intitulé ANTIOPE AND D.R.C.S.

Des efforts sont actuellement faits pour définir un procédé permettant de rendre compatibles les deux structures DRCS, avec un minimum de distorsions. A la réunion du CEPT pour la vidéographie, tenue du 25 au 27 mars 1981 à Darmstadt, un projet de transcodage d'origine suédoise, intitulé "Common coding schemes for 8 and 12 dot DRCS" a été proposé. Son utilisation semble entraîner des déformations importantes des formes originelles.

15 Un objet de la présente invention consiste à prévoir un système de transcodage qui apporte de faibles distorsions et qui peut être mis en oeuvre par des moyens simples ne grévant pas sensiblement le coût du terminal.

Suivant une caractéristique de la présente invention, il est 20 prévu un système de transcodage d'une matrice 12x10 points en matrice 8x10 points, dans lequel la conversion comporte deux phases, une première phase dans laquelle les pixels de chaque ligne sont groupés par trois dans l'ordre naturel et dans laquelle chaque groupe de trois pixels est traité logiquement pour obtenir un groupe de deux 25 pixels transformés, une seconde phase dans laquelle la configuration de l'ensemble initial des quatre pixels qui est à cheval sur la limite entre deux groupes est examiné de manière que, quand cet ensemble est différent de 0110, l'ensemble transformé formé des deux pixels transformés de la première phase, qui sont de part et d'autre 30 de la limite, est conservé et que, dans le cas contraire, la configuration de l'ensemble initial correspondant de la ligne antérieure est examiné et:

- s'il est trouvé égal à 0110, les pixels de l'ensemble transformé sont remplacés par les pixels correspondants, définitivement transformés de la ligne précédente,

- s'il n'est ni égal à 0110, ni à 0000, les pixels de l'ensemble transformé sont remplacés par des pixels calculés

dans la seconde phase à partir des pixels initiaux, voisins de la ligne courante et de la ligne antérieure,

- s'il est trouvé égal à 0000, l'ensemble initial correspondant de la ligne postérieure est examiné et:

- 5 - s'il est trouvé égal à 0000 ou à 0110, les pixels de l'ensemble transformé sont remplacés par 1 et 1,

- s'il est trouvé différent de 0000 et de 0110, les pixels de l'ensemble transformé sont remplacés par des pixels calculés dans la seconde phase.

10 Suivant une autre caractéristique, dans la première phase, le traitement logique d'un groupe de trois pixels initiaux a, b, c, produit un groupe de pixels transformés  $\hat{a}$ ,  $\hat{b}$ , suivant les formules logiques suivantes:

$$\begin{aligned} \hat{a} &= a + (\bar{b}_{-1} \cdot a_{-1} + \bar{c}_{-1} \cdot b_{-1}) \cdot \bar{a} \cdot b \cdot \bar{c} \\ 15 \quad \hat{b} &= c + (c_{-1} \cdot b_{-1} + \bar{b}_{-1} \cdot \bar{a}_{-1}) \cdot \bar{a} \cdot b \cdot \bar{c} \end{aligned}$$

Suivant une autre caractéristique, les pixels  $\hat{b}$  et  $\hat{a}'$ , calculés dans la seconde phase, sont définis, soit par les deux équations logiques suivantes:

$$\begin{aligned} 20 \quad \hat{b} \cdot \bar{a}' &= a'_{-1} \cdot b'_{-1} \cdot (a_{-1} \cdot b_{-1} \cdot c_{-1} \cdot \bar{c}'_{-1} + \bar{b}_{-1} \cdot c_{-1} + b_{-1} \cdot \bar{c}_{-1}) + \\ &\quad a'_{-1} \cdot \bar{b}'_{-1} \cdot (c_{-1} \cdot c' + b_{-1} \cdot \bar{c}_{-1}) + \bar{b}_{-1} \cdot \bar{c}_{-1} \cdot a'_{-1} \cdot \bar{a} \quad (I) \end{aligned}$$

et

$$\begin{aligned} \hat{b} \cdot \bar{a}' &= b_{-1} \cdot c_{-1} \cdot (\bar{a}_{-1} \cdot a'_{-1} \cdot b'_{-1} \cdot c'_{-1} + a'_{-1} \cdot \bar{b}'_{-1} + \bar{a}'_{-1} \cdot b'_{-1}) + \\ &\quad \bar{b}_{-1} \cdot \bar{c}_{-1} \cdot (a'_{-1} \cdot a + \bar{a}'_{-1} \cdot b'_{-1}) + c_{-1} \cdot \bar{a}'_{-1} \cdot \bar{b}'_{-1} \cdot \bar{c}' \quad (II) \end{aligned}$$

soit par les deux équations logiques équivalentes (I') et (II') où - 25 est remplacé par +.

Suivant une autre caractéristique, il est prévu un circuit de conversion fonctionnant suivant le système de l'invention et comprenant une entrée de signaux numériques de matrice 12x10 reliée à l'entrée d'un jeu de trois registres amont à décalage à douze cellules, montés en série, les sorties des premier et second registres amont étant reliées aux entrées correspondantes d'un circuit de calcul de première phase, une sortie de signal numérique de matrice 8x10 reliée à la sortie d'un jeu de trois registres aval à huit étages, montés en série, les sorties du circuit de calcul de première phase étant reliées aux entrées parallèles du premier registre aval, les sorties parallèles du second registre amont étant reliées à des entrées correspondantes d'un circuit de traitement de seconde phase, les sorties parallèles du premier et du troisième registres amont

étant reliées par un circuit inverseur à des entrées correspondantes du circuit de traitement de seconde phase, les sorties parallèles, sauf la première et la dernière, du troisième registre aval étant reliées à des entrées correspondantes du circuit de traitement de seconde phase, les sorties du circuit de traitement de seconde phase étant reliées aux entrées parallèles, sauf la première et la dernière, du second registre aval, et une base de temps commandant les fonctionnements des circuits de calcul de première phase et de traitement de seconde phase et l'avancement dans les registres.

Les caractéristiques mentionnées ci-dessus, ainsi que d'autres, apparaîtront plus clairement à la lecture de la description suivante d'un exemple de réalisation, ladite description étant faite en relation avec les dessins joints, parmi lesquels:

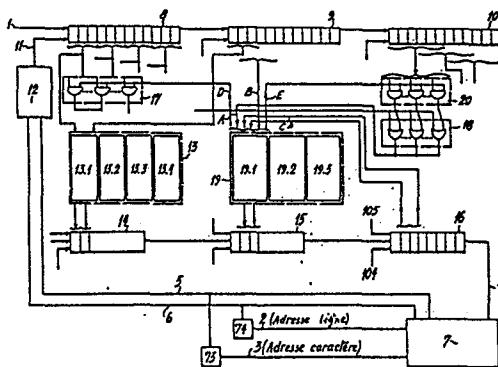

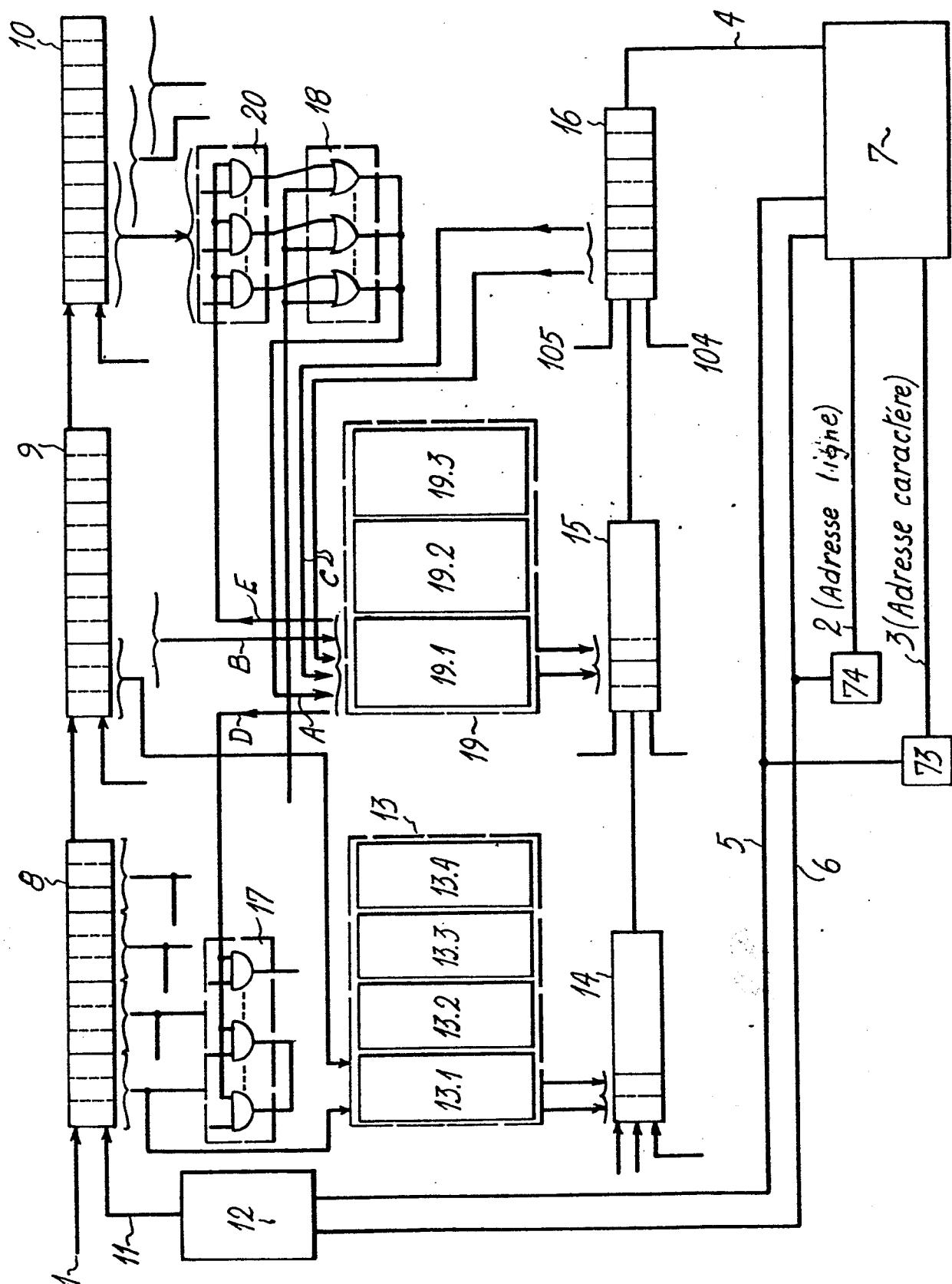

la Fig. 1 est un bloc-diagramme schématique d'un circuit de conversion suivant l'invention,

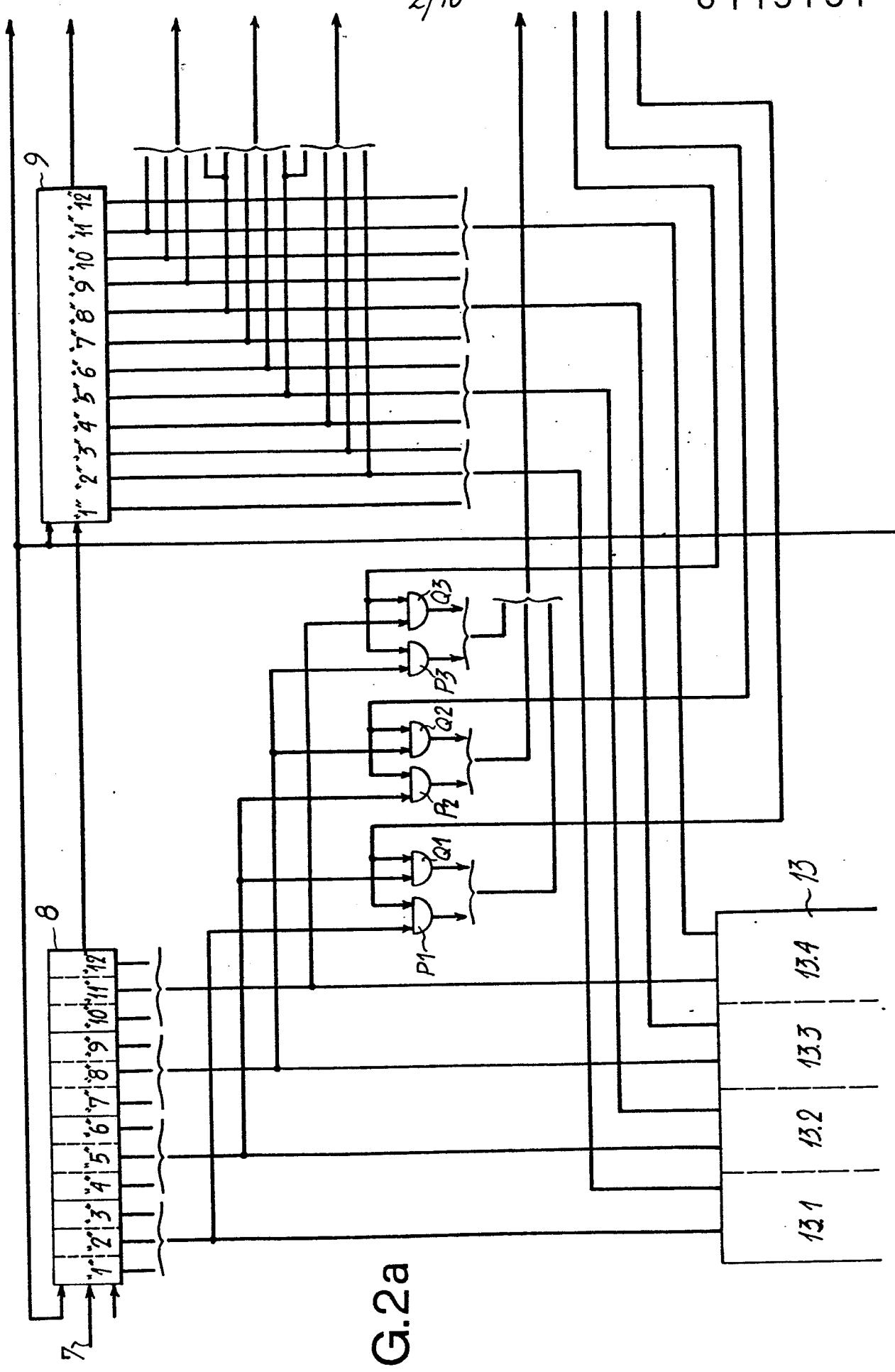

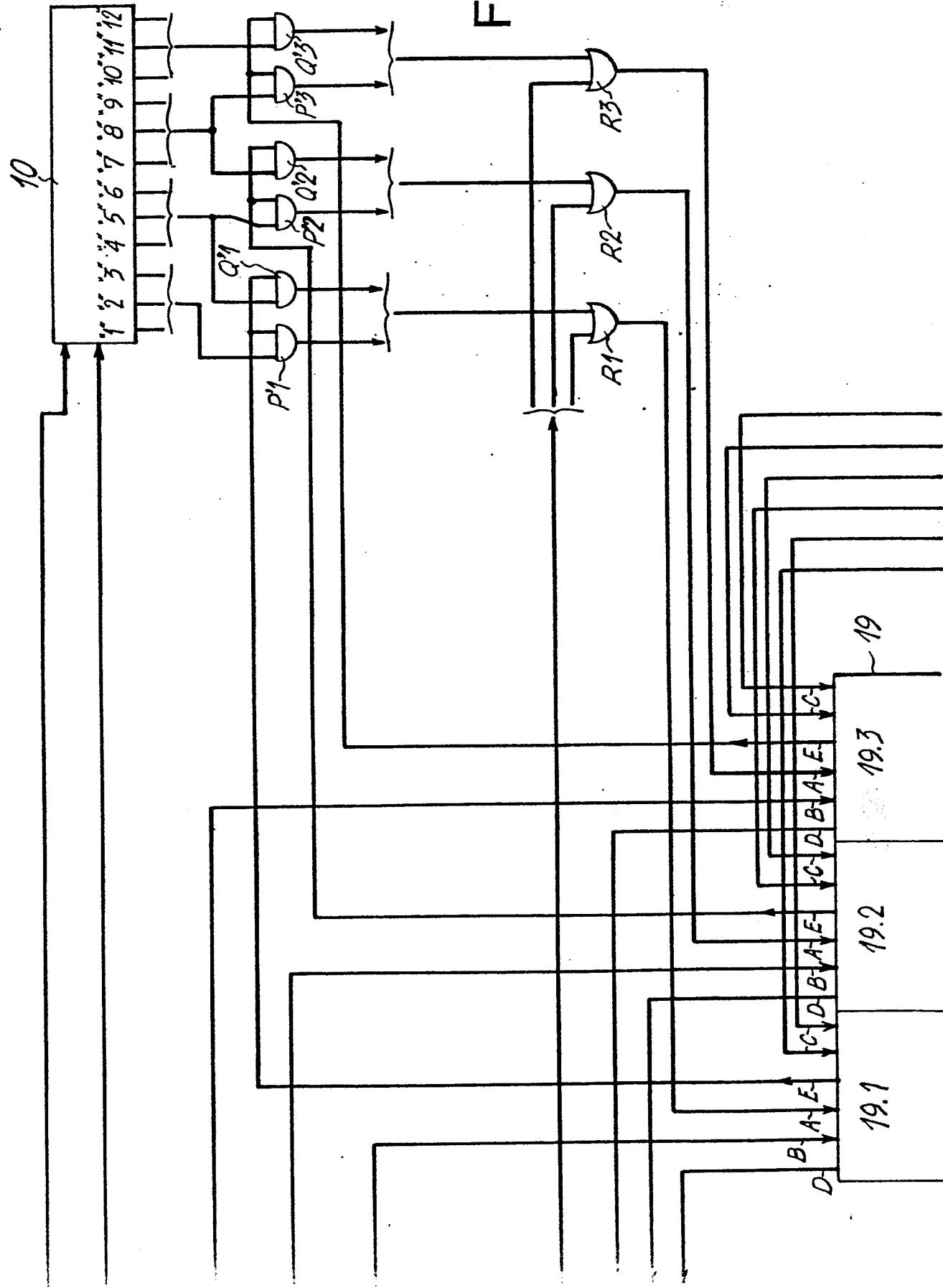

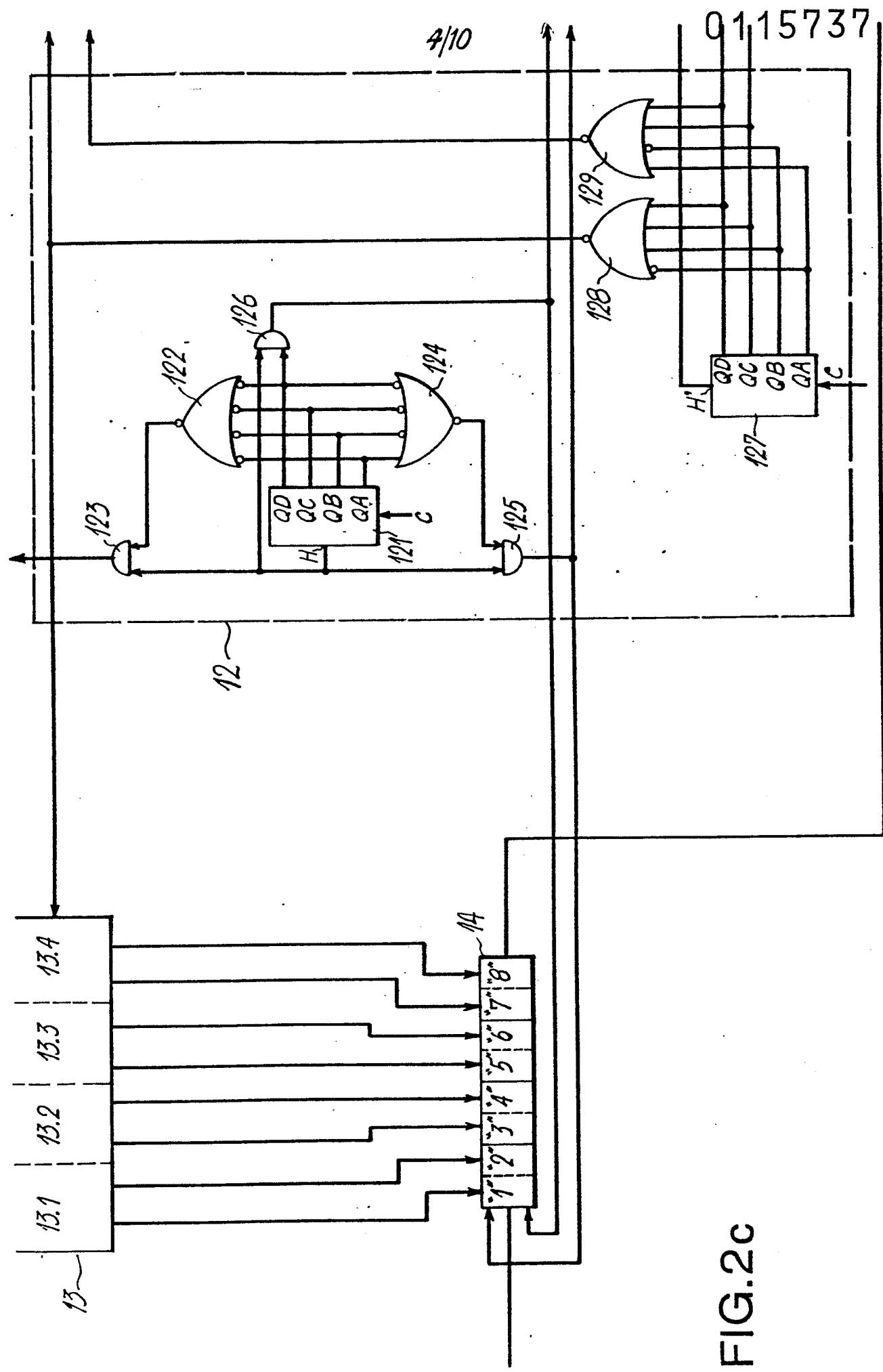

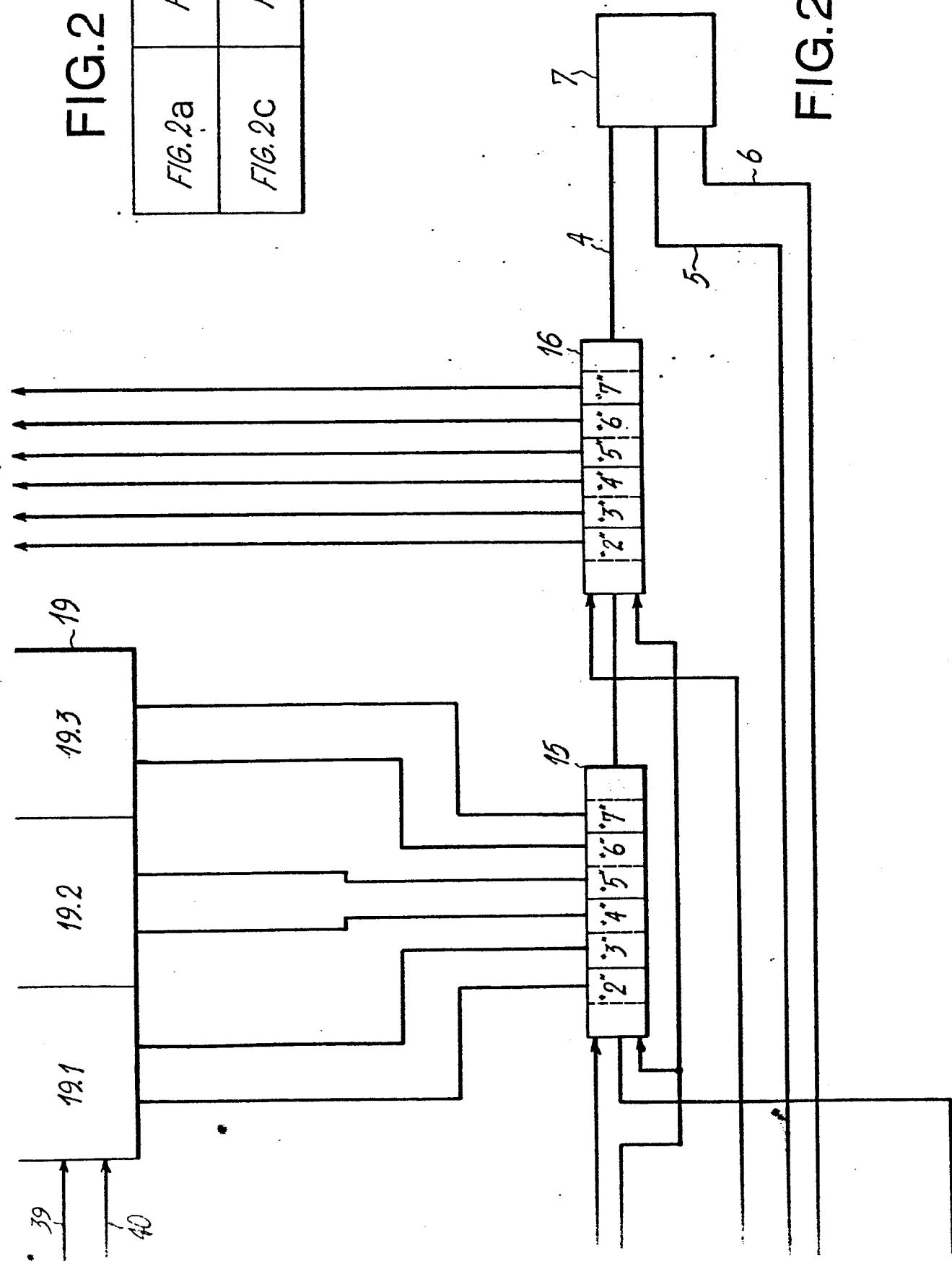

les Figs. 2a à 2d, assemblées comme l'indique la Fig. 2, sont des bloc-diagrammes des différentes parties du circuit de la Fig. 1,

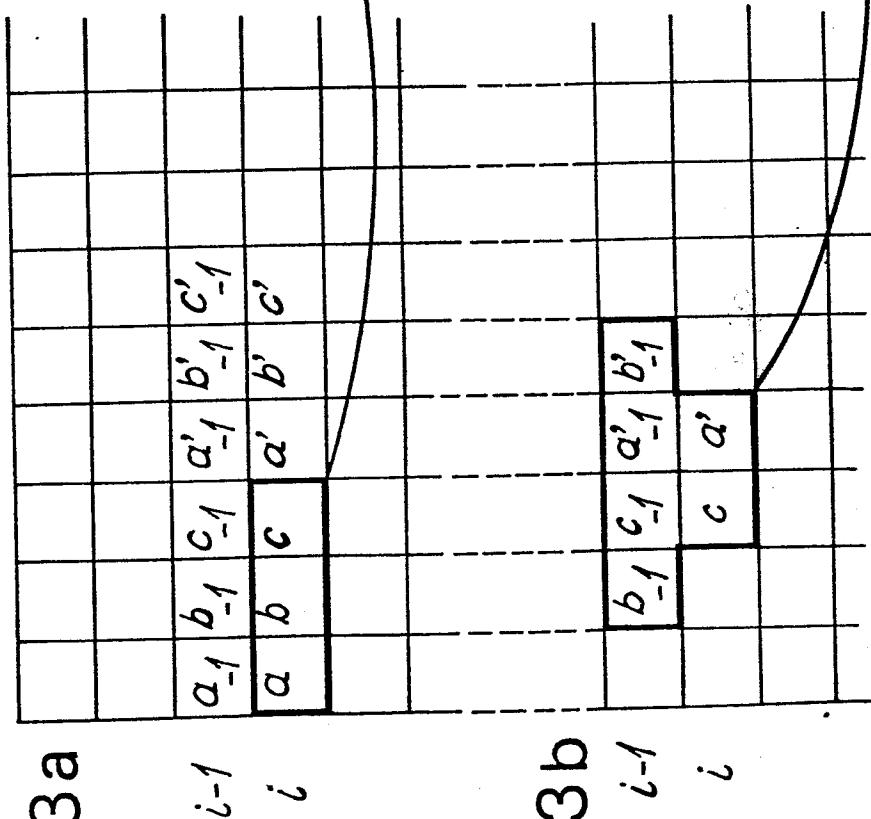

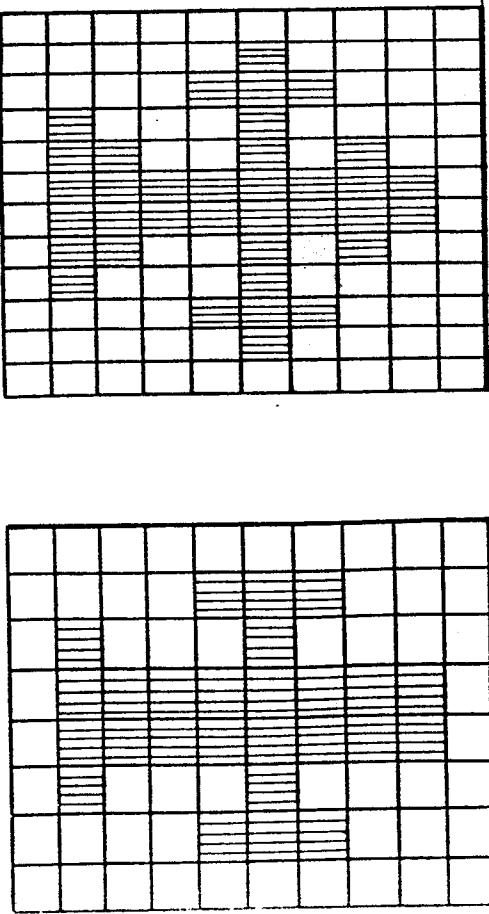

les Figs. 3a et 3b sont des diagrammes illustrant le fonctionnement du circuit des Figs. 1 et 2,

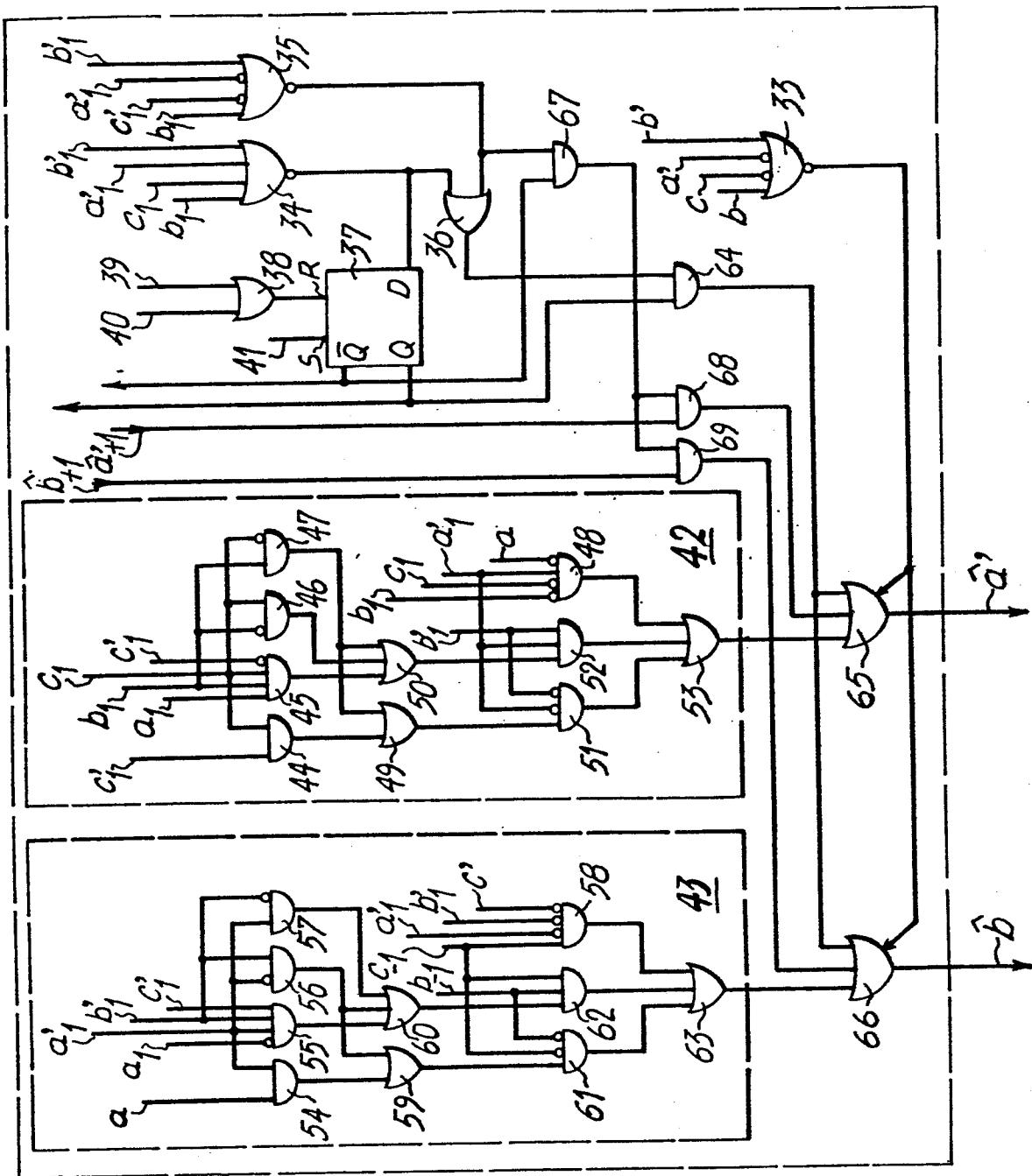

la Fig. 4 est le schéma du circuit de calcul de première phase,

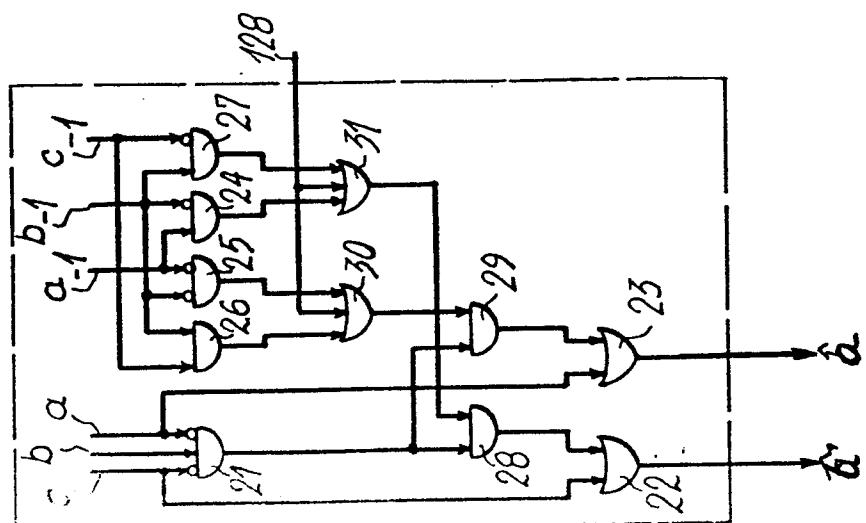

la Fig. 5 est le schéma du circuit de traitement de seconde phase,

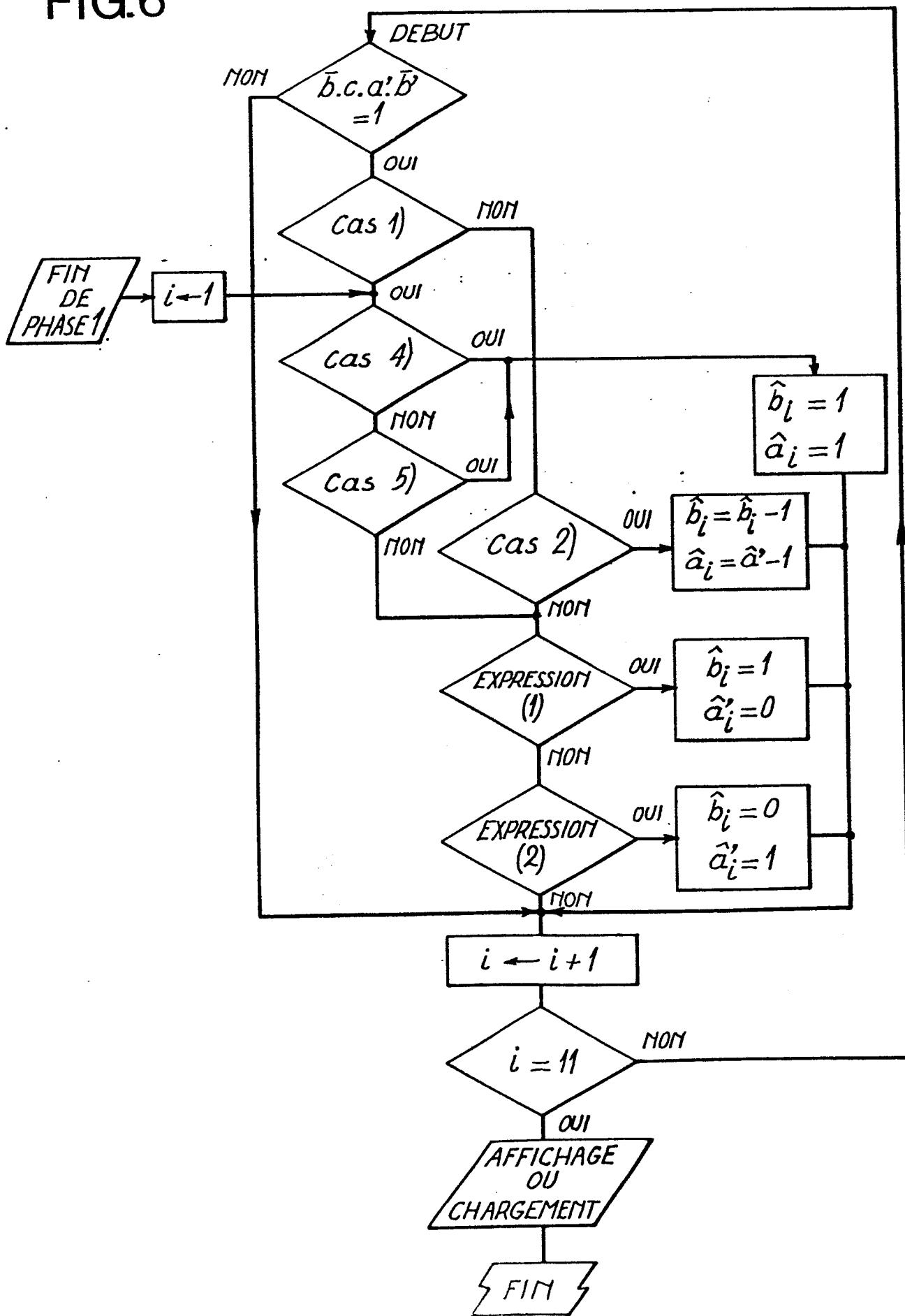

la Fig. 6 est un organigramme illustrant le fonctionnement du circuit de traitement de la Fig. 5,

la Fig. 7 représentent des formes d'onde des signaux de sortie de la base de temps, montrée aux Figs. 1 et 2,

la Fig. 8 est un exemple de conversion de matrice 12x10 en matrice 8x10, et

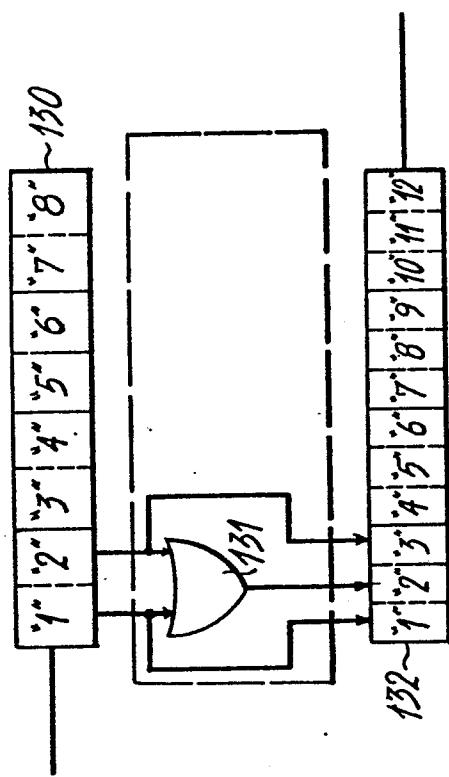

la Fig. 9 est un schéma de conversion de matrice 8x10 en matrice 12x10.

On rappelle que pour écrire, la nouvelle forme d'un caractère dans une mémoire vive, il faut trois données: la première concerne l'adresse de la matrice unitaire dans la mémoire, la seconde l'adresse de la ligne dans la matrice et la troisième les bits constituant la ligne. Dans le brevet 2 419 623, ces trois données sont transmises sur trois fils 83, 84 et 85, Fig. 7, vers la mémoire vive 37, les trois fils 83 à 85 constituant la liaison 80. Le circuit de transcodage

0115737

ge, suivant l'invention, utilisé avec le système de télétexthe du brevet 2 419 623, trouve sa place, monté en série dans la liaison 80.

La Fig. 1 est un bloc-diagramme relativement simplifié montrant l'ensemble du convertisseur 12/8.

5 Les fils d'entrées du circuit de transcodage de la Fig. 1 comprennent les fils 1, 2 et 3 correspondant respectivement aux fils 85, 84 et 83 mentionnés plus haut, et les fils de sortie 4, 5, et 6 reliés à une mémoire vive de caractère 7, correspondant à 37.

Le fil 3 est relié à l'entrée d'un registre à décalage 73 qui 10 est destiné à retarder l'adresse caractère d'un temps équivalent au traitement des trois premières lignes du caractère. La synchronisation du registre 73 est effectuée par le signal présenté sur le fil 5 provenant de la logique de commande 12.

Le fil 2 est relié à l'entrée d'un registre à décalage 72 qui 15 est destiné à retarder chaque adresse ligne reçue d'un temps de traitement équivalent au temps de traitement de trois lignes de caractère. La synchronisation du registre 72 est effectuée par le signal présenté sur le fil 6 provenant de la logique de commande 12.

Le fil 1 est relié à l'entrée de données d'un registre à 20 décalage 8 dont la sortie série est reliée à l'entrée de données d'un registre à décalage 9. La sortie série du registre à décalage 9 est reliée à l'entrée de données d'un registre à décalage 10. Les trois registres à décalage 8, 9 et 10 comportent chacun douze étages et peuvent donc emmagasiner chacun une ligne de matrice. Leurs entrées 25 d'horloge sont reliées à la sortie 11 d'un circuit d'horloge 12. En pratique, les registres 8 à 10 peuvent être des circuits du type commercialisé sous la référence DM 74 195.

Le registre 8 a ses sorties parallèles "1", "2" et "3" reliées aux entrées correspondantes d'un premier circuit de traitement logique 13.1, ses sorties parallèles "4", "5" et "6" reliées aux entrées correspondantes d'un second circuit de traitement logique 13.2, ses sorties "7", "8" et "9" reliées aux entrées correspondantes d'un troisième circuit de traitement logique 13.3, et ses sorties parallèles "10", "11" et "12" reliées aux entrées correspondantes d'un 35 quatrième circuit de traitement logique 13.4. L'ensemble des circuits 13.1, 13.2, 13.3 et 13.4, qui sont identiques, forme un circuit de

conversion 13 qui convertit des tranches de trois pixels en tranches de deux pixels.

D'une manière analogue, le registre 9 a ses sorties parallèles "1", "2" et "3" reliées à des entrées correspondantes du circuit 13.1, ses sorties parallèles "4", "5" et "6" reliées à des entrées correspondantes du circuit 13.2, ses sorties parallèles "7", "8" et "9" reliées à des entrées correspondantes du circuit 13.3, et ses sorties parallèles "10", "11" et "12" reliées à des entrées correspondantes du circuit 13.4.

Le circuit 13.1 a deux sorties qui sont respectivement reliées aux entrées parallèles "1" et "2" d'un registre à décalage 14 à huit étages; le circuit 13.2 a deux sorties respectivement reliées aux entrées parallèles "3" et "4" du registre 14; le circuit 13.3 a deux sorties reliées respectivement aux entrées parallèles "5" et "6" du registre 14; et le circuit 13.4 a deux sorties respectivement reliées aux entrées "7" et "8" du registre 14. La sortie série du registre 14 est reliée à l'entrée d'un registre à décalage 15 à huit étages. La sortie série du registre 15 est reliée à l'entrée série d'un autre registre à décalage 16 à huit étages dont la sortie est reliée au fil 4.

Le registre 8 a encore ses sorties parallèles "1" à "3" reliées respectivement aux premières entrées de trois portes ET P1; ses sorties parallèles "4" à "6" reliées respectivement, d'une part, aux premières entrées de trois portes ET Q1 et, d'autre part, aux 25 premières entrées de trois portes ET P2; ses trois sorties parallèles "7" à "9" reliées respectivement, d'une part, aux premières entrées de trois portes ET Q2 et, d'autre part, aux premières entrées de trois portes ET P3; et, enfin, ses trois sorties parallèles "10" à "12" reliées aux premières entrées de trois portes ET Q3. L'ensemble 30 des portes ET P1 à P3 et Q1 à Q3 forment un commutateur 17.

Les sorties des portes ET P1 et Q1 sont respectivement reliées aux premières entrées de six portes OU R1; les sorties des portes ET P2 et Q2 sont respectivement reliées aux premières entrées de six portes OU R2, et les sorties des portes ET P3 et Q3 sont respectivement reliées aux premières entrées de six portes OU R3. Les portes OU R1 à R3 forment le circuit de liaison 18. Les sorties des six portes OU R1 sont reliées aux entrées correspondantes A1 à A6 d'un circuit

de traitement logique 19.1; les sorties des six portes OU R2 sont reliées aux entrées correspondantes A d'un circuit de traitement logique 19.2, et les sorties des six portes OU R3 sont reliées aux entrées correspondantes A d'un troisième circuit de traitement logique 19.3. Les circuits 19.1 à 19.3, qui sont identiques, forment le circuit de traitement 19.

Le circuit 19.1 a deux sorties qui sont respectivement reliées aux entrées parallèles "2" et "3" du registre 15; le circuit 19.2 a deux sorties qui sont respectivement reliées aux entrées "4" et "5" du registre 15; et le circuit 19.3 a deux sorties qui sont respectivement reliées aux entrées "6" et "7" du registre 15.

Par ailleurs, le circuit 19.1 a des entrées B qui sont respectivement reliées aux sorties parallèles "2", "3", "4" et "5" du registre 9; le circuit 19.2 a des entrées B qui sont respectivement reliées aux sorties parallèles "5", "6", "7" et "8" du registre 9; et le circuit 19.3 a des entrées B qui sont respectivement reliées aux sorties "8", "9", "10" et "11" du registre 9.

Le circuit 19.1 a encore des entrées C qui sont respectivement reliées aux sorties parallèles "2" et "3" du registre 16; le circuit 19.2 a des entrées C qui sont respectivement reliées aux sorties parallèles "4" et "5" du registre 16; et le circuit 19.3 a des entrées C qui sont respectivement reliées aux sorties parallèles "6" et "7" du registre 16.

Enfin, le circuit 19.1 a une sortie D reliée aux secondes entrées des portes P1 et Q1; le circuit 19.2 a une sortie D reliée aux secondes entrées des portes ET P2 et Q2; et le circuit 19.3 a une sortie D reliée aux secondes entrées des portes ET P3 et Q3.

Le registre 10 a ses sorties parallèles "1" à "3" reliées respectivement aux premières entrées de trois portes ET P'1; ses sorties parallèles "4" à "6" reliées respectivement, d'une part, aux premières entrées de trois portes ET Q'1 et, d'autre part, aux premières entrées de trois portes ET P'2; ses trois sorties parallèles "7" à "9" reliées respectivement, d'une part, aux premières entrées de trois portes ET Q'2 et, d'autre part, aux premières entrées de trois portes ET P'3; et, enfin, ses trois sorties parallèles "10" à "12" reliées aux premières entrées de trois portes ET Q3. L'ensemble des portes ET P'1 à P'3 et Q'1 à Q'3 forment un commutateur

teur 20.

Les sorties des portes ET P'1 et Q'1 sont respectivement reliées aux secondes entrées des six portes OU R1; les sorties des portes ET P'2 et Q'2 sont respectivement reliées aux secondes entrées 5 des six portes OU R2, et les sorties des portes ET P'3 et Q'3 sont respectivement reliées aux secondes entrées des six portes OU R3.

Le circuit 19.1 a une sortie E reliée aux secondes entrées des portes P'1 et Q'1; le circuit 19.2 a une sortie E reliée aux secondes entrées des portes ET P'2 et Q'2; et le circuit 19.3 a une sortie E 10 reliée aux secondes entrées des portes ET P'3 et Q'3.

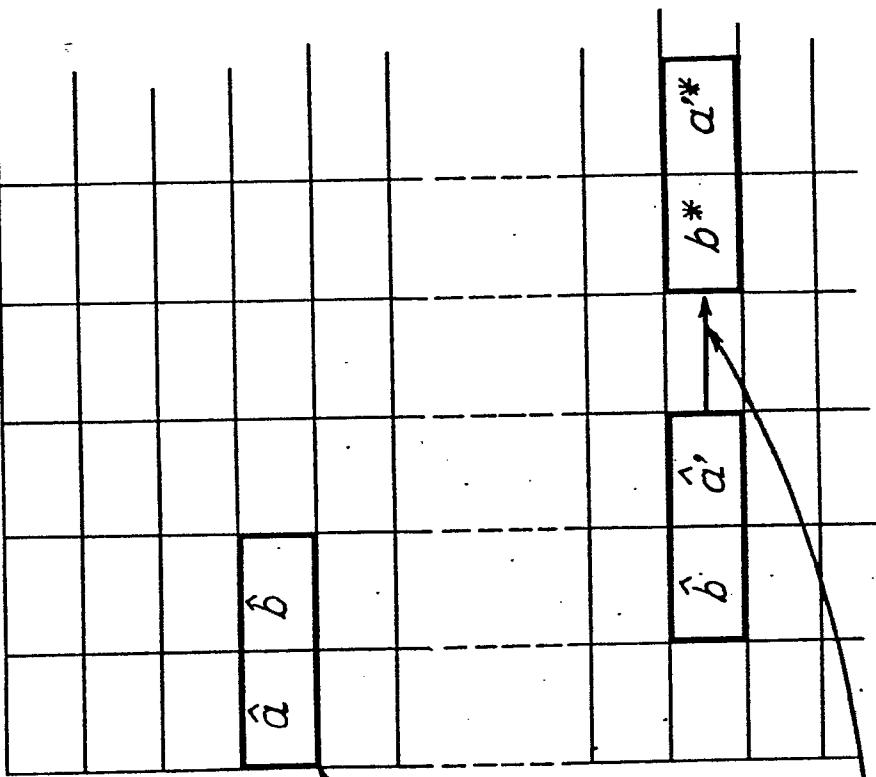

Avant de décrire en détail le circuit de traitement logique 13.1, Fig. 4, et le circuit de traitement logique 19.1, Fig. 5, on va considérer les diagrammes des Figs. 3a et 3b. Dans le diagramme de la Fig. 3a, on a représenté à gauche, en regardant le dessin, une portion de matrice 12x10 et, à droite, la portion transformée de matrice 8x10, après passage dans le circuit 13.1. Cette transformation sera, dans la suite, désignée par première phase ou phase 1. On notera que, dans cette phase, les douze pixels d'une ligne i sont groupés en quatre groupes de trois pixels: a, b, c; a', b', c'; a'', b'', etc. Chaque groupe de trois pixels est transformé en un groupe de deux pixels dans la matrice 8x10. Chaque ligne de la matrice 8x10 comprend quatre groupes de pixels transformés:  $\hat{a}$ ,  $\hat{b}$ ;  $\hat{a}'$ ,  $\hat{b}'$ ;  $\hat{a}''$ , etc. Plus particulièrement, pour la matrice 12x10, on a représenté, à la ligne i, un premier groupe de trois pixels a, b, c, suivi d'un second 20 groupe de trois pixels a', b', c', et, à la ligne (i-1), le premier groupe correspondant de trois pixels  $a_{-1}$ ,  $b_{-1}$ ,  $c_{-1}$ , suivi du second groupe correspondant de trois pixels  $a'_{-1}$ ,  $b'_{-1}$ ,  $c'_{-1}$ . Il leur correspond, dans la matrice 8x10, à la ligne i, le premier groupe de deux pixels  $\hat{a}$ ,  $\hat{b}$ , suivi du second groupe de deux pixels  $\hat{a}'$ ,  $\hat{b}'$ .

30 La Fig. 4 représente en détail le schéma logique du circuit de traitement logique 13.1 qui calcule les pixels  $\hat{a}$  et  $\hat{b}$  en fonction des pixels a, b, c,  $a_{-1}$ ,  $b_{-1}$  et  $c_{-1}$ , suivant les équations logiques suivantes:

$$\begin{aligned}\hat{a} &= a + (\bar{b}_{-1} \cdot a_{-1} + \bar{c}_{-1} \cdot b_{-1}) \cdot \bar{a} \cdot b \cdot \bar{c} \\ 35 \quad \hat{b} &= c + (c_{-1} \cdot b_{-1} + \bar{b}_{-1} \cdot \bar{a}_{-1}) \cdot \bar{a} \cdot b \cdot \bar{c}\end{aligned}$$

Dans le circuit 13.1, les références numériques des entrées

sont celles des données des pixels auxquelles elles correspondent. L'entrée a est reliée, d'une part, à l'entrée inverseuse d'une porte ET 21 et, d'autre part, à l'entrée d'une porte OU 22. L'entrée b est reliée à l'entrée non inverseuse de la porte ET 21. L'entrée c est 5 reliée, d'une part, à l'autre entrée inverseuse de la porte ET 21 et, d'autre part, à une entrée d'une porte OU 23. L'entrée  $a_{-1}$  est reliée, d'une part, à une entrée directe d'une porte ET 24 et, d'autre part, à une entrée inverseuse d'une porte ET 25. L'entrée  $b_{-1}$  est reliée, d'une part, à des entrées inverseuses des portes 24 et 25 10 et, d'autre part, à des entrées directes de portes ET 26 et 27. L'entrée  $c_{-1}$  est reliée, d'une part, à une entrée directe de la porte ET 26 et, d'autre part, à une entrée inverseuse de la porte ET 27.

La sortie de la porte ET 21 est reliée aux premières entrées de deux portes ET 28 et 29. Les sorties des portes ET 25 et 26 sont 15 respectivement reliées à deux entrées d'une porte OU 30 à trois entrées. Les sorties des portes ET 24 et 27 sont respectivement reliées à deux entrées d'une porte OU 31 à trois entrées. Les sorties des portes OU 30 et 31 sont respectivement reliées aux secondes entrées des portes ET 29 et 28. Les sorties des portes ET 28 et 29 20 sont respectivement reliées aux secondes entrées des portes OU 22 et 23. Les troisièmes entrées des portes OU 30 et 31 sont reliées à l'entrée d'activation 32. Les sorties des portes OU 22 et 23 délivrent respectivement les pixels  $\hat{a}$  et  $\hat{b}$  qui sont transmis par les fils de sortie de 13.1 vers les entrées "1" et "2" du registre 14.

25 Bien entendu, le circuit 13.2 calcule les pixels  $\hat{a}'$  et  $\hat{b}'$  à partir des seconds groupes de trois pixels des lignes i et (i-1), etc.

Dans le diagramme de la Fig. 3b, on a représenté, à gauche, une portion de matrice 12x10 et, à droite, la portion transformée de matrice 8x10, après première phase et la portion transformée après 30 deuxième phase. En pratique, la deuxième phase est utile pour réduire aux frontières entre les groupes de deux pixels les épaisseurs des traits.

Dans la matrice 12x10, Fig. 3b, on considère la fenêtre d'observation comportant, ligne i, les pixels c et  $a'$ , et, ligne (i-1), les 35 pixels  $b_{-1}$ ,  $c_{-1}$ ,  $a'_{-1}$ ,  $b'_{-1}$ . Les pixels de cette fenêtre servent, dans certains cas, que l'on définira ci-dessous, à éventuellement

modifier les pixels  $b$  et  $\hat{a}'$  résultant des traitements dans les circuits 13.1 et 13.2 pour obtenir les pixels définitifs  $b^*$  et  $a'^*$  résultant du traitement dans le circuit 19.1.

Le traitement dans le circuit 19.1 n'est déclenché que pour une configuration des pixels  $b$ ,  $c$ ,  $a'$ ,  $b'$  égale à 0110. Dans ce cas, le circuit 19.1, Fig. 5, permet de prendre en compte des pixels de la ligne  $(i-1)$ , et éventuellement des pixels de la ligne  $(i+1)$ , ou de la ligne  $(i+1)$ , pour définir les pixels transformés  $\hat{b}$  et  $\hat{a}'$  de la ligne  $i$ . Dans toutes les autres configurations des pixels  $b$ ,  $c$ ,  $a'$ ,  $b'$ , les pixels transformés  $\hat{b}$  et  $\hat{a}'$  sont ceux qui ont été calculés par les circuits 13.1 et 13.2.

Dans le cas,  $(b, c, a', b') = 0110$ , plusieurs circonstances peuvent se présenter:

$$1) b_{-1}, c_{-1}, a'_{-1}, b'_{-1} = 0000$$

15

$$2) b_{-1}, c_{-1}, a'_{-1}, b'_{-1} = 0110$$

3) la ligne  $i$  est la première ligne d'une matrice,

20

$$4) b_{+1}, c_{+1}, a'_{+1}, b'_{+1} = 0000$$

$$5) b_{+1}, c_{+1}, a'_{+1}, b'_{+1} = 0110$$

6) les cas différents des cas 1) à 5).

25

Dans le cas 6), les pixels transformés  $\hat{b}$  et  $\hat{a}'$  sont définis, soit par les deux équations logiques suivantes:

$$\begin{aligned} \hat{b} \cdot \hat{a}' &= a'_{-1} \cdot b'_{-1} \cdot (a_{-1} \cdot b_{-1} \cdot c_{-1} \cdot \bar{c}'_{-1} + \bar{b}_{-1} \cdot c_{-1} + b_{-1} \cdot c_{-1}) + \\ &\quad a'_{-1} \cdot \bar{b}'_{-1} \cdot (c_{-1} \cdot c' + b_{-1} \cdot \bar{c}_{-1}) + \bar{b}_{-1} \cdot \bar{c}_{-1} \cdot a'_{-1} \cdot \bar{a} \quad (\text{I}) \end{aligned}$$

30 et

$$\begin{aligned} \bar{\hat{b}} \cdot \hat{a}' &= b_{-1} \cdot c_{-1} \cdot (a_{-1} \cdot a'_{-1} \cdot b'_{-1} \cdot c'_{-1} + a'_{-1} \cdot \bar{b}'_{-1} + \bar{a}'_{-1} \cdot b'_{-1}) + \\ &\quad \bar{b}_{-1} \cdot \bar{c}_{-1} \cdot (a'_{-1} \cdot a + \bar{a}'_{-1} \cdot b'_{-1}) + c_{-1} \cdot \bar{a}'_{-1} \cdot \bar{b}'_{-1} \cdot \bar{c}' \quad (\text{II}) \end{aligned}$$

soit par les deux équations logiques équivalentes (I') et (II') où  $-$  est remplacé par  $+$ .

35

Les entrées de données du circuit 19.1 sont l'entrée A à six fils permettant de recevoir les données des pixels  $a_{-1}$ ,  $b_{-1}$ ,  $c_{-1}$ ,

0115737

$a'_{-1}, b'_{-1}, c'_{-1}$ , quand le fil E est activé, ou les données des pixels  $a_{+1}, b_{+1}, c_{+1}, a'_{+1}, b'_{+1}, c'_{+1}$ , quand le fil D est activé; l'entrée B à quatre fils permettant de recevoir les données des pixels b, c, a', b'; et l'entrée C permettant de recevoir les données 5 des pixels  $b^*_{+1}, a^*_{+1}$ .

Dans le circuit 19.1, une porte NI 33 a ses entrées directes reliées aux entrées b et b' et ses entrées inverseuses aux entrées c et a'. La porte 33 permet de détecter la configuration 0110, mentionnée plus haut, dans la ligne i.

10 Une porte NI 34 a ses quatre entrées directes reliées aux fils  $b_1, c_1, a'_1$  et  $b'_1$ . La porte 34 sert à détecter le cas 1) ou le cas 4), mentionnés ci-dessus.

Une porte NI 35 a ses deux entrées reliées aux fils  $b_1$  et  $b'_1$ , et ses entrées inverseuses aux fils  $c_1$  et  $a'_1$ . La porte 35 sert à 15 détecter le cas 2) ou le cas 5), mentionnés ci-dessus.

Les sorties des portes 34 et 35 sont respectivement reliées aux deux entrées d'une porte OU 36 dont la sortie est reliée à une entrée d'une porte ET 64. La sortie de la porte 34 est encore reliée à l'entrée D d'une bascule 37 qui a une entrée R de remise à zéro 20 reliée à la sortie d'une porte OU 38 dont une entrée est reliée à l'entrée de commande 39 et l'autre entrée à l'entrée de commande 40, une entrée S de mise à un reliée à l'entrée de commande 41, une sortie Q reliée au fil de sortie D et une sortie  $\bar{Q}$  reliée au fil de sortie E.

25 Le circuit 19.1 comprend encore deux circuits de calculs 42 et 43 effectuant respectivement les deux calculs logiques mentionnés ci-dessus.

Dans le circuit 42, une porte ET 44 a ses deux entrées directes reliées aux fils  $c'$  et  $c_1$ ; une porte ET 45 a trois entrées directes 30 reliées aux fils  $a_1, b_1, c_1$  et une entrée inverseuse reliée au fil  $c'_1$ ; une porte ET 46 a une entrée directe reliée au fil  $c_1$  et une entrée inverseuse reliée au fil  $b_1$ ; une porte 47 a une entrée directe reliée au fil  $b_1$  et une entrée inverseuse reliée au fil  $c_1$ ; une porte ET 48 a une entrée directe reliée au fil  $a'_1$  et trois entrées 35 inverseuses reliées aux fils  $b_1, c_1$  et a. On notera que ci-dessus on n'a pas précisé le signe de l'indice 1, car il est négatif ou positif

selon l'état de la bascule 37.

Les sorties des portes ET 44 et 47 sont reliées aux deux entrées d'une porte OU 49. Les sorties des portes ET 45, 46 et 47 sont reliées aux trois entrées d'une porte OU 50. La sortie de la 5 porte OU 49 est reliée à l'entrée directe d'une porte ET 51 dont les entrées inverseuses sont reliées aux fils  $a'_1$  et  $b'_1$ . La sortie de la porte OU 50 est reliée à une entrée directe d'une porte ET 52 dont les deux autres entrées directes sont reliées aux entrées  $a'_1$  et  $b'_1$ . Les sorties des portes ET 48, 51 et 52 sont reliées à trois entrées 10 d'une porte OU 53 dont la 4<sup>e</sup> entrée est reliée à la sortie de la porte ET 67.

Dans le circuit 43, une porte ET 54 a ses deux entrées directes reliées aux fils  $a$  et  $a'_1$ ; une porte ET 55 a trois entrées directes reliées aux fils  $a'_1$ ,  $b'_1$ ,  $c'_1$  et une entrée inverseuse reliée au fil 15  $a_1$ ; une porte ET 56 a une entrée directe reliée au fil  $a'_1$  et son entrée inverseuse reliée au fil  $b'_1$ ; une porte ET 57 a son entrée directe reliée au fil  $b'_1$  et son entrée inverseuse reliée au fil  $a'_1$ ; et une porte ET 58 a une entrée directe reliée au fil  $c_1$  et trois entrées inverseuses reliées aux fils  $a'_1$ ,  $b'_1$  et  $c'$ .

20 Les sorties des portes ET 54 et 56 sont reliées aux deux entrées d'une porte OU 59. Les sorties des portes ET 55, 56 et 57 sont reliées aux trois entrées d'une porte OU 60. La sortie de la porte OU 59 est reliée à l'entrée directe d'une porte ET 61 dont les entrées inverseuses sont reliées aux fils  $b_1$  et  $c_1$ . La sortie de la 25 porte OU 60 est reliée à une entrée directe d'une porte ET 62 dont les deux autres entrées directes sont reliées aux fils  $b_1$  et  $c_1$ . Les sorties des portes ET 58, 60 et 62 sont reliées à trois entrées d'une porte OU 63, dont la 4<sup>e</sup> entrée est reliée à la sortie de la porte ET 67.

30 La sortie de la porte OU 36 est reliée à une entrée d'une porte ET 64 dont l'autre entrée est reliée à la sortie Q de la bascule 37 et dont la sortie est reliée à la première entrée de deux portes OU 65 et 66. Les portes OU ont chacune une entrée d'activation qui est reliée à la sortie de la porte NI 33.

35 La sortie de la porte NI 35 est encore reliée à une entrée d'une porte ET 67 dont l'autre entrée est reliée à la sortie  $\bar{Q}$  de la

0115737

bascule 37 et dont la sortie est reliée à la première entrée de deux portes ET 68 et 69. Les secondes entrées des portes 68 sont respectivement reliées aux fils  $a^{*+1}$  et  $b^{*+1}$  de l'entrée C et leurs sorties sont respectivement reliées aux premières entrées de portes OU 65 et 66. Les secondes entrées des portes 65 et 66 sont respectivement reliées aux sorties des portes 53 et 63 et leurs troisièmes entrées aux sorties des portes 68 et 69.

Quand la configuration  $bca'b' = 0110$  n'apparaît pas dans une ligne i, les portes OU 65 et 66 sont inhibées si bien que le circuit 19.1 est inopérant. Dans le cas contraire, c'est le circuit 19.1 qui sert à définir les pixels transformés  $\hat{b}$  et  $\hat{a}'$  de la ligne i. Dans l'exemple de réalisation décrit, le circuit 19.1 fonctionne quel que soit l'état de la sortie de 33 qui ne sert qu'à valider les calculs.

A chaque ligne i, avec  $i \neq 1$ , écrite dans le registre 9, la bascule 37 est remise à zéro par 39 ou 40. Donc la sortie  $\bar{Q}$  est à "1" si bien que les signaux entrant dans 19.1 sont ceux qui sont présents dans les registres 9 et 10. Autrement dit, l'indice 1 des entrées de 42 et 43 est égal à -1 et les formules I et II s'appliquent. L'état de la porte 34 indique si on rencontre le cas 1) et celui de la porte 35 si l'on rencontre le cas 2), ou leurs états indiquent que l'on est dans le cas 6). Trois fonctionnements différents peuvent donc être déclenchés:

cas 1: Par 34, l'entrée D de la bascule 37 passe à "1" si bien que sa sortie Q passe à "1". Il en résulte que les signaux entrants sont maintenant ceux des registres 8 et 9. On analyse donc la ligne (i+1) avec la ligne i. Les trois cas 4), 5) ou 6) peuvent se présenter:

cas 4): la sortie de 34 est à "1" et la sortie Q de 37 est à "1", ce qui entraîne la sortie de la porte ET 64 à "1". Donc, les sorties  $\hat{b}$  et  $\hat{a}'$  sont à "1". Les pixels transformés en phase 2 sont  $\hat{b} = \hat{a}' = 1$ .

cas 5: la sortie de 35, donc de 36, est à "1" et la sortie Q de 37 est à "1", ce qui entraîne la sortie de la porte ET 64 à "1". Donc, les sorties  $\hat{b}$  et  $\hat{a}'$  sont à "1". Les pixels transformés en phase 2 sont  $\hat{b} = \hat{a}' = 1$ .

cas 6: les sorties de 34 et de 35 sont à "0". Donc les

portes 66 et 65 laissent passer les pixels calculés par 43 et 42 et les pixels transformés en phase 1 sont modifiés. Les formules I' et II' s'appliquent.

5           cas 2): La sortie de 35 est à "1" et la sortie  $\bar{Q}$  de 37 est à "1". Donc, la sortie de la porte 67 est à "1" ce qui entraîne que les portes ET transmettent les données des pixels  $b_{-1}^*$  et  $a_{-1}^{**}$  qui viennent prendre la place des pixels transformés en phase 1.

10          cas 3: Les pixels de la première ligne à transformer sont écrits dans le registre 9. L'entrée 41 est activée si bien que la sortie Q de la bascule 37 est à "1". Il en résulte que les signaux entrants sont immédiatement ceux des registres 8 et 9. Les trois cas 4), 5) ou 6) peuvent se présenter:

15          cas 4: on retrouve le fonctionnement décrit en relation avec le cas 1) ci-dessus.

cas 5: la sortie de 35 est à "1" et la sortie  $\bar{Q}$  de 37 est à "1", ce qui entraîne la sortie de la porte ET 64 à "1". On retrouve le cas 4) ci-dessus.

20          cas 6: Les sorties de 34 et de 35 sont "0". Donc, on retrouve le cas 6) mentionné ci-dessus.

25          cas 6: on retrouve les fonctionnements déjà vus pour ce cas. Les pixels transformés sont obtenus à partir des calculs logiques effectués dans 42 et 43. Les formules I et II s'appliquent. La base de temps ou commande logique 12 comprend un compteur 121 à quatre étages recevant en C le signal d'horloge bit qu'il délivre aussi en H. Par ailleurs ses sorties QA, QB, QC et QD sont respectivement reliées aux deux premières entrées inverseuses, à la troisième entrée non inverseuse et à la quatrième entrée inverseuse d'une porte NI 122. La sortie de la porte 122 et la sortie H de 121 sont reliées aux entrées d'une porte ET 123 dont la sortie est reliée aux entrées d'horloge des registres 8, 9 et 10. Par ailleurs, les sorties QA, QB, QC et QD sont respectivement reliées à la première entrée non inverseuse et aux trois autres entrées inverseuses d'une porte NI 124. La sortie de la porte 124 et la sortie H de 121 sont reliées aux entrées d'une porte ET 125 dont la sortie est reliée aux entrées d'horloge des registres 14, 15 et 16.

Les sorties QA et H de 121 sont encore reliées aux entrées

d'une porte ET 126 dont la sortie est reliée aux entrées d'horloge des registres 14 à 16.

Le circuit 12 comprend un autre compteur 127 dont l'entrée C reçoit le signal d'horloge bit et dont la sortie H' délivre des 5 signaux d'horloge. Le compteur 127 a ses sorties QA, QB, QC et QD respectivement reliées à la première entrée inverseuse et aux trois autres entrées non inverseuses d'une porte NI 128, d'une part, et à la première entrée non inverseuse, à la seconde entrée inverseuse et aux deux autres entrées non inverseuses d'une porte NI 129.

10 La sortie de la porte 128 fournit le signal à l'entrée des portes 30 et 31 des circuits 13.1 à 13.4.

Les sorties des portes 128 et 129 fournissent les signaux 40 et 41 dans les circuits 19.1 à 19.2.

La Fig. 9 est le schéma d'un circuit de conversion 8x10 vers 15 12x10. Il comprend un registre à décalage 130 à huit étages dont l'entrée de données reçoit les bits des pixels de ligne d'une matrice 8x10. Ses sorties "1" et "2" sont respectivement reliées aux entrées d'une porte OU 131. Par ailleurs, le circuit comprend un registre à décalage à douze étages 132 qui délivre les bits des pixels de ligne 20 d'une matrice 12x10. La sortie "1" de 130 est reliée à l'entrée parallèle "1" de 132, la sortie de la porte 131 est reliée à l'entrée parallèle "2" de 132 et la sortie "2" de 130 est reliée à l'entrée parallèle "3" du registre 132. On retrouve ensuite trois fois la même 25 structure pour successivement les sorties "3" à "8" de 130 et les entrées "4" à "12" de 132.

## REVENDICATIONS

1) Système de transcodage d'une matrice 12x10 points en matrice 8x10 points, caractérisé en ce que la conversion comporte deux phases, une première phase dans laquelle les pixels de chaque ligne sont groupés par trois dans l'ordre naturel et dans laquelle chaque groupe de trois pixels est traité logiquement pour obtenir un groupe de deux pixels transformés, une seconde phase dans laquelle la configuration de l'ensemble initial des quatre pixels qui est à cheval sur la limite entre deux groupes est examiné de manière que, quand cet ensemble est différent de 0110, l'ensemble transformé formé des deux pixels transformés de la première phase, qui sont de part et d'autre de la limite, est conservé et que, dans le cas contraire, la configuration de l'ensemble initial correspondant de la ligne antérieure est examiné et:

15 - s'il est trouvé égal à 0110, les pixels de l'ensemble transformé sont remplacés par les pixels correspondants, définitivement transformés de la ligne précédente,

20 - s'il n'est ni égal à 0110, ni à 0000, les pixels de l'ensemble transformé sont remplacés par des pixels calculés dans la seconde phase à partir des pixels initiaux, voisins de la ligne courante et de la ligne antérieure,

25 - s'il est trouvé égal à 0000, l'ensemble initial correspondant de la ligne postérieure est examiné et:

- s'il est trouvé égal à 0000 ou à 0110, les pixels de l'ensemble transformé sont remplacés par 1 et 1;

25 - s'il est trouvé différent de 0000 et de 0110, les pixels de l'ensemble transformé sont remplacés par des pixels calculés dans la seconde phase.

30 2) Système suivant la revendication 1, caractérisé en ce que, dans la première phase, le traitement logique d'un groupe de trois pixels initiaux a, b, c, produit un groupe de pixels transformés  $\hat{a}$ ,  $\hat{b}$ , suivant les formules logiques suivantes:

$$\hat{a} = a + (\bar{b}_{-1} \cdot a_{-1} + \bar{c}_{-1} \cdot b_{-1}) \cdot \bar{a} \cdot b \cdot \bar{c}$$

$$b = c + (c_{-1} \cdot b_{-1} + \bar{b}_{-1} \cdot \bar{a}_{-1}) \cdot \bar{a} \cdot b \cdot \bar{c}$$

35 3) Système suivant la revendication 1, caractérisé en ce que les pixels b et  $\hat{a}'$ , calculés dans la seconde phase, sont définis,

soit par les deux équations logiques suivantes:

$$\begin{aligned}\hat{b} \cdot \hat{a}' = & a'_{-1} \cdot b'_{-1} \cdot (a_{-1} \cdot b_{-1} \cdot c_{-1} \cdot \bar{c}'_{-1} + \bar{b}_{-1} \cdot c_{-1} + b_{-1} \cdot \bar{c}_{-1}) + \\ & \bar{a}'_{-1} \cdot \bar{b}'_{-1} \cdot (c_{-1} \cdot c'_{-1} + b_{-1} \cdot \bar{c}_{-1}) + \bar{b}_{-1} \cdot \bar{c}_{-1} \cdot a'_{-1} \cdot \bar{a} \quad (\text{I})\end{aligned}$$

et

$$\begin{aligned}5 \quad \hat{b} \cdot \hat{a}' = & b_{-1} \cdot c_{-1} \cdot (\bar{a}_{-1} \cdot a'_{-1} \cdot b'_{-1} \cdot c'_{-1} + a'_{-1} \cdot \bar{b}'_{-1} + \bar{a}'_{-1} \cdot b'_{-1}) + \\ & \bar{b}_{-1} \cdot \bar{c}_{-1} \cdot (a'_{-1} \cdot a + \bar{a}'_{-1} \cdot b'_{-1}) + c_{-1} \cdot \bar{a}'_{-1} \cdot \bar{b}'_{-1} \cdot \bar{c}'_{-1} \quad (\text{II})\end{aligned}$$

soit par les deux équations logiques équivalentes (I') et (II') où - est remplacé par +.

- 4) Circuit de conversion fonctionnant suivant le système de l'une des revendications 1 à 3, caractérisé en ce qu'il comprend une entrée de signaux numériques de matrice 12x10 reliée à l'entrée d'un jeu de trois registres amont à décalage à douze cellules, montés en série, les sorties des premier et second registres amont étant reliées aux entrées correspondantes d'un circuit de calcul de première phase, une sortie de signal numérique de matrice 8x10 reliée à la sortie d'un jeu de trois registres aval à huit étages, montés en série, les sorties du circuit de calcul de première phase étant reliées aux entrées parallèles du premier registre aval, les sorties parallèles du second registre amont étant reliées à des entrées correspondantes d'un circuit de traitement de seconde phase, les sorties parallèles du premier et du troisième registres amont étant reliées par un circuit inverseur à des entrées correspondantes du circuit de traitement de seconde phase, les sorties parallèles, sauf la première et la dernière, du troisième registre aval étant reliées à des entrées correspondantes du circuit de traitement de seconde phase, les sorties du circuit de traitement de seconde phase étant reliées aux entrées parallèles, sauf la première et la dernière, du second registre aval, et une base de temps commandant les fonctionnements des circuits de calcul de première phase et de traitement de seconde phase et l'avancement dans les registres.

FIG.1

FIG. 2a

0115737

3/10

FIG.2b

FIG. 2c

FIG.2

FIG.2d

6/10

0115737

FIG.3a

FIG.3b

FIG.5

FIG.4

FIG.6

FIG.7

FIG. 8

FIG. 9

10/10

0115737

Office européen

des brevets

## RAPPORT DE RECHERCHE EUROPEENNE

0115737

Numéro de la demande

EP 83 46 0006

### DOCUMENTS CONSIDERES COMME PERTINENTS

| Catégorie                                                                                                                                                                                                                           | Citation du document avec indication, en cas de besoin,<br>des parties pertinentes           | Revendication<br>concernée                                                                                                                                                                             | CLASSEMENT DE LA<br>DEMANDE (Int. Cl. 3) |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| A, D                                                                                                                                                                                                                                | FR-A-2 419 623 (TELEDIFFUSION<br>DE FRANCE ET BRUSQ)<br>* Page 4, lignes 1-35 *<br><br>----- | 1                                                                                                                                                                                                      | G 09 G 1/16                              |

| DOMAINES TECHNIQUES<br>RECHERCHES (Int. Cl. 3)                                                                                                                                                                                      |                                                                                              |                                                                                                                                                                                                        |                                          |

| G 09 G 1/16<br>H 04 N 7/00<br>G 06 F 15/62                                                                                                                                                                                          |                                                                                              |                                                                                                                                                                                                        |                                          |

| Le présent rapport de recherche a été établi pour toutes les revendications                                                                                                                                                         |                                                                                              |                                                                                                                                                                                                        |                                          |

| Lieu de la recherche<br>LA HAYE                                                                                                                                                                                                     | Date d'achèvement de la recherche<br>18-04-1984                                              | Examinateur<br>VAN ROOST L.L.A.                                                                                                                                                                        |                                          |

| CATEGORIE DES DOCUMENTS CITES                                                                                                                                                                                                       |                                                                                              | T : théorie ou principe à la base de l'invention<br>E : document de brevet antérieur, mais publié à la date de dépôt ou après cette date<br>D : cité dans la demande<br>L : cité pour d'autres raisons |                                          |

| X : particulièrement pertinent à lui seul<br>Y : particulièrement pertinent en combinaison avec un autre document de la même catégorie<br>A : arrière-plan technologique<br>O : divulgation non-écrite<br>P : document intercalaire |                                                                                              | & : membre de la même famille, document correspondant                                                                                                                                                  |                                          |