(11) Publication number:

0 122 432

**A1**

(12)

## **EUROPEAN PATENT APPLICATION**

(21) Application number: 84102465.6

(51) Int. Cl.<sup>3</sup>: **G** 08 **B** 17/10 **G** 08 **B** 29/00

(22) Date of filing: 08.03.84

(30) Priority: 21.03.83 JP 46683/83

(43) Date of publication of application: 24.10.84 Bulletin 84/43

(84) Designated Contracting States: BE CH DE FR GB IT LI

(71) Applicant: Nohmi Bosai Kogyo Co., Ltd. No. 7-3, Kudanminami 4-chome Chiyoda-ku Tokyo 102(JP)

(72) Inventor: Morita, Toshikazu c/o NOHMI BOSAI KOGYO CO., LTD. 7-3, Kudan-Minami 4-chome Chiyoda-ku Tokyo(JP)

(74) Representative: Tiemann, Ulrich, Dr.-Ing. et al, c/o Cerberus AG Patentabteilung Alte Landstrasse 411 CH-8708 Männedorf(CH)

(54) Photoelectric smoke detector equipped with smoke detecting function test means.

(57) This invention relates to a photoelectric smoke detector which is capable of readily and precisely checking by itself whether light intensity reaching the smoke detector is within the normal level at which no false alarm, alarm failure nor delayed alarm is caused on the basis of the signal sent from a control panel through the lines connecting between the smoke detector and the control panel, and of reporting the result to the control panel through the same lines.

N 266 EP

Photoelectric smoke detector equipped with smoke detecting function test means.

It has been known that the operating test of the smoke detector which detects presence of smoke by scattering of light caused by entry of smoke into the light from the light emitting element and falling onto the light receiving element is carried out by increasing, from

the control panel, the output of the light emitting element to increase the output of the light receiving element with the noise light scattered in all directions on the wall surfaces in the labyrinth. Nevertheless, none of the photoelectric smoke detectors of this kind has ever had such a provision for checking, by remote operation from the control panel, the important function the detector, i.e. whether the output of the light receiving element of the detector is within the normal level range which causes no false alarm, alarm failure nor delayed alarm.

The purpose of this invention is to obtain a photoelectric smoke detector equipped with a smoke detecting function test means which, upon receipt of a signal sent from a control panel through lines connecting the smoke detector with the control panel, is capable of automatically, readily and precisely checking whether the output of the light receiving element in the smoke detector is within the normal level range, and of reporting to the control panel on the result of the check through the same lines. This invention is described below with reference to embodiments shown with figures.

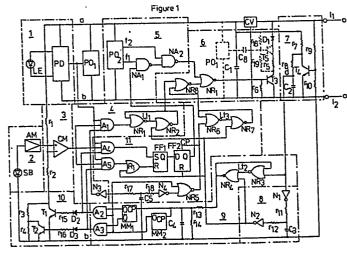

Figure 1 is a circuit diagram of an embodiment according to the present invention relating to the light scattering type smoke detector which detects presence of smoke by scattered light. Figure 2 is a circuit diagram of a control panel used for this embodiment.

Shown in Figure 1 are as follows: Two lines  $l_1$ ,  $l_2$  which connect the light scattering type smoke detector shown in the Figure with the control panel shown in Figure 2. Conductors a, b connected with the lines  $l_1$ ,  $l_2$  through a voltage stabilizing circuit CV. A pulse oscillator PO<sub>1</sub> for synchronized signal connected between the conductors a, b. A light emitting part  $\underline{l}$  which comprises a light emitting element LE such as light emitting diode, and a drive circuit PD connected between the conductors a, b. A light receiving part  $\underline{l}$  comprising a light receiving element SB such as solar cell which receives light emitted by the light emitting element LE and scattered by smoke, and an amplifier AM to amplify the output of the light receiving element SB. A comparison part  $\underline{l}$  which comprises a comparator CM with its - terminal on the input side connected with the voltage as operating level at the junction of resistors  $\underline{l}$ ,  $\underline{l}$  of those

resistors r1, r2, r3, r4 connected in series between the conductors a, b, and its + terminal on the input side connected with the output of the amplifier AM of the light emitting part 2. The resistors  $r_1$ , r2, r3, r4 are provided to determine a fire level, an upper level of the normal level range as a threshold level at which a false alarm is likely to be produced, and a lower level of the normal level range as a threshold level at which alarm failure or delayed alarm is likely to occur. A fire discriminating part 4 which comprises an AND gate A<sub>1</sub> and a latch Lt<sub>1</sub> formed by NOR gates NR<sub>1</sub>, NR<sub>2</sub>. The AND gate A<sub>1</sub> receives outputs of the pulse oscillator PO, for synchronized signal, the comparator CM in the comparison part 3 and a NOT gate N: to the input terminal of which Q output of a monostable multivibrator MM2 in a timer circuit 9 described hereafter is applied. is set by output of the AND gate A, and cleared by output of the NOT gate  $N_2$  in a reset signal generating circuit 8 which is described hereafter. A signal generating circuit 5 which comprises a pulse oscillator PO2 and NAND gates NA1, NA2. The pulse oscillator PO2 is connected between the conductors a, b and generates pulse outputs with low frequency f, and high frequency f2. The NAND gate NA, receives the pulse output with frequency f, and the output of the flip-flop circuit FF2 in a smoke detecting function discriminating circuit 11 described hereafter. The NAND gate NA2 receives the pulse output with frequency f2 and the output of the gate NA1. A signal transmission circuit 6 which comprises NOR gates NRs, NRs and a series circuit connected between the lines 1, 12, and sends out the pulse signal with frequency f1, or f2 to the lines 11, 12 by controlling the conduction of a transistor T3 with output of the gate NR $_{\scriptsize 9}$ . The NOR gate NR $_{\scriptsize 8}$  receives outputs developed when the fire discriminating part 4 has detected a fire and of a latch Lt3 formed by NOR gates NR<sub>6</sub>, NR<sub>7</sub> in the smoke detecting function discriminating circuit 11. The NOR gate NR, receives outputs of the NOR gate NR, and the NAND gate NA2 in the signal generating circuit 5. The series circuit is formed by a diode D1, resistor r5 and a transistor T3 with a resistor r6 connected between the base and emitter. An additional circuit shown with dotted lines in the signal generating circuit 6 is provided for identifying an alarming detector at the control panel in case plural detectors are connected in parallel between the same

lines 1, 12. An oscillator PO, generating pulses which vary with each detector and have far higher frequencies than f1, f2 is connected between the conductors a, b. A transistor T5 is connected between the diode D<sub>1</sub> and the resistor r<sub>5</sub>. Resistors r<sub>18</sub> and r<sub>19</sub> are connected between the conductor a and the base of the transistor Ts, and between the base of the transistor  $T_{\mbox{\scriptsize 5}}$  and the collector of the transistor T<sub>3</sub> respectively. A capacitor C<sub>6</sub> is connected between the oscillator PO<sub>3</sub> and the base of the transistor T<sub>5</sub>. With the pulse signal from the oscillator PO3, each pulse of the pulse signals with frequencies  $f_1$ ,  $f_2$  sent from each detector to the lines  $l_1$ ,  $l_2$  is modulated. A signal receiving circuit 7 which receives a single pulse signal with narrow width for test start and a single pulse signal with wide width for resetting which are sent out from the control panel shown in Figure 2. The signal receiving circuit 7 is formed by resistors  $r_7$ ,  $r_8$  and a capacitor  $C_2$  which are connected in series between the conductors a, b; an output line d which is led from the junction between the resistor rs and the capacitor C2 to a reset signal generating circuit 8 and a timer circuit 9 described hereafter; and a transistor T4, conduction of which is controlled by voltage at the junction of the resistors  $r_9$ ,  $r_{10}$  connected in series between the lines  $l_1$ ,  $l_2$  and which shorts the series circuit of the resistor re and the capacitor  $C_2$  when became conductive. The reset signal generating circuit 8confirms receipt of the reset signal from the control panel and transmits the reset signal to the detector. The reset signal generating circuit 8 is equipped with a capacitor Co which is charged with output of the signal receiving circuit  $\frac{7}{2}$  through a NOT gate N<sub>1</sub> and a resistor  $r_{11}$ , and produces the reset signal with the voltage of the capacitor  $C_3$  through the resistor  $r_{12}$  and NOT gate  $N_2$ . The timer circuit  $\underline{9}$ operates when the signal receiving circuit 7 has received the test start signal from the control panel, and comprises a latch Lt2, resistors r13, r14, a capacitor C4, monostable multivibrators MM1, MM2 and AND gates A2, A3. The latch Lt2 is formed by NOR gates NR3, NR4 which are set by output of the signal receiving circuit 7. The output of the latch Lt2 is sent to the monostable multiviblators MM1, MM2 having a short and long operating time respectively through the delay circuit formed by the resistor r13, capacitor C4 and resistor r14 to prevent the timer circuit  $\underline{9}$  from operating with the output of the

latch Lt2 when the signal receiving circuit 7 has received the reset signal from the control panel. The output of the monostable multivibrators MM1, MM2 are applied to the input terminals of the AND gates A2, A3. An operating level changeover circuit 10 which changes over the operating level of the comparator CM in the comparison part 3, and operates as follows. With the output of the AND gate A2 in the timer circuit 9 transmitted through a diode D2 and a resistor r15, the transistor T1 becomes conductive and shorts the series circuit formed by resistors r3, r4. With the output of the AND gate A3 transmitted through a diode D<sub>3</sub> and a resistor r<sub>16</sub>, the transistor T<sub>2</sub> becomes conductive and shorts the resistor ru alone. Thus, the voltage applied as operating level to the - terminal on the input of the comparator CM in the comparison part 3 becomes the fire level of the light scattering type smoke detector while the both transistors T1, T2 are not conducting. As the transistor T, become conductive, the voltage becomes the lower limit of the normal level range as a threshold level of the detector at which alarm failure or delayed alarm is likely to occur. As the transistor T2 becomes conductive, the voltage becomes the upper level of the normal level range as a threshold level of the detector at which a false alarm is likely to be produced. A smoke detecting function discriminating circuit 11 which comprises AND gates A4, A5, OR gate R<sub>1</sub>, R - S flip-flop circuit FF<sub>1</sub>, D-type (delayed) flip-flop circuit FF2, lesistors 117, r18, capacitor C5, NOT gate N4, NOR gate NRs and latch Lt3 formed by NOR gates NR6, NR7. The AND gates A4, A5 are connected with the outputs of the pulse oscillator PO, for synchronized signal, the comparator CM in the comparison part 3 and AND gates A2, A3 in the timer circuit 9. The R - S flip-flop circuit FF1 receives the output of the AND gate A4 as set input and the output of the OR gate R1 as reset input which is connected with the outputs of the AND gate As and the reset signal generating circuit 8. The D type flip-flop circuit FF2 receives Q output of the flip-flop circuit FF1 as D input, the clock signal as CP input generated by the NOR gate NRs and the output of the circuit 8 as reset input. The NOR gate NRs serving as clock signal generator is connected with the Q output of the monostable multivibrator MM2 in the timer circuit 9 and the output of the NOT gate N4 to which the voltage of the capacitor Cs charged with the Q output through the resistor r17 is applied through

the resistor  $r_{18}$ . The latch Lt<sub>3</sub> formed by the NOR gates NR<sub>6</sub>, NR<sub>7</sub> receives the output of the NOR gate NR<sub>5</sub> as set input and is cleared by output of the reset signal generating circuit 8.

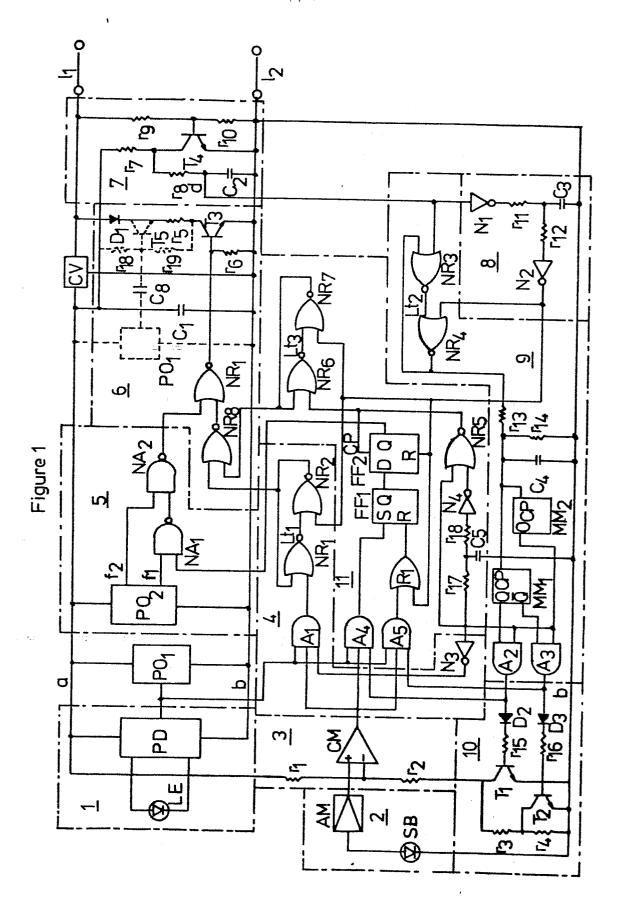

Shown in Figure 2 are; a d.c. power supply E; a detecting circuit M for abnormal signal with frequency f2 including a fire signal; a detecting circuit N for normal signal with frequency f1; a relay X which operates when a test start switch SW1 has closed; a relay Y which operates when a reset switch SW2 has closed; a test start signal generator TS which operates when the contact  $x_1$  of the relay X has closed; a reset signal generator RS which operates when the contact y1 of the relay Y has closed; a fire indicator lamp La1 which is lit through the break contact x4 of the relay X and the make contact m<sub>1</sub> of the relay M; an abnormal indicator lamp La<sub>2</sub> which is lit through the make contact x3 of the relay X and the make contact m2 of the relay M; a normal indicator lamp La3 which is lit through the make contact x3 of the relay X and the make contact n1 of the relay N; a timer T which starts operating when the contact x₅ of the relay X has closed; and a trouble indicator lamp La, which is operated through the make contact t of the timer T and the break contacts m3, n2 of the relays M, N to indicate accidents such as trouble in the detector lines or interruption of the lines  $l_1$ ,  $l_2$ .

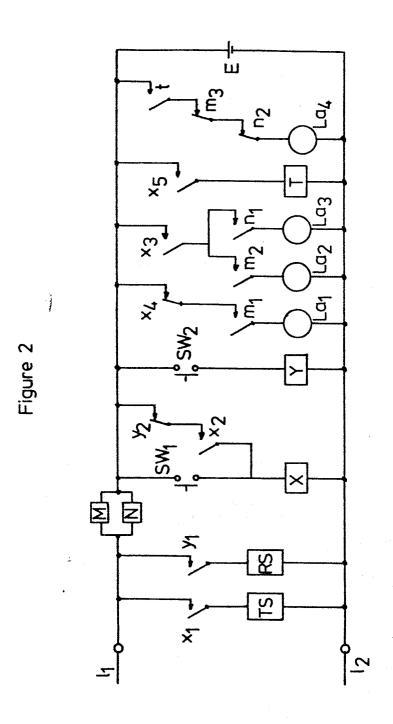

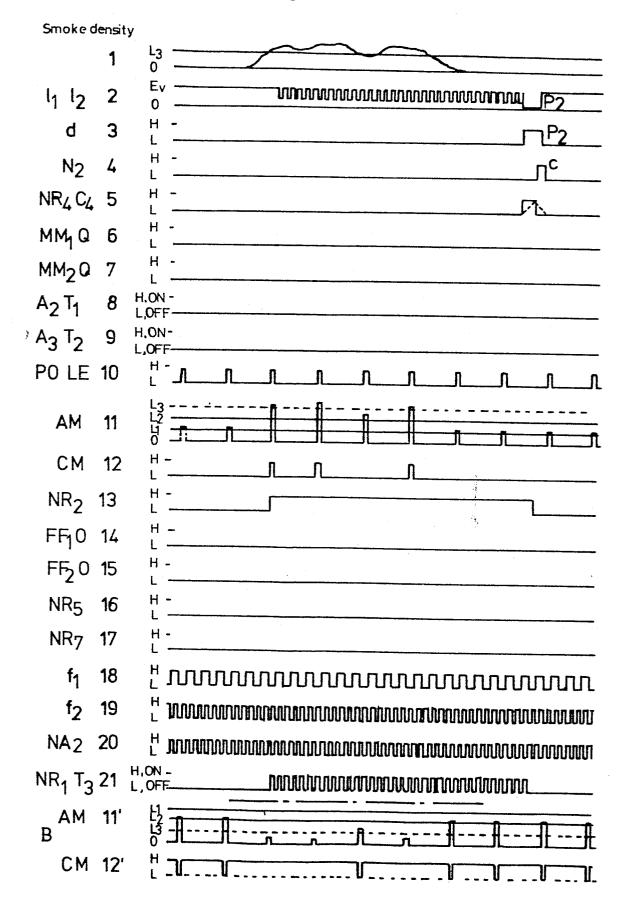

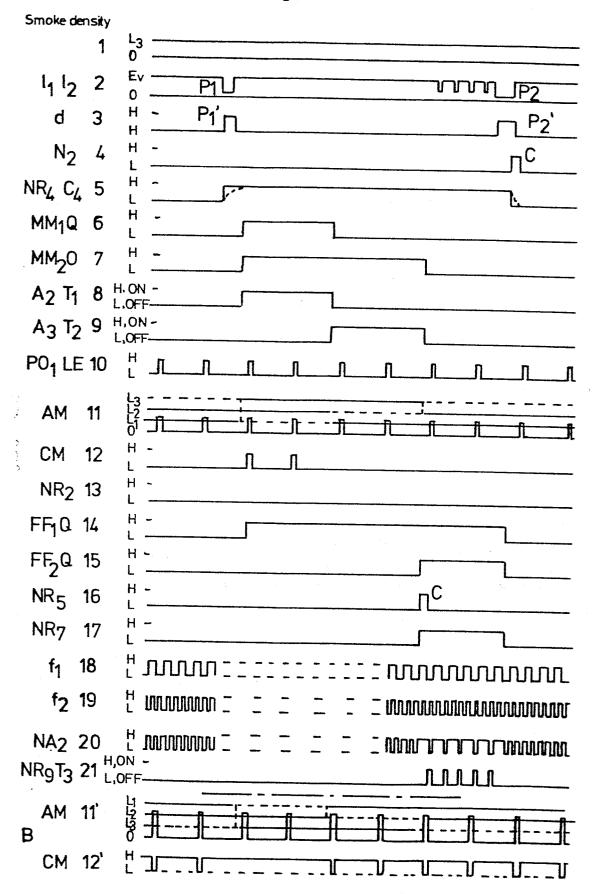

Firstly, operation of each part of this embodiment during the normal supervisory condition and in case of fire is described with reference to the time charts shown in Figure 3 (A). Shown in Figure 3 (A) are smoke density (1), voltage (2) on the lines 1, 1, 1, During the normal supervisory condition without smoke, the voltage on the lines 1, 1, is Evas shown in the left part of Figure (1) while the voltage on the output line d of the signal receiving circuit 7 is at L level as shown at the left part of Figure (3) because the transistor T4 is conducting. Consequently, in the reset signal generating circuit 8, the output of the NOT gate N1 becomes H level. With this output the capacitor C3 is charged, and the output of the NOT gate N2 becomes L level, thus no reset signal is generated as shown at the left part of Figure (4). In the timer circuit 9, the latch Lt2 formed by the NOR gates NR3, NR4 has the input of L level, and accordingly its output, too, is at L level as shown in the left part of Figure (5), thus no

clock signal is generated. As shown in Figures (6), (7), the Q outputs of the monostable multivibrators MM1, MM2 are at L level, the O output of the former MM, is at H level, and the outputs of the AND gates A2, As are at L level. Therefore, the transistors T1, T2 in the operating level changeover circuit 10 do not switch on, and as shown with the dotted line in Figure (11) the operating level of the comparator CM in the comparison part 3 is at fire level L3 which is determined by dividing ratio of the resistance values of the resistors r1 are r2+r3+r4. The light emitting element LE emits light through the driving circuit PD in the light emitting part 1 each time the pulse oscillator PO<sub>1</sub> generates the synchronizing signal as shown in Figure (10). With the scattered light from the inner wall of the labyrinth the output amplifier AM of the light receiving element SB in the light receiving part 2 gives off an output as shown in Figure (11). Nevertheless, since this output is below the fire level L3 under the condition without smoke, the comparator CM in the comparison part 3 has no output as shown in the left part of Figure (12). In the fire discriminating part 4 the output of the NOT gate  $N_3$  is at H level because the Q output of the monostable multivibrator  $MM_2$  in the timer circuit 9 is at L level. However, since the output of the comparator CM is at L level, the output of the AND gate A, becomes L level, and accordingly the input of the latch Lt, formed by NOR gates NR, NR2 and the output of the NOR gate NR2 are at L level as shown in the left part of Figure (13). In the smoke detecting function discriminating circuit 11 the output of the comparator CM in the comparison part 3 being at L level, the outputs of the AND gates A4, A5 are at L level. Accordingly the output of the OR gate  $R_1$  is at L level and the Q output of the R-Sflip-flop circuit FF; is at L level as shown in Figure (14). The Q output of the monostable multivibrator  $MM_2$  in the time circuit 9 is at L level while the output of the NOT gate N. is at H level. Accordingly, the outputs of the NOR gate NR<sub>5</sub> serving as clock signal generator, the Q output of the D-type flip-flop circuit FF2 and the output of the latch Lt<sub>3</sub> formed by NOR gate NR<sub>6</sub>, NR<sub>7</sub> are at L level as shown in Figure (16), (15) and (17) respectively. Therefore, in the signal generating circuit 5 the pulse oscillator PO2 produces pulses with frequencies f1 and f2 shown in Figure (18) and (19) respectively. With the pulse having frequency f, and the Q output of

the circuit  $FF_2$  being at L level, the output of the NAND gate NA<sub>1</sub> becomes continuous H level. With the pulse signal having frequency  $f_2$  and the continued H level output of the NAND gate NA<sub>1</sub>, the NAND gate NA<sub>2</sub> generates a pulse signal with a phase opposite to that of the pulse signal having frequency  $f_2$  from the pulse oscillator  $PO_2$  as shown in Figure (20). Since the output of the NOR gate NR<sub>6</sub> in the signal transmission circuit  $\underline{6}$  is at H level, the output of the NOR gate NR<sub>7</sub> is at L level as shown in the left part of Figure (21), consequently the transistor  $F_3$  does not become conductive, and no output appears on the lines  $F_1$ ,  $F_2$  as shown in the left part of Figure (2).

When smoke generated by fire enters the labyrinth and its density exceeds the fire level L3 as shown in the middle part of Figure (1), the amplifier AM for the light receiving element SB generates a pulse signals exceeding the fire level L3 as shown in Figure (11), and the comparator CM generates a corresponding pulse signal as shown in Figure (12) at the time of light emission from the light emitting element LE. With this pulse signal, the synchronizing signal generated by oscillator PO<sub>1</sub> as shown in Figure (10) and the H level output of the NOT gate N3, the AND gate A1 generates a pulse signal corresponding to the output of the comparator CM. This pulse signal sets the output of the latch Lt, formed by NOR gates  $NR_1$ ,  $NR_2$  as shown in Figure (13), and the NOR gate NR2 generates a fire detecting output. With the fire detecting output from the NOR gate NR, the output of the NOR gate NR, in the signal transmission circuit 6 becomes L level. With this L level output and the pulse signal of frequency f2 from the NAND gate N2 in the signal generating circuit 5 as shown in Figure (20), the NOR gate NR, generates a pulse signal with frequency f2 as shown in Figure (21) and sends an abnormal signal with frequency f2 as fire signal as shown in Figure (2) to the lines  $l_1$ ,  $l_2$  through the transistor  $T_3$ . As the abnormal signal detecting circuit M in the control panel shown in Figure 2 detects the fire signal, the contact m, closes and the fire indicator lamp La, lights. In order to reset the alarming detector the reset switch SW2 on the control panel is closed to operate the relay Y. Then, the contact y1 closes to operate the reset signal generator RS, which sends out the reset signal as shown with the symbol  $P_2$  in Figure (2) to the lines  $l_1$ ,  $l_2$ . With the signal  $P_2$  the transistor T4 in the signal receiving circuit 7 in the detector stops conducting,

and the signal P2 as shown in Figure 3 (3) is generated in the output line d in the circuit 7, As a result of this, the output of the NOT gate N; in the reset signal generating circuit 8 becomes L level, and the charge on the capacitor C, is released through the NOT gate N1. When the input of the NOT gate N2 becomes L level, the NOT gate  $N_2$  generates the clear signal c as shown in Figure (4). On the other hand, if the output P2 of the circuit 7 is received by the input terminal of the latch Lt2 formed by NOR gates NR3, NR4 in the timer circuit 9 before the NOT gate N2 generates the clear signal, the latch Lt<sub>2</sub> is set and the NOR gate NR<sub>4</sub> gives an output at H level as shown in Figure (5). With the output of the NOR gate NR4 the capacitor C4 is charged as shown with the dotted line in Figure (5) through the resistor  $r_{13}$ . Since the circuit 8 generates the clear signal c as shown in Figure (4) before the capacitor voltage reaches such a level as may be judged as a clock signal, the setting of the latch Lt2 is cleared by this signal c and the charge on the capacitor C4 is released through the resistor r14, thus no clock signal is generated. When resetting the detector in the above manner, if the smoke density is below the fire level L3 as shown in Figure (1), setting of the latch Lt, formed by NOR gates NR, NR2 is cleared by the clear signal c shown in Figure (4), and the fire detecting output of the NOR gate NR2 stops as shown in Figure (13). Then the output of the NOR gate NR, in the signal transmission circuit 6 becames H level, and the output of the NOR gate NR, stops, thus no fire signal is sent to the lines l1, L2. Consequently, the abnormal signal detecting circuit M in the control panel shown in Figure 2 no longer detects the fire signal, thus the contact m1 opens, and the fire indicator lamp La, extinguishes.

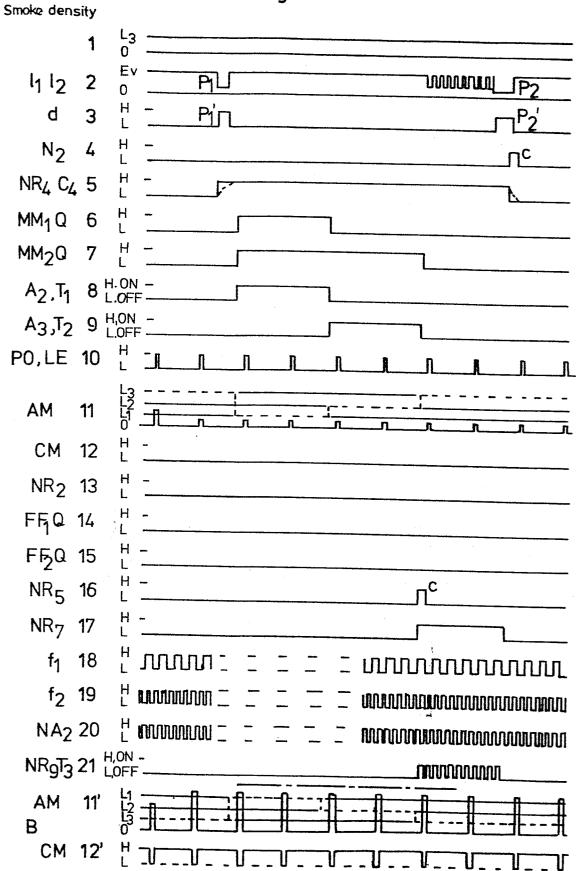

Operation of each part at the time of testing while the output of the amplifier AM in the light receiving part  $\underline{2}$  is within the normal level range is described below with reference to the time chart shown in Figure 4 (A).

As the test start switch  $SW_1$  in the control panel shown in Figure 2 is closed, the relay X operates and the contacts  $x_1 \sim x_3$  close. The test start signal generator TS sends the test start signal shown with a symbol  $P_1$  in Figure 4A (2) to the lines  $l_1$ ,  $l_2$  to interrupt, for a short time, conduction of the transistor  $T_4$  in the signal receiving

circuit 7 of the detector shown in Figure 1. The circuit 7 generates the pulse signal P1' in the output line d as shown in Figure (3). With the signal P1', the output of the NOT gate N1 in the reset signal generating circuit 8 becomes L level, and the charge on the capacitor C3 is released through the NOT gate N1. Nevertheless, before the voltage of the capacitor C3 raises the output of the NOT gate N2 to H level, the output P1' disappears and the output of the NOT gate N1 again becomes H level. Therefore, the capacitor C3 is recharged, thus the NOT gate N2 maintains the L level output as shown in Figure (4). The output P<sub>1</sub>' of the circuit 7 also sets the latch Lt<sub>2</sub> formed by NOR gates NR2, NR4 in the timer circuit 9. As the capacitor C4 is charged with the H level output of the NOR gate NR4 through the resistor  $r_{13}$  as shown with the dotted line in Figure (5) and its voltage reaches the H level, the clock signal is sent to the CP terminals of the monostable multivibrators MM1, MM2 with this voltage. At the Q terminals of the monostable multivibrators MM1, MM2, H level outputs develop as shown in Figures (6), (7), and a L level output develops on the  $\overline{Q}$  terminal of the monostable multivibrator MM1, then the output of the AND gate A2 becomes H level as shown in Figure (8). The transistor T<sub>1</sub> in the operating level changeover circuit 10 too is conducting while the output of the AND gate A2 is at H level. Thus, the operating level of the comparator CM in the comparison part 3 becomes the lower level L<sub>1</sub> of the normal level range which is determined by resistance dividing ratio of the resistor r1, r2, as shown with the dotted line in Figure (11). Furthermore, since the Q output of the monostable multivibrator MM2 is at H level, the output of the NOT gate No becomes L level and inhibits operation of the AND gate A1. On the other hand the capacitor C5 in the function discriminating circuit 11 is charged. When its voltage reaches a predetermined value, the output of the NOT gate N4 becomes L level, but the other input of the NOR gate NRs is at H level. Therefore, the NOR gate NR, does not produce the clock signal.

Under this condition, if the pulse output of the amplifier AM in the signal receiving part  $\underline{2}$  lies between the lower level  $L_1$  and the upper level  $L_2$  of the normal level range as shown in Figure (11), the comparator CM generates detecting pulse signal as shown in Figure

(12) because the pulse output of the amplifier AM is above the operating level of the comparator CM. With this pulse output of the comparator CM, synchronized signal generated by the pulse oscillator PO<sub>1</sub> and H level output of the AND gate A<sub>2</sub>, the AND gate A<sub>4</sub> generates the pulse output similar to that of the comparator CM as shown in Figure (12). This output of the AND gate A<sub>4</sub> sets the Q output of the circuit FF<sub>1</sub> in the function discriminating circuit 11 at H level as shown in Figure (14). On the other hand the Q output of the circuit FF<sub>2</sub> remains at L level as shown in Figure (15) because the CP terminal receives no clock signal from the NOR gate NR<sub>5</sub>.

After lapse of a predetermined short time the Q output and  $\overline{Q}$  output of the monostable multivibrator MM1 in the timer circuit 9 become L level and H level respectively as shown in Figure (6). Consequently, the output of the AND gate A2 becomes L level as shown in Figure (8), inhibiting operation of the AND gate A4 in the circuit 11, and rendering the transistor T<sub>1</sub> in the circuit 10 non conductive. On the other hand, the output of the AND gate A3 becomes H level as shown in Figure (9), the transistor T2 becomes conductive, and the operating level of the comparator CM in the comparison part 3 reaches the upper level of the normal level range as shown with the symbol L2 in Figure (11) which is determined by dividing ratio of the resistors  $r_1$  and  $r_2+r_3$ . Under this condition, if the amplifier AM in the light receiving part 2 has the normal output as shown in Figure (11), the output of the comparator CM is at L level as shown in Figure (12) because the output of the amplifier AM is below the level L2.

When the output of the monostable multivibrator  $MM_2$  becomes L level as shown in Figure (7) after lapse of a predetermined long time, this L level output and the output of the NOT gate  $N_4$  in the function discriminating circuit  $\underline{11}$  at L level cause the NOR gate  $NR_5$  to generate the clock signal c as shown in Figure (16). With this signal c, the Q output of the flip-flop circuit  $FF_2$  becomes H level as shown in Figure (15) because the Q output of the flip-flop circuit  $FF_1$  is at H level as shown in Figure (14). With the H level output of the flip-flop circuit  $FF_2$ , the NAND gate  $NA_1$  in the signal generating circuit  $\underline{5}$  generates a pulse signal having the phase opposite to that of the

pulse signal with frequency f1 generated by the oscillator PO2, and the NAND gate NA2 generates a pulse signal with frequency f1 as shown in Figure (20). The clock signal from the NOR gate NR5 sets the latch Lt3 formed by NOR gates NR6, NR7, and the output of the NOR gate NR7 becomes H level. With this H level output, the output of the NOR gate NRs in the signal transmission circuit 6 becomes L level, and the NOR gate NR, generates a pulse signal with frequency f, as shown in Figure (21), by which conduction of the transistor T<sub>3</sub> is controlled and the normal signal shown in Figure (2) is sent to the lines  $l_1$ ,  $l_2$ . Lastly, as the signal receiving circuit 7 has received the reset signal P2 shown in Figure (2) and has an output P2' shown in Figure (3) on its output line d, the NOT gate N2 in the reset signal generating circuit 8 generates a clear signal c shown in Figure (4), which resets the latches Lt2, Lt3 formed by NOR gates NR3, NR4 and NR6, NR7 respectivel in the same manner as resetting in case of fire. Then, the outputs of the NOR gates NR4, NR7 become L level as shown in Figure (5) and (17) respectively. With the L level output of the NOR gate NR, the NOR gate NR, no longer generates the pulse signal as shown in Figure (21), and accordingly the signal transmission circuit 6 stops transmitting the normal signal as shown in Figure (2). The clear signal from the NOI gate N2 resets the flip-flop circuit FF1 in the function discriminatin circuit 11 through the OR gate R1, and the flip-flop circuit FF, directly. The Q outputs of the both circuits become L level as shown in Figures (14), (15). With the L level output of the flip-flop circuit FF2, the output of the NAND gate NA1 in the signal generating circuit 5 become H level and the NOT gate NA2 generates the pulse signal with frequency  $f_2$  as shown in Figure (20), thus each part of the detector returns to the original state.

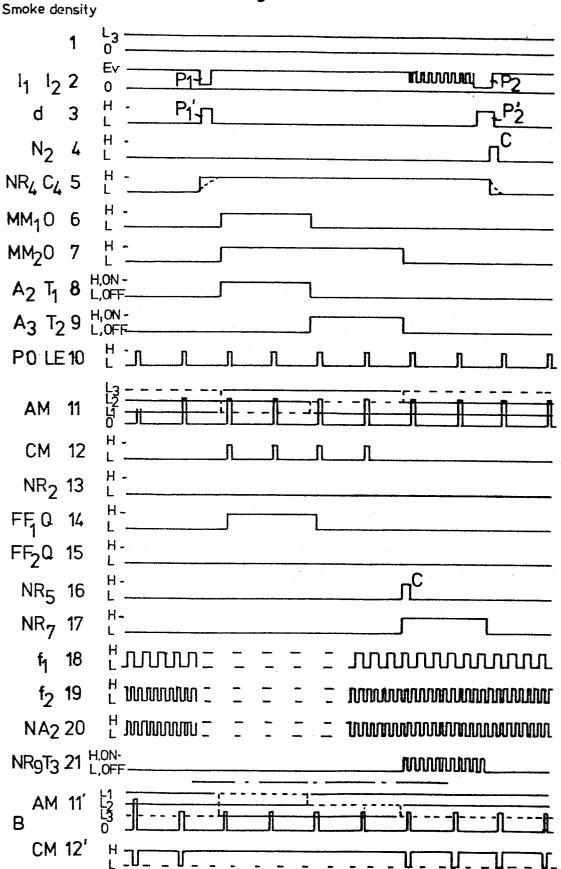

Now, the following describes operation of each part during the test with reference to the time chart shown in Figure 5 (A) in case that the output of the amplifier AM has been reduced below the lower level  $L_1$  of the normal level range due to soiling by dust accumulating over the light receiving surface of the light receiving element SB in the light receiving part  $\underline{2}$ .

In this case, too, the signal receiving circuit  $\underline{7}$  in Figure 1 generates a pulse signal  $P_1$  in the output line d with the test start signal  $P_1$

from the control panel shown in Figure 5 (A) (2). However, due to narrow pulse width of the pulse signal P<sub>1</sub>', the NOT gate N<sub>2</sub> in the reset signal generating circuit 8 generates no clear signal. On the other hand the latch Lt<sub>2</sub> formed by NOR gates NR<sub>3</sub>, NR<sub>4</sub> in the timer circuit 9 is set as shown in Figure (5) with the pulse signal P<sub>1</sub>'. When the capacitor C<sub>4</sub> is charged with the H level output of the NOR gate NR<sub>4</sub> through the resistor r<sub>13</sub> as shown with the dotted line in Figure 5 (A) (5) and the voltage reaches the H level, outputs of H level develop at the Q terminals of the monostable multivibrators MM<sub>1</sub>, MM<sub>2</sub> as shown in Figure (6), (7), and the output of the AND gate A<sub>2</sub> becomes H level. Then, the transistor T<sub>1</sub> in the operating level changeover circuit 10 becomes conductive as shown in Figure (8), and the operating level of the comparator CM in the comparison part 3 becomes the lower level L<sub>1</sub> of the normal level range as shown with the dotted line in Figure (11).

With the H level output of the monostable multivibrator  $MM_2$ , the output of the NOT gate  $N_3$  in the fire discriminating part  $\frac{4}{2}$  becomes L level and inhibits operation of the AND gate  $A_1$ , while on the other hand the NOR gate  $NR_5$  in the function discriminating circuit  $\underline{11}$  generates no clock signal as shown in Figure (16).

Under this condition, if the output of the amplifier AM in the light receiving part  $\underline{2}$  is below the level  $L_1$  as shown in Figure (11), the transistor  $T_1$  in the operating level changeover circuit  $\underline{10}$  becomes conductive as shown in Figure (8). Therefore, even if the operating level of the comparator CM in the comparison part  $\underline{3}$  becomes the lower level  $L_1$  as shown in Figure (11), no detecting signal is generated in the comparator CM as shown in Figure (12), the AND gate  $A_4$  in the function discriminating circuit  $\underline{11}$  has no output, and the flip-flop circuit  $\underline{FF_1}$  is not set as shown in Figure (14).

Then, after lapse of a predetermined time, the Q output of the monostable multivibrator  $MM_1$  in the timer circuit  $\underline{9}$  becomes L level as shown in Figure 6, and the  $\overline{Q}$  output becomes H level. The outputs of the AND gates  $A_2$ ,  $A_3$  become L and H levels respectively as shown in Figures (8), (9), thus rendering the transistor  $T_1$  non-conductive and the transistor  $T_2$  conductive. Consequently the operating level of the comparator CM becomes the level  $L_2$  as shown in Figure (11). Enen

at this level L<sub>2</sub>, the comparator CM has no output as shown in Figure (12), and the AND gate A<sub>5</sub>, too, has no output. After further lapse of a predetermined time the Q output of the monostable multivibrator MM<sub>2</sub> becomes L level as shown in Figure (7), and the NOR gate NR<sub>5</sub> generates the clock signal c shown in Figure (16), which sets the latch Lt<sub>3</sub>. As the output of the NOR gate NR<sub>6</sub> in the signal transmission circuit 6 becomes L level with the H level output of the NOR gate NR<sub>7</sub> shown in Figure (17), the NOR gate NR<sub>9</sub> generates a pulse signal with frequency f<sub>2</sub> as shown in Figure (21) because the NAND gate NA<sub>2</sub> in the signal generating circuit 5 is generating a pulse signal with frequency f<sub>2</sub> as shown in Figure (20). By the pulse signal from the NOR gate NR<sub>9</sub>, conduction of the transistor T<sub>3</sub> is controlled, and the abnormal signal is sent to the control panel through the lines l<sub>1</sub>, l<sub>2</sub> as shown in Figure (2).

The following describes operation of each part during the test with reference to the time chart shown in Figure 6 (A), which is carried out in case the output of the amplifier AM for the light receiving element SB in the light receiving part 2 has exceeded the upper level L<sub>2</sub> of the normal level range due to accumulation of dust in the labyrinth.

As in the case of the foregoing, the signal receiving circuit 7 in Figure 1 generates the pulse signal P1' in the output line d shown in Figure (3) with the test start signal P<sub>1</sub> from the control panel shown in Figure 6 (A) (2). Although the NOT gate  $N_2$  in the reset signal generating circuit 8 does not generate the clear signal, the latch Lt2 in the timer circuit 9 is set. The capacitor C4 is charged with the H level output of the NOR gate NR, as shown with the dotted line in Figure (5). When the voltage reaches the H level, outputs of H level develop at the Q terminals of the monostable multivibrators MM1, MM2 as shown in Figure (6), (7) and the output of the AND gate A2 becomes H level. Then, the transistor T<sub>1</sub> in the operating level changeover circuit 10 becomes conductive as shown in Figure 6 (8), and the operating level of the comparator CM in the comparison part 3 becomes the lower level L<sub>1</sub> of the normal level range as shown with the dotted line in Figure (11). With the H level output of the Q terminal of the monostable multivibrator MM2, the output of the NOT gate N3 in the fire discriminating circuit 4 becomes L level and inhibits operation of the AND gate A1,

while on the other hand the NOR gate NR, in the function discriminating circuit 11 generates no clock signal.

Under this condition, if the output of the amplifier AM in the light receiving part 2 is over the level L2 as shown in Figure (11), the transistor T<sub>1</sub> in the operating level changeover circuit 10 become conductive as shown in Figure (8). As the operating level of the comparator CM in the comparison part 3 becomes the level L1 as shown in Figure (11), the output of the comparator CM becomes the H level. With this output of the comparator CM, the output of the AND gate A4 in the function discriminating circuit 11 becomes H level, and accordingly the Q output of the flip-flop circuit FF1 is set at H level as shown in Figure (14). However, since the CP terminal of the flip-flop circuit FF2 receives no clock signal from the NOR gate NR5, the Q output of the flip-flop circuit remains at L level. After lapse of a predetermined time under this condition, the Q output of the monostable multivibrator  $MM_1$  in the timer circuit  $\underline{9}$  becomes L level as shonw in Figure (6) and Q output becomes H level. The outputs of the AND gates A2, A3 become L and H levels respectively as shown in Figure (8), (9). Thus, the transistor  $T_1$  becomes non-conductive and the transistor  $T_2$  conductive. Then, the operating level of the comparator CM changes to level L2 as shown in Figure (11), the output of the comparator CM remains at H level. With this output the AND gate As and the OR gate R1 generate H level outputs successively. With the output reaching the reset terminal R of the flip-flop circuit FF1, the Q output of the flip-flop circuit FF1 is reset at the L level as shown in Figure (14). Even if the comparator CM has an output thereafter, the Q output of the flip-flop circuit FF1 remains at L level as shown in Figure (14) as long as the operating level of the comparator CM is at the level L2, because the output of the comparator CM reaches the R terminal of the flip-flop circuit FF1 through the AND gate As and the OR gate R1. As in the previous case, after lapse of a predetermined time the Q output of the monostable multivibrator MM2 becomes L level as shown in Figure (7), and the NOR gate NR5 in the circuit 11 generates the clock signal c shown in Figure (16), which sets the latch Lt3. As the NOR gate NR7 has H level output shown in Figure (17), and the output of the NOR gate NRs in the signal transmission circuit 6 becomes the L level, the NAND gate NA2 in the signal generating circuit 5 generates a pulse signal with frequency f2 as shown in Figure

(20), and accordingly the NOR gate NR, generates a pulse signal of frequency  $f_2$  as shown in Figure (21) to control conduction of the transistor  $T_3$  and to send an abnormal signal to the control panel through the lines  $l_1$ ,  $l_2$  as shown in Figure (2).

Now, the following describes how the signal receiving circuit 7 operates with the reset signal P<sub>2</sub> shown in Figure 5 (A) and 6 (A) (2) and received from the control panel after the test conducted in case that the output of the amplifier AM has fallen below the lower level L<sub>1</sub> and exceeded the upper level L<sub>2</sub>. The signal receiving circuit 7 generates a pulse signal P<sub>2</sub>' shown in Figure (3) in the output line d. The NOT gate N<sub>2</sub> in the reset signal generating circuit 8 generates the clear signal c shown in Figure 6 (4), with which the latches Lt<sub>2</sub>, Lt<sub>3</sub> formed by NOR gates NR<sub>3</sub>, NR<sub>4</sub> and NR<sub>6</sub>, NR<sub>7</sub> respectively are reset. Then, the outputs of the NOR gates NR<sub>4</sub>, NR<sub>7</sub> become L level as shown in Figures (5) and (17). Because of this L level output of the NOR gate NR<sub>7</sub>, the NOR gate NR<sub>9</sub> no longer generates the pulse signal as shown in Figure (21), and the signal transmission circuit 6 stops transmitting the abnormal signal to the lines l<sub>1</sub>, l<sub>2</sub> as shown in Figure (2), thus each part of the detector resets to the original condition.

Lastly, the following describes operation of the control panel when the test is conducted with the test start signal from the control panel shown in Figure 2. When the switch SW, is closed for testing, the relay X operates to close the contacts  $x_1 \sim x_3$  and open the contact  $x_4$ . Therefore, on receipt of the normal signal from the detector shown in Figure 1, the relay N operates and close the contact N1, and the normal indicator lamp La3 lights. When the abnormal signal is received, the relay M operates and closes the contacts m1, m2 to cause the abnormal indicator lamp La2 to light up indicating that there is abnormality in the smoke detecting function. As the switch SW2 is closed to reset the detector, the relay Y operates and closes the contact y, and opens the contact  $y_2$  to actuate the reset signal generator RS which sends the reset signal to the lines  $l_1$ ,  $l_2$ . At the same time, operation of the relay X is stopped and the contacts x1, x2, x3 are opened to prevent the test signal generator TS from operating and to extinguish the normal indicator lamps La2, La3. The contact x4 is closed to reset the control panel in the normal supervisory condition.

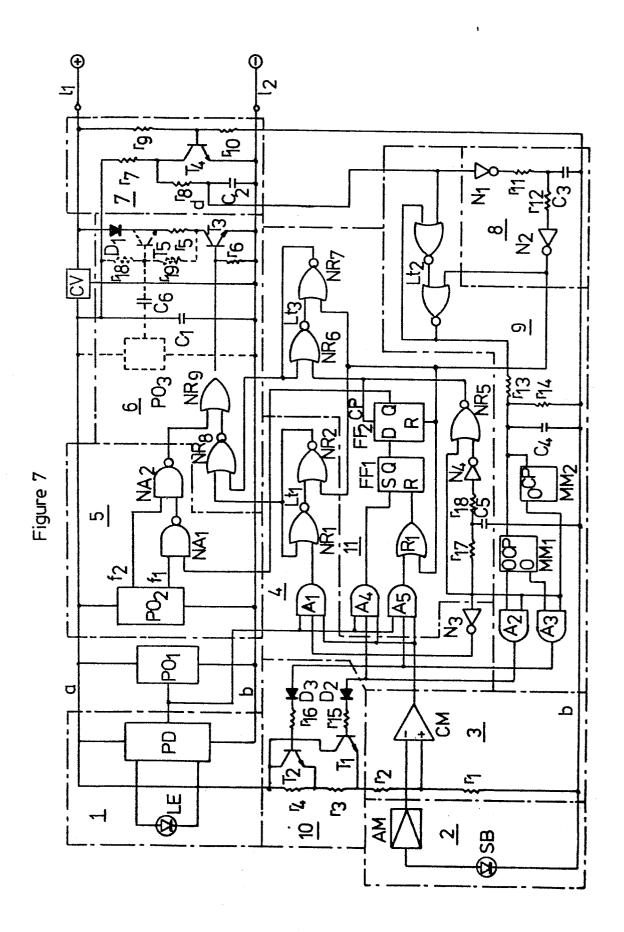

Figure 7 is a circuit diagram of another embodiment according to the present invention relating to a light extinction type smoke detector which detects smoke on light extinction principle. The circuit diagram of the control panel used for this embodiment is the same as Figure 2. The light extinction type smoke detector shown in Figure 7 only differs from Figure 1 in that the resistors  $\tau_1 \sim \tau_4$  are connected in series across the conductors a, b in opposite order to determine the upper level  $L_1$  of the normal level range as threshold level at which alarm failure or delayed alarm is likely to occur,

a lower level  $L_2$  as threshold level at which false alarm is likely to be produced, and the fire level  $L_3$ , and that the voltage of operating level developing at the junction of the resistors  $r_1$  and  $r_2$  is applied to the + terminal of the comparator CM in the comparison part  $\underline{3}$  and the output of the amplifier AM in the light receiving part  $\underline{2}$  is led to the - terminal so that the comparator CM generates the detecting output when the output of the amplifier AM has fallen below the operating level. Therefore, as compared with the time chart of Figure 3 (A) of the embodiment shown in Figure 1, the normal supervisory state of this embodiment and the operating state of each part in case of fire only differs in the outputs of the amplifier AM in the light receiving part  $\underline{2}$  and of the comparator CM in the comparison part  $\underline{3}$  as shown in Figures (11) and (12). Therefore, these different outputs shown with Figures (11), (12) are extracted and indicated at the lower part of Figure 3 (A) as Figures (B) (11'), (12').

Now, operation of the embodiment is described with reference to Figures 3 (A) but (11), (12), and (B) (11'), (12'). With respect to Figure 3 (A) some descriptions have already been made, and only their summary is given hereunder. In normal supervisory condition without smoke the transistor  $T_1$  in the signal receiving circuit 7 is conducting and its output line d has no output as shown in the left part of Figure (3). Consequently, the outputs of the reset signal generating circuit 8 and of the AND gates  $A_2$ ,  $A_3$  in the timer circuit 9 are L level, and the transistors  $T_1$ ,  $T_2$  in the operating level changeover circuit 10 do not conduct. As the operating level of the comparator CM in the comparison part 10 is at the fire level 10 (e.g. 10 85% light transmittivity of the output of the amplifier AM as indication of light transmittivity while

no smoke presents), the comparator CM has the L level output shown in Figure (12') and the output of the AND gate A, is at the L level when the amplifier AM generates a pulse signal exceeding the level L, shown in Figure (11'). Consequently, no signal is sent to the lines 1, 12. Nevertheless, when the amplifier AM has generated a pulse signal below the fire level as shown Figure (11') as a result of entry of smoke from fire between the light emitting element LE in the light emitting part l and the light receiving element SB in the light receiving part 2, the comparator CM has the H level output as shown in Figure (12'), with which and the synchronizing signal from the oscillator PO, and the H level output of the NOT gate No, the AND gate A<sub>1</sub> in the fire detecting part 4 generates a pulse signal corresponding to the output of the comparator CM. Then, the latch Lt, formed by the NOR gates NR, NR2 is set as shown in Figure (13). With the H level output of the NOR gate NR2, a fire signal with frequency  $f_2$  shown in Figure (2) is sent to the lines  $l_1$ ,  $l_2$  through the signal transmission circuit 6. Operation of the control panel after receipt of this fire signal and resetting of the fire detector by reset signal from the control panel are same as in the case of the light scattering type smoke detector.

Operation of each part at the time of the test while the output of the amplifier AM in the light receiving part 2 of this embodiment only differs in Figure (11) showing the output of the amplifier AM in the light receiving part 2 and Figure (12) showing the output of the comparator CM in the comparison part 3 as compared with the time chart, Figure 4 (A) for the embodiment shown in Figure 1. Therefore, only these different outputs shown with Figures (11), (12) are extracted and indicated at the lower part of Figure 4 (A) as Figure (B) (11'), (12').

Now, operation of the embodiments is described with reference to Figures 4 (A) but (11), (12), and (B) (11'), (12'). With the test start signal  $P_1$  shown in Figure (2) from the control panel the signal receiving circuit  $\overline{P}_1$  generates a pulse output  $P_1$ ' shown in Figure (3) in its output line d, but the reset signal generating circuit  $\overline{P}_1$  does not generate the clear signal due to the narrow pulse width. The pulse signal  $P_1$ ' sets the latch  $P_1$  formed by NOR gates  $P_1$  in the timer circuit  $P_1$ . With the H level output of the NOR gate  $P_1$  shown

in Figure (5) the capacitor C4 is charged as shown with the dotted line in Figure (5). As the voltage of the capacitor C4 reaches the H level, the clock signal is transmitted to the CP terminals of the monostable multivibrators MM1, MM2. Then, the Q terminals of the monostable multivibrators MM1, MM2 have H level outputs as shown in Figures (6), (7), with which the output of the AND gate A2, too, become the H level as shown in Figure (8), and the transistor T<sub>1</sub> in the operating level changeover circuit 10 becomes conductive. The operating level of the comparator CM in the comparison part 3 becomes the upper level L, of the normal level range (e.g. 105% light transmittivity) as shown with the dotted line in Figure (11'). Under this condition, if the pulse output of the amplifier AM in the light receiving part 2 lies between the upper level L1 and the lower level L2 of the normal level range as shown in Figure (11'), the pulse output is below the operating level of the comparator CM. Therefore, the comparator CM has no L level output, but H level output as shown in Figure (12'). With this H level output and the synchronizing signal from the oscillator PO; and the H level output of the AND gate A2, the AND gate A4 generates a pulse output which is similar to that shown in Figure (12). By this pulse signal the output of the Q terminal of the flip-flop circuit FF; in the function discriminating circuit 11 is set at H level. However, since no clock signal is transmitted from the NOR gate  $NR_5$  to the CP terminal of the flip-flop circuit  $FF_2$ , the output of the Q terminal remains at L level as shown in Figure (15): After lapse of a predetermined time the output of the Q terminal of the monostable multivibrator MM, in the timer circuit 9 becomes L level as shown in Figure (6), and the output of the Q terminal becomes H level. The outputs of the AND gates A2 and A3 become L and H levels respectively as shown in Figures (8) and (9). In the operating level changeover circuit 10, the transistor T<sub>1</sub> stops conducting and the transistor T<sub>2</sub> become conductive, thus the operating level of the comparator CM in the comparison part 3 becomes the lower level  $L_2$  of the normal level range. Under this condition, the output of the amplifier AM in the light receiving part 2, if generated, is above the level L2, and therefore the output of the comparator CM becomes the L level as shown in Figure (12'). When the output of the monostable multivibrator MM2 in the timer circuit 9 become L level as shown in Figure (7) after lapse of a predetermined

time, this L level output and the L level output of the NOT gate N<sub>4</sub> in the function discriminating circuit 11 cause the NOR gate NR<sub>5</sub> to generate the clock signal c as shown in Figure (16). With this signal c the flip-flop circuit FF<sub>2</sub> has the H level output shown in Figure (15) at the Q terminal. With this H level output and the H level output shown in Figure (17) of the NOR gate NR<sub>7</sub> of the latch Lt<sub>3</sub> which is set by the clock signal c, the normal signal shown in Figure (2) is sent to the lines 1<sub>1</sub>, 1<sub>2</sub> through the signal generating circuit 5 and the signal transmission circuit 6. As the signal receiving circuit 7 receives from the control panel the reset signal P<sub>2</sub> shown in Figure (2), each part of the fire detector returns to its original state in the same manner as the light scattering type smoke detector.

Operation of each part at the time of the test in case the output of the light receiving element SB in the light receiving element 2 has increased due to influence of the external light and the output of the amplifier AM has exceeded the upper level L<sub>1</sub> of the normal level range only differs in Figure (11) showing the output of the amplifier AM and Figure (12) showing the output of the comparator CM in the comparison part 3 as compared with the time chart, Figure 5 (A) for the embodiment shown in Figure 1. Therefore, only these different outputs shown in Figures (11), (12) are extracted and indicated at the lower part of Figure 5 (A) as Figure (B) (11'), (12').

Now, operation of the embodiment is described with reference to Figure 5 (A) but (11), (12), and to Figures (B) (11'), (12'). With the test start signal P<sub>1</sub> shown in Figure (2) the signal receiving circuit 7 generates a pulse output P<sub>1</sub>' shown in Figure (3) in its output line d, but the reset signal generating circuit 8 does not generate a clear signal due to the narrow pulse width. The pulse signal P<sub>1</sub>' sets the latch Lt<sub>2</sub> formed by NOR gates NR<sub>3</sub>, NR<sub>4</sub> in the timer circuit 9. With the H level output of the NOR gate NR<sub>4</sub> shown in Figure (5), the H level outputs shown in Figures (6), (7) appear on the Q terminals of the monostable multivibrators MM<sub>1</sub>, MM<sub>2</sub>, and the output of the AND gate A<sub>2</sub> becomes H level, and the transistor T<sub>1</sub> in the operating level changeover circuit 10 becomes conductive as shown in Figure (8). Thus, the operating level of the comparator CM becomes the upper level L<sub>1</sub> of the normal level range as shown with the dotted line in Figure (11'). Under this condition, if the output of the amplifier AM in

The light receiving part 2 is above the upper level L<sub>1</sub>, the comparator CM in the comparison part 3 has no output as shown in Figure (12'), and The transistors T<sub>1</sub>, T<sub>2</sub> in the operating level changeover circuit 10 become conductive as shown in Figures (8), (9). Therefore, even if the operating level of the comparator CM has changed from the level L<sub>1</sub> to the level L<sub>2</sub>, the comparator CM has no output. After lapse of a predetermined time the output of the Q terminal of the monostable multivibrator MM<sub>2</sub> becomes L level as shown in Figure (7). The NOR gate NR<sub>5</sub> in the smoke detecting function discriminating circuit 11 generates the clock signal c shown in Figure (16), and the NOR gate NR<sub>7</sub> has the H level output as shown in Figure (17). The output of the NOR gate NR<sub>8</sub> in the signal transmission circuit 6 becomes L level. Then, the NOR gate NR<sub>9</sub> generates a pulse output with frequency f<sub>2</sub> as shown in Figure (21) to send the abnormal signal to the lines l<sub>1</sub>, l<sub>2</sub> as shown in Figure (2).

Operation of each part at the time of the test in case the output of the amplifier AM has fallen below the lower level L<sub>2</sub> of the normal level range due to soiling of the light receiving surface of the light receiving element SB in the light receiving part 2 by dust only differs in Figure (11) showing the output of the amplifier AM and Figure (12) showing the output of the comparator CM as compared with the time chart, Figure 6 (A) for the embodiment shown in Figure 1. Therefore, only these different outputs shown in Figures (11), (12) are extracted and indicated at the lower part of Figure 6 (A) as Figures (B) (11'), (12').

Now, operation of the embodiment is described with reference to Figure 6 (A) but (11), (12), and to Figures (B) (11'), (12'). With the test start signal P<sub>1</sub> shown in Figure (2) the signal receiving circuit 7 generates a pulse output P<sub>1</sub>' with narrow width shown in Figure (3) in its output line d, but the reset signal generating circuit 8 does not generate a clear signal. The latch Lt<sub>2</sub> formed by NOR gates NR<sub>3</sub>, NR<sub>4</sub> is set. With the H level output of the NOR gate NR<sub>4</sub> shown in Figure (5) the H level outputs shown in Figures (6), (7) appear on the Q terminals of the monostable multivibrators MM<sub>1</sub>, MM<sub>2</sub>, and the output of the AND gate A<sub>2</sub> becomes H level, and the transistor T<sub>1</sub> in the operating level changeover circuit 10 becomes conductive as shown in Figure (8). Thus, the operating level of the comparator

CM becomes the upper level L1 of the normal level range as shown with the dotted line in Figure (11'). If the output of the amplifier AM in the light receiving part 2 is below the lower level L2 of the normal level range at this time, the comparator CM has no L level output but the H level output as shown in Figure (12'). With this H level output the AND gate A4 in the function discriminating circuit 11 generates a pulse output similar to that shown in Figure (12). This pulse output sets the output of the Q terminal of the flip-flop circuit at H level as shown in Figure (14), but the output of the Q terminal of the flip-flop circuit FF2 remains at L level because no clock signal is transmitted to the CP terminal of the flip-flop circuit FF2. Under this condition, the transistor T2 soon becomes conductive in place of the transistor  $T_1$  as shown in Figure (9), and the operating level of the comparator CM changes to the level L2 as shown in Figure (11'). In this case, too, the output of the comparator CM is at H level, with which the AND gate As and OR gate  $R_{\mbox{\scriptsize 1}}$  successively generate H level outputs to the R terminal of the flip-flop circuit FF1, the Q output of which becomes the L level as shown in Figure (14). After lapse of a predetermined time as the output of the Q terminal of the monostable multivibrator  $\text{MM}_2$ becomes L level as shown in Figure (7), and the NOR gate NR, in the function discriminating circuit 11 generates the clock signal c as shown in Figure (16), the latch Lt, formed by NOR gates NR6, NR7 is set. Then, the NOR gate NR, has a H level output as shown in Figure (17), and the abnormal signal is transmitted to the control panel through the signal transmission circuit 6 and the lines 1, 12 in the same manner as described with regard to Figure 6 (A) for the light scattering type smoke detector.

Operation of the smoke detector when its signal receiving circuit  $\frac{7}{2}$  has received the reset signal  $P_2$  from the control panel after the test in case the output of the amplifier AM exceeded the upper level  $L_1$  of the normal level range and fallen below the lower level  $L_2$ , and operation of the control panel when tested with the test start signal from the control panel are same as in the case of the light scattering type smoke detector.

In the both cases of the light scattering type and light extinction type smoke detectors, if there is a trouble in the detector circuit or interruption of the lines  $l_1$ ,  $l_2$ , and neither normal signal nor abnormal signal from the detector reaches the control panel despite the lapse of the operating time of the timer T after the test start signal is sent from the control panel shown in Figure 2, the timer T operates and closes its contact t to operate the trouble indicator lamp La4, by which it is possible to know the trouble in the detector circuit or lines  $l_1$ ,  $l_2$ .

In the above embodiments, the descriptions are made with respect to such cases that the smoke detector and the control panel are connected by two lines which are commonly used as power supply lines and signal lines. However, in Figures 1 and 7 the terminal on the right side of the voltage stabilizing circuit CV may be disconnected from the line 1, and connected with a third line 1, which is exclusively used for power supply so that the power supply lines may be separated from the signal lines to avoid influence of the pulse signal width upon the voltage stabilizing circuit and to get a larger S/N ratio.

As can be seen from the above description, the photoelectric type smoke detector equipped with smoke detecting function test means according to this invention has such as advantage that with proper composition it is capable of automatically, readily and precisely checking, on the basis of the signal sent from the control panel through the lines connecting the smoke detector with the control panel, whether the output of the detector is within the normal level range which cause no false alarm, alarm failure nor delayed alarm, i.e. an important function of this type of detector, and of reporting to the control panel on results of the test through the same lines.

## 4. Brief Description of Drawings

Figures 1 and 7 are circuit diagrams of embodiments of the light scattering type and light extinction type smoke detectors equipped with smoke detecting function test means according to this invention.

Figure 2 is a circuit diagram of a control panel which is common to these two embodiments. Figures 3 through 6 are time charts showing operating status of each part of the embodiments shown with Figures 1 and 7 in different casses, i.e. Figure 3 (A) is the one for the embodiment of Figure 1 in normal condition and in case of fire, Figure 4 (A) is the one at the time of test while the output of the embodiment

shown in Figure 1 is within the normal level range, and Figures 5

(A) and 6 (A) are the ones at the time of tests in the cases that the output of the embodiment shown in Figure 1 is below the lower limit and above the upper limit of the normal level range. Figures 3 (B) through 6 (B) shown only outputs (11') and (12') of amplifier AM and comparator CM respectively which differ from those shown in Figures 3 (A) through 6 (A) in the time charts corresponding to Figures 3

(A) through 6 (A) of the embodiment shown with Figure 7.

| 1  | • • • • • • • • • • • • • • • • • • • • | Light emitting part                     |

|----|-----------------------------------------|-----------------------------------------|

| 2  | •••••                                   | Light receiving part                    |

| 3  | •••••                                   | Comparison part                         |

| 4  |                                         | Fire discriminating part                |

| 5  |                                         | Signal generating part                  |

| 6  |                                         | Signal transmission circuit             |

| 7  |                                         | Signal receiving circuit                |

| 8  |                                         | Reset signal generating circuit .       |

| 9  |                                         | Timer circuit                           |

| 10 | • • • • • • • • • • • • • • • • • • • • | Operating level changeover circuit      |

| 11 |                                         | Smoke detecting function discriminating |

|    |                                         | circuit                                 |

## Claims

- 1. A photoelectric smoke detector equipped with smoke detecting function test means which is characterized in that an operating level changeover circuit and a smoke detecting function discriminating circuit are provided to automatically changeover, with test start signal from a control panel, the operating level from the fire level to the upper and lower level of the normal level range of the received light within which no false alarm, alarm failure nor delayed alarm is caused, and to send a normal signal to the control panel when the light received is within the normal level range, and an abnormal signal to the control panel when the light received is out of the normal level range.

- 2. A photoelectric smoke detector equipped with smoke detecting function test means as set forth in Claim 1 wherein changeover of the operating level is done by changeover of another input value having the equivalent operating level to that of the comparator to the input side of which the output of the received light is applied.

- 3. A photoelectric smoke detector equipped with smoke detecting function test means as set forth in Claim 1 wherein the normal signal and abnormal signal are discriminated by difference in pulse frequencies of the pulse signals.

Figure 3

Figure 4

Figure 5

Figure 6

## **EUROPEAN SEARCH REPORT**

TEP 84102465.6

| DOCUMENTS CON                                                                                                                    | EP 84102465.6                                            |                          |                                                                             |

|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--------------------------|-----------------------------------------------------------------------------|

|                                                                                                                                  | vith indication, where appropriate,<br>evant passages    | Relevant<br>to claim     | CLASSIFICATION OF THE APPLICATION (Int. Cl. 7)                              |

|                                                                                                                                  |                                                          |                          |                                                                             |

| A EP - A2 - 0 0                                                                                                                  | 67 339 (SIEMENS)                                         | <sup>-</sup> 1           | G 08 B 17/10                                                                |

| * Page 1,<br>line 5 *                                                                                                            | line 1 - page 2,                                         |                          | G 08 B 29/00                                                                |

| ,                                                                                                                                |                                                          |                          |                                                                             |

| A <u>US - A - 4 37</u>                                                                                                           | 4 329 (SCHOENFELDER et al.)                              | 1                        |                                                                             |

| column 7                                                                                                                         | , lines 5-31;<br>, line 35 - column<br>18; fig. 8-11 *   |                          |                                                                             |

| A US - A - 4 30                                                                                                                  | 6 230 (FORSS et al.)                                     | 1                        |                                                                             |

|                                                                                                                                  | , line 33 - column<br>16; fig. 1-3 *                     |                          |                                                                             |

|                                                                                                                                  | - w -                                                    |                          |                                                                             |

|                                                                                                                                  |                                                          |                          | TECHNICAL FIELDS<br>SEARCHED (Int. Cl. <sup>3</sup> )                       |

|                                                                                                                                  |                                                          |                          |                                                                             |

|                                                                                                                                  |                                                          |                          | G 08 B 17/00                                                                |

| X.                                                                                                                               |                                                          |                          | G 08 B 29/00                                                                |

|                                                                                                                                  |                                                          |                          | G 08 B 26/00                                                                |

|                                                                                                                                  |                                                          |                          |                                                                             |

|                                                                                                                                  |                                                          |                          |                                                                             |

| ·                                                                                                                                |                                                          |                          |                                                                             |

|                                                                                                                                  |                                                          |                          |                                                                             |

|                                                                                                                                  |                                                          |                          |                                                                             |

|                                                                                                                                  |                                                          |                          |                                                                             |

|                                                                                                                                  | ·                                                        |                          |                                                                             |

| The present search report has                                                                                                    | s been drawn up for all claims                           |                          |                                                                             |

| Place of search Date of completion of the search                                                                                 |                                                          | 1                        | Examiner                                                                    |

| VIENNA 10-07-1984                                                                                                                |                                                          |                          | HAJOS                                                                       |

| CATEGORY OF CITED DOO  X: particularly relevant if taken alon Y: particularly relevant if combined document of the same category | E : earlier pate after the fil with another D : document | ent document<br>ing data | riying the invention<br>t, but published on, or<br>pplication<br>or reasons |

| A : technological background     O : non-written disclosure     P : intermediate document                                        | &: member of document                                    | the same pa              | tent family, corresponding                                                  |