(1) Publication number:

0 123 305

A2

(12)

#### **EUROPEAN PATENT APPLICATION**

(21) Application number: 84104516.4

(51) Int. Cl.<sup>3</sup>: B 41 F 13/12

(22) Date of filing: 20.04.84

(30) Priority: 25.04.83 US 488401

(43) Date of publication of application: 31.10.84 Bulletin 84/44

Designated Contracting States:

DE FR GB

(71) Applicant: QUAD/TECH

Pewaukee Wisconsin(US)

(72) Inventor: Quadracci, Thomas A. 2625 Almesbury Avenue Brookfield Wisconsin 53005(US)

72) Inventor: Kirby, Jerry L. 16640 Queen Ann Drive Brookfield Wisconsin 53005(US)

(72) Inventor: Sainio, Jeffrey W. 200 Millington, Apt. No. 2 Hartland Wisconsin 53029(US)

(72) Inventor: Reynolds, Bruce A. 1301D Camden Way Waukesha Wisconsin 53186(US)

(74) Representative: Lippert, Hans, Dipl.-Ing. et al, Reichel und Reichel Parkstrasse 13 D-6000 Frankfurt (Main) 1(DE)

(54) Register control system for a printing press.

(5) Optical scanners (18, 19) mount to a press (1 to 8) and provide information to a register control system (15, 16, 17, 20) which automatically maintains color-to-color register. The same information is processed to provide signals to a scanner

interface circuit (17) which controls the position of the optical scanners (18, 19) to insure that they track the register patterns on the moving web (6).

Croyden Printing Company Ltd

## Register control system for a printing press

The field of the invention is control systems for adjusting the color-to-color register on web offset presses, gravure presses and flexographic presses.

In both processes a web of material to be printed is driven through a series of cylinders which separately print an image on the web using inks of selected colors. The rotational and lateral position of each print cylinder is precisely aligned such that the register of the separate colors is maintained to provide an accurate and clear print image.

Numerous types of register control systems are employed in the art to maintain color-to-color register under a variety of operating conditions. These control systems are in most cases open loop systems in which an operator periodically examines the print image and manually enters correction values to adjust the lateral or rotational alignments of one or more print cylinders.

Closed loop register control systems have been

20 employed on gravure printing presses. In such control

systems a series of register marks is printed by each

print cylinder and an optical detector is positioned

after each print cylinder to detect these marks. The

timing of the electrical pulses produced by the optical

25 detector and the duration of each pulse provide position

feedback information indicative of the rotational and

lateral alignment of the print cylinder with respect to

the framework of the press. This position feedback

information is employed to automatically adjust the

30 register of the print cylinder with respect to the press

framework.

Prior closed loop register control systems have not been used on offset presses. The web on offset presses is not mechanically constrained after passing over each print cylinder, and as a result, an optical detector cannot accurately read a register mark.

Instead, such measurements must be made at the output of the press after all colors have been printed and the ink dried.

The present invention relates to a closed loop register control system in which a single optical scanner is employed to provide position feedback information that indicates the relative register of each print cylinder with respect to a designated reference print cylinder. Each print cylinder produces a specific 15 register mark which forms part of a register pattern. The feedback signal produced by the optical scanner as it reads the register pattern is analyzed to determine the lateral and rotational register of each print cylinder with respect to the reference print cylinder. 20 Register error signals are thus produced for each print cylinder and are employed to control motors that adjust the position of each.

A general object of the invention is to provide a closed loop register control system for an offset printing press. A single optical scanner may be employed and it is positioned at the output of the press where the moving web can be properly constrained to allow accurate detection of the register pattern.

Another object of the invention is to provide an accurate register control system. By measuring the relative register of each print cylinder with respect to the reference print cylinder rather than a timing signal related to press position, mechanical inaccuracies in the press gear train are eliminated.

Yet another object of the invention is to provide an accurate indication of register error which is not subject to spurious deviations. Each signature which is output by the press contains a register pattern and 5 thus discrete position feedback signals are generated at a high rate. Spurious position feedback signals are eliminated in a first analysis which rejects position feedback signals that indicate extraordinary register errors. The position error signal used for control 10 purposes is obtained by averaging a series of acceptable readings.

A more specific object of the invention is to enable the register control system to be easily configured to any press. The set-up procedure is an inter-15 active process in which the operator is prompted to enter the required data. Such data includes offset data for each color print cylinder to account for printing errors in the register pattern. The print cylinder which is to be used as the reference color is also identified during set-up.

20

25

The foregoing and other objects and advantages of the invention will appear from the following description. In the description, reference is made to the accompanying drawings which form a part thereof. and in which there is shown by way of illustration a preferred embodiment of the invention. Such embodiment does not necessarily represent the full scope of the invention, however, and reference is made therefore to the claims herein for interpreting the scope 30 of the invention.

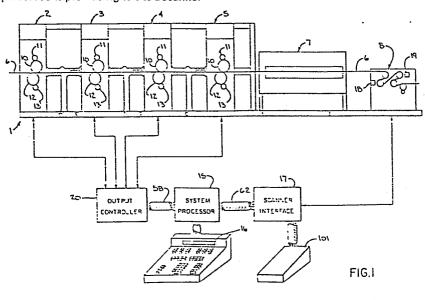

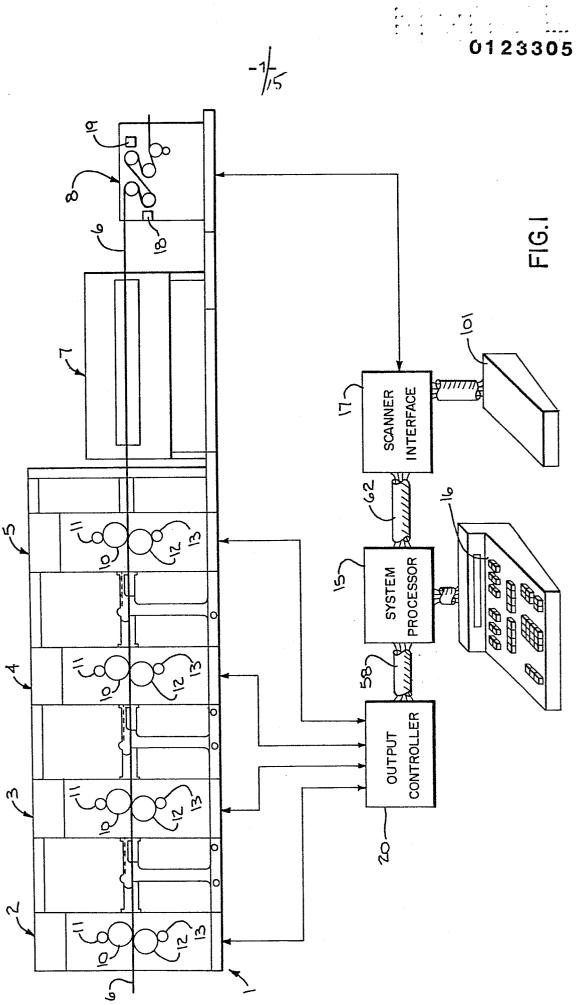

- F I G . 1 is a schematic drawing of a printing press which employs the register control system of the present invention;

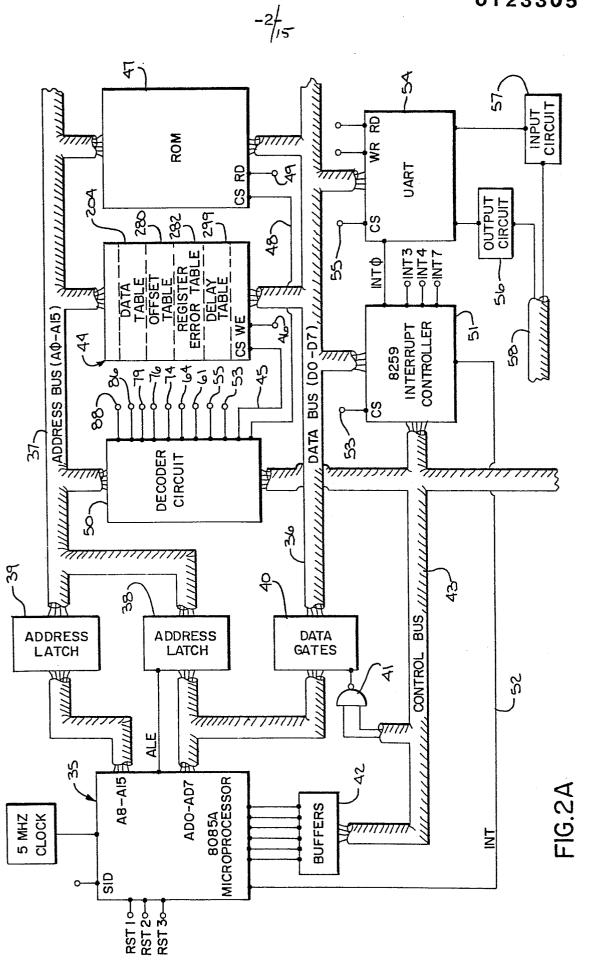

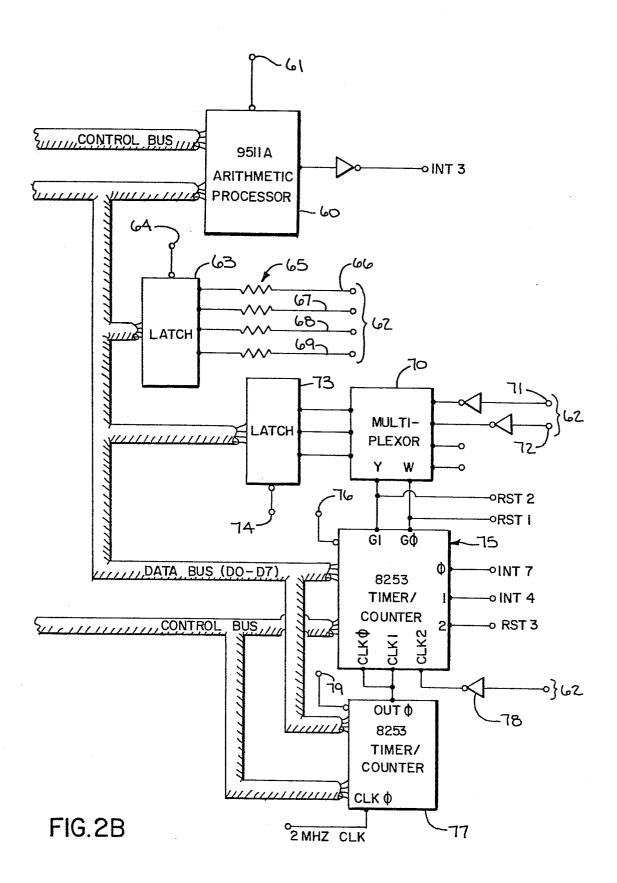

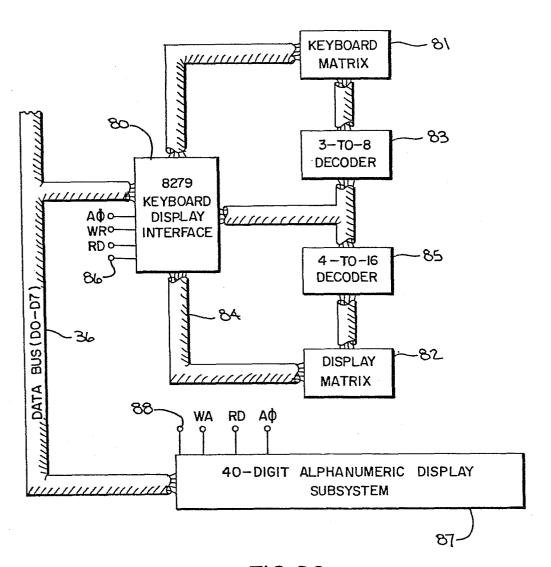

- FIG. 2A to 2C are electrical schematic diagrams of the system processor which forms part of the system of Fig. 1;

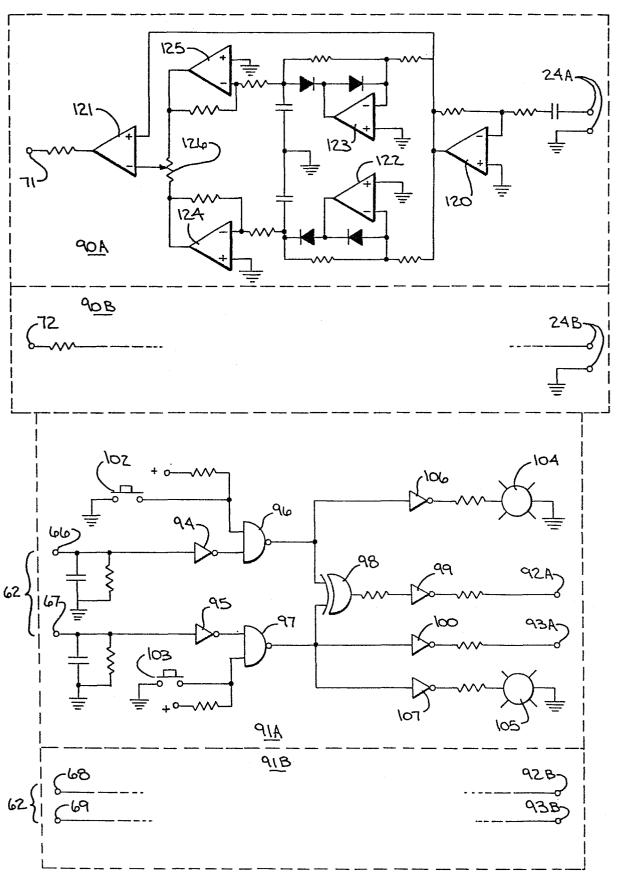

- FIG. 3 is an electrical schematic diagram of 10 the scanner interface which forms part of the system of Fig. 1;

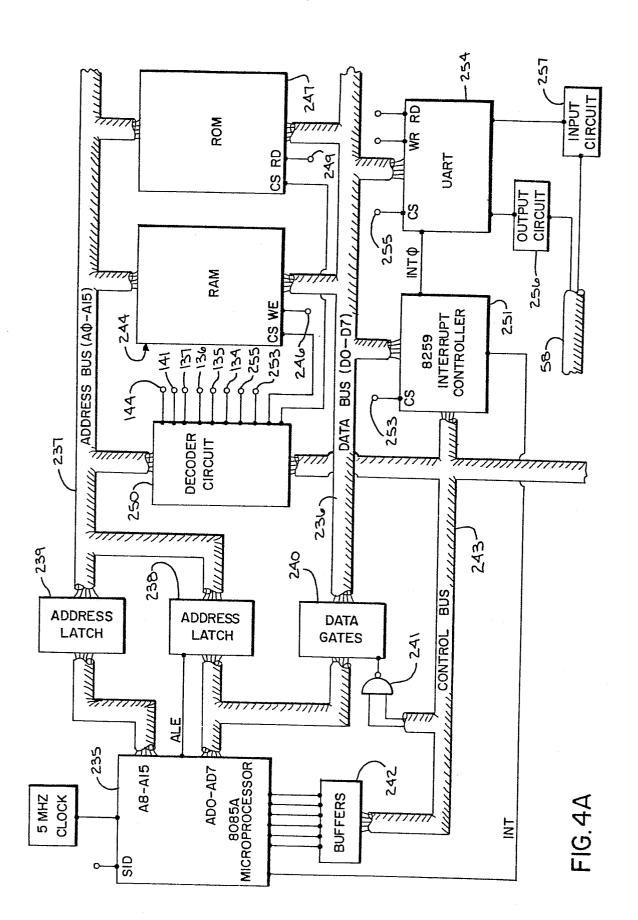

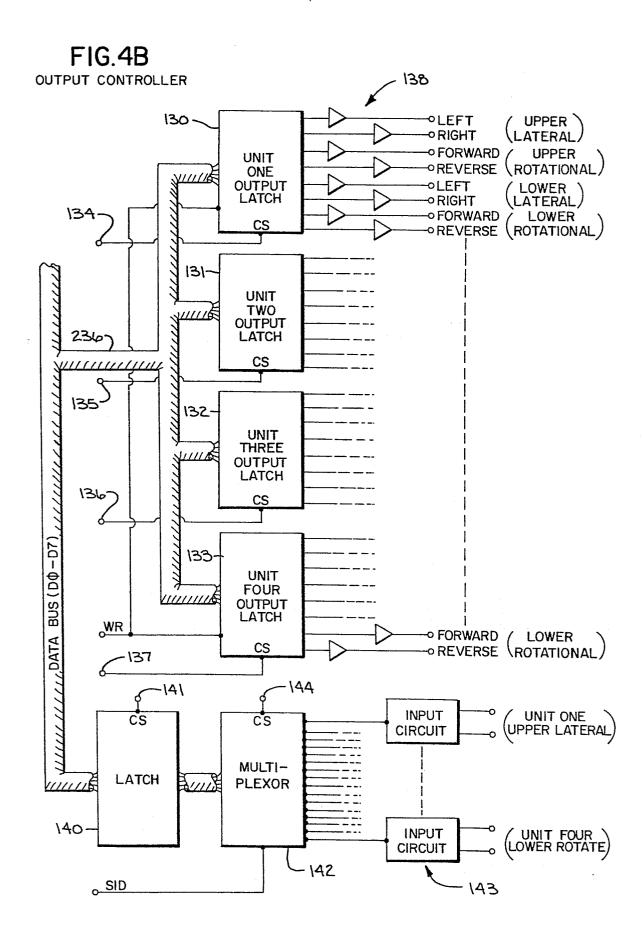

- F I G . 4A and 4B are electrical schematic diagrams of the output controller which forms part of the 15 system of Fig. 1;

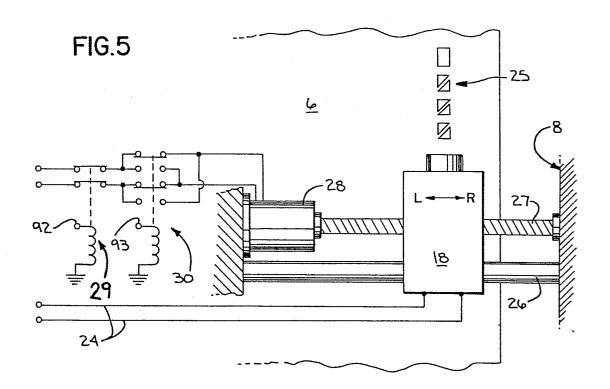

- FIG. 5 is a partial elevation view of an optical scanner which forms part of the system of Fig. 1;

20

30

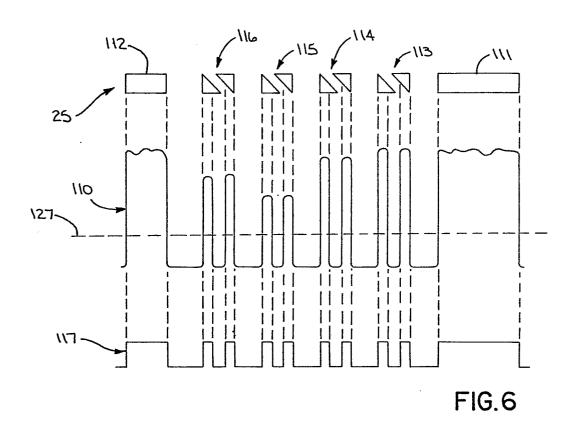

- FIG. 6 is a schematic representation of the register pattern and corresponding electrical signals which appear in the register control system;

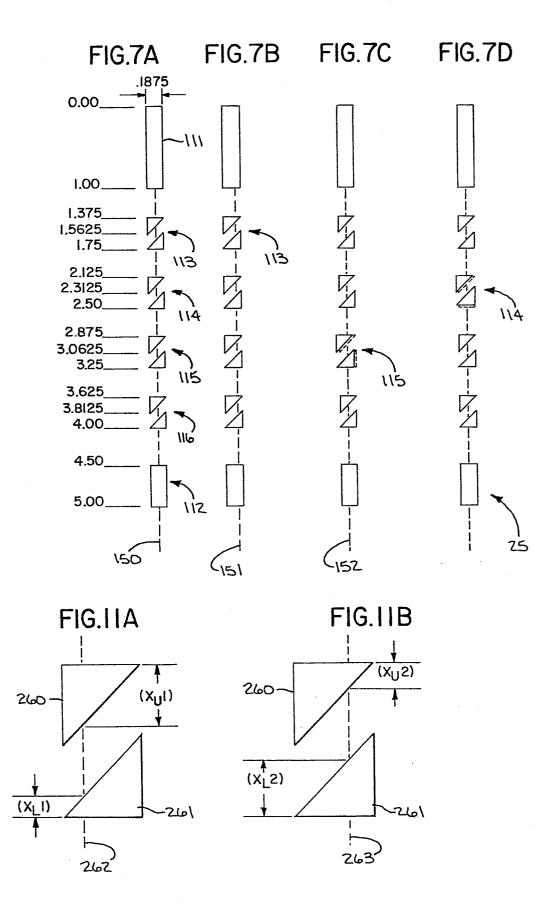

- FIG. 7A to 7D are schematic representations of register patterns illustrating types of misregister;

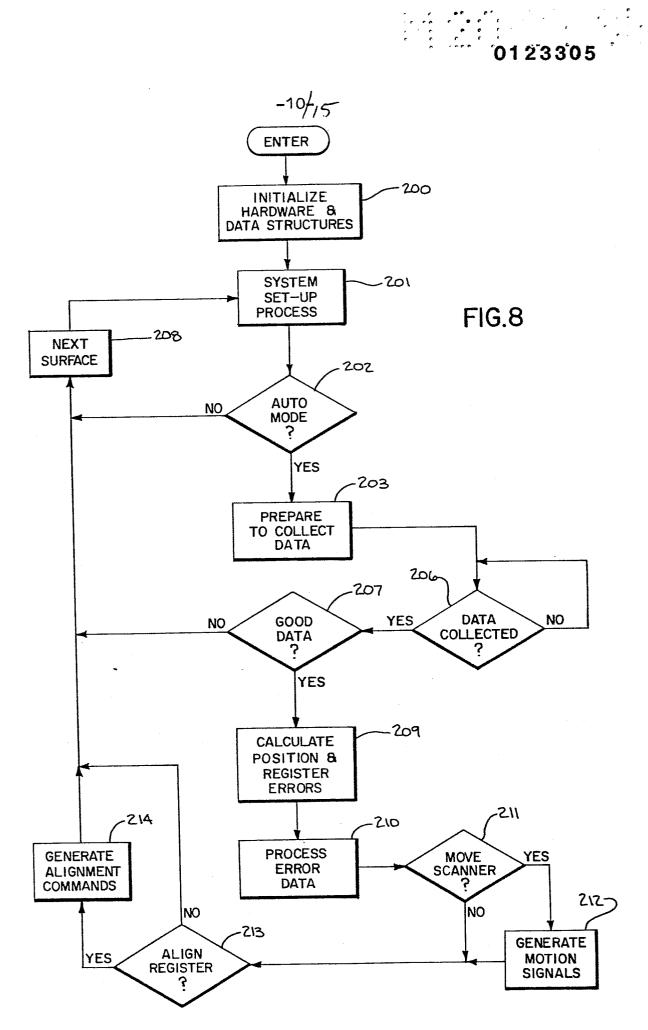

- F I G . 8 is a general flow chart of the manner in which the system processor of Fig. 2 operates;

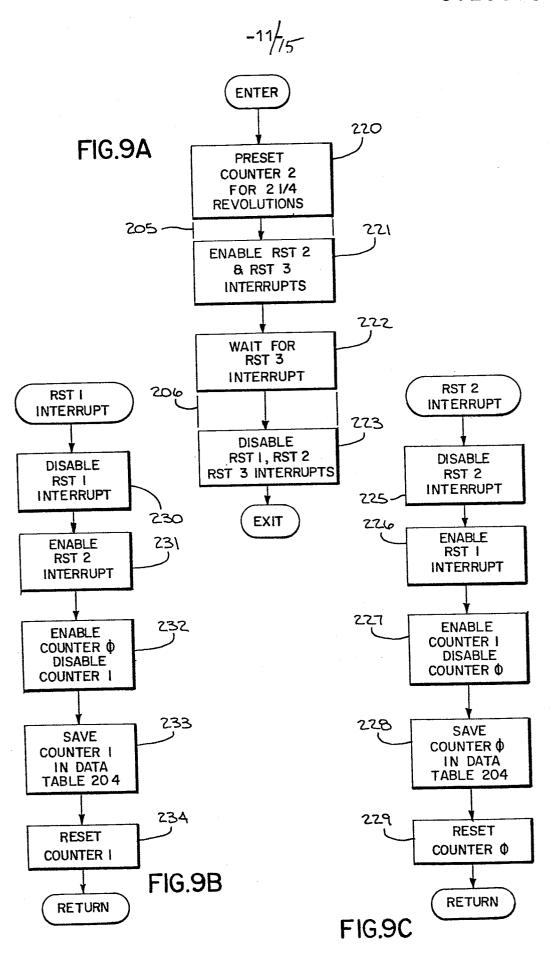

- FIG. 9A to C are flow charts of interrupt service routines executed by the system processor of Fig. 2;

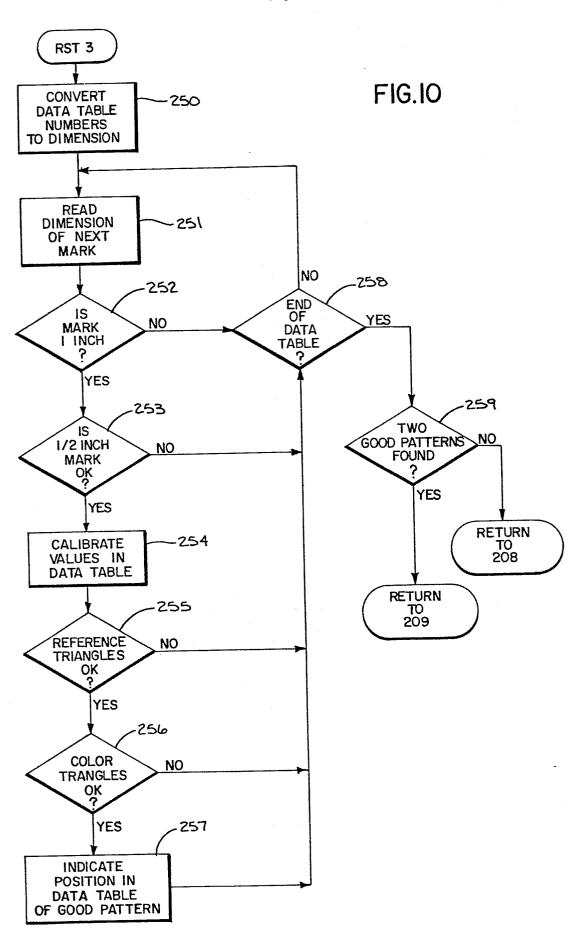

- FIG. 10 is a flow chart of an interrupt service routine executed by the system processor of Fig. 2;

- FIG. 11A to B are schematic representations of a portion of a register pattern;

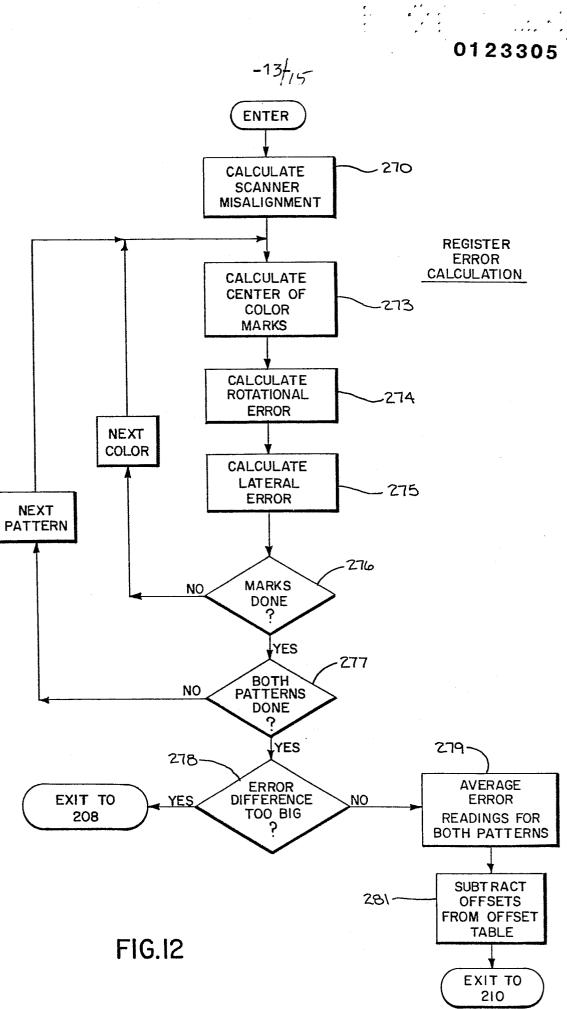

- FIG. 12 is a flow chart of the register error calculation routine executed by the system processor of Fig. 2;

- FIG. 13 is a portion of a register pattern; and

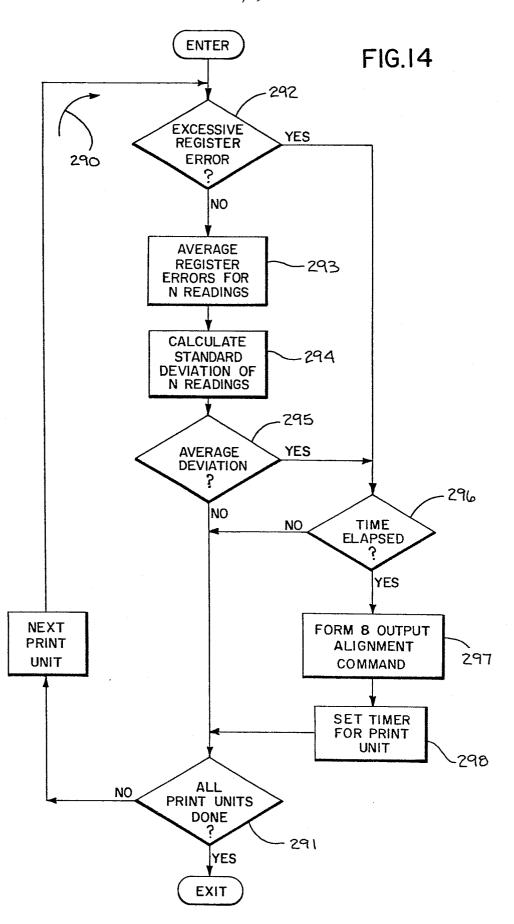

F I G . 14 is a flowchart of programs executed by the system processor of Fig. 2.

10

Referring particularly to Fig. 1, the present invention is applied to a web offset printing press 1 which includes four blanket-to-blanket printing units 2 to 5. A web 6 is fed through the successive printing 5 units 2 to 5 from a reel stand (not shown in the drawings) and it is then fed through a dryer unit 7 and a chill unit 8. The printed web 6 may then be guided through coating equipment (not shown) and folding equipment (not shown) which fold and separate the web into individual signatures.

Each printing unit 2 to 5 includes an upper printing couple comprised of an upper blanket cylinder 10 and upper plate cylinder 11, and a lower printing couple comprised of a lower blanket cylinder 12 and 15 lower plate cylinder 13. In a typical multicolor printing operation the printing unit 2 prints the color black on the top and bottom surfaces of the web 6, and subsequent printing units 3 to 5 print other colors on both surfaces of the web 6. Both the lateral and 20 rotational position of the upper plate cylinders 11 and lower plate cylinders 13 are separately controlled by electric motors to precisely register the separate color images.

10

In prior presses which employ the offset lithography 25 process register of the various colors is maintained manually. The pressman examines signatures at the output of the press and enters lateral and rotational offset values into a register control system which operates the proper electric motor. The maintenance of color 30 register in such systems requires the constant attention of the pressman during a typical run, since register is often lost due to a number of uncontrollable variables in the web material and the press hardware.

The present invention is a register control system 35 which automatically controls the register of the four printing units 2 to 5. It will become evident that while a four unit, single web, offset lithography

printing press is shown and described in this specification, that the present invention is applicable to other presses.

Referring still to Fig. 1, the register control 5 system includes a centrally located system processor 15 which is operated from a main control panel 16. mation regarding the register of the four printing units 2 to 5 is received by the system processor 15 from a scanner interface 17, which in turn connects to 10 a pair of optical scanner units 18 and 19 mounted in the chill unit 8. Based on the register information received from the scanner interface 17, the system processor 15 operates an output controller 20. output controller 20 operates in response to commands 15 from the system processor 15 to separately operate the motors which control the lateral and rotational alignment of the upper plate cylinder 11 and lower plate cylinder 13 in each of the four printing units 2 to 5. A closed loop register control system is thus formed.

20 Referring particularly to Figs. 1 and 5, the optical scanners 18 and 19 are slidably mounted to the frame of the chill unit 8 with one scanner 18 directed at the bottom surface of the web 6 and the other scanner 19 directed at the top surface. The scanners 18 and 19 25 may be mounted on other "downstream" equipment which provides good web support. The scanners 18 and 19 produce signals on lines 24 which are proportional in amplitude to the light reflected from the surface of the web 6. Each scanner includes a lens which focuses 30 on a small area of the web 6 and the scanners 18 and 19 are positioned to sense a register pattern 25 which is repeatedly printed along one edge of the web 6 by the printing units 2 to 5. The scanners 18 and 19 are mounted to read the register pattern 25 as the support-35 ing web 6 passes over a chill roller. As a result, the pattern 25 is relatively stable and an accurate reading

of register can be obtained.

The signal generated by each scanner 18 and 19 not only contains color register information, but also, information which indicates when the register pattern 5 25 has shifted laterally to the left or right of the focal point of the scanner. As shown in Fig. 5, the scanner 18 is mounted for translation along a slide 26 when a worm gear 27 is rotated by a scanner motor 28. The motor 28 is energized when a power relay 29 is 10 energized and the direction of travel is determined by the state of a direction relay 30. One of the functions of the register control system of the present invention is to operate the power relay 29 and direction relay 30 for each optical scanner 18 and 19 to maintain their 15 focal points near the center of the register patterns 25 which pass beneath. Thus the scanners 18 and 19 will "track" the register patterns 25 as the web 6 shifts laterally in the press.

20 Referring particularly to Fig. 2A, the system processor 15 is structured about an 8-bit microprocessor 35 which couples to an 8-bit bi-directional data bus 36 and a 16-bit address bus 37. During a read or write cycle, a least significant byte of address data 25 is output to a latch 38 when an ALE control line is active, and immediately thereafter the least significant byte of address data is output to an address latch 39. Data is either read from the data bus 36 through a set of bi-directional data gates 40 or out-30 put through the data gates 40 to an addressed device coupled to the data bus 36. The direction of data flow through the gates 40 is determined by the microprocessor control lines, RD and INTA, which connect to a NAND gate 41 through a set of buffers 42. control lines along with the remaining microprocessor 35 control lines (CLKOUT, WR, IO/M, RST ) form a control

bus 43 which connects to a number of system elements.

A random access, read/write memory (RAM) 44 connects to the address bus 37 and data bus 36. As will be explained in more detail hereinafter, the RAM 5 44 stores a variety of data structures which are employed by the register control system and which may be separately read into the microprocessor 35 for processing or which may be altered by a write operation. A chip select control line 45 enables the RAM 44 and a 10 memory write control line 46 determines whether a read or write operation is performed. The processor 15 also includes a read-only memory (ROM)47 which stores machine language program instructions and constants. 47 is enabled when a chip select control line 48 is 15 active and addressed data is read therefrom when a memory read control line 49 is active. The program instructions which direct the operation of the microprocessor 35 are sequentially read from the ROM 47 and executed to control the operation of the system 20 processor 15.

A decoder circuit 50 connects to the address bus 37 and control bus 43. The decoder circuit 50 includes 2-to-4 and 3-to-8 decoder circuits along with associated gates which generate chip select signals to the various system elements. These include the RAM control line 45 and ROM control line 48 which are enabled when an address whithin their range appears on the address bus 37.

Referring still to Fig. 2A, an interrupt control30 ler circuit 51 connects to the data bus 36 and control

bus 43. The interrupt controller 51 accepts interrupt

requests generated on four lines INT, INT, INT4 and

INT7, determines which request has the highest priority, determines whether the incoming request has a

35 higher priority than the process currently being

serviced, and issues an interrupt through INT control

line 52 to the microprocessor 35 based on this determination. An 8259 programmable interrupt controller manufactured by Intel Corporation is employed and it is enabled to receive control data from the data bus 36 by a control line 53 which is driven by the decoder circuit 50.

A universal asynchronous receiver/transmitter (UART) 54 generates one of the interrupt requests (INTo) whenever it receives or transmits a character. 10 The UART 54 connects to the data bus 36 and it is enabled through a control line 55. A character may be output through the UART 54 for transmission through a serial output circuit 56 or a character may be input serially through input circuit 57 and read from the The circuits 56 and 57 interface the UART 54 15 UART 54. to a serial data link 58 which connects to the output controller 20. The UART 54 serves as the means for outputting control data over a substantial distance, and the system processor 15 may thus be centrally 20 located while the output controller 20 may be located adjacent the printing press 1.

Referring particularly to Figs. 2A and 2B, the system processor 15 includes an arithmetic processor 60 for performing high speed arithmetic functions. 25 The processor 60 is enabled by the decoder circuit 50 through a control line 61 and data may be written to it for processing. A 9511A processor manufactured by Advanced Devices, Inc. is employed, and when an answer is ready, the processor 60 generates an interrupt 30 request to the interrupt controller 51 through the INT3 control line. When the interrupt is serviced by the microprocessor 35, it is vectored to a service routine which directs the microprocessor 35 to read the arithmetic result from the arithmetic processor 60 35 and set a flag in RAM 44 which indicates that the arithmetic processor is available for further computations.

Referring particularly to Figs. 1 and 2B, the system processor 15 receives data from the scanner interface 17 and outputs data to the scanner interface 17 through a parallel I/O bus 62. Four bits of output data are stored in a latch 63 when a chip select control line 64 is driven low by the decoder circuit 50. This 4-bit nibble is coupled through resistors 65 to corresponding leads 66 to 69 in the I/O bus 62. As will be explained in more detail below, this data indicates if either of the optical scanners 18 or 19 are to be repositioned, and if so, in which direction.

Three bits of data are input from the scanner Two of these are received at two inputs interface 17. of a multiplexer 70. These two input signals 71 and 72 15 are digital representations of the signals generated by respective optical scanners 18 and 19 as the register patterns 25 pass beneath them. One of these two signals is selected for analyses by the multiplexer 70 which has its select terminals connected to the out-20 puts of a latch 73. By enabling the latch 73 through chip select line 74, the microprocessor 35 can write a code to the latch 73 which selects either of the two scanner signals 71 or 72. The selected scanner signal appears at a "Y" output on the multiplexer 70 and its 25 inversion appears at a "W" output. The selected scanner signal is applied directly to RST1 and RST2 inputs on the microprocessor 35 and to gate inputs Go and G1 on a timer/counter circuit 75.

Referring still to Fig. 2B, the timer/counter 75

30 is a programmable device which receives data through

the data bus 36 when a chip select control line 76 is

active. It contains three counters which are preset

to given values and which are decremented by pulses

received at clock inputs CLK¢, CLK1 and CLK2. The

35 clock inputs CLK¢ and CLK1 are driven by the output of

a second timer/counter 77, and the third clock input

CLK2 is driven by a gate 78 which receives a press speed feedback signal in the form of a pulse stream produced by a shaft encoder. An RST3 control line is enabled when the internal counter driven by the speed feedback signal (CLK2) reaches its terminal count, and this event is employed by the microprocessor 35 to sense press speed.

The other two counters in the timer/counter 75 generate interrupt requests INT7 and INT4 when their 10 terminal counts are reached. Only one of these counters is operated at any single moment, since the gate inputs G1 and Go are always in opposite logic states. example, when the scanner signal at the multiplexer output "Y" is high, counter 1 is enabled through gate The logic low voltage at the "W" output disables counter of through gate Go and it generates a reset request to the microprocessor 35 through control line RST1. In response the microprocessor 35 reads the value of counter of and resets to a preselected value. When 20 the multiplexer outputs Y and W change logic state the reverse is true. Counter & becomes active and counter 1 is stopped. The reset request on RST2 vectors the microprocessor 35 to a program which reads the value of counter 1 and presets it for the next cycle. 25 timer/counter 75 is thus employed to measure the duration of each light and dark portion of the register pattern 25 as it passes beneath the optical scanner 18 or 19. These measured intervals are employed by the microprocessor 35 to determine the register of each 30 printing unit 2 to 5 as will be described in more detail below.

Referring particularly to Figs. 1 and 2C, the last section of the system processor 15 interfaces with the main control panel 16. This interface includes a keyboard/display interface circuit 80 which connects to the data bus 36 and to a number of control lines in the

bus 43. A model 8279 integrated circuit manufactured by Intel, Inc. is employed and it is programmed with control data from the microprocessor 35 to scan a keyboard matrix 81 and to maintain a display matrix 82.

5 The keyboard matric includes a variety of control panel switches which are arranged in an eight-by-eight matrix. The interface circuit 80 outputs a sequence of three-bit codes to a 3-to-8 decoder 83 and inputs a corresponding sequence of eight bytes of keyboard data through a

10 bus 84. The state of up to sixty-four keys are stored in a keyboard image table inside the interface 80, and this table may be read by the microprocessor 35. Similarly, an output image table is written to the interface circuit 80 by the microprocessor 35 and the

15 keyboard/display interface 80 operates to output this data in sequence through an eight-bit bus 84 to the display matrix 82. The display 82 is comprised of individual lamps arranged in an eight-by-sixteen matrix with the sixteen rows being sequentially selected by a 20 4-bit code applied to a 4-to-16 decoder circuit 85.

The control panel 16 also includes a 40-digit alphanumeric display subsystem 87 which connects to the data bus 36 and control bus 43. A display subsystem model DE/240 manufactured by Digital Electronics Corporation is employed and it is enabled through a control line 88 by the decoder circuit 50. ASCII characters, including control characters, may be output to the display 87 and an internal cursor determines where the next ASCII character will appear. This cursor may be moved by outputting ASCII control characters to the display 87.

Referring particularly to Figs. 1, 3 and 5, the scanner interface 17 couples information between the optical scanners 18 and 19 and the system processor 15.

The scanner interface 17 includes a pair of identical input circuits 90A and 90B and a pair of identical output

circuits 91A and 91B. The output circuit 91A connects to the output port leads 66 and 67 in the I/O bus 62 and its output terminal 92A and 93B connect respectively to the scanner motor relay 29 and the scanner motor direc-5 tion relay 30. When a logic high voltage appears on lead 66 the scanner 18 is to be moved left, and when a logic high voltage appears on lead 67, it is to be moved to the right. These signals are applied through inverter gates 94 and 95 to respective NAND gates 96 and 97, and 10 the NAND gates 96 and 97 drive the inputs of an exclusive OR gate 98. The OR gate 98 energizes the scanner motor on/off relay 29 through an inverter gate 99 when motion in either direction is indicated. The output of NAND gate 97 provides a direction indication which is 15 coupled through inverter gate 100 to energize or deenergize the scanner motor direction relay 30.

Referring particularly to Figs. 1 and 3, the scanners 18 and 19 can also be positioned manually using a remote control panel 101 which connects to the scanner 20 interface 17. This manual mode of operation is used primarily during start-up to orient the scanners 18 and 19 for automatic operation. The panel 101 includes a pair of pushbutton switches 102 and 103 which connect to inputs on respective NAND gates 96 and 97. 25 depressing the pushbutton 102 the operator can move the scanner 18 to the left and by depressing pushbutton 103 the scanner 18 moves to the right. The panel 101 also includes a pair of indicator lamps 104 and 105, one of which is energized when the optical scanner 18 is moved 30 in either direction. The lamps 104 and 105 are driven by inverter gates 106 and 107 which connect to the outputs of NAND gates 96 and 97.

Referring particularly to Fig. 3, the input circuit 90A of the scanner interface 27 receives an analog electrical signal through the leads 24A from the optical scanner 18 and generates a corresponding digital signal

35

to the system processor 15 through lead 71. As shown in Fig. 6, as the register pattern 25 passes beneath the optical scanner 18, an analog signal 110 is produced. The register pattern 25 includes reference portions 111 5 and 112 which are printed by one of the printing units 2 to 5 along with reference color marks 113. reference color is preferably black because it produces a strong output signal from the optical scanner 18. Additional colors, indicated by color marks 114 to 116, may be printed by the remaining printing units, and the amplitude of the scanner output signal which they produce will depend on the color of the ink. The scanner interface 17 converts this analog signal 110 to a corresponding logic level signal 117 for input to the 15 system processor 15.

Referring still to Fig. 3, the analog input signal 110 is received through leads 24 and amplified by operational amplifier 120. The output of amplifier 120 is applied directly to one input of a comparator 121 20 and to the inputs of a positive precision peak detector formed around amplifier 122 and a negative precision peak detector formed around amplifier 123. The outputs of the peak detectors 122 and 123 are buffered by amplifiers 124 and 125 and summed at potentiometer 126. 25 The reference signal produced at potentiometer 126 is applied to the inverting input of the comparator 121, and it serves as a voltage level which is proportional to approximately twenty percent of the peak signal produced by the optical scanner 18. As shown in Fig. 6, 30 this reference level is indicated by dashed line 127 and it is well below the minimum signal produced by any colored mark in the register pattern 25. The comparator 121 is thus driven sharply into and out of saturation to produce the digitized output signal 117 35 on the lead 71.

Referring particularly to Figs. 1 and 4A, the output controller 20 receives command data from the system processor 15 through the serial data link 58 and operates the motors which control the register for each printing 5 unit 2 to 5. As shown in Fig. 4A, the output controller 20 is microprocessor-based and includes many of the same circuit elements as the system processor 15. Indeed. these same elements are indicated with the same reference numbers as in Fig. 2A, but with the prefex "2" to distinguish them from the corresponding system processor elements. Although the RAM 244 and ROM 247 are the same as the corresponding elements in the system processor, it can be appreciated that the data structures and programs stored therein are different and that their size need not be the same. 15

Referring particularly to Fig. 4B, the input/output section of the output controller 20 is substantially different than that of the system processor 15. includes a set of four 8-bit latches 130 to 133 which 20 connect to the data bus 236 and which are separately enabled through chip select lines 134 to 137 driven by the decoder circuit 250. An 8-bit byte of data may be written to a selected latch 130 to 133 when a write control line WR is driven low. The outputs of each latch 130 to 133 are connected through line drivers 138 to relays which operate the register control motors on each printing unit 2 to 5. For example, the latch 130 drives the four motors (upper lateral, upper rotational lower lateral and lower rotational) on the first 30 printing unit 2. If the top print image for unit 2 is to be advanced, the upper rotational motor is energized in the forward direction by outputing a logic "1" to the bit 3 position of latch 130. When the adjustment has been made, a logic "O" is output to de-energize the same motor. 35

The status of the four register control motors in each printing unit 2 to 5 is also continuously monitored by the output controller 20. Referring again to Fig. 4B, a 4-bit latch 140 connects to the data bus 236 and is enabled through a chip select line 141 to apply a 4-bit code to the select inputs of a The sixteen inputs on the multiplemultiplexor 142. xor 142 connect to input circuits 143 which receive signals from each register control motor on the press 1 indicating whether or not the motor is energized. When a chip select line 144 is enabled, one of the sixteen inputs to the multiplexor 142 is selected and the signal thereon is applied to a serial input port SID on the microprocessor 235. By sequentially writing different codes to the latch 140 and enabling the multiplexor 142, the microprocessor 235 can scan the state of the register control motors and transmit a two-byte status message to the system processor 15 through the serial data link 58.

10

15

20 It should be apparent that a number of variations are possible in the hardware of the preferred embodiment. Although the system could be formed as a single microprocessor-based unit, it is physically convenient to separate the output controller from the centrally 25 located system processor 15 in most installations. output controller 20 is usually located on the press 1 with other press control electronics. Also, the hardware disclosed herein is shown controlling four printing units for a single web 6. However, it may be more economical in some installations to use the same system 30 processor to control register on additional printing units for additional webs. Indeed, the system processor 15 and output controller 20 disclosed herein have been employed to control register for both sides of 35 two webs, or in other words, eight printing units and four optical scanners.

Before discussing in detail the operation of the register control system, it is helpful to discuss the manner in which the register marks 111 to 116 in the register pattern 25 are employed to control color-tocolor register. Referring to Figs. 6 and 7A, when register is perfect and the optical scanner is positioned to focus at the center (dashed line 150) of the register pattern 25 as it passes by, a series of voltage pulses are produced as shown at 110. Each register mark 113 to 116 is comprised of two triangu-10 lar sections that produce two voltage pulses of equal time duration. If the focal point of the scanner is not centered as shown by the dashed line 151 in Fig. 7B. the two pulses produced by the reference mark 113 are not of equal duration. When this condition is sensed by the system processor 15, it outputs signals to the scanner interface 16 which reposition the optical scanner 18 or 19 at the center of the pattern. Thus, if the web 6 shifts laterally as it passes through the 20 dryer 7 and chill unit 8, the optical scanners 18 and 19 will automatically track the movement.

Referring particularly to Figs. 1 and 7C, if the print unit 4, for example is misregistered in the lateral direction, the register mark 115 which it produces will not be properly aligned. With the optical scanner properly centered as indicated by dashed line 152, the two voltage pulses produced by the register mark 115 will be unequal in duration. If the misregister is to the left as shown, the first pulse will be shorter, and if the misregister is to the right, the second voltage pulse will be shorter. Either situation is sensed by the system processor 15 which monitors the scanner waveform 117 (Fig. 6) and which outputs corrective commands to the output controller 20 to move the print cylinder back into register.

25

30

35

Referring to Figs. 1 and 7D, if the printing unit 3 is misregistered in the rotational direction, the register mark 114 which it produces will not be properly aligned in the register pattern 25. More specifically, 5 the two voltage pulses produced by the register mark 114 are either advanced or delayed relative to the remainder of the registration pattern 25. As shown in Fig. 7A the leading and trailing edges of the register mark 114 are 5.40 and 6,35 cm (2.125 and 2.50 inches) respectively 10 from the leading edge of the pattern 25 when register is The center of the mark 114 is, therefore, proper. 5.87 cm (2.3125 inches) from the pattern reference point when the printing unit 3 is in register. As will be explained in more detail below, the system processor 15 15 analyzes the signal 117 (Fig. 6) produced by the optical scanners 18 and 19 and determines the center of the register marks 114 to 116 relative to the pattern reference point. If any deviations of these center points are detected, the system processor 15 outputs 20 a command to the output controller 20 which brings the printing unit back into register.

Referring particularly to Fig. 1, the register control system can be operated in a conventional "open loop", or "manual" mode in which the human operator enters corrective data into the system through the main control panel 16. Such corrective data is processed by the system processor 15 to form an alignment command which is output to the controller 20. Such an alignment command may, for example, direct that the register control motor for the upper portion of the printing unit 2 be energized to move laterally 12.7/1000 of a cm (five-thousandths of an inch). The output controller 20 accepts such commands and operates the proper motor to carry out the alignment motion. The human operator then checks the register of the signatures at the output of the press to determine if further corrections are

necessary. While the system of the present invention may be operated in this conventional manual mode, it can also be switched to an automatic mode in which the register of the signatures is examined by the optical scanner 18 or 19 and appropriate alignment commands are automatically produced and output to the controller 20. While the automation of this process may appear straight forward, in practice there are many difficulties which must be overcome.

10 Most of the difficulties which arise relate to the imperfect nature of the printing process. For example. the register pattern 25 may not print accurately or properly at all times. One of its marks may not be properly aligned with the image which it is to regis-15 ter, or the pattern may be distored by stretching of the web due to press tension. Also, the web has a certain amount of random lateral motion, or "jitter". as it moves through the press which produces a corresponding random misregister. Such random misregister 20 can be caused by other factors as well, such as momentary variations in web thickness. It is neither possible nor desirable to make register corrections in response to such short term changes. The human operator is capable of discerning the difference between 25 these random short term changes and long term changes in register, and it is important that the automatic register control do the same.

As indicated above, the programs which direct the operation of the system processor 15 are stored in its 30 ROM 47. The operation of the register control system will now be described with reference to flow charts which schematically illustrate the functions carried out by these programs. The overall operation will be described in general terms first, and then the data collection and data analysis functions will be described in detail.

Referring particularly to Fig. 8, when the register control system is powered up, a set of instructions indicated by process block 200 is executed to initialize the system hardware and the data structures stored in 5 the RAM 44 (Fig. 2A). A loop is then entered in which a set of instructions, indicated by process block 201, is executed to enable the operator to enter data. will be described in more detail below, this set-up data includes information about the particular printing job, 10 such as which printing unit is the reference unit and which register marks are produced by which units. addition. the set-up data may pertain to the press, such as its characteristic jitter and its speed. operator may also enter offset data which compensates for errors in the printing of the register pattern 25. 15

After the system has been set up the operator may switch to automatic control of register. Each surface of the web 6 is controlled separately and it is possible to have automatic control of one surface and manual control of the other surface. If automatic control has 20 been selected, as indicated at decision block 202, a data collection sequence is begun for one surface of the web 6. This sequence includes a preparation phase indicated by process block 203 in which a data table 204 in the RAM 44 is cleared. Referring to Fig. 2B. 25 such preparation includes the selection of the proper input channel on the multiplexer 70 and the presetting of the counter (2) in the timer/counter 75. The counter (2) is decremented by pulses received from an encoder on the printing press, and when decremented to zero, 30 an interrupt request is generated on line RST3. counter (2) is preset to a value which will result in an interrupt after the plate cylinders in each press unit have rotated two and one-quarter revolutions. This ensures that at least two register patterns 25 are 35 scanned during the data acquisition interval. actual data acquisition is accomplished by two interrupt driven routines which store a sequence of numbers in the data table 204.

When the data acquisition sequence is completed, as indicated at process block 206, the numbers stored in the data table 204 are examined to determine if the register patterns 25 were correctly and accurately scanned. As indicated at decision block 207, if good data was not obtained, the system loops back through process block 208 to collect data on the other surface of the web 6. As indicated above, there are many reasons why poor register data may be obtained, but in most instances the situation corrects itself and good data may be collected a moment later.

Referring still to Fig. 8, when good data is ob

15 tained from a scan sequence, the data is analyzed and

used both to correct the lateral position of the

scanner 18 or 19 and to correct the register of the

printing units 2 to 5. As shown by process block 209,

the errors in both scanner position and color register

20 are calculated. The errors are computed by averaging

the errors indicated by the two register patterns

scanned during the data acquisition sequence. This

averaged error data is then processed as indicated by

block 210, to determine if corrections should be made.

25 This further processing is designed to eliminate needless corrections where the measured errors are due to

short term random events such as jitter.

If the optical scanner 18 or 19 is not centered on the register pattern 25 and a move is required as indicated at decision block 211, a routine indicated by process block 212 is executed. Referring to Figs. 2B and 5, this routine 212 writes data to the latch 63 which energizes the proper scanner motor 28 in the desired direction. The counter (2) in the timer/counter circuit 75 is then preset to an appropriate value, and when it "times out", the scanner motor 28 is turned off

by again writing to the latch 63. In this manner, the scanner 18 or 19 can be moved to the left or right to "track" the register patterns 25 being printed on the web 6.

Referring again to Fig. 8, before looping back to 5 perform the next data collection sequence, register corrections are made. As determined at decision block 213. when significant register errors are detected. a routine 214 is executed to generate alignment commands 10 to the output controller 20. Referring particularly to Fig. 2A, the routine 214 generates a message to the output controller 20 through the UART 54. This message is a command that identifies the print unit, web surface and the lateral or rotational motor. The alignment 15 command also indicates the direction of the move and the distance in 2.54/1000 of a cm (thousandths of an inch). Referring particularly to Figs. 4A and 4B, the output controller 20 receives this alignment command at its UART 254 and writes an appropriate bit pattern 20 to one of the output latches 130 to 133 to energize the proper alignment motor for the time needed to move this commanded distance. Referring again to Fig. 8, after the alignment commands have been issued to the output controller 20, the system loops back to 25 the process block 208 to scan the other surface of the web 6.

It should be apparent from this general description that the register control system collects data from one web surface, makes corrections to scanner position and color register when necessary, and then repeats the sequence with the other web surface. The number of print surfaces which can be monitored in this manner need not be limited to two. The system is much faster than human operators in making register corrections, even when four print surfaces are scanned and even when a significant portion of the collected scanner data is

discarded as unacceptable. Indeed, one of the functions of the process indicated by block 210 is to average the large amount of collected data, and to thereby effectively slow the response of the register control system to a level which is appropriate to the particular press and printing process being controlled.

Referring particularly to Figs. 2B and 9A-C, the automatic control of color register will now be described in more detail. Each data collection cycle 10 is comprised of a series of interrupts which are produced by the scanner signal appearing at the Y and W outputs on the multiplexer 70. As indicated at process block 220, this cycle is initiated by first presetting the counter (2) in the timer/counter 75 to a value 15 which represents two and one-quarter revolutions of a plate cylinder. The RST2 and RST3 interrupts are then enabled as indicated at process block 221, and the system then waits for the RST3 interrupt to occur at process block 222. Incremental position feedback 20 pulses are applied to decrement the counter (2) through the gate 78, and after two and one-quarter plate cylinder revolutions, and RST3 interrupt occurs and the data collection cycle is terminated. As indicated at process block 223, the three interrupts 25 RST1. RST2 and RST3 are then disabled and the system proceeds to examine the collected data.

Referring particularly to Figs. 2B and 6, as the register pattern 25 passes beneath the active scanner 18 or 19 during the data collection cycle, a series of logic high (light) and logic low (dark) signals are produced and a corresponding series of RST1 and RST2 interrupts occur. That is, when the scanner "sees" a mark in the pattern 25 an RST1 interrupt is produced, and when it sees light, and RST2 interrupt is produced.

35 Referring particularly to Fig. 9C, an RST2 interrupt occurs immediately after the data collection cycle

begins and the system is vectored to an RST2 interrupt routine. As indicated at process blocks 225 and 226, the first functions performed by this routine is to disable further RST2 interrupts and to enable the RST1 interrupt. As indicated at process block 227, the counter (1) in the timer/counter 75 is then enabled and the counter (0) is disabled. The value of counter (0) is then read from the timer/counter 75 and saved in the data table 204 of the RAM 44 (Fig. 2A), as indicated at process block 228. The counter (0) is then reset, as indicated at process block 229, and the system returns to await the RST1 interrupt.

Referring particularly to Fig. 2B, when the leading edge of a mark in the register pattern 25 is detected, an RST1 interrupt occurs. The system is vectored to a service routine which disables the RST1 interrupt and enables the RST2 interrupt as indicated at process blocks 230 and 231. The counter (1) in the timer/counter 75 is then disabled and counter (0) is enabled to start counting, as indicated at process block 232. The count in counter (1) is then read from the timer/counter 75 and saved in the data table 204, as indicated at process block 233; and the counter (1) is reset at process block 234 in preparation for the next RST2 interrupt.

The RST1 and RST2 interrupts occur alternately during the data collection cycle as the scanner 18 or 19 alternately sees light and dark segments of the register patterns 25. The counter values which are stored in the data table 204 by the RST1 and RST2 interrupt routines represent the duration of each light or dark segment seen by the scanner 18 or 19 and these numbers can be converted to dimensions which correlate with those dimensions illustrated in Fig. 7A.

The data collection sequence is terminated when an RST3 interrupt occurs after two and one-quarter revolutions of each printing unit plate cylinder. Referring to Figs. 7 and 10. the RST3 interrupt 5 service routine is then executed, and the first function, as indicated by process block 250, is to convert the sequence of counter numbers stored in the data table 204 to corresponding dimensions. These dimensions indicate the size of each mark and their spacing. 10 As indicated at process block 251, the size of each mark is then read from the data table 204 and examined to determine if it is the 2.54 cm (one inch) reference mark 111 which indicates the beginning of the register pattern 25. If not, as determined at decision block 15 252. the system loops to read the next mark from the data table 204. When the 2.54 cm (one inch) reference mark 111 is found, the dimension which corresponds to the 1.27 cm (one-half inch) reference mark 112 is read from the data table 204. If this mark is indeed 1.27 cm (one-half inch) long, a register pattern 25 has been found. Otherwise, the system loops at decision block 253 to continue the search for valid data.

When a register pattern 25 is found in the data table 204, the dimensions thereof are calibrated as 25 indicated by process block 254. This is accomplished by finding the distance between the leading edge of the 2.54 cm (one inch) reference mark 111 and the leading edge of the 1.27 cm (one-half inch) reference mark 112. This distance should be exactly 11.43 cm (four and 30 one-half inches), and all of the data table entries are scaled to exactly produce this distance. distance measurement is employed to calibrate the dimensions in the data table 204 because the measurement between leading edges of the reference marks 111 35 and 112 is relatively immune to inking problems.

Smearing usually occurs at the trailing edge, not the leading edge, and the growth of marks due to an overabundance of ink affects both leading edges equally.

Referring still to Figs. 7 and 10, the reference color marks 113 are examined next to determine if they are present and are printed properly. If not, as indicated at decision block 255, the system loops and continues the search for good data. The same tests are then performed on the color marks 114 to 116 as indicated at decision block 256, and if good data is obtained for the entire register pattern 25, the location of this data in the table 204 is identified, as indicated by process block 257.

The system continues to read from the data table

204 until the last entry is reached. When this occurs, as determined at decision block 258, a test is made at decision block 259 to determine if good data for two register patterns 25 has been located. If so, the system returns to process the data, otherwise, the

20 data is discarded and the system loops to scan the other web surface as shown in Fig. 8.

The division of the reference mark 113 and color marks 114 to 116 into two triangular segments provides considerable diagnostic information which facilitates 25 the above-described process. Referring particularly to Figs. 11A and 11B, each mark 113 to 116 is comprised of an upper section 260 and a lower section 261. The sections 260 and 261 are triangular in shape, and when formed properly, they have a combined length L which is constant regardless of their position relative to the scanner path 262 and 263. For example, the scanner path 262 passes through the sections 260 and 261 left of center to produce entries in the data table 204 of duration X<sub>U</sub>1 and X<sub>L</sub>1. On the other hand, the scanner path 263 passes through the sections 260 and 261 right of center to produce entries in the data

table 204 of duration X<sub>U</sub>2 and X<sub>L</sub>2. Regardless of the scanner path, the sum of these readings is a constant value and a significant deviation from this constant value indicates that the register mark is not properly printed. That is:

$$X_{U}^{1} + X_{L}^{1} = L = X_{U}^{2} + X_{L}^{2}$$

This diagnostic check is made by a set of instructions which are listed in Appendix A and which are executed as part of the decision blocks 255 and 256 shown in 10 Fig. 10.

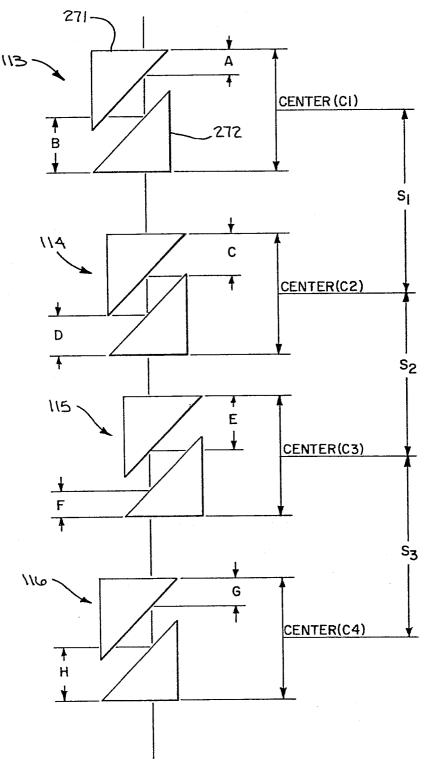

After two register patterns 25 have been successfully scanned, the rotational and lateral register errors are calculated for each print unit. Referring particularly to Figs. 12 and 13, the scanner misalignment is calculated first as indicated by process block 270. This is accomplished by measuring the difference between the measured length (A) on the upper section 271 of the reference mark 113 and the measured length (B) of the lower section 272. The misalignment, or tracking error, of the scanner 18 or 19 is given by the following expression:

$$Error = (B-A)/2$$

A loop is then entered in which the rotational and lateral register error for each print unit is 25 calculated. As indicated by process block 273, the center C1 to C4 of each mark 113 to 116 is calculated by averaging the distance to its leading edge and its trailing edge. This method has been found to provide good immunity to colorimetry changes, since colorimetry changes usually cause both the leading and trailing 30 edges to shift equally toward or away from the center. The centerlines of each mark 113 to 116 are ideally spaced 1.91 cm (.75 inches) apart and any deviation from this pattern is a direct measure of rotational 35 misregister of the print unit. The rotational register error indicated by the respective color marks 114 to 116 is calculated as follows:

These values are calculated at process block 274 and 5 saved in the RAM 44 (Fig. 2A).

Referring still to Figs. 12 and 13, the lateral register error for a printing unit is calculated next as indicated at process block 275. If the color marks 114 and 116 are in perfect register, they should be 10 "off-center" by the same amount as the reference mark 113. The lateral register error indicated by the respective color marks 114 to 116 is calculated as follows:

LATERROR (114) =

$$[(D-C) - (B-A)]/2$$

LATERROR (115) =  $[(F-E) - (B-A)]/2$

LATERROR (116) =  $[(H-G) - (B-A)]/2$

15

The division by 2 in these equations accounts for the 45-degree angle of the hypotenuse of the color triangles.

After each color mark 114 to 116 is analyzed as determined at decision block 276, the same analysis is performed on the data obtained for the second register pattern 25. When both patterns have been analyzed, as determined at decision block 277, the errors indicated by each pattern are compared. If the measured errors are substantially different, bad data is indicated and the system branches at decision block 278. Otherwise, the errors indicated by the two scanned register patterns 25 are averaged and saved in the RAM 44 as indicated at process block 279. This averaging step eliminates needless register corrections which would otherwise occur due to "packing errors".

Finally, although the color marks 114 to 116 may indicate a register error, this does not necessarily indicate that the print images are out of register. For example, the register marks 114 to 116 are generally

laid down separately from the print image material on the plate, and perfect alignment is difficult. As a result, the register indicated by the marks may require an offset to give correct register of the print 5 image. This offset may be entered by the operator during system set-up (Fig. 8) and the offset values are stored in a table 280 in the RAM 44 (Fig. 2A). These offsets are added to the measured register errors at process block 281 to provide register error data 10 which is stored in a table 282 in the RAM 44. As indicated above, this error data is employed to form motion commands to the scanner interface 17 to realign the scanner 18 or 19 with the center line of the register patterns 25. This data is also employed 15 to produce alignment commands for the output controller 20 which correct the register errors in each printing unit 2 to 5.

Referring particularly to Fig. 8, the error data in table 282 is processed at block 210 prior to the 20 formation of any scanner motion signal or alignment command. This processing is indicated by the flow chart of Fig. 14, and it is intended to further eliminate needless corrections. A loop 290 is entered which processes the register error data for each print 25 unit in the press, and when the data for all print units has been processed, as determined at decision block 291, the loop 290 is exited.

If the measured rotational or lateral register error exceeds a preset limit, as determined at decision block 292, a correction is made. This preset limit is entered by the operator during the set-up process, and it is typically set to a value which is greater than the random jitter characteristic of the press. Register errors less than this limit may be self-correcting and changes are not made immediately. Instead, as indicated by process block 293, the most recent register error reading is averaged with the

N-1 previous error readings. The standard deviation of these n register error readings is then calculated at process block 294, and the average error is compared with this standard deviation. The standard deviation can be viewed as a measure of the uncertainty of the register error readings, and as long as the average error is less than this uncertainty, no corrections are made. When the average error increases above this uncertainty level however, a register correction is needed, as indicated at decision block 295. The number of readings (N) which are averaged in this manner is selected by the operator during the set-up process.

Even though a register correction is indicated,

such corrections cannot be made at a high repetition

rate because it requires motion for corrected signatures to travel from the printing units 2 to 5 to the

chill rolls 8 where the scanners 18 and 19 are located.

Thus, a motion delay is imposed in the register control

loop to insure that signatures containing prior

register corrections have ample opportunity to pass

through the press. This delay is different for each

printing unit 2 to 5 and it is selected when the

control system is installed.

As determined at decision block 296, if the delay has elapsed since the last register correction, a register alignment command for the proper printing unit 2 to 5 and web surface is formed. As indicated at process block 297, the alignment command may alter either rotational or lateral register or both. The command is output to the output controller 20 which operates to execute the alignment command. As indicated at process block 298, a timer associated with the printing unit 2 to 5 and web surface which is affected by this alignment command is then preset to provide the necessary delay time. As shown in Fig. 2A, a delay

table 299 is stored in the RAM 44 which includes a "software" timer for each printing unit and web surface. The appropriate timer is set at process block 298 with the proper delay time, and this delay time is subsequently measured by periodic comparison with a real time clock formed by the timer/counter circuit 77 (Fig. 2B).

The register control system controls the register of each printing unit relative to the printing unit

10 which produces the reference marks 111, 112 and 113. Because register is measured relative to the reference marks 111, 112 and 113, rather than being measured relative to the frame of the press, any changes in the register of the reference printing unit will be corrected by making corresponding changes in the register of each color printing unit. While it is preferable this "reference" printing unit produces a black image, the selection of a reference printing unit and the number and position of the color printing units may be determined by the operator during the set-up process.

# APPENDIX A REGISTER MARK DIAGNOSTIC PROGRAM

| OBJECT<br>CODE         | SOURCE<br>STATEMEN | NT              | COMMENTS                                  |

|------------------------|--------------------|-----------------|-------------------------------------------|

| 08D4 2A2F09<br>08D7 EB |                    | lhld clrtop     | ;get top of color ;in DE                  |

| 08D8 2A3109            |                    | lhld clrbot     | ; and bottom                              |

| 08DB CD0000            |                    | call avgdh      | ;get center                               |

| 08DE 44                |                    | mov b,h         | ;sav in BC                                |

| 08DF 4D                |                    | mov c,1         |                                           |

| 08E0 2A2B09            |                    | lhld topsiz     | ;get top triangle size                    |

| 08E3 EB                |                    | xchg            | ;in DE                                    |

| 08E4 2A2D09            |                    | lhld botsiz     | ;get bottom size                          |

| 08E7 E5                |                    | push h          | ;sav bottom size                          |

| 08E8 19                |                    | dad d           | get total size                            |

| 08E9 D5                |                    | push d          | ;save top size                            |

| 08EA E5                |                    | push h          | ; save total                              |

| 08EB 110B09            | •                  | lxi d, tottsz+2 | ;allow for black                          |

| 08EE 2A8D09            | 1                  | lhld totptr     | ;get offset                               |

| 08Fl 29                |                    | dad h           | ;2 bytes apiece                           |

| 08F2 19                |                    | dad d           | ;add in array start                       |

| 08F3 EB                |                    | xchg            | ;save this                                |

| 08F4 2A9409            |                    | lhld surfac     |                                           |

| 08F7 29                |                    | dad h           | ; 2                                       |

| 08F8 29                |                    | dad h           | ; 4                                       |

| 08F9 29                |                    | dad h           | ;8 bytes/surface                          |

| 08FA 19                |                    | dad d           | <pre>;point to right part  of array</pre> |

| 08FB D1                |                    | pop d           | ;get total back                           |

| 08FC 73                |                    | mov m,e         | ;save for viewing                         |

| 08FD 23                |                    | inx h           |                                           |

| 08FE 72                |                    | mov m, d        |                                           |

| 08FF EB                |                    | xchg            | ;put total back in HL                     |

| 0900 E5                |                    | push h          | ;save total                               |

| 0901 2A9409            | 9                  | lhld surfac     | ;12 bytes/surface                         |

| 0904 29                |                    | dad h           | ; 2                                       |

| 0905 29                |                    | dad h           | ; 4                                       |

| 0906 54                |                    | mov d,h         |                                           |

| 0907 5D                |                    | mov e,l         | ;save this                                |

| 0908 29                |                    | dad h           | ;8                                        |

| 0909 19                | 0                  | dad d           | ;12!                                      |

| 090A 11C50             | 8                  | lxi d,colszl    | limits of allowable size                  |

| 090D 19                |                    | dad d           | ;index into array                         |

| 090E EB                |                    | xchg            | ;save in DE                               |

| 090F 2A8D0             | 9                  | lhld totptr     | get color;                                |

| 0912 29                |                    | dad h           | ;2 words/color                            |

| 0913 29                |                    | dad h           | · · · · · · · · · · · · · · · · · · ·     |

| 0914 19                |                    | dad d           | point to this color;                      |

| 0915 5E                |                    | mov e,m         |                                           |

| 0916 23                |                    | inx h           |                                           |

| 0917 56                |                    | mov d, m        | get max size                              |

| 0918 23                |                    | inx h           | ;point to lsb of min                      |

# APPENDIX A (continued)

## REGISTER MARK DIAGNOSTIC PROGRAM

| OBJECT                                                                                                                                     | SOURCE     |                                                                                       |                                                                                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CODE                                                                                                                                       | STATEMENT  | ľ                                                                                     | COMMENTS                                                                                                                                                   |

| 0919 229099                                                                                                                                | dsec       | shld mmxptr                                                                           | ; save pointer to min                                                                                                                                      |

| 0999                                                                                                                                       | mmxptr: ds | 2                                                                                     | ;temp pointer to colszl                                                                                                                                    |

| 091C E1<br>091D CD0000                                                                                                                     | Cae        | pop h<br>call cmpDE                                                                   | ;get total back                                                                                                                                            |

| 0920 Dl                                                                                                                                    | -          | pop d                                                                                 | <pre>;get top triangle size back</pre>                                                                                                                     |

| 0921 E1<br>0922 DA2B09                                                                                                                     |            | pop h<br>jc totrsm                                                                    | <pre>;and bottom size ;skip this if total not too big</pre>                                                                                                |

| 0925 E3<br>0926 7E<br>0927 F604<br>0929 77<br>092A E3                                                                                      |            | <pre>xthl mov a,m ori 4 mov m,a xthl</pre>                                            | get pointer to status; mark smudges in data                                                                                                                |

| 092B E5<br>092C D5<br>092D E5<br>092E 2A9909                                                                                               | totrsm:    | push h push d push h lhld mmxptr                                                      | <pre>;save bottom size ;and top size ;save total size ;get pointer to minimum size</pre>                                                                   |

| 0931 5E<br>0932 23<br>0933 56<br>0934 E1<br>0935 CD0000<br>0938 D1<br>0939 E1<br>093A D24209<br>093D E3<br>093E 7E<br>093F F608<br>0941 E3 |            | mov e,m inx h mov d,m pop h call cmpDE pop d pop h jnc totrbg xthl mov a,m ori 8 xthl | ;get total size back<br>;carry here if too small<br>;get top size<br>;and bottom size<br>;skip this if OK<br>;get pointer to status<br>;show marks missing |

### Claims

海流 医二氯化合物

1. A register control system for a printing press, the combination comprising:

optical scanner means (18, 19) positioned to detect a register pattern (25) on a moving web (6), which 5 pattern includes register marks (113 to 116) produced by a plurality of separately adjustable printing units (2 to 5), the optical scanner means being operable to generate an electrical signal indicative of the relative position of each register mark;

a processor (15) coupled to the optical scanner means to receive the electrical signal and including:

- (a) means for designating a reference printing unit,

- (b) means for establishing the relative position of each register mark produced by the other printing units with respect to the register mark produced by the designated reference printing unit,

- (c) means for establishing a desired position for each of the other printing units,

- (d) means for comparing each established relative position with the corresponding desired position to produce a register error for each of the other printing units which indicates their misregister with respect to the reference printing unit, and

- (e) means for adjusting the position of each printing unit in response to its associated register error to reduce its misregister.

30

25

10

15

20

- 2. The register control system as recited in claim 1 in which each printing unit (2 to 5) has a rotational and a lateral position adjustment, the means for establishing the relative position of each register mark with respect to the register mark produced by the designated reference printing unit provides a lateral relative position and a rotational relative position, separate lateral and rotational desired positions are established for each of the other printing units, and separate lateral and rotational register errors are produced for separately operating the respective lateral and rotational adjustments of each of the other printing units.

- 15 3. The register control system as recited in claim 1 in which a keyboard (16) is coupled to the processor and the processor includes means for receiving position offset data from the keyboard and adding such position offset data to a selected desired position.

20

4. The register control system as recited in claim 1 in which each register mark (113 to 116) is divided into an upper section (260) and a lower section (261) and in which the length (L) of the register mark taken 25 along any longitudinal axis through the register mark is a constant value

$L = X_{II} + X_{I}$

where:  $X_U$  = longitudinal dimension of upper section,  $X_L$  = longitudinal dimension of lower section, 30 and the processor (15) includes error detection means for summing the lengths of the signals produced by the optical scanner means as it detects both the upper and lower sections of each register mark, and for indicating an error when the sum deviates a preset amount from said constant value.

- 5. The register control system as recited in claim 1 in which each register mark (113 to 116) is comprised of two sections (260, 261) and the optical scanner means produces two voltage pulses when it detects each register mark and the two sections are shaped such that the relative duration of the two voltage pulses indicates the lateral misregister of the printing unit which produced the register mark.

- 10 6. The register control system as recited in claim 1 in which said means for adjusting the position of each printing unit includes:

means for averaging successive ones of the register errors to produce an average register error for each of 15 the other printing units; and

means for reducing the misregister of each of the other printing units when its associated average register error exceeds a selected amount.

20 7. The register control system as recited in claim 6 in which the means for adjusting the position of each printing unit also includes:

25

means for calculating the standard deviation of successive ones of the register errors to produce said selected amount.

- 8. The register control system as recited in claim 1 the processor (15) further includes:

- (f) means for establishing a time delay interval

30 when the position of a printing unit is adjusted to

reduce misregister; and

- (g) means for inhibiting the position adjustment of each printing unit until the time delay interval associated with that printing unit has expired.

9. A register control system for a printing press, the combination comprising:

optical scanner means (18, 19) mounted to detect a series of register patterns (25) on a moving web (6) 5 and being operable to generate an electrical signal indicative of the register of each printing unit (2 to 5) in the press;

adjusting means (26 to 30) for moving the optical scanner laterally across the moving web in response to an adjustment command:

10

20

tracking means (15, 17) connected to receive the electrical signal from the optical scanner means (18, 19) and being operable to generate adjustment commands to the adjusting means (26 to 30) to maintain the optical scanner means (18, 19) in alignment with the register patterns on the moving web; and

processor means (15, 17, 20) connected to receive the electrical signal from the optical scanner means (18, 19) and being operable in response thereto to control the register of the printing units (2 to 5).

10. The register control system as recited in claim 6 in which the optical scanner means (18, 19) includes a scanner interface circuit (90A, 90B) which converts the analog signal (110) from an optical scanner device to a digital signal (117) comprised of voltage pulses of substantially uniform amplitude.

FIG.2C

FIG.3

FIG.13