(1) Veröffentlichungsnummer:

0 123 791

12

## EUROPÄISCHE PATENTANMELDUNG

Anmeldenummer: 84100832.9

(f) Int. Cl.3: **G 04 G 3/00**, G 06 F 3/00

Anmeldetag: 26.01.84

Priorität: 03.02.83 DE 3303662

Anmelder: Siemens Aktiengesellschaft, Berlin und München Wittelsbacherplatz 2, D-8000 München 2 (DE)

Veröffentlichungstag der Anmeldung: 07.11.84 Patentblatt 84/45

Benannte Vertragsstaaten: AT CH DE FR IT LI

Erfinder: Nagel, Klaus, Dr., Cajetan-Strasse 7, D-8000 München 80 (DE)

## 54 Zeitgeber mit hoher Auflösung.

57 Ein Zeitgeber mit hoher Auflösung, z.B. eine Auflösung von 1 µsec, wird unter Verwendung einer Zähleinrichtung realisiert, die die von einem Oszillator gelieferten Zähltakte zählt. Die Zähleinrichtung besteht aus einem ersten Zählerteil für die niederwertigeren Zählstellen, die in einer schnel-Ien Schaltkreistechnik, z.B. TTL Technik, realisiert ist und aus einem zweiten Zählerteil, der in einer langsameren Schaltkreistechnik, z.B. MOS Technik, realisiert ist. Dem ersten Zählerteil (ZA1) wird der Zähltakt (S1) vom Oszillator (OS) zugeführt. Tritt ein Übertrag auf, wird dies dem zweiten Zählerteil, der aus einem Mikroprozessor (MP) besteht, mitgeteilt. Dieser erhöht dann einen aus einem internen Zähler und internen Register bestehenden Zähler um eine Einheit. Aus dem Zähltakt (S1) wird ein synchron auftretender, aber phasenverschobener Übernahmetakt (S2), gewonnen, der dazu verwendet werden kann, um den Inhalt des ersten Zählerteils (ZA1) in ein Zwischenregister zu übertragen. Bei Anlegen einer Zeitnahmeanforderung (REQ) von einem Verbraucher liest der Mikroprozessor (MP) den Inhalt des Zwischenregisters im ersten Zählerteil (ZA1) ein und gibt diesen zusammen mit dem Inhalt des internen Zählerteils an einen Pufferspeicher (PF), von dem der Verbrauch das Zählergebnis mit einem Auslesetakt (AT) abholen kann.

Ш

ACTORUM AG

SIEMENS AKTIENGESELLSCHAFT Berlin und München

Unser Zeichen VPA 83 P 1046 E

## Zeitgeber mit hoher Auflösung

5

Die Erfindung bezieht sich auf einen Zeitgeber mit hoher Auflösung unter Verwendung einer Zähleinrichtung, die von einem Oszillator gelieferte Zähltakte zählt und deren Inhalt ein Maß für die Zeit ist, bei dem die Zähleinrichtung aus einem ersten, die niederwertigen Zählstellen umfassenden, den Zähltakt zählenden Zählerteil und aus einem zweiten, die höherwertigen Zählstellen umfassenden und mit dem höchstwertigen Zählstellenausgang des ersten Zählerteils verbundenen Zählerteil besteht.

15

Für die Prozeßsteuerung oder für die Zeitmessung interner Abläufe benötigen Computersysteme einen Zeitgeber, auch Echtzeituhr genannt, hoher Auflösung. Um auch kurze Intervalle messen zu können, müssen Messungen schnell hintereinander möglich sein. Probleme bereitet es, die Uhrzeit auszulesen, ohne den Gang des Zeitgebers zu stören.

Solche Zeitgeber bestehen gewöhnlich aus einer Zähleinrichtung, die von einem Oszillator gelieferte Zähltakte bestimmter Frequenz zählt und deren Inhalt ein Maß für die abgelaufene Zeit ist. Die Zähleinrichtung kann dabei aus mehreren Zählerteilen bestehen, wobei in einem ersten Zählerteil die niederwertigen Zählstellen, in einem zweiten Zählerteil die höherwertigen Zählstellen enthalten sind und der höchstwertige Zählstellenausgang des ersten Zählerteils mit dem Eingang des zweiten Zählerteils verbunden ist.

Um Zeitgeber hoher Auflösung zu realisieren, kann eine Zähleinrichtung verwendet werden, die aus schnellen Bausteinen

niedrigen Integrationsgrades besteht. Dies führt allerdings

zu aufwendigen, teuren Lösungen. Der Einsatz z.B. billiger

MOS Mikroprozessoren scheitert dagegen an den hohen FrequenII 1 The - 18.1.1983

zen, die durch die hohe Auflösungsanforderung bei Computersystemen bedingt sind.

Die der Erfindung zugrundeliegende Aufgabe steht darin, einen Zeitgeber mit hoher Auflösung unter Verwendung einer Zähleinrichtung anzugeben, bei dem die Zeit ausgelesen werden kann, ohne den Gang des Zeitgebers zu stören und dessen Realisierung trotzdem nicht teuer ist. Diese Aufgabe wird bei einem Zeitgeber der eingangs angegebenen Art da-10 durch gelöst, daß der erste in einer schnellen Schaltkreistechnik realisierte Zählerteil aus einem ersten Zähler für die niederwertigen Zählstellen und einem Zwischenregister besteht, in das der Inhalt des ersten Zählers in Abhängigkeit eines mit dem Zählertakt synchron, jedoch phasenver-15 schoben auftretenden Übernahmetaktes übernehmbar ist, und daß der zweite in einer langsameren Schaltkreistechnik realisierte Zählerteil aus einem Mikroprozessor besteht, bei dem interne Zähler und Register einen zweiten Zähler für die höherwertigen Zählstellen bilden und der bei Anliegen einer 20 Zeitnahmeanforderung von einem Verbraucher den Inhalt des Zwischenregisters des ersten Zählerteils übernimmt und diesen Inhalt zusammen mit dem Inhalt des zweiten Zählers an den anfordernden Verbraucher abgibt.

25 Zweckmäßigerweise kann der erste Zählerteil in TTL Technik realisiert sein, während der zweite Zählerteil, also der Mikroprozessor, in MOS Technik realisiert ist.

Das Zwischenregister im ersten Zählerteil übernimmt somit

30 phasenverschoben zum Zählertakt jeweils den Inhalt des ersten Zählers mit Hilfe des Übernahmetaktes. Liegt eine Zeitnahmeanforderung von einem Verbraucher vor, dann wird der

Übernahmetakt mit Hilfe einer bistabilen Kippschaltung, die

zwischen Oszillator und erstem Zählerteil angeordnet ist,

35 kurzzeitig abgeschaltet, und der Inhalt des Zwischenregi-

sters in den Mikroprozessor übernommen. Nach der Übernahme des Inhalts des Zwischenregisters in den Mikroprozessor, gibt der Mikroprozessor die bistabile Kippschaltung wieder frei, so daß die Übernahme-5 takte wieder auf das Zwischenregister einwirken können.

Es ist vorteilhaft, zwischen dem Mikroprozessor und dem Verbraucher einen Pufferspeicher anzuordnen, in den der Mikroprozessor bei Anliegen einer Zeitnahmeanforderung das Zählergebnis überträgt, und von dem Verbraucher mit einem vom Verbraucher gelieferten Auslesetakt das Zählergebnis übernehmen kann.

In einem anderen Ausführungsbeispiel kann das Zwischenregi15 ster ein first-in / first-out Pufferspeicher sein. Mit

Hilfe einer Anordnung zur Durchschaltung des Übernahmetaktes an den Pufferspeicher wird dieser nur dann an den Freigabeeingang des Pufferspeichers angelegt, wenn der erste

Zähler einen Übertrag anzeigt, bzw. wenn eine Zeitnahmean20 forderung von einem Verbraucher anliegt.

Bei diesem Ausführungsbeispiel/liest der Mikroprozessor ständig den Inhalt des Pufferspeichers und erhöht den Inhalt des zweiten Zählers um eine Einheit, wenn der ausgelesene 25 Zählerinhalt O ist.

Andere Weiterbildungen der Erfindung ergeben sich aus den Unteransprüchen.

30 Anhand von Ausführungsbeispielen, die in den Figuren dargestellt sind, wird die Erfindung weiter erläutert. Es zeigen

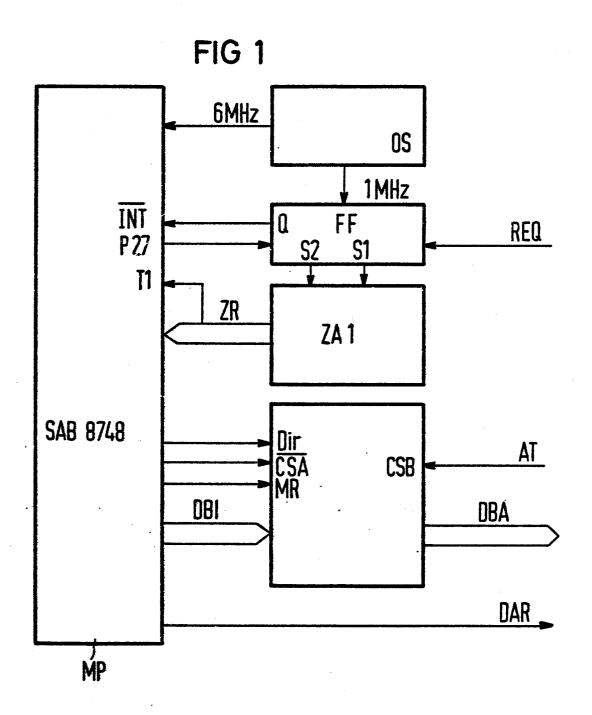

Figur 1 ein Blockschaltbild eines ersten Ausführungsbeispiels des erfindungsgemäßen Zeitgebers,

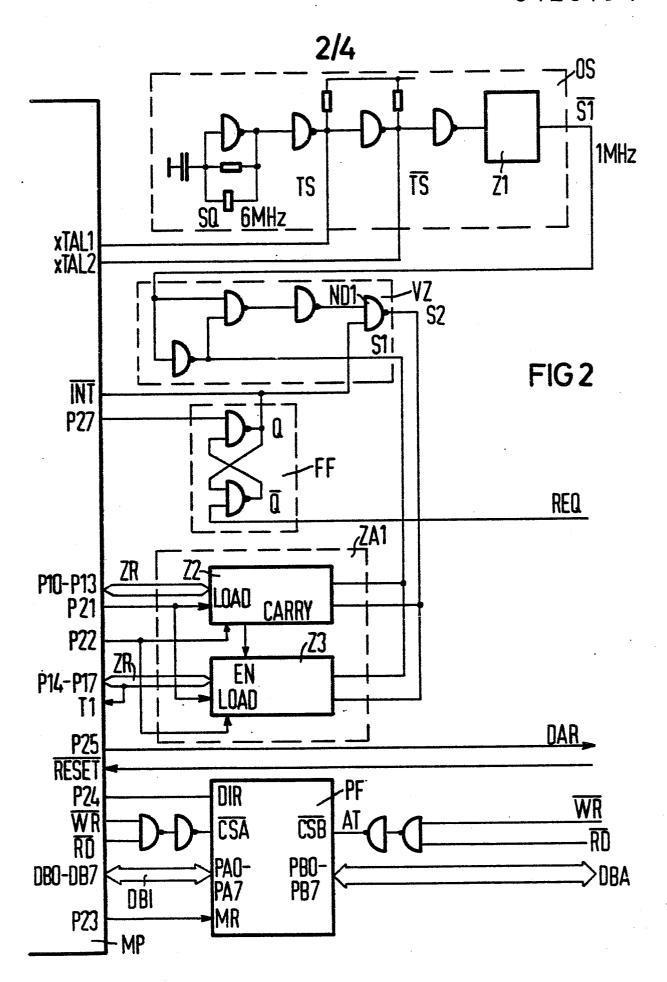

35 Figur 2 das Schaltbild des Zeitgebers der Figur 1,

83 P 1046 E

VPA

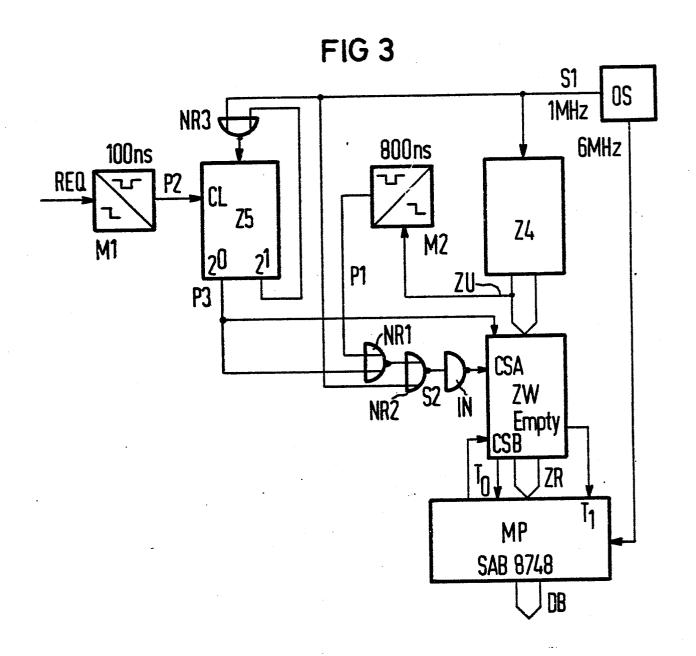

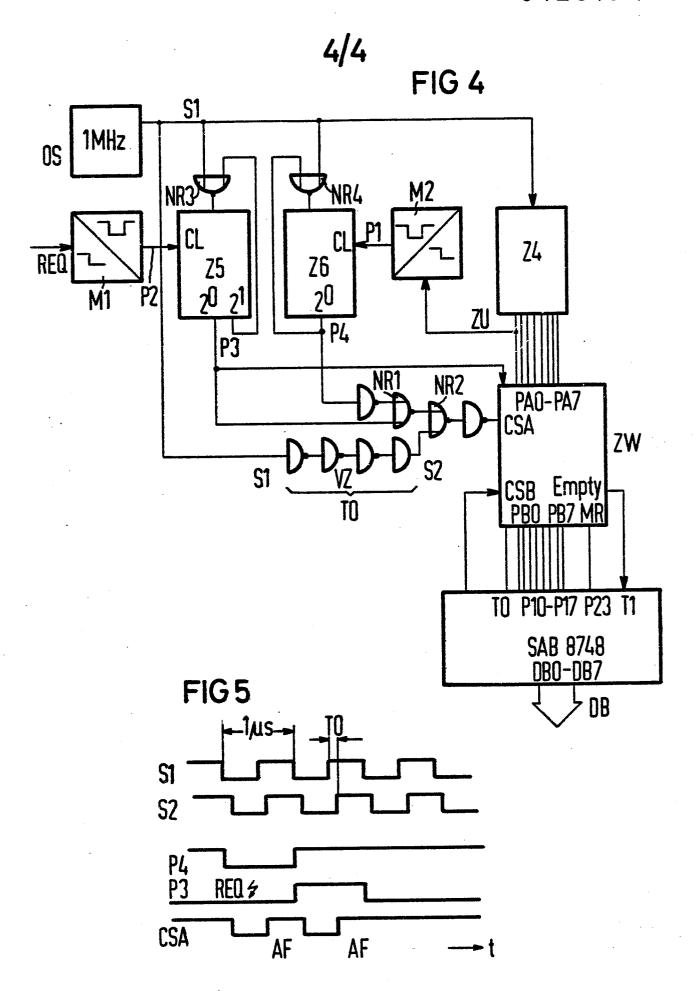

Figur 3 ein zweites Ausführungsbeispiel des Zeitgebers, Figur 4 ein drittes Ausführungsbeispiel des Zeitgebers, Figur 5 ein Impulsdiagramm aufgetragen über der Zeit t, indem die an verschiedenen Stellen des Zeitgebers nach Figur 4 auftretenden Impulse dargestellt sind.

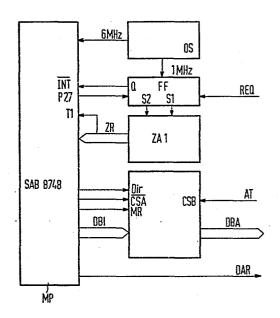

Das in Figur 1 gezeigte Blockschaltbild eines Zeitgebers enthält einen Oszillator OS, der ein Taktsignal von 6 MHz für einen Mikroprozessor MP und einen Zähltakt von 1 MHz 10 für die Zähleinrichtung erzeugt. Die Zähleinrichtung besteht dabei aus einem ersten Zählerteil ZA1 und einem zweiten Zählerteil, der in dem Mikroprozessor MP enthalten ist. Zwischen dem Oszillator OS und dem ersten Zählerteil ZA1 ist eine bistabile Kippschaltung FF eingeschaltet, die von 15 einer Zeitnahmeanforderung REQ von einem Verbraucher zurückgesetzt werden kann bzw. von einem Signal des Mikroprozessors MP gesetzt werden kann. Aus dem Zähltakt 51 von 1 MHz wird nämlich ein Übernahmetakt S2 gewonnen, der gegenüber dem Zähltakt phasenverschoben ist. Dieser Übernahmetakt <sup>\$2</sup> 20 kann mit Hilfe der bistabilen Kippschaltung FF unterbrochen werden. Der Übernahmetakt \$2 liegt ebenfalls am ersten Zählerteil ZA1 an und bewirkt, daß ein im ersten Zählerteil ZA1 enthaltenes Zwischenregister den Inhalt des im ersten Zählerteil ZA1 ebenfalls enthaltenen ersten Zählers über-25 nimmt.

Der Inhalt des Zwischenregisters im ersten Zählerteil ZA1 kann über einen Bus ZR in den Mikroprozessor MP übernommen werden. Der Ausgang der höchstwertigen Zählstelle des er30 sten Zählerteils ZA1 wird an einen Eingang T1 des Mikroprozessors MP angelegt, von dem er an den Eingang des internen Zählers oder zweiten Zählerteils im Mikroprozessor MP angelegt wird.

35 Zwischen Verbraucher und Mikroprozessor MP kann schließlich ein Pufferspeicher PF angeordnet werden, in den bei Vorlie-

gen einer Zeitnahmeanforderung REQ der Inhalt der Zähleinrichtung über einen Bus DBI übertragen wird und aus dem

mit Hilfe eines vom Verbraucher gelieferten Auslesetaktes

AT dieses Zählergebnis an den Verbraucher ausgelesen werden

kann. Das Zählergebnis wird dabei über den Bus DBA abgegeben. Über eine Steuerleitung DAR wird dem Verbraucher mitgeteilt, daß die auszulesenden Daten bereitstehen.

Dem Mikroprozessor MP wird am Eingang TNT mitgeteilt, wenn

10 eine Zeitnahmeanforderung REQ anliegt, um den Mikroprozessor

MP zu veranlassen, den Inhalt des ersten Zählerteils ZA1 einzulesen. Wenn dies geschehen ist, gibt der Mikroprozessor

MP am Ausgang P27 ein Signal ab, das die bistabile Kippschaltung FF wieder setzt und damit den Übernahmetakt S2 wieder

15 an die erste Zähleinrichtung ZA1 anlegt.

Eine genaue Realisierung des Zeitgebers nach Figur 1 ergibt sich aus Figur 2. Hier ist zunächst der Aufbau des Oszillators OS dargestellt. Dieser enthält einen Schwingquarz SQ, 20 der z.B. Taktsignale TS der Frequenz von 6 MHz erzeugt. Diese Taktsignale werden über Inverter einem Zähler Z1 zugeführt, der die vom Schwingquarz SQ abgegebene Frequenz von 6 MHz in eine Frequenz von 1 MHz umwandelt. Am Ausgang des Zählers Z1 werden somit die Zähltakte S1 abgegeben. Die Taktsignale TS bzw. die invertierten Taktsignale TS werden dem Mikroprozessor MP zugeleitet und zwar den Eingängen XTAL1 bzw. XTAL2 des Mikroprozessors MP. Dabei wird als Mikroprozessor MP ein Baustein SAB 8748 gewählt.

30 Aus den Zähltakten S1 werden die Übernahmetakte S2 mit Hilfe einer Verzögerungsschaltung VZ gewonnen, die aus NAND Gliedern aufgebaut ist. Die Übernahmetakte S2 treten synchron zu den Zähltakten S1 auf, sind jedoch gegenüber diesen Zähltakten S1 phasenverschoben. Die Übernahmetakte S2 können 35 schließlich mit Hilfe des NAND-Gliedes ND1 der Verzögerungs-

schaltung VZ abgeschaltet werden.

Das Abschalten der Übernahmetakte S2 über das NAND Glied ND1 erfolgt mit Hilfe der bistabilen Kippschaltung FF. Der Setzeingang der bistabilen Kippschaltung FF ist mit dem Ausgang P27 des Mikroprozessors MP verbunden. Am Rücksetzeingang der bistabilen Kippschaltung FF liegt ein Zeitnahmeanforderungsignal REQ an. Solange somit keine Zeitnahme angefordert wird, ist die bistabile Kippschaltung FF gesetzt 10 und damit das NAND Glied ND1 freigegeben, so daß die Übernahmetakte S2 am Ausgang der Verzögerungsschaltung VZ abgegeben werden. Tritt dagegen eine Zeitnahmeanforderung REQ von einem Verbraucher auf, wird die bistabile Kippschaltung FF zurückgesetzt und damit das NAND Glied ND1 gesperrt. Da-15 mit wird das Auftreten der Übernahmetakte S2 am Ausgang der Verzögerungsschaltung VZ unterbunden. Gleichzeitig wird an den Eingang TNT des Mikroprozessors MP ein Signal angelegt, das dem Mikroprozessor MP mitteilt, daß eine Zeitnahmeanforderung von einem Verbraucher vorliegt.

20

Die Zähltakte S1 und die Übernahmetakte S2 werden dem ersten Zählerteil ZA1 zugeführt. Der erste Zählerteil ZA1 ist in TTL Technik realisiert und nimmt die niederwertigen Zählstellen auf. Er besteht in Figür 2 aus zwei Teilen Z2 und Z3. Jeder Teil Z2 bzw. Z3 weist vier Zählstellen auf, so daß der gesamte Zählerteil ZA1 acht Zählstellen hat. Die Bauteile Z2 und Z3 können z.B. synchrone Binärzähler 74 LS 691 sein, die jeweils ein Zwischenregister enthalten. Den Bausteinen Z2 und Z3 des ersten Zählerteils ZA1 werden sowohl die Zähltakte S1 als auch die Übernahmetakte S2 zugeführt. Die Bausteine Z2 und Z3 sind dabei üblicherweise zu einem Zähler zusammengefaßt. Der vom Baustein Z2 abgegebene Übertrag "Carry" wird dabei dem Freigabeeingang EN des Bauteils Z3 zugeführt. Die Bauteile Z2 und Z3 sind über Busse ZR mit mit Mikroprozessor MP verbunden, über die der Jählinhalt in

den Mikroprozessor MP übertragen werden kann. Dabei wird der Inhalt der Zwischenregister, der vom Zähler in Abhängigkeit des Übernahmetaktes S2 übernommen worden ist, an den Mikroprozessor MP an den Eingängen P10 bis P13 bzw. P14 bis P17 übertragen. Der Ausgang der höchstwertigsten Zählstelle des ersten Zählerteiles ZA1 wird weiterhin am Eingang T1 des Mikroprozessors MP angelegt. Durch die an diesem Eingang T1 auftretenden Signale wird der interne Zähler des Mikroprozessors MP hochgezählt. Der interne Zähler des Mikroprozessors MP oder zweite Zählerteil besteht aus dem internen Zähler und internen Registern des Mikroprozessors MP. Der zweite Zählerteil kann z.B. aus dem internen Zähler und fünf Registern bestehen. Dann hätte der interne oder zweite Zählerteil eine Breite von 48 bit und der gesamte Zähler eine 15 Breite von 56 bit.

Die Übergabe des Inhalts des ersten Zählerteils ZA1 in den Mikroprozessor MP kann durch ein Signal am Ausgang P21 veranlaßt werden. Dieses Signal am Ausgang P21 wird dann auf-20 treten, wenn eine Zeitnahmeanforderung REQ bzw. ein Signal am Eingang TNT am Mikroprozessor anliegt.

Die Zusammenschaltung des Pufferspeichers PF mit dem Mikroprozessor MP ergibt sich aus Figur 2. Als Mikroprozessor

25 kann ein Baustein WD 1510-01 gewählt werden. Mit Hilfe des

Signals am Ausgang P24 kann der Mikroprozessor MP die Richtung festlegen, in der die Daten übertragen werden. Sollen

dabei Daten vom Mikroprozessor MP in den Pufferspeicher PF

übertragen werden, so wird dies dem Pufferspeicher PF am

30 Eingang DIR mitgeteilt und anschließend ein Freigabesignal

am Eingang CSA angelegt. Dann können die Daten, d.h. der Zählerinhalt, über den Bus DBI in den Pufferspeicher PF übertragen werden.

Über die Leitung DAR, die am Ausgang P25 angeschlossen ist, wird dem Verbraucher mitgeteilt, daß die Daten, das Zählergebnis, im Pufferspeicher bereitliegt. Der Verbraucher kann dann mit dem Auslesetakt AT, der am Freigabeeingang CSB anliegt, die Daten über den Bus DBA abrufen.

Die weiteren in Figur 2 dargestellten Verbindungen zwischen den einzelnen Bausteinen sind bekannt und können den Datenblättern der entsprechenden Bausteine entnommen werden.

10

Unter der Annahme, daß der Zähltakt 1 MHz ist, beträgt die Auflösung der Zähleinrichtung 1 usec. Es ist zweckmäßig den Übernahmetakt S.2 jeweils 500 ns nach dem Zähltakt S.1 auftreten zu lassen. Der Übernahmetakt S.1 tritt dann zu einem 15 Zeitpunkt auf, zu dem der Zähler im ersten Zählerteil bereits zur Ruhe gekommen ist. Erst jetzt kann der Inhalt des Zählers in das Zwischenregister übernommen werden. Der Zählers in das Zwischenregister übernommen werden. Der Zählers in das Zwischenregister übernommen werden. Der Zählers in des Zwischenregister übernommen werden.

- reits zur Ruhe gekommen ist. Erst jetzt kann der Inhalt des Zählers in das Zwischenregister übernommen werden. Der Zähler zählt die Zähltakte weiter, ohne daß er durch die übernahme des Inhalts des Zähler in das Zwischenregister ge-

- 20 stört würde. Bei Auftreten einer Zeitnahmeanforderung wird der Übernahmetakt S:2 gesperrt, jedoch höchstens für die halbe Zeit zwischen zwei Überläufen des ersten Zählerteils. Dadurch wird verhindert, daß während der Übernahme des Inhalts des ersten Zählerteils in den Mikroprozessor MP ein den zwei-

- 25 ten Zählerteil im Mikroprozessor MP erhöhende Übertrag am Eingang T1 unterdrückt wird.

Aus Figur 3 ergibt sich eine weitere Ausbildung des Zeitgebers. Ein Oszillator OS erzeugt sowohl einen Takt von

30 6 MHz für einen Mikroprozessor MP als auch einen Zähltakt

S1 für die Zähleinrichtung. Der Oszillator OS kann entsprechend Figur 2 realisiert sein. Der Zähltakt S1 wird einem

Zähler Z4 zugeführt, der zusammen mit dem Zwischenregister

ZW den ersten Zählerteil bildet. Das Zwischenregister ZW

35 kann als first-in / first-out Speicher realisiert sein und

aus dem Baustein WD 1510-01 bestehen.

Der Inhalt des Zählers Z4 wird dann in das Zwischenregister ZW übertragen, wenn beim Zähler Z4 ein Zählübertrag ZU auftritt bzw. eine Zeitnahmeanforderung REQ anliegt. Ein übertrag ZU am Zähler Z4 wird an einer negativen Flanke des Bits 2<sup>7</sup> des Zählers Z4 festgestellt, wenn der Zähler Z4 aus acht Zählstellen besteht.

Das Übertragssignal ZU und das Zeitnahmeanforderungssignal REQ wird dazu verwendet, eine Anordnung zur Durchschaltung 10 des Übernahmetaktes S2 an das Zwischenregister ZW anzusteuern.

Die Anordnung zur Durchschaltung des Übernahmetaktes S2 besteht aus monostabilen Kippschaltungen M1 und M2, einem Zäh15 ler Z5, NOR Gliedern NR1 bis NR3 und einem Inverter IN.

Die monostabile Kippschaltung M2 erzeugt aus dem Übertragssignal ZU vom Zähler Z4 einen Impuls P1 von z.B. 800 ns. Dieser erste Impuls P1 wird dem NOR Glied NR1 zugeführt und ge-

- 20 langt von dort zum NOR Glied NR2, wodurch der Übernahmetakt S2 an den Freigabeeingang CSA des Zwischenregisters ZW angelegt wird. Damit wird der Inhalt des Zählers Z4 in das Zwischenregister ZW übernommen. Zu diesem Zeitpunkt ist der Inhalt des Zählers Z4 auf allen Zählstellen binär O. Liegt

- 25 von einem Verbraucher eine Zeitnahmeanforderung REQ vor, dann erzeugt die monostabile Kippschaltung M1 aus der Rückflanke des zugeordneten Signals einen Impuls P2 von z.B. 100 ns Länge. Mit dem Impuls P2 wird der Zähler Z5 zurückgesetzt. Durch den nächsten Zähltakt S1 wird dann der Zähler Z5 über

- 30 das NOR Glied NR3 am Zähleingang angesteuert und damit die Zählstelle 2<sup>0</sup> binär 1. Damit erscheint am Ausgang der Zählstelle 2<sup>0</sup> der Impuls P3, der über das NOR Glied NR1 dem NOR Glied NR2 zugeführt wird, wodurch wieder der übernahmetakt S2 an den Freigabeeingang CSA des Zwischenregisters ZW ange-

- 35 legt wird. Damit wird der Inhalt des Zählers Z4 in das Zwischenregister ZW eingelesen. Mit dem nächsten Zähltakt S1 wird die Zählstelle 2<sup>1</sup> des Zählers Z5 gesetzt, die mit dem

NOR Glied NR3 verbunden ist, dem auch der Zähltakt S1 zugeführt wird. Damit wird verhindert, daß weitere Zähltakte S1 zum Zähler Z5 gelangen.

- Der Inhalt des Zählers Z4 wird somit nur dann in das Zwischenregister ZW übertragen, wenn entweder ein Zählerübertrag ZU oder eine Zeitnahmeanforderung REQ vorliegt. Denn

nur dann wird der Übernahmetakt S2 an das Zwischenregister

ZW angelegt. Da der Ausgang 2<sup>0</sup>des Zählers Z5 außerdem mit

- 10 dem Zwischenregister ZW direkt verbunden ist, wird für jedes in das Zwischenregister ZW übernommene Zählergebnis vom Zähler Z4 auch eingetragen, ob der Grund für die Übernahme eine Zeitnahmeanforderung REQ war.

- 15 Der Mikroprozessor MP ist mit dem Ausgang des Zwischenregisters ZW über den Bus ZR verbunden und liest ständig durch Signale am Freigabeeingang CSB den Inhalt des Zwischenregisters ZW ein, solange das Zwischenregister ZW nicht leer ist. Dabei erkennt der Mikroprozessor MP einen Überlauf ZU

- 20 am Zählerstand O und erhöht den internen Teil des Zählers, also den zweiten Zählerteil, der die hochwertigen Zählstellen enthält, um eine Einheit. Erkennt der Mikroprozessor MP am Eingang TO aus dem Inhalt des übernommenen Ergebnisses aus dem Zwischenregister ZW, daß eine Zeitnahmeanforderung

- 25 REQ zur Übernahme des Zählergebnisses geführt hat, dann veranlaßt der Mikroprozessor MP die Übergabe des Zählergebnisses, also der Zusammenfassung des Zählergebnisses vom

Zähler Z4 und vom internen Zähler, über den Bus DB zum anfordernden Verbraucher.

30

Der Zeitgeber nach Figur 4 unterscheidet sich von der Figur 3 dadurch, daß an den Ausgang der monostabilen Kippschaltung M2 ein weiterer Zähler Z6 angeschaltet ist. Der Ausgang 2<sup>0</sup> des Zählers Z6 ist mit einem NOR Glied NR4 ver- 35 bunden, dem auch der Zähltakt S1 zugeführt wird. Der Aus-

gang des NOR Gliedes NR4 liegt dann am Zähleingang des Zählers Z6. Mit Hilfe des am Ausgang der monostabilen Kippschaltung M2 abgegebenen Impulses P1 wird der Zähler Z6 zurückgesetzt und dann durch den Zähltakt S1 wieder gesetzt.

5 Erst jetzt erscheint synchron zum Zähltakt S1 am Ausgang des Zählers Z6 der Impuls P4, der das NOR Glied NR2 freigibt, so daß der nächste Übernahmetakt S2 zum Freigabeeingang CSA des Zwischenregisters ZW gelangen kann. Durch die Einfügung des Zählers Z6 wird somit eine Synchronisierung des Impulses P4, der von dem Übertragsignal ZU ausgelöst wird, auf den Zähltakt S1 erreicht. Die Übrige Schaltung entspricht der der Figur 3, bis auf die Ausnahme, daß zur Erzeugung des Übernahmetaktes S2 aus dem Zähltakt S1 noch weitere Inverterglieder zur Bildung einer Verzögerungsschaltung VZ vorgesehen sind.

Die Reihenfolge des Auftretens der einzelnen Impulse in Figur 4 ergibt sich aus Figur 5. Hier ist in der ersten Zeile der Zähltakt S1 dargestellt. Aus dem Zähltakt S1 wird 20 mit Hilfe der Verzögerungsschaltung VZ der Übernahmetakt S2 erzeugt, der um die Zeit T0 gegenüber dem Zähltakt S1 phasenverschoben ist. In der dritten Zeile ist der Verlauf des Impulses P4 am Ausgang des Zählers Z6 dargestellt. Es ist zu sehen, daß nach Auslösung durch das Übertragssignal ZU 25 die Flanken des Impulses P4 zum Zeitpunkt der Rückflanken des Zähltaktes S1 auftreten.

Die vierte Zeile der Figur 5 zeigt den Verlauf des Impulses P3 am Ausgang des Zählers Z5. Voraussetzung für dessen Auf-30 treten ist das Anliegen eines Zeitnahmeanforderungssignales REQ. Es ist zu sehen, daß die Flanken des Impulses P3 ebenfalls mit den Rückflanken des Zähltaktes S1 auftreten.

Durch die Impulse P3 und P4 wird festgelegt, wann der Über-35 nahmetakt S2 an den Auslöseeingang CSA des Zwischenregisters ZW anliegt. Der Verlauf des Signals am Eingang cSA des Zwischenregisters ZW ist in der letzten Zeile der Figur 4 gezeigt. Auslösende Flanken sind dabei die mit AF dargestellten Impulsflanken. Diese treten synchron zu Flanken des Übernahmesignals S2 auf.

Ein Vorteil der Ausführungsbeispiele der Figur 3 und der Figur 4 gegenüber dem Ausführungsbeispiel der Figur 1 und der Figur 2 besteht darin, daß die Meßwiederholfrequenz er10 heblich größer ist.

10 Patentansprüche5 Figuren

## Patentansprüche

abgibt.

- 1. Zeitgeber mit hoher Auflösung unter Verwendung einer Zähleinrichtung, die die von einem Oszillator gelieferten 5 Zähltakte zählt und deren Inhalt ein Maß für die Zeit ist, bei dem die Zähleinrichtung aus einem ersten, die niederwertigen Zählstellen umfassenden den Zähltakt zählenden Zählerteil und aus einem zweiten, die höherwertigen Zählstellen umfassenden, mit dem höchstwertigen Zählstellenausgang 10 des ersten Zählerteils verbundenen Zählerteil besteht, dagekennzeichnet , daß der erste in einer schnellen Schaltkreistechnik realisierte Zählerteil (ZA1 bzw. Z4, ZW) aus einem ersten Zähler (Z4) für die niederwertigeren Zählstellen und aus einem Zwischenregister 15 (ZW) besteht, daß der Inhalt des ersten Zählers in Abhängigkeit eines mit dem Zähltakt (S1) synchron jedoch phasenverschoben auftretenden Übernahmetakt (S2) übernehmbar ist, und daß der zweite in einer langsameren Schaltkreistechnik realisierte Zählerteil aus einem Mikroprozessor (MP) be-20 steht, bei dem interne Zähler und Register einen zweiten Zähler für die höherwertigeren Zählerstellen bilden und der bei Anlegen einer Zeitnahmeanforderung (REQ) von einem Verbraucher den Inhalt des Zwischenregisters des ersten Zählerteils übernimmt und diesen Inhalt zusammen mit dem In-25 halt des zweiten Zählers an den anfordernden Verbraucher

- Zeitgeber nach Anspruch 1, dadurch gekennzeich net, daß der erste Zählerteil (ZA1 bzw. Z4, ZW) in

TTL Technik und der zweite Zählerteil (MP) in MOS Technik realisiert ist.

- Zeitgeber nach Anspruch 1 oder 2, dadurch gekenn-zeich net, daß zwischen Oszillator (OS) und erstem

Zählerteil (ZA1 bzw. Z4, ZW) eine Verzögerungsschaltungs(VZ)

zur Erzeugung des Übernahmetaktes (S2) aus dem Zähltakt (S1) angeordnet ist.

- 4. Zeitgeber nach Anspruch 3, dadurch gekenn -5 zeichnet , daß eine bistabile Kippschaltung (FF) vorgesehen ist, die bei Anliegen einer Zeitnahmeanforderung (REQ) den Ausgang der Verzögerungsschaltung (VZ) sperrt und nach Bearbeitung der Zeitnahmeanforderung durch den Mikroprozessor (MP) die Verzögerungsschaltung später freigibt.

- 5. Zeitgeber nach einem der Ansprüche 1 bis 4, dadurch gekennzeich net, daß zwischen Mikroprozessor (MP) und Verbraucher ein Pufferspeicher (PF) angeordnet ist, in den der Mikroprozessor bei Anliegen einer Zeitnahmean-

- 15 forderung (REQ) das Zählergebnis überträgt und von dem der Verbraucher mit einem Auslesetakt (AT) das Zählergebnis übernimmt.

- 6. Zeitgeber nach Anspruch 1 oder 2, dadurch ge 20 k e n n z e i c h n e t , daß das Zwischenregister (ZW) aus einem first-in / first-out Speicher besteht, daß dem Oszillator (OS) eine Verzögerungsschaltung (VZ) nachgeschaltet ist, die aus dem Zähltakt (S1) den Übernahmetakt (S2) erzeugt, und daß eine Anordnung zur Durchschaltung des Über-

- 25 nahmetaktes an das Zwischenregister (ZW) vorgesehen ist, die den Übernahmetakt (S2) an den Freigabeeingang (CSA) des Zwischenregisters anlegt, wenn der erste Zähler (Z4) einen Übertrag (ZU) anzeigt oder wenn eine Zeitnahmeanforderung (REQ) anliegt.

7. Zeitgeber nach Anspruch 6, gekennzeich - net durch die Anordnung aus einer ersten monostabilen Kippschaltung (M2), an der das Übertragssignal (ZU) des ersten Zählers (Z4) anliegt und die daraus einen ersten 35 Impuls (P1) erzeugt, aus einer zweiten monostabilen Kipp-

30

schaltung (M1), an der die Zeitnahmeanforderung (REQ) anliegt und die daraus einen zweiten Impuls (P2) erzeugt, aus

einem dritten Zähler (Z5), an dessen Rücksetzeingang der

zweite Impuls (P2) anliegt, dessen Zähleingang mit einem

5 an den Oszillator (OS) und den 2<sup>1</sup>-Ausgang des dritten Zählers angeschlossenen NOR Glied (NR3) verbunden ist und dessen 2<sup>0</sup>-Ausgang einen dritten Impuls (P3) abgibt und aus einer

Verknüpfungsschaltung (NR1, NR2), an der der Übernahmetakt

(\$2) und der erste und dritte Impuls (P1, P3) anliegt und

10 die für das Zwischenregister (ZW) synchron zu dem Übernahmetakt ein Signal zur Übernahme des Inhalts des ersten Zählers

(Z4) erzeugt, wenn entweder ein Übertragssignal (ZU) oder

eine Zeitnahmeanforderung (REQ) vorliegt.

15 8. Zeitgeber nach Anspruch 7, dadurch gekenn - zeichnet , daß zwischen der ersten monostabilen Kippschaltung (M2) und der Verknüpfungsschaltung (NR1,NR2) ein vierter Zähler (Z6) angeordnet ist, dessen Rücksetzeingang mit dem Ausgang der ersten monostabilen Kippschaltung 20 (M1) verbunden ist, dessen Zähleingang mit einem an den Oszillator (OS) und den 20-Ausgang des vierten Zählers (Z6) angeschlossenen NOR Glied (NR4) verbunden ist und der am 20-Ausgang den der Verknüpfungsschaltung zuzuführenden Impuls (P4) erzeugt.

25

9. Zeitgeber nach Anspruch 7 oder 8, dadurch gekennzeich net , daß der  $2^0$ -Ausgang des dritten Zählers (Z5) direkt mit dem Eingang für eine Speicherstelle des Zwischenregisters (ZW) verbunden ist.

30

10. Zeitgeber nach einem der Ansprüche 6 bis 9, dadurch g e k e n n z e i c h n e t , daß der Mikroprozessor (MP) ständig die in das Zwischenregister (ZW) eingeschriebenen Zählerinhalte ausliest und bei Zählerinhalt 0 den zweiten 35 Zählerinhalt um eine Einheit erhöht.