(1) Publication number:

**0 150 600** A2

12

## **EUROPEAN PATENT APPLICATION**

21 Application number: 84308746.1

1 Int. Cl.4: H 01 H 13/70

② Date of filing: 14.12.84

30 Priority: 22.12.83 US 564278

- 7) Applicant: AMP INCORPORATED, P.O. Box 3608 449 Eisenhower Boulevard, Harrisburg Pennsylvania 17105 (US)

- Date of publication of application: 07.08.85

Bulletin 85/32

- Inventor: Bures, Milan, 5294 Crown Point Drive, Tobaccoville, NC 27050 (US) Inventor: Rowlette, John Robert, 720 LaVale Drive, Clemmons, NC 27012 (US)

- Ø Designated Contracting States: BE DE FR GB IT NL

- (GB)

Representative: Gray, Robin Oliver et al, BARON & WARREN 18 South End Kensington, London W8 5BU

- (54) Membrane switch assembly.

- (5) A membrane switch assembly (10) is comprised of spaced apart layers (12, 16) having corresponding patterns of conductive switch contacts (28, 28') arranged in series thereon, the layers (12, 16) being separated by spacing means (20) having openings therein. The switch contacts (28, 28') on each layer are spaced along a single conductive path (24, 24') so that a regular unit value of impedance means exists between the switch contacts (28, 28'). When the electrical circuit is completed by closing a switch site, the resulting total impedance is essentially equal to the sum of the unit values of the impedance means along the circuit path formed by the closed switch.

## "MEMBRANE SWITCH ASSEMBLY"

The invention relates generally to membrane or diaphragm switches, and more specifically, to membrane keyboard switch assemblies used for data entry.

5

10

15

20

25

30

In recent years, the need has increased for reliable and economical membrane or diaphragm keyboard switch assemblies for use in data entry technology. Typically, these switches are comprised of a base substrate and a flexible layer separated by spacing means. The spacing means has a plurality of openings constituting switch sites. The internal surfaces of both the substrate and flexible layer have a pattern of conductive switch contacts thereon, the switch contacts on the layer being aligned with the openings in the spacing means.

The conductive switch contacts are most generally arranged in the form of a matrix. The circuit path is completed between the rows and columns of the matrix by depressing the upper layer so that it touches the lower layer. In order to determine which switch site has been pressed, it is necessary to electronically actuate the columns individually and scan the rows of the matrix for the resulting signals.

According to the invention a membrane switch assembly comprised of a base substrate and at least one flexible layer separated from each other by spacing means, the spacing means having a plurality of openings therein constituting switch sites, the internal surfaces of layers adjacent the spacing means having a pattern of conductive switch contacts thereon, the switch contacts on the surfaces being aligned with the openings

in the spacing means, the membrane switch assembly

is characterised in that:

5

10

15

the conductive switch contacts on each surface are interconnected in series along a single conductive path,

the contacts of the series are spaced along the respective single paths so that in each path the value of impedance existing between successive switch contacts bears a regular relationship to the impedance of the path to the succeeding and/or from the preceding switch contact, the change in impedance between each pair of adjacent switch contacts being uniformly incremental along the path whereby, when an electrical circuit is completed by applying force to the flexible layer to bring together the conductive switch contacts of the substrate and flexible layer, the resulting total impedance is essentially equal to the sum of the unit values of the impedance means along the circuit path formed by the closed switch.

The present invention discloses a membrane switch assembly in which the conductive switch contacts on each layer are interconnected in series along a single conductive path in such a way that a regular unit value of impedance means exists between the switch contacts. The unit value of impedance means on one layer may be the same or different from the unit value of impedance means on the other layer.

Moreover, it has been discovered that for ease of manufacturing the switches, it is preferable that the unit value of impedance used on one layer be significantly different from the unit value on the

٤..:٤

25

30

other layer. It is understood, however, that the unit values of impedance on different layers may be varied in any proportion without departing from the spirit or scope of the invention. The impedance means may present resistance, capacitance or an

10 inductance between successive switch contacts.

When the circuit is completed at a switch site, the signal received is essentially equal to the summation of the unit values along the circuit path. This analog signal can be directly converted to digital.

15 There is an economy of electronic implementation by utilization of an analog to digital converter.

Increased number of switches can be utilized for a given summation of unit impedance means by utilization of increased digital word length of the A/D converter.

If more than one switch is closed at the same time, the signal received will be from the switch having the shortest circuit path. The invention disclosed herein is therefore protected from false readings owing to the "phantom key" effect which can occur with a matrix switch array.

The output signal from the switch depends on the ratio of the summation of unit value impedance means to that switch site to a reference impedance or to the totality of unit value of 5

10

15

20

25

30

impedance means. The output signal therefore is independent of variations in environmental and physical changes that may occur to the switches.

The invention will now be described by way of example with reference to the accompanying partly diagrammatic drawings in which:

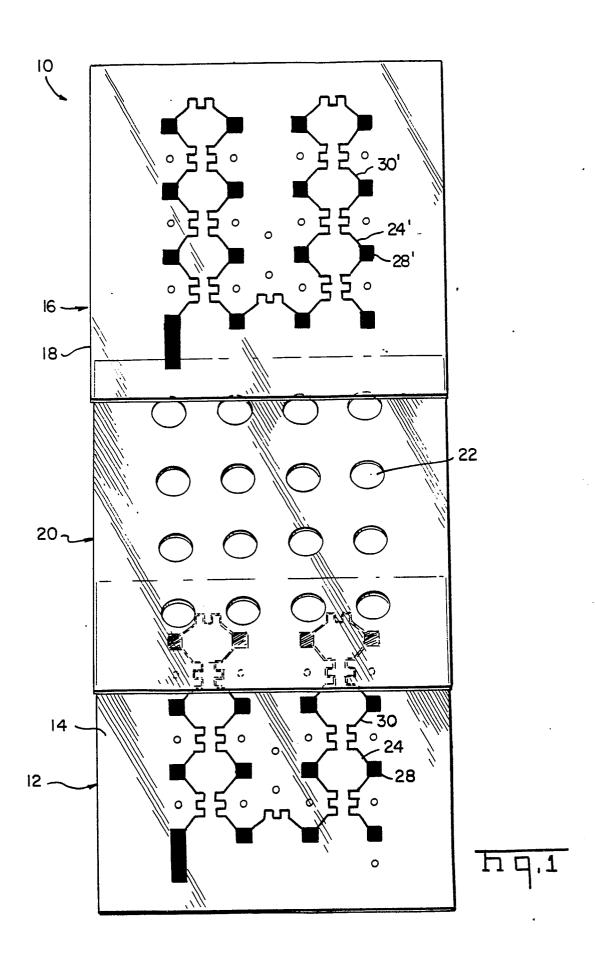

FIGURE 1 is an exploded view of the present invention.

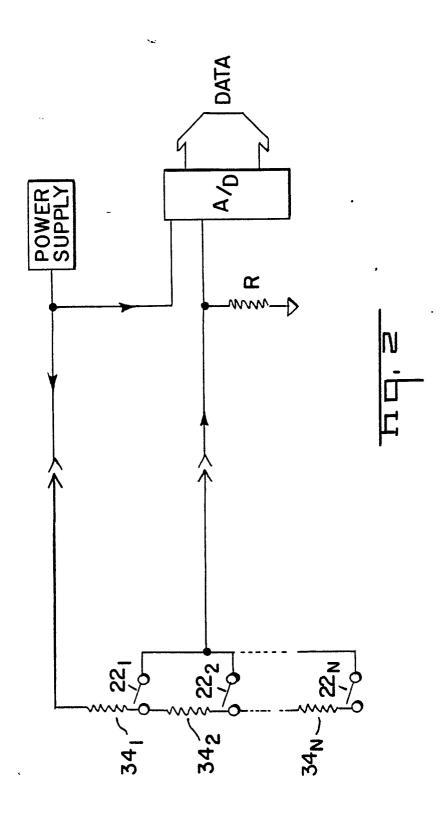

FIGURE 2 is a circuit schematic for the herein disclosed invention.

As is shown in Figure 1, the membrane switch assembly 10 is comprised of an insulating substrate 12, an insulating spacing means 20 and an insulating film layer 16. Spacing means 20 separates the internal surface 14 of substrate 12 and the internal surface 18 of layer 16. Spacing means 20 has openings 22 therein which constitute switch sites.

The internal surfaces 14 and 18 have a pattern of conductive switch contacts 28 and 28' respectively, thereon. The contacts 28 on surface 14 are interconnected in a series along a single conductive path 24. The contacts 28' on surface 18 are interconnected in a series along a single conductive path 24'. Switch contacts 28 are spaced apart and aligned with switch contacts 28' and with switch sites 22 in the completed assembly.

In accordance with the invention, conductors 24 and 24' are deposited on surfaces 14 and 18 respectively, so that a regular unit value of impedance means 30, 30' exists between successive switch contacts 28, 28'. The unit values of impedance 30 and 30' need not be the same for both layers.

In the preferred embodiment, the impedance means presents a resistance between successive switch contacts. For ease of manufacture, different unit values of resistance are used on the layers. In addition, the change of impedance between any two adjacent switch contacts is uniformly incremental. Conductive ink is used for the conductor paths in the preferred embodiment. Other means as known in the art can be used to

form the conductive paths.

5

10

15

20

Figure 2 is the circuit schematic for the preferred embodiment. Successive switch sites 22 and resistors 34 are denoted by subscripts. When force is applied at a switch site 22, the signal is essentially equal to the summation of the series of unit values of impedance along with the path of the completed electrical circuit. Thus, if the circuit is completed at switch site  $22_2$ , the signal would be equal to the sum of the impedance of resistors  $34_1$ ,  $34_2$ .

The invention as disclosed can be used, for example, in calculators, and keyboards for typewriters and computers. The invention also can be used for multiple layers of switches by using additional flexible conductive layers. The invention further can be used in touch entry devices for mounting on CRT's if in addition to layer 16, substrate 12 and spacing means 20 are also flexible layers.

While in the preferred embodiment the impedance characteristic is resistance, the paths may be inductive or capacitive so that variations in inductive and capacitive impedance is sensed. For example the conductive paths may be defined by pairs of spaced conductors extending in parallel or otherwise.

## CLAIMS

1. A membrane switch assembly (10) comprised of a base substrate (12) and at least one flexible layer (16) separated from each other by spacing means (20), the spacing means (20) having a plurality of openings

5 (22) therein constituting switch sites, the internal surfaces (14,18) of layers (12,16) adjacent the spacing means having a pattern of conductive switch contacts (28,28') thereon, the switch contacts (28,28') on the surfaces (14,18) being aligned with the openings (22) in the spacing means (20), the membrane switch assembly (10) being characterised in that:

the conductive switch contacts (28,28') on each surface (14,18 ) are interconnected in series along a single conductive path (24,24'),

along the respective single paths so that in each path the value of impedance (30,30') existing between successive switch contacts (28,28') bears a regular relationship to the impedance of the path to the succeeding and/or from the preceding switch contact,

- the change in impedance between each pair of adjacent switch contacts being uniformly incremental along the path whereby, when an electrical circuit is complete by applying force to the flexible layer (16) to bring together the conductive switch contacts (28,28')

- of the substrate (12) and flexible layer (16), the resulting total impedance is essentially equal to the sum of the unit values of the impedance means along the circuit path formed by the closed switch.

- The membrane switch assembly (10) as recitedin claim 1 further characterised in that the impedance

- means presents a resistance along the conductive paths (24,24').

- 3. The membrane switch assembly (10) as recited in claim 1 further characterised in that the impedance

- 5 means presents a capacitance along the conductive paths (24,24').

- 4. The membrane switch assembly (10) as recited in claim 1 further characterised in that the impedance means presents an inductance along the conductive paths (24,24').

- 5. The membrane switch assembly (10) as recited in claim 2 wherein the resistance between any two adjacent switch contacts (28,28') increases with respect to the resistance between the previous two adjacent switch contacts (28,28').

- 6. A switch assembly as claimed in claim 1, characterised in that the conductive switch contacts (28) of the substrate (12) are interconnected so that the impedance (30) between successive adjacent switch

- contacts (28) of the series presents an equal first value of resistance, and the conductive switch contacts (28') of the flexible layer (16) are interconnected so that the impedance between successive adjacent switch contacts of the series presents an

- 25 equal second value of resistance.

10

15

- 7. The membrane switch assembly (10) as recited in claim 6 wherein said conductive paths (24,24') on layers (14,18) are conductive ink.

- 8. The membrane switch assembly (12) as recited in claim 6 wherein said first value of resistance is substantially greater than said second value of resistance.