(11) Numéro de publication:

**0 157 668** A1

12

#### **DEMANDE DE BREVET EUROPEEN**

(1) Numéro de dépôt: 85400398.5

61 Int. Cl.4: G 06 G 7/184

22) Date de dépôt: 01.03.85

30 Priorité: 05.03.84 FR 8403356

Demandeur: THOMSON-CSF, 173, Boulevard Haussmann, F-75379 Paris Cedex 08 (FR)

Date de publication de la demande: 09.10.85

Bulletin 85/41

(72) Inventeur: Berger, Jean-Luc, THOMSON-CSF SCPO 173, bld Haussmann, F-75379 Paris Cedex 08 (FR) Inventeur: Coutures, Jean-Louis, THOMSON-CSF SCPO 173, bld Haussmann, F-75379 Paris Cedex 08 (FR)

(84) Etats contractants désignés: DE GB NL

Mandataire: Ruellan-Lemonnier, Brigitte et al, THOMSON-CSF SCPI 173, boulevard Haussmann, F-75379 Paris Cedex 08 (FR)

### (54) Intégrateur analogique non récursif.

(5) La présente invention concerne un intégrateur analogique non récursif réalisant l'intégration d'un signal analogique échantillonné V<sub>n.m</sub> sur M séquences.

Cet intégrateur comporte un démultiplexeur d'entrée (A) série parallèle pour envoyer successivement sur N capacités de stockage (C¹, C², ...CN), reliées en parallèle au démultiplexeur d'entrée, M fois le signal analogique échantillonné, chaque capacité de stockage réalisant pour les M sé-

quences la sommation sous forme de charge  $(\sum_{n}^{\infty}, Q_{n,m})$  de l'échantillon de rang correspondant du signal analogique  $V_{n,m}$ . Il comporte, de plus, un multiplexeur (B) parallèle-série de sortie relié aux N moyens de stockage pour délivrer en sortie, à la fin de M séquences, un signal analogique  $(\sum_{n=1}^{\infty}, M V_{n,m})$ .

Cet intégrateur s'applique notamment à la détection des raies d'un spectre récurrent en sortie d'un analyseur à onde acoustique de surface.

### INTEGRATEUR ANALOGIQUE NON RECURSIF

La présente invention concerne un intégrateur analogique non récursif, notamment un intégrateur utilisant le transfert de charge pour réaliser l'intégration d'un signal analogique échantillonné sur M séquences.

Les intégrateurs sont en général utilisés dans le traitement de signaux analogiques pouvant être définis comme une séquence répétitive et à variation lente soit pour diminuer l'énergie du signal émis soit pour extraire du bruit le signal reçu. En effet, l'intégration de ces séquences répétitives permet d'améliorer le rapport signal/bruit d'un facteur \( \vec{M} \) si l'intégration porte sur M séquences. Ainsi des intégrateurs peuvent être utilisés, par exemple, pour la détection des raies d'un spectre recurrent en sortie d'un analyseur à onde accoustique de surface.

Les intégrateurs employés pour ce type de traitement peuvent être des intégrateurs numériques ou analogiques, récursifs ou nonrécursifs.

Les intégrateurs numériques présentent l'inconvénient de nécessiter un temps de traitement très long. D'autre part, la fréquence d'échantillonnage analogique et la dynamique sont limitées par le convertisseur analogique-numérique d'entrée.

Il existe aussi différents types d'intégrateurs analogiques récursifs ou non-récursifs utilisant des dispositifs à transfert de charge.

20

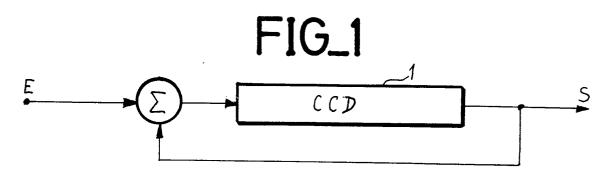

Comme représenté schématiquement sur la figure 1, les intégrateurs analogiques récursifs sont en général constitués par un registre à décalage à transfert de charge 1 dont le signal de sortie S est rebouclé sur le signal d'entrée E auquel il vient s'ajouter dans le sommateur \( \subseteq \). Toutefois, du fait de la détérioration de l'intégration due à l'inéfficacité de transfert dans le registre à transfert de charge 1, le nombre de rebouclage est limité. D'autre part, la génération thermique de charges dans le registre 1 entraîne une saturation rapide dudit registre et est un facteur d'instabilité dans la boucle.

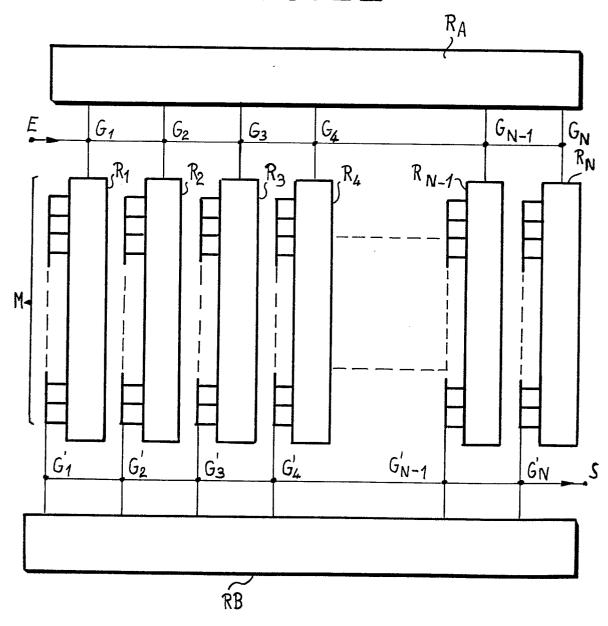

Comme représenté sur la figure 2, un intégrateur analogique non-récursif est constitué essentiellement par N registres à décalage à transfert de charge  $R_1, R_2, ..., R_N$ , à entrée série et sorties parallèles, chaque registre comportant M étages pour intégrer les M échantillons de rang n (n variant entre 1 et N) du signal d'entrée, les N registres  $R_1, R_2, ..., R_N$  étant montés entre un registre d'adressage d'entrée  $R_A$  et un registre d'adressage de sortie  $R_B$  adressant successivement, en commutant des portes analogiques  $G_1, ..., G_N$  et  $G'_1, ..., G'_N$ , les entrées ou les sorties des N registres à décalage  $R_1, R_2, ..., R_N$  pour d'abord entrer dans les registres à décalage  $R_1, R_2, ..., R_N$  M fois le signal d'entrée échantillonné E puis pour sortir un signal analogiques correspondant à la somme des signaux entrés. Toutefois, la génération thermique des registres à décalage du type à transfert de charge limite le temps d'intégration.

5

10

15

20

25

30

La présente invention a pour but de remédier à ces inconvénients en proposant un intégrateur analogique non récursif dans lequel la génération thermique au niveau des sites d'intégration est relativement faible, ce qui permet un temps d'intégration élevé.

La présente invention a, en conséquence, pour objet un intégrateur analogique non récursif réalisant l'intégration d'un signal analogique échantillonné  $V_{n,m}$  sur M séquences, caractérisé en ce qu'il comporte un démultiplexeur d'entrée série-parallèle pour envoyer successivement sur N capacités dont une électrode est à un potentiel flottant par rapport à un potentiel de référence, les capacités étant reliées en parallèle au démultiplexeur d'entrée, M fois le signal analogique échantillonné, chaque capacité réalisant pour les M séquences la sommation sous forme de charges de l'échantillon de rang correspondant au signal analogique  $V_{n,m}$  et en ce qu'il comporte un multiplexeur parallèle-série de sortie relié aux M moyens de stockage pour délivrer en sortie, à la fin des M séquences, un signal analogique  $\sum_{m=1,M} V_{n,m}$ .

Selon un mode de réalisation préférentiel, le démultiplexeur d'entrée est constitué par un registre à décalage à transfert de charge ou registre CCD (pour charge coupled device en langue

anglaise) à entrée série et sorties parallèles et le multiplexeur de sortie par un registre CCD à entrée parallèles et sortie série. L'utilisation de deux registres CCD comme démultiplexeur d'entrée et multiplexeur de sortie permet d'avoir une fréquence de fonctionnement élevée pour l'intégrateur. En effet, le transfert des charges à l'intérieur du registre de sortie vers l'étage de lecture est réalisé pendant au moins une partie du cycle d'intégration suivant. D'autre part, la fréquence de transfert dans le registre de sortie peut être relativement lente par rapport à la fréquence de transfert dans le registre d'entrée. En effet, la relation entre ces deux fréquences doit être

$$F_B \gg \frac{1}{M} F_A$$

dans laquelle:

5

10

15

20

25

30

$F_{\mathbf{p}}$  est la fréquence de transfert du registre de sortie  $F_A$  est la fréquence de transfert du registre d'entrée, et M est le nombre de séquences.

D'autre part, la charge transférable par un registre à décalage de type CCD étant limitée ( $\simeq 10^{\prime}$  électrons), de préférence, les capacités de stockage ou sites d'intégration sont constitués chacun par deux capacités dont une électrode est à un potentiel flottant, interconnectées par une porte analogique, avec de plus entre les capacités et le registre à décalage de sortie un dispositif d'aiguillage permettant d'envoyer les charges soit vers le registre à décalage de sortie soit vers un moyen d'évacuation des charges.

Selon un autre mode de réalisation, le multiplexeur de sortie peut être constitué par des portes analogiques connectées respectivement entre chaque moyen de stockage et l'étage de lecture, lesdites portes étant commandées successivement par une impulsion envoyée par un registre d'adressage. Dans ce cas, toutefois, il est nécessaire de réaliser la lecture de tous les moyens de stockage avant de recommencer l'intégration suivante au niveau desdits moyens de stockage.

D'autres caractéristiques et avantages de la présente invention apparaîtront à la lecture de la description de différents modes de réalisation d'intégrateurs analogiques non récursifs conformes à la présente invention, faite avec référence aux dessins ci-annexés dans lesquels:

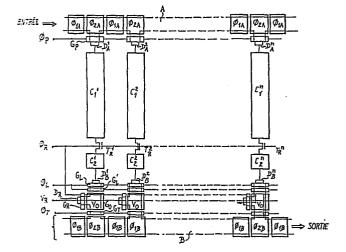

- la figure 1, déjà décrite, est une vue schématique d'un intégrateur analogique récursif de l'art antérieur,

- la figure 2, déjà décrite, est une vue schématique d'un intégrateur analogique non récursif de l'art antérieur,

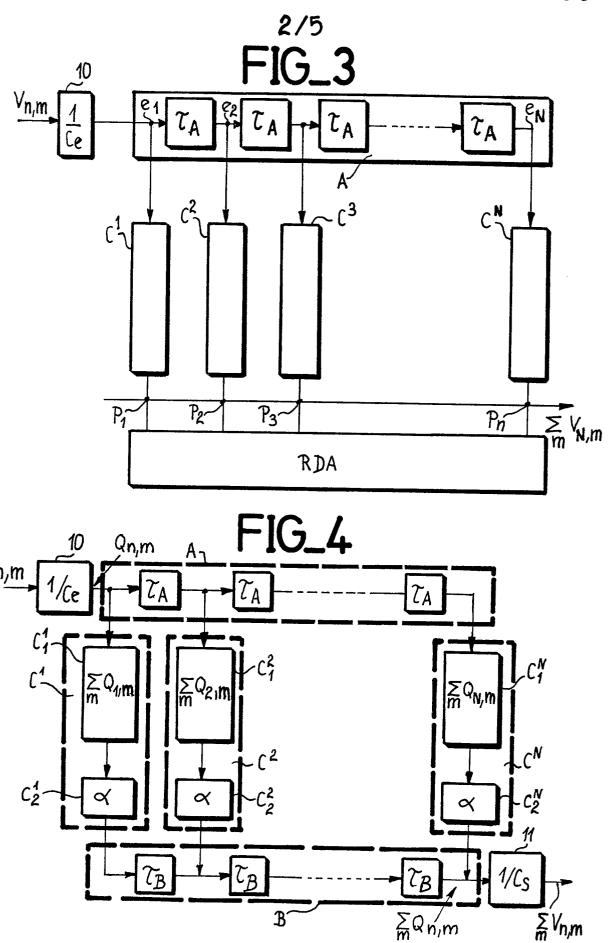

- la figure 3 est une vue schématique d'un intégrateur analogique non-récursif conforme à la présente invention,

- la figure 4 est une vue schématique d'un autre mode de réalisation d'un intégrateur analogique non-récursif conforme à la présente invention,

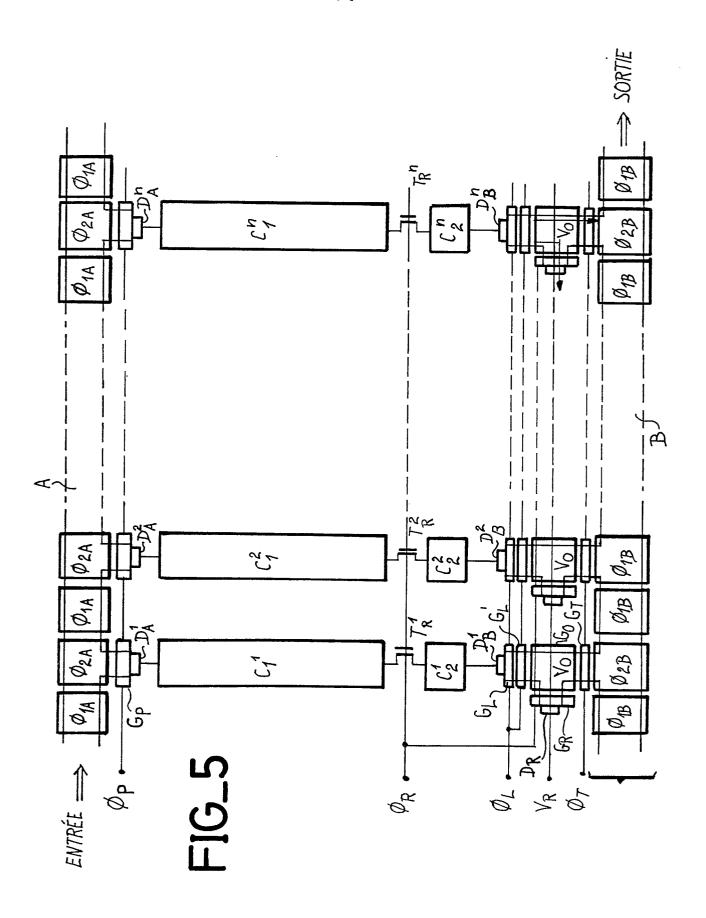

- la figure 5 est une vue en plan de dessus d'un mode de réalisation d'un intégrateur analogique non-récursif conforme à la présente invention,

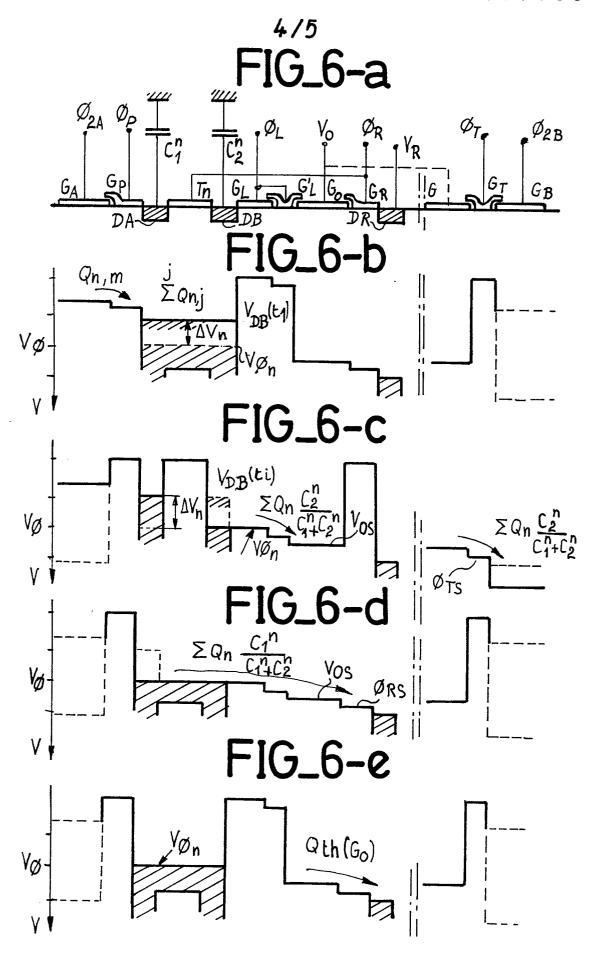

- les figures 6a à 6e sont respectivement une vue en coupe schématique par VI - VI de figure 5 et des schémas représentant l'évolution des potentiels de surface en fonction du temps,

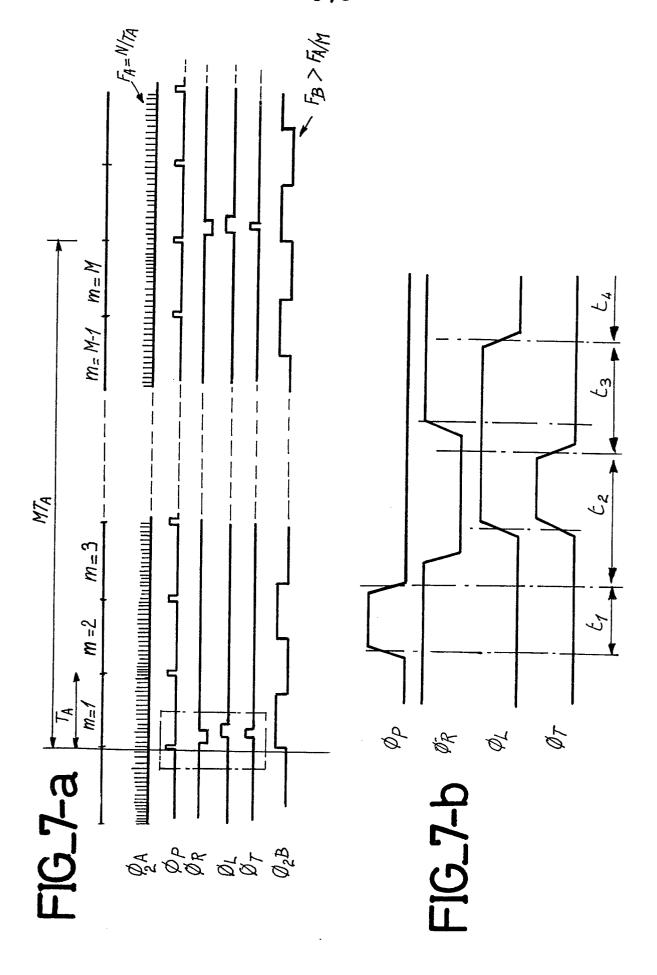

- les figures 7a et 7b sont des diagrammes des différentes tensions de commande appliquées sur l'intégrateur de la figure 5.

Dans les figures, les mêmes éléments portent les mêmes références. Toutefois, pour des raisons de clarté, les cotes et proportions des divers éléments n'ont pas été respectées.

Les figures 3 et 4 sont des schémas de principe de deux modes de réalisation d'un intégrateur analogique récursif conforme à la présente invention. Les intégrateurs décrits ci-après permettent de réaliser l'intégration sur M séquences, la résolution de chaque séquence se faisant sur N points pour une durée  $T_A$  donnant ainsi un signal analogique d'entrée échantillonné  $V_{n,m}$  avec

m = rang de la séquence

n = rang de l'échantillon dans la séquence

1 & n & N.

5

20

30

L'intégrateur de la figure 3 comporte tout d'abord un étage 10 de conversion tension-charge présentant une capacité  $1/_{\hbox{Ce}}$  et

transformant le signal analogique échantillonné  $V_n$ , men une quantité de charge  $Q_n$ , m. L'étage 10 est suivi d'un registre à décalage à transfert de charge A qui reçoit les N quantités de charge correspondant aux N échantillons d'une séquence. Le registre A est constitué par une série de N étages de transfert  $e_1$  à  $e_N$  introduisant chacun un même retard  $\mathbf{T}_A$  qui est donné par la période du potentiel appliqué aux électrodes assurant le transfert de charge.

Le retard  $T_A$  est choisi tel que :

15

25

$NTA = T_A = la durée d'une séquence d'entrée.$

Après chaque durée  $T_A$ , on a en sortie de chaque étage de rang n (avec  $1 \le n \le N$ ) une quantité de charge  $Q_{n, m}$  correspondant à l'échantillon de rang n de la séquence d'entrée considérée. Sur la figure 3, on a représenté uniquement les sorties des N étages et symbolisé par des carrés référencés  $T_A$ , le retard entre les différents étages.

Conformément à la présente invention, la sortie de chaque étage du registre à décalage A est connectée à des moyens de stockage des charges constitués par des capacités  $C^1$ ,  $C^2$ , ...  $C^N$  à potentiel flottant, dont le fonctionnement sera décrit de manière plus détaillée ci-après. Chaque capacité  $C^1$ ,  $C^2$ , ...  $C^N$  réalise pour l'ensemble des M séquences la sommation des charges en sortie de l'étage correspondant du registre A. De ce fait, à la fin des M séquences, c'est-à-dire après une durée MTA correspondant à un cycle d'intégration, chaque capacité  $C^N$  de rang n (avec n variant de l à N) contient une quantité de charge  $Q_{In} = \sum_{m=0}^{\infty} Q_{n,m}$ .

Les capacités de stockage sont connectées à un étage de lecture unique par l'intermédiaire de portes analogiques  $P_1$ ,  $P_2$ , ...  $P_N$  dont la fermeture est commandée par un registre d'adressage RDA qui envoie cycliquement à la fin d'un cycle d'intégration un niveau logique "1" sur chaque sortie, les autres sorties se trouvant à cet instant au niveau logique "0". Cela permet la lecture successive des quantités de charge  $\sum_{m=1}^{\infty} Q_{n,m}$  intégrées dans chaque capacité  $C^1$ ,  $C^2$ , ...  $C^N$  et l'obtention en sortie d'un signal échantillonné  $\sum_{m=1}^{\infty} V_{n,m}$ . Un inconvénient de cet intégrateur réside dans le fait que le

transfert des charges du registre A dans les capacités  $C^1$ ,  $C^2$ , ...  $C^N$  ne peut être réalisé que lorsque l'ensemble des capacités  $C^1$ ,  $C^2$ , ...  $C^N$  a été lu. En conséquence, le temps de lecture de l'ensemble des capacités doit être inférieur à  $T_{A^*}$ .

La figure 4 représente un mode de réalisation préférentiel de la présente invention. Dans ce mode de réalisation, le démultiplexeur d'entrée est identique à celui de l'intégrateur de la figure 3. En conséquence, il ne sera pas redécrit. L'intégrateur de la figure 4 diffère de l'intégrateur de la figure 3 par le fait que le multiplexeur de sortie est aussi constitué par un registre à décalage B à 10 transfert de charge de type CCD. Ce registre à décalage à entrées parallèles et sortie série comporte N étages de transfert introduisant chacun un même retard  $\tau_{

m p}$  qui est donné par la période du potentiel appliqué aux électrodes assurant le transfert de charge. Comme expliqué de manière plus détaillée ci-après, le retard C<sub>B</sub> est le plus souvent différent du retard **T**<sub>A</sub>. Chaque entrée du registre B est connectée à une des capacités C<sup>1</sup>, C<sup>2</sup>, ... C<sup>N</sup> par l'intermédiaire d'une grille de passage non-représentée. La sortie du registre B est connectée à un étage de conversion charge-tension 11 présentant une capacité C5. D'autre part, la charge transférable par un registre 20 CCD étant limitée, pour pouvoir intégrer une quantité importante de charge, les moyens de stockage  $C^1$ ,  $C^2$ , ...  $C^N$  sont constitués chacun par deux capacités  $C_1^1$ ,  $C_1^2$ , ...  $C_1^N$  et  $C_2^1$ ,  $C_2^2$ , ...  $C_2^N$ interconnectées dont les dimensions ont été choisies de manière à n'envoyer qu'une fraction  $\alpha$  des échantillons de charge  $\sum_{n} Q_{n, m}$ 25 comme cela sera expliqué de manière plus détaillée ci-après.

Avec l'intégrateur de la figure 4, après avoir intégré pendant la durée MTA, des échantillons de charge  $Q_{In} = \sum_{m} Q_{n, m}$  sur chaque capacité  $C^1$ ,  $C^2$ , ...  $C^N$ , on transfert simultanément l'ensemble des échantillons  $Q_{IN}$  dans les étages correspondants du registre à décalage B de sortie. Pendant le début d'une nouvelle intégration dans les capacités  $C^1$ ,  $C^2$ , ...  $C^N$ , le registre B de sortie transfert les échantillons de charges  $Q_{IN}$  and  $Q_{IN}$  en série vers l'étage de conversion charge-tension qui donne un signal analogique

de sortie échantillonné  $\sum_{m} V_{n, m}$ .

Dans ce cas le gain du système est donné par l'équation suivante

$$\frac{\sum_{n,m} V_{n,m}}{V_{n,m}} = AM \frac{C_e}{C_S}$$

D'autre part, le temps d'intégration sur les M séquences étant  $MT_A$ , la durée de la séquence de sortie doit être :

5

15

En conséquence, les retards élémentaires  $\tau_B$  du registre de sortie B doivent être :

$$T_B = T_B / N \leq MT_A / N = MT_A$$

.

Il résulte que la fréquence relative de transfert entre les registres d'entrée et de sortie doit satisfaire à l'équation suivante

$$F_B \gtrsim \frac{1}{M}$$

$F_A$

On décrira maintenant avec référence aux figures 5 à 7, un mode de réalisation détaillé d'un intégrateur analogique non-récursif du type de l'intégrateur de la figure 4. Cet intégrateur a été réalisé sous forme intégrée en utilisant la technologie N MOS - CCD sur un substrat en silicium de type P. Il est évident pour l'homme de l'art que cet intégrateur peut être réalisé sur d'autres substrats tels qu'un substrat en silicium de type N, en arséniure de gallium ou similaire. De même, l'intégrateur peut être réalisé sur une zone N prévue dans le substrat P de manière à effectuer le transfert des charges en volume. De préférence, l'intégrateur est entièrement intégré sur une seule puce et même plusieurs intégrateurs identiques ou non peuvent être intégrés sur la même puce. Toutefois, on peut envisager un intégrateur conforme à la présente invention constitué de plusieurs parties connectées entre elles.

Comme représenté sur la figure 5, le démultiplexeur d'entrée est constitué par un registre à décalage A de type CCD fonctionnant en biphasé. De façon connue, chaque étage du registre est constitué par deux couples d'électrodes comprenant chacun une électrode de

transfert et une électrode de stockage. Chaque couple d'électrodes est relié à un potentiel de commande  $\phi_{1A}$  et  $\phi_{2A}$  alternatif et en opposition de phase. D'autre part, l'électrode de stockage du couple d'électrodes commandé par  $\phi_{2A}$  est utilisée comme sortie et elle est référencée  $G_A$  sur la figure 6a. L'électrode  $G_A$  de chaque étage du registre à décalage A est séparée du moyen de stockage des charges par une grille de passage  $G_p$  reliée à un potentiel  $\phi_p$ .

Les moyens de stockage ou sites d'intégration comprennent des diodes  $D_A^{-1}$ ,  $D_A^{-2}$ ,... $D_A^{-N}$  réalisées de manière connue par une diffusion de type N lorsque le substrat est de type P. Chaque diode  $D_A^{-n}$  est reliée à une première capacité  $C_1^{-n}$  réalisée par le substrat, une couche d'isolant, de préférence en oxyde de silicium et une grille, de préférence en aluminium ou en silicium polycristallin. Les premières capacités  $C_1^{-1}$ ,  $C_1^{-2}$ ,  $C_1^{-N}$  sont interconnectées par des transistors MOS  $T_R^{-1}$ ,  $T_R^{-2}$ , ...  $T_R^{-N}$  à des secondes capacités  $C_2^{-1}$ ,  $C_2^{-2}$ , ...  $C_2^{-N}$  réalisées comme les premières capacités. La grille des transistors MOS  $T_R^{-1}$  est connectée à un potentiel  $\phi_R^{-1}$  pour bloquer ou rendre passant lesdits transistors. Les secondes capacités  $C_2^{-1}$ ,  $C_2^{-2}$ , ...  $C_2^{-N}$  sont connectées à des diodes  $D_B^{-1}$ ,  $D_B^{-2}$ ,  $D_B^{-N}$  réalisées par une diffusion de type N.

Les diodes  $D_B^n$  sont reliées aux entrées du multiplexeur de sortie par l'intermédiaire d'un dispositif d'aiguillage. Le dispositif d'aiguillage est constitué pour chaque moyen de stockage ou site d'intégration par deux grilles adjacentes  $G_L$ ,  $G'_L$  commandées par le même potentiel  $\Phi_L$ ,  $G'_L$  se trouvant sur une surépaisseur d'oxyde pour obtenir des potentiels de canal sans charge étagés sous  $G_L$  et  $G'_L$ , par une grille de passage intermédiaire  $G_O$  reliée à un potentiel fixe  $V_O$ , par deux grilles de transfert  $G_R$  et  $G_P$  prévues sur deux cotés de la grille  $G_O$  et séparant la grille  $G_O$  respectivement du multiplexeur  $G_C$ 0 et d'un drain d'évacuation  $G_C$ 1 constitué par une diffusion de type  $G_C$ 2 est reliée à un potentiel  $G_C$ 3 au potentiel  $G_C$ 4 est reliée à un potentiel  $G_C$ 5 au grille  $G_C$ 6 est reliée à un potentiel  $G_C$ 7 la grille  $G_C$ 8 au potentiel  $G_C$ 9.

Le multiplexeur B de sortie est constitué par un registre à décalage à transfert de charge de type CCD biphasé. Ce registre à

une structure identique au registre A.

5

15

20

Il est commandé par des potentiels de commande  $\phi_{1B}$  et  $\phi_{2B}$ en opposition de phase. D'autre part, l'électrode de stockage du couple d'électrodes commandé par  $\phi_{2\mathrm{B}}$  est utilisée comme entrée. Elle est référencée G<sub>B</sub> sur la figure 6a.

On décrira maintenant en se référant plus particulièrement aux figures 6b à 6e et aux figures 7a et 7b, le fonctionnement de l'intégrateur analogique non récursif des figures 5 et 5a.

La figure 7a représente le diagramme fonction du temps des potentiels  $\phi_{2A}$ ,  $\phi_{p}$ ,  $\phi_{R}$ ,  $\phi_{L}$ ,  $\phi_{T}$  et  $\phi_{2B}$  appliqués sur les différentes 10 grilles de l'intégrateur pendant un cycle d'intégration, à savoir pendant une durée MTA. On voit qu'après chaque durée TA, il y a transfert des charges du registre A dans les capacités de stockage. A la fin du temps d'intégration total, à savoir de la durée MTA, il y a transfert dans le registre à décalage B.

La figure 7b représente de manière agrandie le diagramme fonction du temps des potentiels  $\phi_{\rm p},~\phi_{\rm R},~\phi_{\rm L},$  et  $\phi_{\rm T}.$  Ce diagramme correspond à la partie entourée de tirets sur la figure 7a. De ce fait, on se référera plus particulièrement aux figures 6a à 6e et à la figure 7b pour expliquer le fonctionnement de l'intégrateur.

Ainsi, pendant le temps t<sub>1</sub>, lorsque chaque séquence m a été entièrement introduite dans le registre CCD A et que les échantillons de rang n sont sur les électrodes de stockage  $G_A$  au niveau des capacités de stockage de même rang, le potentiel  $\phi_{\rm p}$  passe au niveau haut. Comme représenté sur la figure 6b, la charge Q<sub>n. m</sub>  $_{

m 25}$  sous  $_{

m A}$  est transférée vers le moyen de stockage et se répartit sur les capacités  $C_1^n$  et  $C_2^n$  interconnectées par le transistor  $T_R^n$  en régime triode, car le potentiel  $\phi_{R}$  est à l'état haut.

La somme des charges arrivant successivement après M séquences d'entrée sur les capacités  $C_1^n$  et  $C_2^n$  s'accompagne d'une 30 variation de potentiel  $\Delta$   $V_n$  a partir d'un potentiel initial  $V_{Qn}$  défini ci-après.

En fin d'intégration, on a

$$\Delta V_n = \sum_{m} Q_{n,m} / (C_1^n + C_2^n)$$

(1)

avec  $\Delta V_n = V_{DB}(t_1) - V_{Qn}$ .

Pendant le temps  $t_2$ , le potentiel  $\phi_p$  étant revenu à un niveau bas pour permettre l'entrée d'une nouvelle séquence dans le registre A, le potentiel  $\phi_R$  passe à un niveau bas. Simultanément le transistor  $T_R^n$  se bloque isolant la capacité  $C_2^n$  de la capacité  $C_1^n$  tandis que la grille  $G_R$  passe à un potentiel bas isolant le canal sous la grille  $G_Q$  du drain  $D_R$ .

Ensuite, simultanément ou non, les potentiels  $\phi_L$  et  $\phi_T$  passent au niveau haut. La grille  $G_L$  définit un potentiel de canal sans charge correspondant au potentiel de référence  $V_{On}$  et la grille  $G_T$  permet le passage des charges de la capacité  $C_2^{\ n}$  vers l'étage  $G_B$  correspondant du registre de sortie B. Pour cela, les potentiels au niveau haut sous  $G_L$ ,  $G_O$ ,  $G_T$  et  $G_B$  doivent être tels que

$v_{Qn} = \phi_{LS} \langle v_{OS} \langle \phi_{TS} \langle \phi_{2BS} \rangle$

$\rm V_{OS},\,\phi_L,\,\phi_{TS},\,\phi_{BS}$  étant les potentiels de canal sans charge sous les grilles  $\rm G_L,\,G_O,G_T$  et  $\rm G_B$  .

Les charges stockées sur l'électrode de la capacité  $C_2^{\ n}$  sont evacuées dans le canal CCD du registre B comme représenté sur la figure 6c.

Les charges évacuées vers le registre B répondent à l'équation

20  $Q_{Ln} = [V_{DB}(t_1) - V_{Qn}] C_2^n$  (2) avec  $V_{DB}(t_1) = V_{DA}(t_1) = V_D$ .

Pendant le temps  $t_3$ , le potentiel  $\phi_T$  appliqué sur la grille  $G_T$  passe à l'état bas isolant le registre B de sortie de la grille de passage  $G_O$ .

Ensuite le potentiel  $\phi_R$  passe à l'état haut permettant simultanément d'interconnecter les deux capacités  $C_1^n$  et  $C_2^n$  et de ramener le canal sous la grille  $G_R$  à un niveau haut pour interconnecter les capacités avec le drain d'évacuation des charges  $D_R$ .

En effet, les potentiels au niveau haut sous  $\mathbf{G}_{R}$ ,  $\mathbf{G}_{O}$  et  $\mathbf{G}_{L}$  étant choisis tels que

$V_{Qh} = \phi_{LS} \langle V_{OS} \langle \phi_{RS} \rangle$ une quantité de charge présente sur la capacité  $C_{L}^{n}$  est évacuée vers le drain  $D_{R}$  comme représenté sur la figure 6d.

Cette quantité de charge correspond à

$$Q_{En} = [V_{DB}(t_1) - V_{Qn}] C_1^n$$

(3)

Lorsque cette charge est évacuée, le potentiel des capacités  $C_1^n$  et  $C_2^n$  est défini par le potentiel du canal sans charge  $V_{Qn}$  sous la grille G<sub>1</sub> tel que

5

15

$V_{Qn} = Q_{L \text{ haut}} - V_{Tn}$ Ce potentiel de référence  $V_{Qn}$  est fonction du seuil  $V_{Tn}$  du MOS induit de grille  $G_{Ln}$ .

En fait, une dispersion des seuils  ${\bf V}_{{\bf T}n}$  entre étages n ne modifie pas le rapport de charge  $Q_{Ln}$  /  $\frac{\sum}{m}$   $Q_{n, m}$ .

En effet, pour un même étage,  $V_{Qn}$  est le même aux temps  $t_2$ 10 et  $t_3$ , car il est défini par le même MOS induit de grille  $G_{\rm I}$  .

En partant des équations (1), (2) et (3), on a :

$$\sum_{m}^{\infty} Q_{n, m} = (V_D - V_{Qn}) (C_1^n + C_2^n)$$

$$Q_{Ln} = (V_D - V_{Qn}) C_2^n$$

$$Q_{En} = (V_D - V_{Qn}) C_1^n$$

La charge évacuée vers le registre de sortie est donc

$$Q_{Ln} = A \sum_{m=0}^{\infty} Q_{n, m}$$

avec

$$A = \frac{C_2^n}{C_1^n + C_2^n}$$

La charge éliminée par le drain  $\mathbf{D}_{\mathbf{R}}$  est donc :

$$Q_{En} = (1 - A) \qquad Q_{n,m}$$

$Q_{En} = (1 - A)$   $_{m}$   $Q_{n}$ ,  $_{m}$  Pendant le temps  $t_{4}$ , le potentiel  $\phi_{L}$  passe à l'état bas séparant les capacités  $C_{1}^{n}$  et  $C_{2}^{n}$  du système d'aiguillage. Comme  $^{25}$  représenté sur la figure 6e, le potentiel des capacités  $\mathrm{C_1}^{\mathrm{n}}$  et  $\mathrm{C_2}^{\mathrm{n}}$ est à  $V_{Qn}$ . Le système est prêt à réaliser l'intégration suivante.

D'autre part, les charges thermiques générées sous la grille de passage  $G_O$  sont évacuées vers le drain  $D_R$  pendant tout le temps d'intégration des charges sur  $C_1^n$  et  $C_2^n$  puisque  $\phi_R$  reste au niveau 30 haut.

Avec l'intégrateur décrit ci-dessus, le temps de fractionnement et de transfert des charges vers le registre de sortie peut être relativement long vis à vis de la période d'échantillonnage d'entrée. Il peut durer le temps d'une séquence d'entrée.

5

De même, comme déjà mentionné avec référence à la figure 4, la fréquence d'échantillonnage de sortie peut être M fois plus faible que celle d'entrée avec M = nombre de séquences intégrées.

D'autre part, l'intégrateur peut avoir un temps d'intégration élevé, car la génération thermique sur les sites d'intégration est faible et due uniquement au courant de fuite des diodes  $D_A$  et  $D_{R^{\bullet}}$

Il est aussi possible de monter plusieurs intégrateurs du type ci-dessus en parallèle avec un multiplexage sur les entrées et les sorties. Cela permet de multiplier par p (p > 2), la fréquence maximale de fonctionnement tout en multipliant par p, le nombre de points de résolution de chaque séquence.

Il est évident pour l'homme de métier qu'un certain nombre de modifications peut être apporté aux intégrateurs décrits ci-dessus sans sortie du cadre de la présente invention. Par exemple, les registres CCD peuvent être à quatre phases de commande et non biphasés.

### REVENDICATIONS

1. Intégrateur analogique non-récursif réalisant l'intégration d'un signal analogique échantilloné  $V_{n,\ m}$  sur M séquences, caractérisé en ce qu'il comporte un démultiplexeur d'entrée (A) série parallèle pour envoyer successivement sur N capacités (C<sup>1</sup>, C<sup>2</sup>, ... C<sup>N</sup>) dont une électrode est à un potentiel flottant par rapport à un potentiel de référence, les capacités étant reliées en parallèle au démultiplexeur d'entrée, M fois le signal analogique échantillonné, chaque capacité de stockage réalisant pour les M séquences la sommation sous forme de charge ( $\sum_{m=1}^{\infty} Q_{n,\ m}$ ) de l'échantillon de rang correspondant du signal analogique  $V_{n,\ m}$  et en ce qu'il comporte un multiplexeur (B) parallèle-série de sortie relié aux N moyens de stockage pour délivrer en sortie, à la fin des M séquences, un signal analogique  $\sum_{m=1,M} V_{n,\ m}$ .

2. Intégrateur selon la revendication 1, caractérisé en ce que

- 2. Intégrateur selon la revendication 1, caractérisé en ce que le démultiplexeur d'entrée (A) est constitué par un registre à décalage à transfert de charge à entrée série et sorties parallèles à N étages dont chaque étage est connecté à un moyen de stockage  $(C^1, C^2, ... C^N)$  par l'intermédiaire d'un commutateur  $(\phi_p)$  qui est fermé après chaque séquence.

- 3. Intégrateur selon l'une quelconque des revendications 1 et 2, caractérisé en ce que le multiplexeur de sortie (B) est constitué par un registre à décalage à transfert de charge à entrées parallèles et sortie série comportant N étages reliés chacun à un des moyens de stockage ( $C^1$ ,  $C^2$ ,... $C^N$ ) par l'intermédiaire d'un commutateur ( $\phi_T$ ) fermé périodiquement après chaque période de M séquences.

- 4. Intégrateur selon l'une quelconque des revendications 1 et 2, caractérisé en ce que le multiplexeur de sortie est constitué par des portes analogiques (P<sub>1</sub>, P<sub>2</sub>, ...P<sub>N</sub>) connectées respectivement entre chaque moyen de stockage (C<sup>1</sup>, C<sup>2</sup>, ... C<sup>N</sup>) et l'étage de lecture, les portes étant commandées successivement par une impulsion envoyée par un registre d'adressage (RDA).

5. Intégrateur selon l'une quelconque des revendications 2 à 3, caractérisé en ce que les fréquences de transfert des registres à décalage (A) et (B) répondent à l'équation suivante

$$F_B \nearrow \frac{1}{M} F_A$$

5 dans laquelle:

20

25

30

F<sub>B</sub> est la fréquence de transfert du registre à décalage (B) de sortie:

F<sub>A</sub> est la fréquence de transfert du registre à décalage (A) d'entrée;

10 M est le nombre de séquence.

- 6. Intégrateur selon l'une quelconque des revendications 1 à 5, caractérisé en ce que les capacités  $(C_1^1, C_2^2, ... C_N^N)$  sont constituées de deux capacités  $(C_1^1, C_1^2, ... C_1^N)$  et  $C_2^1, C_2^2, ... C_2^N)$  interconnectées par un moyen de commutation  $(T_R^N)$ .

- 7. Intégrateur selon la revendication 6, caractérisé en ce qu'il comporte de plus entre les capacités de stockage et le multiplexeur de sortie, un dispositif d'aiguillage (G<sub>L</sub>, G<sub>O</sub>, G<sub>T</sub> et G<sub>R</sub>) pour connecter les capacités soit vers un drain d'évacuation (D<sub>R</sub>) soit vers le multiplexeur (B) de sortie.

- 8. Intégrateur selon la revendication 7, caractérisé en ce que le dispositif d'aiguillage est constitué par une grille de passage  $(G_O)$  portée à un potentiel fixe, prévue entre chaque moyen de stockage  $(C^1, C^2, ..., C^N)$  et l'étage d'entrée correspondant du multiplexeur de sortie (B), la grille de passage étant séparée des moyens de stockage, des drains d'évacuation et du multiplexeur de sortie par des grilles  $(G_2, G_R, \text{ et } G_T)$  portées à des potentiels variables.

- 9. Intégrateur selon la revendication 8, caractérisé en ce que les niveaux hauts des potentiels appliqués sur  $(G_L, G_R, G_O \text{ et } G_T)$  ont les relations suivantes :

$$v_{\phi_n} = \phi_{LS} \angle v_{OS} \angle \phi_{TS} \angle \phi_{BS}$$

et  $v_{\phi_n} = \phi_{LS} \angle v_{OS} \angle \phi_{RS}$

dans lequel

$\mathbf{V}_{Qn} = \mathbf{\Phi}_{LS}$  correspond au potentiel haut de canal dans charge sous  $\mathbf{G}_{L}$

$v_{\phi\!S}$  correspond au potentiel de canal sans charge sous  ${\bf G}_O$   $\phi_{TS}$  correspond au potentiel haut de canal sans charge sous  ${\bf G}_T$   $\phi_{RS}$  correspond au potentiel haut de canal sans charge sous  ${\bf G}_R$   $\phi_{BS}$  correspond au potentiel haut de canal sans charge sous  ${\bf G}_R$  du multiplexeur B.

- 10. Intégrateur selon la revendication 9, caractérisé en ce que le potentiel de référence des capacités de stockage est donné par le potentiel haut de canal sans charge sous la grille  $G_{\rm I}$ .

- 11. Intégrateur analogique non récursif constitué par p inté-10 grateurs selon l'une quelconque des revendications 1 à 10 avec p > 1 dont les entrées et les sorties sont multiplexées.

5

FIG\_2

# RAPPORT DE RECHERCHE EUROPEENNE

EP 85 40 0398

| · · · · · · · · · · · · · · · · · · · | DOCUMENTS CONSID                                                                                                                                                                                     | CLASSEMENT                                                                                | DELA                                           |                                                |                                                   |      |

|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------------------------------------------------|------------------------------------------------|---------------------------------------------------|------|

| atégorie                              | Citation du document avec indication, en cas de besoin,<br>des parties pertinentes                                                                                                                   |                                                                                           |                                                | Revendication concernée                        | DEMANDE (Int. Cl.4)                               |      |

| Y                                     | IEEE JOURNAL OF<br>CIRCUITS, vol. 3<br>février 1978, pa<br>New York, US; D<br>"Signal process:<br>charge-coupled of<br>* Figures 1,<br>colonne de gau<br>colonne de droit<br>49, colonne de<br>2-3 * | SC-13, no. 1 ages 34-51, F. BARBE et ing with devices", 2,28; paguche, aliné te, alinéa 4 | ,<br>IEEE,<br>al.:<br>e 35,<br>a 3 -<br>; page | 1,2                                            | G 06 G                                            | 7/18 |

| A                                     | IDEM                                                                                                                                                                                                 |                                                                                           |                                                | 3,5                                            |                                                   | 3    |

| Y                                     | IEEE TRANSACTIONS ON ELECTRON DEVICES, vol. ED-26, no. 4, avril 1979, pages 596-603, IEEE, New York, US; D.A. GANDOLFO et al.: "Analog-binary CCD correlator: A VLSI signal                          |                                                                                           |                                                | 1,2                                            | DOMAINES TECHNIQUES<br>RECHERCHES (Int. CI.4)     |      |

|                                       | processor"  * Figures 1 colonne de gauch 601, colonne de                                                                                                                                             | - page                                                                                    |                                                | G 06 G<br>G 06 G                               |                                                   |      |

| A                                     | IDEM                                                                                                                                                                                                 |                                                                                           | 4,6-8                                          |                                                |                                                   |      |

|                                       |                                                                                                                                                                                                      |                                                                                           |                                                |                                                |                                                   |      |

| l_e p                                 | resent rapport de recherche a été ét                                                                                                                                                                 |                                                                                           |                                                |                                                | , , , , , , , , , , , , , , , , , , ,             |      |

|                                       | Lieu de la recherche<br>LA HAYE                                                                                                                                                                      | Date d'achèvement d<br>13-06-                                                             | le la recherche<br>1985                        | LEDRU:                                         | Examinateur<br>P.                                 |      |

| Y: par<br>aut<br>A: arri              | CATEGORIE DES DOCUMENT<br>ticulièrement pertinent à lui seu<br>ticulièrement pertinent en comb<br>re document de la même catégo<br>ère-plan technologique<br>ulgation non-écrite                     | I<br>I<br>Dinaison avec un D                                                              | : document d                                   | e brevet antérie<br>ôt ou après cet<br>demande | e de l'invention<br>eur, mais publié à<br>le date | la   |

# RAPPORT DE RECHERCHE EUROPEENNE

Numero de la demande

EP 85 40 0398

| DOCUMENTS CONSIDERES COMME PERTINENTS |                                                                                                                                                                                                           |                                                                                                |                                                     |                              |                                                          | Page 2                                        |  |

|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-----------------------------------------------------|------------------------------|----------------------------------------------------------|-----------------------------------------------|--|

| Catégorie                             | Citation du document avi<br>des part                                                                                                                                                                      | ec indication, en cas de<br>les pertinentes                                                    | e besoin,                                           |                              | vendication<br>oncernee                                  | CLASSEMENT DE LA<br>DEMANDE (Int. CI.4)       |  |

| Y                                     | IEEE JOURNAL OF CIRCUITS, vol. Saoût 1979, pages New York, US; C. al.: "A nonrecur integrator using structure"  * Figures 1,2; de gauche, avant colonne de droit                                          | SC-14, no.<br>5 742-746,<br>P. TRAYNAR<br>sive signa<br>g a paralle<br>page 742,<br>t-dernière | 4, IEEE, et l cl CCD colonne ligne -                | -                            | 1,2                                                      |                                               |  |

| A                                     | IDEM                                                                                                                                                                                                      |                                                                                                |                                                     | 4                            | 1                                                        |                                               |  |

| Y                                     | DE-A-2 838 279 * Figure 3; ralinéa - page 1                                                                                                                                                               | dernier<br>alinéa                                                                              | -                                                   | L                            |                                                          |                                               |  |

|                                       |                                                                                                                                                                                                           |                                                                                                |                                                     |                              |                                                          | DOMAINES TECHNIQUES<br>RECHERCHES (Int. Ci.4) |  |

|                                       |                                                                                                                                                                                                           |                                                                                                |                                                     |                              |                                                          |                                               |  |

| Lei                                   | présent rapport de recherche a été é                                                                                                                                                                      | tabli pour toutes les rev                                                                      | vendications                                        |                              |                                                          |                                               |  |

| Lieude la recherche Date              |                                                                                                                                                                                                           | Date d'achèveme<br>13-06                                                                       | e d'achèvement de la recherche<br>13-06-1985        |                              | LEDRUT                                                   | Examinateur<br>P.                             |  |

| Y : par<br>aut<br>A : arr<br>O : div  | CATEGORIE DES DOCUMENT<br>ticulièrement pertinent à lui seu-<br>ticulièrement pertinent en comb<br>re document de la même catégo<br>ière-plan technologique<br>ulgation non-écrite<br>cument intercalaire | ıl<br>Dinaison avec un                                                                         | date de dép<br>D : cité dans la<br>L : cité pour d' | de b<br>ôt der<br>der<br>aut | revet antérieu<br>ou après cette<br>nande<br>res raisons | ır, mais publié à la                          |  |