Numéro de publication:

0 161 176

A1

(12)

## DEMANDE DE BREVET EUROPEEN

(21) Numéro de dépôt: 85400735.8

(51) Int. Ci.4: G 09 G 1/16

22) Date de dépôt: 12.04.85

30 Priorité: 17.04.84 FR 8406053

Date de publication de la demande: 13.11.85 Bulletin 85/46

84 Etats contractants désignés: BE DE GB (7) Demandeur: THOMSON VIDEO EQUIPEMENT 94, rue du Fossé Blanc F-92230 Gennevilliers(FR)

172) Inventeur: Pham Van Cang, Luc THOMSON-CSF SCPI 173, bld Haussmann F-75379 Paris Cedex 08(FR)

74) Mandataire: Lincot, Georges THOMSON-CSF SCPI 173, Bid Haussmann F-75379 Paris Cedex 08(FR)

Dispositif pour l'obtention de tracés continus sur l'écran d'une console de visualisation commandée par un processeur graphique.

Et dispositif selon l'invention comprend une mémoire graphique (4) pour mémoriser sous une forme binaire la matrice de points ou pixels représentant l'image visualisés sur l'écran et une mémoire d'attribut (12) contenant les attributs de chacun des points de l'image. Un circuit d'interpolation (14) contient une table de calcul des attributs des points intermédiaires entre points consécutifs de la matrice de point. La table du circuit d'interpolation est adressée par la valeur pré-existante PA du pixel à modifier trouvée dans la mémoire d'attribut pour la valeur nouvelle PN de l'attribut des pixels à modifier pour les faire figurer sur le tracé et par une valeur d'interpolation F égale à la partie fractionnaire de la position du point intermédiaire à modifier, chaque emplacement de la table contient une valeur d'attribut PM vérifiant la relation

PM = F.PA + (1-F).PN

La valeur PM obtenue est transférée dans la mémoire d'attribut (12) pour mettre à jour le contenu de l'emplacement correspondant à l'adresse du point du pixel modifié.

Application: processeurs graphiques.

1

Dispositif pour l'obtention de tracés continus sur l'écran d'une console de visualisation commandée par un processeur graphique

La présente invention concerne un dispositif pour l'obtention de tracés continus sur l'écran d'une console de visualisation commandée par un processeur graphique.

Les consoles de visualisation adaptées pour le tracé d'images graphique forment des images à partir d'une matrice ordonnée de points ou de pixels régulièrement répartis à la surface de l'écran et dont la pigmentation est déterminée en fonction du dessin ou du graphique qui est à exécuter. Cette matrice est généralement orthogonale et est constituée par M x N pixels ou points placés sur la surface de l'écran de la console aux intersections de M rangées et de N lignes. Le produit M x N représente le nombre total de pixels ou de points visibles sur l'écran de la console, de lui dépendent les performances du processeur. Dans les réalisations connues, les formats utilisés vont des matrices de points constitués de 512 par 512 à 1024 par 1024 points ou pixels. Ces images sont représentées sur les consoles de visualisation ou sur des moniteurs de télévision noir et blanc ou couleurs à l'aide d'un système d'analyse "colonne-ligne".

Le mode de balayage de télévision par ligne et trame est apprécié dans ces dispositifs pour présenter de nombreux avantages. Cependant la structure échantillonnée de la mémoire graphique qui est interposée entre la console de visualisation et le processeur provoque des défauts caractéristiques appelés globalement "défauts d'aliasing" dans la littérature anglo-saxonne qui se présentent soit sous la forme d'un crénelage visible sur les obliques et les courbes des tracés obtenus sur les écrans lorsque l'image est fixe, soit par la disparition ou l'apparition brutale de détails en fonction d'un faible déplacement de l'image. Ces défauts sont principalement dus à l'échantillonnage du signal aux points discrets de la mémoire d'image interposée entre l'écran de la console et le processeur.

Dans les équipements graphiques de hautes performances ces défauts sont corrigés par diverses techniques consistant, par exemple, à

- - - -

augmenter la définition de l'image visualisée ou à augmenter la capacité de la mémoire graphique en groupant corrélativement chaque pixel ou point analysé avec ses points voisins, ou à compenser les arrondis de position du tracé par une variation de teinte du pixel entourant le tracé ou encore, en effectuant des traitements lors de la lecture de la mémoire graphique consistant à opérer dés filtrages et des calculs d'interpolation sur les signaux lus dans la mémoire graphique. En fait, les procédés qui consistent à augmenter les définitions de l'image visualisée tendent à être remplacés par des procédés de traitement par filtrage et interpolation qui 10 apparaissent nettement plus efficaces et moins coûteux. Ces méthodes de traitement ont toutefois pour inconvénient d'occuper beaucoup de temps de cycles de calcul des processeurs graphiques ce qui rend ces méthodes de tracé relativement lentes. Pour augmenter les vitesses de tracé, des logiques câblées sont utilisées pour remplacer les logiciels des processeurs 15 graphiques mais ces logiques ont pour inconvénient d'être onéreuses et de nécessiter encore, pour obtenir des corrections satisfaisantes, des traitements intermédiaires en utilisant par exemple des mémoires caches, ces traitements étant exécutés à grande vitesse et à haute définition par échange de données entre la mémoire cache et le processeur avant que les résultats soient inscrits dans la mémoire graphique.

Le but de l'invention est de pallier les inconvénients précités.

A cet effet, l'invention a pour objet, un dispositif pour l'obtention de tracés continus sur l'écran d'une console de visualisation commandée par un processeur graphique, l'image étant constituée par une matrice ordonnée de points d'images ou pixels formés par M rangées de N points ou pixels balayés suivant le principe de balayage des images de télévision, le dispositif comprenant une mémoire graphique pour mémoriser sous une forme binaire l'image de la matrice des points visualisés sur l'écran et une mémoire d'attribut pour contenir les attributs de chacun des points de l'image, caractérisé en ce qu'il comprend également une mémoire d'interpolation dans laquelle se trouve mémorisée une table de calcul des attributs des points intermédiaires entre points consécutifs de la matrice de points, la table du circuit d'interpolation étant adressée sur une première entrée par la valeur pré-existante PA du pixel à modifier trouvée dans la mémoire d'attribut, sur une deuxième entrée par la valeur

nouvelle PN de l'attribut des pixels à modifier pour les faire figurer sur le tracé et sur une troisième entrée par une valeur d'interpolation F, calculée par le processeur, égale à la partie fractionnaire de la position du point intermédiaire à modifier, chaque emplacement de la table contenant une valeur d'attribut PM vérifiant la relation

$$PM = F . PA + (1-F) . PN$$

10

la valeur PM obtenue étant transférée dans la mémoire d'attribut pour mettre à jour le contenu de l'emplacement correspondant à l'adresse du pixel modifié.

D'autres caractéristiques et avantages de l'invention apparaîtront au cours de la description faite au regard des dessins annexés donnés uniquement à titre d'exemple et dans lesquels :

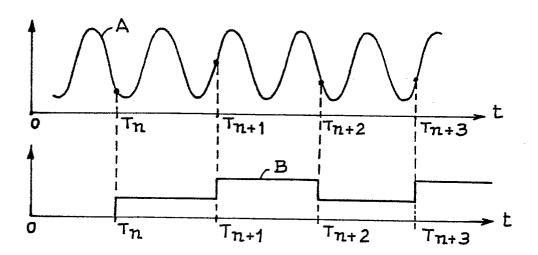

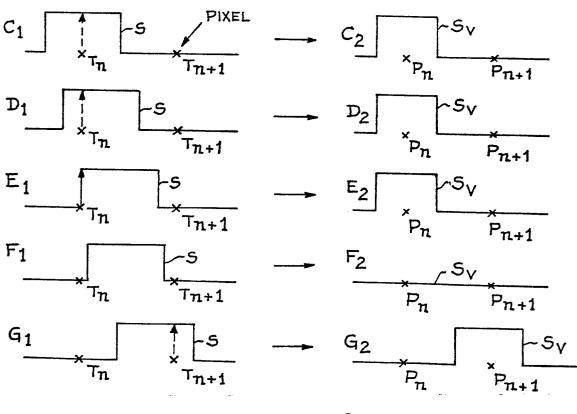

- les figures 1 à 3 sont les représentations des défauts de reconstitution de tracés sur des écrans de consoles graphiques engendrés par l'échantillonnage de points ou pixels de la matrice d'image enregistrés dans la mémoire graphique;

- les figures 4 à 5 illustrent des procédés connus mis en œuvre dans certains processeurs graphiques pour obtenir des tracés ne présentant pas de discontinuité;

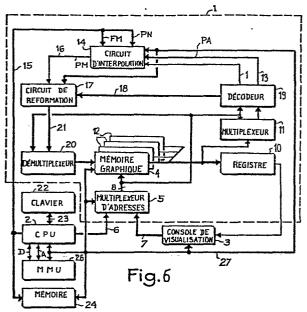

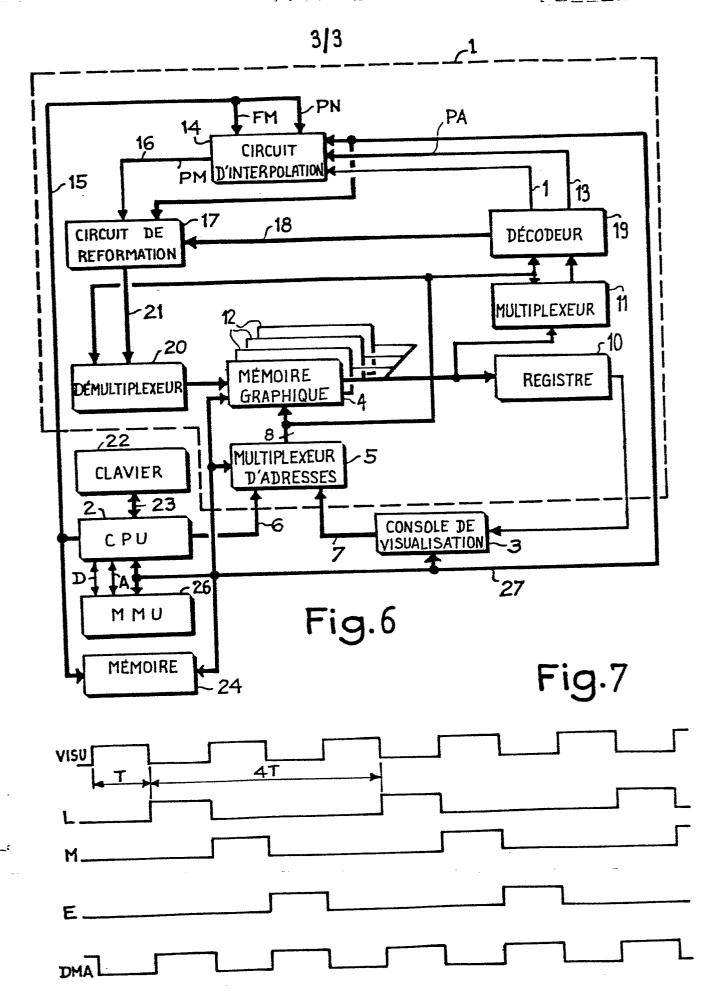

- la figure 6 est une représentation du dispositif selon l'invention pour obtenir des tracés sans discontinuités;

- la figure 7 est une représentation des diagrammes des temps du cycle de rafraichissement de l'écran d'une console de visualisation balayé suivant le principe de balayage des écrans de télévision, du cycle de

lecture, de modification ou d'écriture de la mémoire graphique ainsi que du cycle d'accès direct DMA à la mémoire graphique;

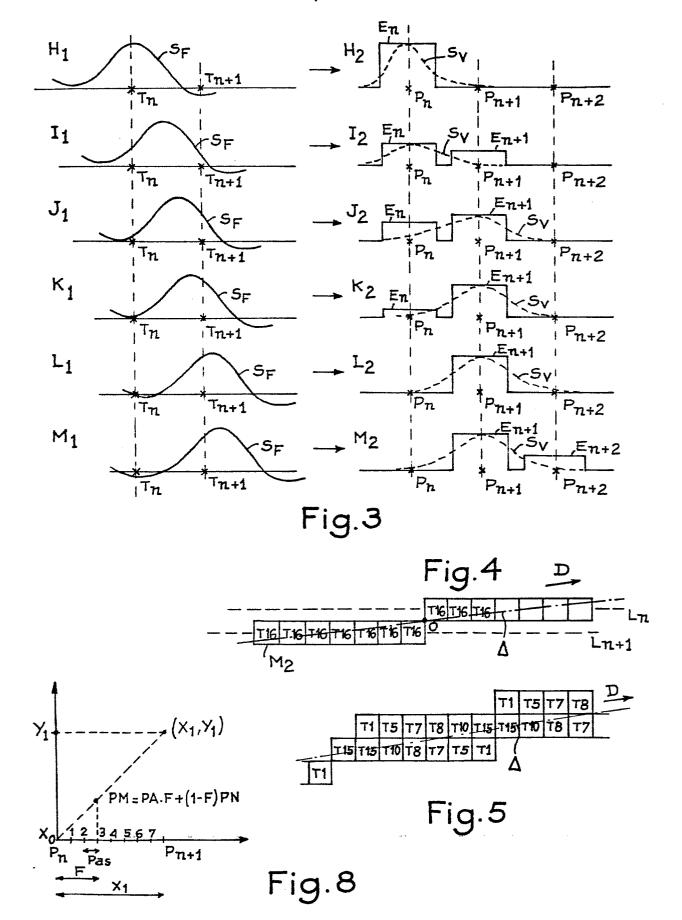

- la figure 8 illustre la méthode d'interpolation linéaire mise en oeuvre par l'invention pour corriger les discontinuités de tracés.

La théorie de l'information montre que l'échantillonnage d'un signal S(t) dépendant du temps, à une cadence C<sub>i</sub> donne des défauts appelés globalement "défauts d'aliasing" si le spectre en fréquence du signal S(t) dépasse la moitié de la fréquence d'échantillonnage du signal d'échantillonnage. Ce défaut traduit le recouvrement entre la moitié supérieure du spectre du signal S(t) et la moitié inférieure lorsque ce

dernier est replié autour de la fréquence  $\frac{C_i}{2}$  moitié de la fréquence  $C_i$  de cadencement du signal d'échantillonnage.

Dans un espace à deux dimensions, les coordonnées X et Y échantillonnées et discrètes de la position de chaque point ou pixel d'une mémoire graphique organisée à la façon d'une matrice orthogonale ayant des colonnes et des lignes obéissent aux mêmes critères, à la différence toutefois que pour le signal graphique la variable se trouve située dans le domaine spatial et non pas dans le domaine temporel. Si le spectre spatial du signal graphique dépasse la demi fréquence spatiale d'échantillonnage les mêmes défauts "d'aliasing" se retrouvent pour les signaux graphiques de la même façon que pour les signaux dépendant du temps.

A titre d'exemple, la figure 1 illustre les défauts de reconstitution d'un signal sinusoïdal A échantillonné à des instants  $T_n$  à  $T_{n+3}$  régulièrement espacés les uns des autres et le signal B reconstitué qui en résulte et qui apparait crénelé sous la forme de marches d'escalier, chaque palier ayant une amplitude constante entre deux instants d'échantillonnage.

La figure 2 illustre les "défauts d'aliasing" spatiaux engendrés par des signaux d'échantillonnage à cadence fixe d'un signal rectangulaire S représentant la position d'un point sur un tracé qui est représenté à 20 l'entrée d'une console graphique dont la mémoire est organisée suivant la forme d'une matrice de points. Suivant la position du signal S par rapport aux instants d'échantillonnage  $T_n$  et  $T_{n+1}$  on peut constater sur la figure 2 que ce signal est ou n'est pas mémorisé à l'intérieur de la mémoire. Dans le cas par exemple du signal S qui est représenté à la ligne F, entre les instants d'échantillonnage  $T_n$  et  $T_{n+1}$  l'image de ce signal (ligne  $F_2$ ) n'est pas enregistrée dans la mémoire graphique puisque le point qu'elle représente est intermédiaire entre la position  $P_n$  et  $P_{n+1}$  de la mémoire graphique correspondant aux instants d'échantillonnage  $T_n$  à  $T_{n+1}$  et que par conséquent ce signal ne peut être visualisé sur la console de visualisation.

Une manière de remédier à ce défaut est représentée à la figure 3 et consiste à filtrer chaque signal d'entrée pour le transformer en un signal  $S_F$  sur les graphes  $H_1$  à  $M_1$  avant de l'échantillonner pour l'inscrire dans la mémoire graphique. Les constantes de filtrage sont définies pour que, quelque soit la position du signal filtré par rapport aux instants

30

d'échantillonnage  $T_n$  et  $T_{n+1}$ , il y ait toujours un échantillon de signal qui puisse être mémorisé à l'intérieur de la mémoire graphique, on profite ensuite des constantes de réponse de l'écran qui opère un filtrage naturel, signal  $S_V$  sur les graphes  $H_2$  à  $M_2$ , sur la grandeur des échantillons restitués par la mémoire graphique.

S'il est relativement simple de filtrer un signal dans le domaine temporel, le filtrage spatial qui vient d'être décrit est cependant plus complexe à réaliser et nécessite en particulier de multiples accès à la mémoire graphique dans la direction des lignes et des colonnes lorsque le filtrage mis en œuvre est bidimensionnel. Les figures 4 et 5 illustrent un procédé moins compliqué et donnant de bons résultats qui est quelque fois employé pour obtenir des traces sans discontinuité sur un écran d'une console graphique de visualisation. La figure 4 montre une trace oblique dirigée selon la direction D obtenue en accolant deux mots  $M_1$  et  $M_2$  de 15 sept pixels chacun, de même teinte T<sub>16</sub>, disposés respectivement sur les lignes  $L_n$  et  $L_{n+1}$  . La trace représentée montre une discontinuité au point 0 au passage de la ligne supérieure  $L_n$  à la ligne directement inférieure L<sub>n+1</sub>. Pour remédier à cette difficulté les dispositifs connus de correction "d'anti-aliasing" opèrent suivant le principe représenté à la figure 5 20 qui montre la même trace que celle figurée à la figure 4 qui est obtenue, à la différence de ce qui est représenté à la figure 4, en corrigeant la teinte des pixels autour de la droite  $\Delta$  de direction D. La teinte des pixels entourant la droite  $\Delta$  de direction D est pondérée par une fonction d'interpolation qui a pour argument l'erreur de position de chaque pixel par rapport à la droite A de direction D. La perte de modulation est négligeable dans ce cas et est largement compensée par des contours plus nets. Ce procédé présente toutefois l'inconvénient de nécessiter l'emploi d'un logiciel ce qui pénalise la vitesse avec laquelle les tracés peuvent être effectués. Le procédé selon l'invention permet de remédier à ces difficultés et consiste à utiliser un dispositif câblé pour exécuter les fonctions d'interpolation linéaire nécessaires en cours de tracé pour supprimer les discontinuités, le principe de ces interpolations consistant à modifier chaque valeur pré-existante d'un pixel situé sur ou à proximité du tracé en fonction de la nouvelle valeur des pixels du tracé et de la position du pixel par rapport à la direction du tracé.

Le dispositif pour la mise en oeuvre du procédé selon l'invention est représenté à l'intérieur d'une ligne en pointillés 1 sur la figure 6. Le dispositif 1 est couplé entre un processeur 2 désigné par l'abréviation CPU qui est la contraction du terme anglo-saxon Central Processing Unit et une console de visualisation 3.

Le dispositif 1 comprend une mémoire graphique 4 qui contient une représentation binaire matricielle de tous les points caractéristiques de l'image graphique qui est visualisée sur la console de visualisation 3, chaque bit d'information contenu dans la mémoire graphique 4 ayant, par exemple, la valeur 0 lorsqu'il correspond au fond uniforme du graphique et la valeur binaire I lorsqu'il correspond à un point ou pixel du graphique qui se détache sur le fond de celui-ci. La mémoire graphique est organisée en mots de n bits représentant l'état de n pixels, chaque mot étant adressé soit par le processeur 2 ou par la console de visualisation 3 par l'intermédiaire d'un circuit multiplexeur d'adresse 5 à deux entrées de multiplexage, une première entrée de multiplexage étant reliée par la ligne d'adresse 6 à la sortie d'adresse du processeur 2 et une deuxième entrée d'adresse étant reliée par la ligne d'adresse 7 à la sortie d'adresse de la console de visualisation 3. La sortie du multiplexeur d'adresse 5 est reliée aux entrées d'adressage de la mémoire graphique 4 au moyen de la ligne d'adresse 8. Les mots lues dans la mémoire graphique 4 aux emplacements de mémoire désignés par les mots d'adresse appliqués sur la ligne d'adresse 8 sont appliquées respectivement aux entrées d'un registre parallèle-série 10 et aux entrées d'un circuit multiplexeur 11. Le dispositif I comprend également une mémoire d'attribut 12 formée éventuellement par p plans de mémoires supplémentaires de la mémoire graphique 4 qui contient les attributs codés sur p bits respectifs à chacun des n pixels représentés dans chaque mot de n bits contenus dans la mémoire graphique 4, cette mémoire d'attribut 12 étant adressée simultanément à la mémoire graphique 4 par la ligne d'adresse 8. Les mots lus dans la mémoire graphique et dans la mémoire d'attribut 12 sont appliqués aux circuits non représentés de la console de visualisation 3, par l'intermédiaire du registre 10, pour permettre la visualisation des pixels qu'ils représentent par la console de visualisation. Les mots d'attribut PA de chaque pixel, adressés par chacun des mots d'adresse appliqués sur la ligne

15

20

25

30

35

d'adressage 8, sont appliqués par une ligne de données 13, sur une première entrée d'un circuit d'interpolation 14 au travers du multiplexeur 11 et d'un décodeur 19 reliés en série. Le circuit d'interpolation 14 est relié par des deuxième et troisième entrées aux sorties de données du 5 processeur 2 au moyen d'une ligne de données 15. Les données de modification notées FM et PN sont appliquées par la ligne de donnée 15 sur les deuxième et troisième entrées du circuit d'interpolation 14, pour modifier les valeurs des attributs PA appliqués sur la première entrée du circuit d'interpolation 14 par la ligne de données 13. La sortie du circuit 10 d'interpolation 14 est reliée par une ligne de donnée 16 à une entrée de donnée d'un circuit de reformation 17 pour enregistrer chaque attribut PM modifié par le circuit d'interpolation 14 à l'emplacement qu'il occupe dans la mémoire d'attribut 12. Le circuit de reformation 17 est également relié par une deuxième entrée, au moyen de la ligne 18, à la sortie du décodeur 15 19 adressé par la ligne d'adresse 8 et relié par son entrée à la sortie du multiplexeur 11. Le décodeur 19 adressé par la ligne d'adresse 8 a pour but de sélectionner, à l'intérieur du mot de n bits appliqué à l'entrée du multiplexeur 11 chaque bit désigné par le mot d'adresse appliqué sur son entrée et le mot d'attribut PA codé sur p bits qui lui correspond. Le bit 20 représentatif du pixel sélectionné et son attribut PA sont appliqués respectivement à une quatrième entrée et à la première entrée du circuit d'interpolation 14 dans le but de modifier éventuellement leurs valeurs en fonction des données d'interpolation qui sont appliquées sur les deuxième et troisième entrées du circuit d'interpolation 14. Les bits non sélection-25 nés par le décodeur 19 sont appliqués par la ligne 18 à l'entrée du circuit de reformation 17 qui reforme, en fonction de l'information modifiée ou non fournie à la sortie du circuit d'interpolation 14, un nouveau mot binaire qui est appliqué à l'entrée d'un circuit démultiplexeur d'écriture 20 au moyen d'une ligne de données 21 pour écrire le mot éventuellement 30 modifié et les attributs correspondants aux adresses qu'ils occupent normalement dans la mémoire graphique 4 et la mémoire d'attribut 12. Les données de modification de chacun des mots contenus dans la mémoire graphique 4 et la mémoire d'attribut 12 sont introduites à partir d'un clavier 22 qui est relié au processeur 2 par l'intermédiaire de la ligne 35 de liaison 23. Une mémoire de masse 24 est éventuellement couplée par

une ligne 25 au processeur 18 pour transférer à l'intérieur du processeur 2 les instructions de programme nécessaires au fonctionnement de l'ensemble. Le processeur 2 est également relié à une mémoire vive MMU 26 chargée de mémoriser en cours de fonctionnement les instructions et les données introduites à partir du clavier 22 ou de la mémoire de masse 24.

La mémoire graphique selon l'invention est à double accès par partage de cycle. Un premier cycle est réservé au fonctionnement de la console de visualisation 3, un deuxième cycle est réservé au fonctionnement du processus de modification contrôlé par le processeur 2, ce cycle de modification étant caractérisé par un cycle de lecture, un cycle de modification et un cycle de ré-écriture des informations modifiées dans la mémoire graphique et un troisième cycle de lecture directe de la mémoire graphique, l'ensemble de ces cycles étant représenté par le diagramme des temps de la figure 7. Les cycles de la figure 7 sont exécutés par le processeur 2 qui applique des signaux de commande sur le bus de commande 27 pour rafraichir les points ou pixels du graphique visualisés sur l'écran de la console de visualisation et commander les cycles de lecture et d'écriture des différents plans de la mémoire graphique 4 qui contiennent les attributs 12 de chaque pixel et qui constituent la mémoire d'attribut 12. Sur la figure 7 le cycle de rafraichissement, marqué "VISU", de la console de visualisation est représenté avec une durée T sur une période de 2T, le cycle de lecture L des informations contenues dans la mémoire graphique 4 et dans la mémoire d'attribut 12 est représenté entrelacé pendant une durée T en dehors de la durée de rafraichissement de la console de visualisation 3 sur une période de durée 4T, le cycle de modification M suit le cycle de lecture L avec une même durée T et une même période égale de durée 4T, le cycle d'écriture E suit le cycle de modification M avec une même durée T durant une période égale à 4T et le cycle d'accès direct à la mémoire graphique et à la mémoire d'attribut a lieu pendant une durée T entre les instants de rafraichissement de la 30 console de visualisation 3. A titre d'exemple, ce mode de partage de cycles peut être avantageusement utilisé pour la visualisation de mots de 16 pixels pendant une durée de 1184 nanosecondes et l'exécution de cycles de lecture-modification-écriture de deux fois 1184 nanosecondes par pixel ou point à modifier ce qui permet, de couvrir des plages de fonctionne-

25

ment élevées, par exemple, un traitement de 720 points d'image ou pixels par ligne de balayage sur 576 lignes en respectant les normes CCIR du balayage de télévision à 625 lignes, le débit de la console de visualisation correspondant dans ce cas au standard de télévision numérique de 13,5 MHZ pour 25 image/seconde et la durée de cycle T étant voisine de 400 nanosecondes. Ces résultats sont obtenus en organisant par exemple la mémoire graphique en mots de 16 pixels et la mémoire d'attribut 12 en mots d'attribut de 3 bits, chacun des mots étant adressé par le processeur 2 par les bits d'adresse appliqués sur le bus d'adresse 8. Chaque mot lu dans la mémoire graphique 4 est appliqué à l'entrée du multiplexeur 11. La place d'un bit dans le mot correspondant au point ou pixel à modifier est sélectionnée par le multiplexeur 11 et le décodeur 19 à partir des quatre bits de poids faible du mot d'adresse en même temps que 3 bits d'attribut correspondants sont adressés dans la mémoire d'attribut 12 par le bus 15 d'adresse 8. Les bits du mot non désignés par le multiplexeur 11 et le décodeur 19 sont dirigés directement vers les entrées du dispositif de reformation du mot 17 tandis que le bit sélectionné est pris en compte par le circuit d'interpolation 14. Les 3 bits d'attribut lus dans la mémoire d'attribut 12 correspondant au point ou au pixel à modifier sont appliqués 20 sur la première entrée du circuit d'interpolation 14 pendant que le processeur 2 applique simultanément par la ligne de données 15,4 bits de modification PN en même temps que 6 bits de fonction correspondant à la fonction d'interpolation FM choisie par l'opérateur permettant ainsi l'exécution de 64 fonctions d'interpolation. Le bit du mot mémoire sélectionné et l'attribut correspondant sont modifiés pour former un mot PM sur 4 bits qui est obtenu à la sortie du circuit d'interpolation 14 qui est fonction de la valeur 0 ou 1 du bit du point ou du pixel à modifier lu dans la mémoire graphique 4, de l'attribut correspondant lu dans la mémoire d'attribut 12, des données de modification PN fournies par le processeur 2 à l'entrée du 30 circuit d'interpolation 14 et de la fonction d'interpolation transmise également sur la troisième entrée du circuit d'interpolation 14 par le processeur 2.

Pour des commodités de réalisation le circuit d'interpolation est constitué par des mémoires mortes électriquement programmables du type connu sous la désignation anglo saxonne "EPROM" ou des mémoires vives du type connu sous la désignation anglo saxonne "RAM" qui contiennent en mémoire des tables de fonction de modification de la

teinte des points de l'image pour la mise en oeuvre du procédé d'interpolation selon l'invention. A chaque modification de pixel ces tables sont adressées par les bits du mot PA lu dans la mémoire d'attribut représentant la valeur pré-existante du pixel modifié, par la nouvelle valeur PN du pixel que l'on cherche à obtenir pour les points appartenant au tracé et par une valeur d'interpolation qui représente une valeur intermédiaire d'adresse entre deux pixels adjacents de la matrice d'image pour permettre la détermination de la teinte des points de l'écran situés dans l'espace intermédiaire entre la position des pixels de la matrice d'image.

10 Le procédé d'interpolation est inscrit dans un programme d'interpolation qui est exécuté par le processeur 2 et dont les étapes peuvent être exécutées de la façon suivante:

Dans une première étape le processeur 2 calcule l'adresse fractionnaire correspondant à la position du pixel à modifier à l'intérieur des points de la matrice d'image, cette adresse étant déterminée en nombre F de pas d'interpolation dans les directions horizontale et verticale de l'image compris entre deux pixels P<sub>n</sub> et P<sub>n+1</sub> successifs de la matrice d'image à la manière représentée à la figure 8. A titre d'exemple trois bits fractionnaires pourront être utilisés pour adresser les points intermédiaires situés entre deux pixels de la matrice d'image ce qui correspond à huit pas d'interpolation successifs. Le procédé consiste ensuite à calculer dans une deuxième étape la valeur PM du pixel ou point correspondant à l'adresse fractionnaire calculée suivant la relation

$$PM = F \cdot PA + (I-F) \cdot PN$$

25

Ce procédé peut s'appliquer à l'exécution de tracés quelconques sur l'écran de la console de visualisation, ces tracés pouvant être obtenus à partir, par exemple, du tracé de plusieurs vecteurs successifs reliant des points de coordonnées bien définies sur l'écran.

Ce procédé a l'avantage d'être simple à mettre en oeuvre car le 30 tracé d'un vecteur reliant deux points rapprochés de coordonnées  $(X_0, Y_0)$  et  $(X_1 \text{ et } Y_1)$  de l'écran situés aux axes orthonormés X et Y n'exige l'écriture que de quelques lignes de programme. En adoptant les notations  $DX = X_1 - X_0$  et  $DY = Y_1 - Y_0$  avec DX > 0 et DY > 0 et en supposant que la position de deux points est telle que les valeurs absolues |DX| et 35 |DY| des écarts DX et DY vérifient entre elles les relations

11

| DX | > DY | l'exécution du programme est assurée dans une première phase par le calcul de l'incrément qu'il faut donner dans la direction verticale de l'écran (axe Y) à chaque pas d'incrémentation exécuté dans la direction horizontale (axe X). Cette première phase de calcul est suivie par une deuxième phase d'initialisation et une troisième phase d'exécution, l'ensemble de ces trois phases exigeant la suite des instructions suivantes :

```

Calcul de l'incrément DYI = DY/DX <= 0

Initialisation

DY0 = 0

X = X0

Début:

= X + 1

10

DY0 = DY0 + DY1 : F = PARTIE FRACTIONNAIRE de DY0

(3 bits)

= Y0 + PARTIE ENTIERE DY0

DY0 = DYO - PARTIE ENTIERE DY0

ECRIRE X,Y,F

ECRIRE X,Y+1,(1-F)

15

Si X > XI OU Y > YI FIN, SINON DEBUT

(LOGICIEL CABLE)

PROCEDURE ECRIRE X,Y,F

PN = NOUVEAU ATTRIBUT

(fourni par le C.P.U.)

PA = ANCIEN ATTRIBUT

(fourni par la Mémoire)

20

PM = F * PA + (1 - F) * PN

ECRIRE PM

```

Naturellement l'exécution du procédé selon l'invention n'est pas limitée au programme de tracé de vecteurs qui vient d'être décrit ni au format des bits d'attribut et pixels qui peut comporter un nombre très 25 étendu de bits. Au niveau de la programmation l'homme de l'art pourra concevoir très facilement d'autres programmes de tracés pour permettre l'exécution d'arcs de cercles, d'ellipses ou de courbes paramétriques interpolées en utilisant des fonctions du type BSPLINE ou BEZIERS sans pour autant s'écarter du procédé d'interpolation selon l'invention. Egale-30 ment comme le procédé "anti-aliasing" décrit ci-dessus repose sur la valeur en amplitude du pixel, il est évident que les résultats corrects ne pourront être obtenus que si l'attribut défini par exemple sur quatre bits peut décrire les seize couleurs d'un pixel à l'intérieur d'une palette à définir par une autre table de couleurs. Le processus "anti-aliasing" qui 35 vient d'être décrit ne concerne en fait que les systèmes sur lesquels au moins trois bits d'attributs ou pixels sont réservés à l'intensité lumineuse ce qui les différencie des systèmes à quatre bits ne disposant que d'un seul bit d'intensité. On conçoit que le procédé "anti-aliasing" de l'invention ne devient réellement performant lorsque les attributs sont définis sur des longueurs supérieures à quatre bits et plus typiquement pour des systèmes où l'attribut comporte huit bits et plus.

## REVENDICATIONS

1. Dispositif pour l'obtention de tracés continus sur l'écran d'une console de visualisation (3) commandée par un processeur graphique (2) l'image étant constituée par une matrice ordonnée de points d'images ou pixels formés par M rangées de N points ou pixels balayés suivant le principe de balayage des images de télévision, le dispositif comprenant une mémoire graphique (4) pour mémoriser sous une forme binaire l'image de la matrice des points visualisés sur l'écran et une mémoire d'attribut (12) pour contenir les attributs de chacun des points de l'image, caractérisé en ce qu'il comprend également un circuit d'interpolation (14) dans 10 lequel se trouve mémorisée une table de calcul des attributs des points intermédiaires entre points consécutifs de la matrice de points, la table du circuit d'interpolation étant adressée sur une première entrée par la valeur pré-existante PA du pixel à modifier trouvée dans la mémoire d'attribut, sur une deuxième entrée par la valeur nouvelle PN de l'attribut 15 des pixels à modifier pour les faire figurer sur le tracé et sur une troisième entrée par une valeur d'interpolation F calculée par le processeur égale à la partie fractionnaire de la position du point intermédiaire à modifier, chaque emplacement de la table contenant une valeur d'attribut PM vérifiant la relation

20  $PM = F \cdot PA + (1-F) \cdot PN$

V .

la valeur PM obtenue étant transférée dans la mémoire d'attribut (12) pour mettre à jour le contenu de l'emplacement correspondant à l'adresse du point ou pixel modifié.

- 2. Dispositif selon la revendication 1, caractérisé en ce que le circuit d'interpolation est constitué par au moins une mémoire programmable pour contenir la table du circuit d'interpolation, la mémoire étant adressée par le processeur graphique (2) et par les bits d'attribut de chaque mot d'attribut sélectionné dans la mémoire d'attribut (12).

- Dispositif selon l'une quelconque des revendications 1 et 2,

caractérisé en ce que le circuit d'interpolation est commandé par le processeur graphique (2) à partir d'instructions entrées dans le processeur (2) à partir d'un clavier (22).

- 4. Dispositif selon l'une quelconque des revendications 1 à 3, caractérisé en ce que la mémoire graphique (4) est adressée d'une part par la console de visualisation et d'autre part par le processeur graphique (2) au travers un multiplexeur d'adresse commandé par le processeur pour partager les cycles d'accès à la mémoire graphique initialisés par la console de visualisation (3) et le processeur (2).

- 5. Dispositif selon la revendication 4, caractérisé en ce que la mémoire graphique (4) est organisée en mots de longueur fixe.

- 6. Dispositif selon les revendications 4 et 5, caractérisé en ce que le cycle d'accès du processeur (2) à la mémoire graphique (4) se décompose en un cycle de lecture de chaque mot dans lequel se trouve le bit d'un point d'image à modifier, et du mot d'attribut correspondant dans la mémoire d'attribut (12), suivi par un cycle, de modification du bit du point correspondant à modifier, identifié à l'intérieur du mot lu dans la mémoire graphique, et de modification du mot d'attribut lu dans la mémoire d'attribut (12), également suivi par un cycle de ré-écriture du mot contenant le bit modifié dans la mémoire graphique (4) et de ré-écriture du mot d'attribut modifié dans la mémoire d'attribut (12).

- 7. Dispositif selon l'une quelconque des revendications 2 à 6,

20 caractérisé en ce que les mémoires programmables du circuit d'interpolation (14) sont des mémoires mortes électriquement programmables.

- 8. Dispositif selon l'une quelconque des revendications 2 à 6, caractérisé en ce que les mémoires programmables du circuit d'interpolation (14) sont des mémoires vives.

## 1/3

Fig.1

Fig.2

<u>. 6 4 2</u> .

## RAPPORT DE RECHERCHE EUROPEENNE

Numero de la demande

EP 85 40 0735

| Catégorie  | Citation du document avec indication, en cas de besoin.<br>des parties pertinentes                                                               |                                                    | Revendication concernee                                                                                             | CLASSEMENT DE LA<br>DEMANDE (Int. Cl.4)       |      |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|------|

| A          | WESCON CONFERENCE 25, septembre 19 - 31/5-10, El Se J.L. WISE et al. graphics with ar controller"                                                | 981, pages 31/5-1<br>egundo, CA., US;<br>.: "Color | 1,3-6                                                                                                               | G 09 G                                        | 1/16 |

| A          | US-A-4 303 986                                                                                                                                   | (HAKAN LANS)                                       | 1                                                                                                                   |                                               |      |

| A          | EP-A-O 092 973<br>INSTRUMENTS)                                                                                                                   | (TEXAS                                             | 1                                                                                                                   |                                               |      |

|            |                                                                                                                                                  |                                                    |                                                                                                                     |                                               |      |

|            |                                                                                                                                                  |                                                    |                                                                                                                     | ·····                                         |      |

|            |                                                                                                                                                  |                                                    |                                                                                                                     | DOMAINES TECHNIQUES<br>RECHERCHES (Int. Ci.4) |      |

|            |                                                                                                                                                  |                                                    |                                                                                                                     | G 09 G                                        | 1/16 |

|            |                                                                                                                                                  |                                                    |                                                                                                                     |                                               |      |

|            |                                                                                                                                                  |                                                    | -                                                                                                                   |                                               |      |

|            |                                                                                                                                                  |                                                    |                                                                                                                     |                                               |      |

|            |                                                                                                                                                  |                                                    |                                                                                                                     |                                               |      |

|            |                                                                                                                                                  |                                                    |                                                                                                                     |                                               |      |

| Le         | présent rapport de recherche a été é                                                                                                             | tabli pour toutes les revendications               |                                                                                                                     |                                               |      |

|            | Lieu de la recherche<br>LA HAYE                                                                                                                  | Date d'achèvement de la rech<br>17-07-1985         | erche VAN R                                                                                                         | OOST L.L.A                                    | •    |

| Y:pa<br>au | CATEGORIE DES DOCUMEN' rticulièrement pertinent à lui seu rticulièrement pertinent en com tre document de la même catégorière-plan technologique | E : docu<br>l date<br>binaison avec un D : cité d  | rie ou principe à la ba<br>ment de brevet antér<br>de dépôt ou après ce<br>dans la demande<br>pour d'autres raisons | ieur, mais publié à l<br>tte date             | a    |