(1) Numéro de publication:

0 165 108

**A1**

(12)

## DEMANDE DE BREVET EUROPEEN

(21) Numéro de dépôt: 85400870.3

(22) Date de dépôt: 06.05.85

(5) Int. Cí.4: G 04 F 10/00 H 03 M 1/50

(30) Priorité: 11.05.84 FR 8407344

43 Date de publication de la demande: 18.12.85 Bulletin 85/51

(84) Etats contractants désignés: AT BE CH DE FR GB IT LI LU NL SE Demandeur: CENTRE NATIONAL DE LA RECHERCHE SCIENTIFIQUE (C.N.R.S.) 15, Quai Anatole France

(72) Inventeur: Genat, Jean-François 9, Boulevard d'Auteuil F-92100 Boulogne(FR)

F-75007 Paris(FR)

(72) Inventeur: Rossel, François 87, Rue de la Forêt F-93160 Noisy Le Grand(FR)

(74) Mandataire: Joly, Jean-Jacques et al, CABINET BEAU DE LOMENIE 55, rue d'Amsterdam F-75008 Paris(FR)

(54) Convertisseur temps-numérique ultra-rapide.

(57) Une chaîne (10) de portes (11) est formée sur un même substrat de circuit intégré pour permettre la propgation le long de la chaîne d'un signal de départ reçu à une extrémité de la chaîne, et un circuit de verrouillage (15) formé par exemple par une autre chaîne de portes (16) a des sorties connectées aux portes de la chaîne (10) pour pouvoir bloquer l'état de celle-ci à la suite de la réception d'un signal d'arrêt, de sorte que le nombre de portes traversées par le signal de départ est une fonction linéaire du temps écoulé entre la réception du signal de départ et la réception du signal d'arrêt.

## Convertisseur temps-numérique ultra-rapide.

05

10

15

20

25

30

35

La présente invention concerne un convertisseur tempsnumérique, c'est-à- dire un dispositif destiné à fournir une valeur numérique représentant le temps écoulé entre la réception d'un signal de départ et la réception d'un signal d'arrêt.

Le domaine d'application de l'invention est notamment, mais non exclusivement, celui de la mesure de temps très brefs en électronique nucléaire : physique des hautes énergies, physique nucléaire, ou médecine nucléaire. A titre d'exemple, le convertisseur selon l'invention convient particulièrement à la mesure des intervalles de temps de collection aux extrémités de détecteurs de particules.

Les convertisseurs temps-numérique connus sont essentiellement de deux types. Les premiers utilisent un condensateur qui est chargé à courant constant pendant la durée à mesurer, le niveau de charge étant ensuite numérisé; ces convertisseurs sont généralement précis, mais d'une structure complexe. Les seconds sont basés sur l'utilisation d'horloges de référence; ils sont également de structure complexe et leur précision est liée à celle de l'horloge.

La présente invention a pour but de fournir un convertisseur temps-numérique ayant une structure simple permettant sa réalisation sous forme de circuit intégré. La présente invention a aussi pour but de fournir un convertisseur temps-numérique ultrarapide, c'est à dire ayant un temps de réponse très bref.

Ce but est atteint au moyen d'un convertisseur comportant, conformément à l'invention :

- une chaîne de portes formées sur un même substrat de circuit intégré pour permettre la propagation le long de la chaîne d'un signal de départ reçu à une extrémité de la chaîne, et - un circuit de verrouillage ayant des sorties connectées aux portes de la chaîne pour pouvoir bloquer l'état de celles-ci à la suite de la réception d'un signal d'arrêt, de sorte que le nombre de portes traversées par le signal de départ est une fonction linéaire du temps écoulé entre la réception du signal de départ et

la réception du signal d'arrêt.

05

10

15

20

25

30

35

La présente invention est basée sur l'utilisation, en tant que référence temporelle, des temps de propagation de signaux logiques dans un circuit intégré. En effet, les nouvelles technologies de circuits intégrés, dans le cas présent la fabrication de réseaux de portes prédiffusées, assurent, à l'intérieur d'un même échantillon, des dispersions de l'ordre de quelques pour cent sur des ensembles de portes logiques de plusieurs milliers d'unités.

La mesure est réalisée par l'inhibition, à la suite de la réception du signal d'arrêt, de la propagation du signal de départ dans une chaîne de portes.

Cette inhibition peut être réalisée de plusieurs façons.

Selon un mode de réalisation préféré de l'invention le circuit de verrouillage comprend une deuxième chaîne de portes qui est formée sur un même substrat de circuit intégré et à une extrémité de laquelle est reçu le signal d'arrêt, les deux chaînes formant des trajets parallèles avec liaisons entre les portes de la première chaîne et les portes de la deuxième chaîne de sorte que l'état des portes d'au moins l'une des deux chaînes est verrouillé lorsque le signal de départ se propageant le long de la première chaîne et le signal d'arrêt se propageant le long de la deuxième chaîne se sont rencontrés. La configuration des portes de la première chaîne, de même, éventuellement, que celle des portes de la deuxième chaîne est représentative du temps à mesurer. Aussi, le convertisseur est-il muni de moyens de codage ayant des entrées reliées aux portes d'au moins l'une des chaînes pour fournir une valeur numérique de mesure fonction de l'état de ces portes.

Les sens de propagation du signal de départ et du signal d'arrêt le long des deux chaînes parallèles peuvent être inverses l'un de l'autre ou identiques. Dans ce dernier cas, le temps de propagation à travers les portes de la première chaîne est supérieur au temps de propagation à travers les portes de la deuxième chaîne afin que le signal d'arrêt puisse "rattraper" le

signal de départ.

05

10

15

20

25

30

35

Selon un autre mode de réalisation de l'invention, le circuit de verrouillage comprend un ensemble de trajets formés chacun entre une entrée commune recevant le signal d'arrêt et une porte respective de la chaîne de propagation du signal de départ. Dans ce cas, le signal d'arrêt est appliqué de façon quasi-simultanée aux différentes portes de sorte que l'état de la chaîne est figé dès réception du signal d'arrêt. Des moyens de lecture de l'état des portes de la chaîne de propagation du signal de départ sont prévus pour fournir une valeur numérique représentative du temps à mesurer.

Dans tous les cas, le convertisseur conforme à l'invention permet de donner de façon ultra-rapide le résultat de la mesure de temps très brefs. Un avantage supplémentaire tient à ce que le convertisseur est réalisable sous forme de circuit intégré.

D'autres particularités et avantages du convertisseur tempsnumérique selon l'invention ressortiront à la lecture de la description faite ci-après, à titre indicatif mais non limitatif, en référence aux dessins annexés sur lesquels :

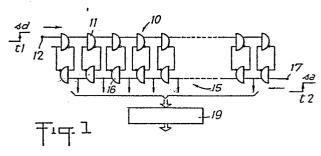

- la figure 1 est un schéma d'un convertisseur temps-numérique selon un premier mode de réalisation de l'invention,

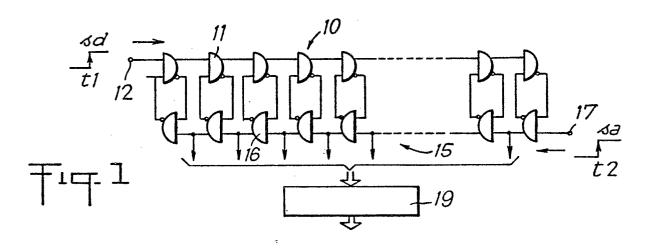

- la figure 2 est un schéma d'un convertisseur temps-numérique selon un mode préféré de réalisation de l'invention, et

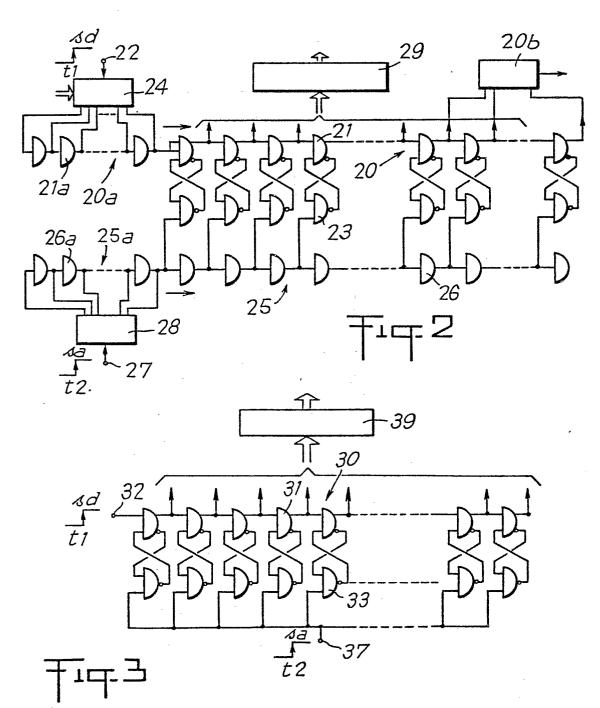

- la figure 3 est un schéma d'un convertisseur temps-numérique selon encore un autre mode de réalisation de l'invention.

Le convertisseur de la figure 1 comporte deux chaînes de portes 10 et 15 similaires, formées parallèlement l'une à l'autre mais avec des directions de propagation opposées. Les chaînes de portes sont formées à partir d'un réseau de portes prédiffusées sur un même substrat de circuit intégré.

Chaque porte 11 de la chaîne 10 a une première entrée reliée à une sortie non-inverseuse de la porte 11 précédente et une seconde entrée reliée à la sortie inverseuse d'une porte 16 associée de la chaîne 15. Celle-ci a une première entrée reliée à la sortie non-inverseuse de la porte 16 précédente et une seconde

entrée reliée à la sortie inverseuse de la porte 11 associée. A chaque porte 11 est ainsi associée une porte 16, et réciproquement. On notera que le terme " porte " est utilisé ici pour désigner un circuit logique à travers lequel un signal entrant peut ou non être propagé selon l'état d'un signal de commande qui peut être reçu également par ce circuit.

05

10

15

20

25

30

35

Un signal de départ sd est appliqué à l'extrémité d'entrée 12 de la chaîne de portes 10 sous forme par exemple d'une transition de niveau logique bas à niveau logique haut à un instant ti. Un signal d'arrêt est appliqué à l'extrémité d'entrée 17 de la chaîne de portes 15 également sous forme d'une transition de niveau logique bas à niveau logique haut à un instant t2. Les entrées 12 et 17 sont situées à des extrémités opposées des chaînes 10 et 15, les signaux sd et sa se propageant en sens opposés. A chaque fois que le signal sd franchit une porte 11, la porte 16 correspondante est bloquée. De la même façon, à chaque fois que le signal sa franchit une porte 16, la porte 11 correspondante est bloquée. La rencontre des signaux sd et sa s'effectue en un point tel que le nombre de portes traversées par l'un deux est une fonction linéaire du temps recherché  $\Delta t = t2 - t1$ . L'état des portes après la rencontre est figé. Il peut être lu immédiatement sur les sorties des portes de l'une des chaînes, par exemple sur les sorties non-inverseuses des portes 16, celles-ci étant reliées à un circuit de codage 19. Si l'on désigne par M le nombre total de portes dans chaque chaine, par m le nombre de portes 11 franchies par le signal de départ, et par  $t_{pd}$  le temps de propagation à travers une porte, l'on a  $\Delta t = t_{pd}$  (2 m - M). Le circuit de codage peut être agencé pour délivrer directement un mot numérique binaire donnant sur N bits une valeur proportionnelle à At.

Le bit de poids faible du mot fourni par le convertisseur vaut 2  $t_{pd}$ . Pour un convertisseur N bits dont le poids faible vaut  $\delta t$  et avec une précision absolue égale au demi-poids faible, la dispersion  $\sigma t_{pd}$  des temps de propagation par porte de circuit intégré doit satisfaire :  $\sigma t_{pd} < \delta t/2^{N/2} + 2$  (1).

L'on peut aussi montrer que pour une dispersion donnée, le nombre N de bits significatifs maximum que le convertisseur peut fournir, est tel que :

$N \le 1/3 (2 \log_2 (T/t_{pd}) - 4),$

10

15

20

25

30

35

O5 Tétant la valeur de la pleine échelle du convertisseur. La valeur du bit de poids faible est ici égale à 2 t<sub>pd</sub>. Une diminution de cette valeur en vue d'améliorer la précision ou la finesse de la mesure requiert une diminution du temps de propagation par porte.

La figure 2 illustre un autre mode de réalisation d'un convertisseur selon l'invention avec lequel le bit de poids faible a une valeur qui peut être inférieure au temps de propagation par porte.

Le signal de départ sd est appliqué à l'extrémité d'entrée 22 d'une première chaîne 20 de portes 21 analogue à la chaîne 10 du convertisseur de la figure 1. Le signal d'arrêt sa est appliqué à l'extrémité d'entrée 27 d'une deuxième chaîne 25 de portes 26 de transmission.

Chaque porte 26 est agencée pour transmettre systématiquement le signal qui se présente sur son entrée de signal, celle-ci étant reliée à son entrée de commande. Chaque entrée d'une porte 26 est reliée à une entrée d'une porte 23 dont la sortie inverseuse est connectée à une entrée d'une porte 21 associée. L'autre entrée de cette porte 21 est reliée à la sortie non-inverseuse de la porte 21 précédente tandis que l'autre entrée de la porte 23 est connectée à la sortie inverseuse de la porte 21 associée. Ainsi, une porte 26 est associée à chaque couple de portes 21 - 23.

Le signal de départ sd est appliqué à l'entrée 22 à l'instant ti et se propage le long de la chaîne 20. On notera que le franchissement de chaque porte 21 par le signal sd s'accompagne du blocage de la porte 23 associée. Le signal d'arrêt sa est appliqué à l'entrée 27 à l'instant t2 et se propage le long de la chaîne 25. La propagation le long de cette chaîne est plus rapide que celle le long de la chaîne 20 de sorte que le signal sa puisse rattraper le signal de départ. Dès que le signal sa rencontre une porte 23 non bloquée, il passe à travers celle-ci pour pouvoir bloquer la porte 21 correspondante, bloquant ainsi la propagation du signal de départ. Le signal sa continue d'être propagé le long de la chaîne 25, bloquant successivement les portes de la chaîne 20 non franchies par le signal de départ. L'état des portes de la chaîne 20 est une fonction linéaire de Δt = t2 - t1. Il peut être lu immédiatement sur les sorties non-inverseuses des portes 21, celles-ci étant reliées à un circuit de codage 29. Si l'on désigne par m le nombre de portes 21 franchies par le signal de départ, par t1<sub>pd</sub> le temps de propagation par porte de la chaîne 20 et par t2<sub>pd</sub> le temps de propagation par porte de la chaîne 25, l'on a Δt = m (t1<sub>pd</sub> - t2<sub>pd</sub>). Le circuit de codage 29 peut être agencé pour fournir le nombre m sous forme d'un mot numérique binaire.

Le temps de propagation à travers les portes d'une chaîne dépend de plusieurs facteurs : nombre de portes connectées en sortie de chaque porte de la chaîne, longueur des connexions entre portes, tension d'alimentation du circuit,... En l'espèce, l'on peut jouer sur l'un ou plusieurs de ces facteurs pour avoir des temps de propagation tipd et t2pd différents tels que : tipd > t2pd.L'on pourrait disposer la chaîne de portes 21 avec les portes 23 associées sur un substrat de circuit intégré et la chaîne de portes 26 sur un autre substrat. Toutefois, de préférence, les portes 21, 23, 26 sont formées à partir d'un réseau de portes prédiffusées sur un même substrat et la différence de temps de propagation est obtenue en jouant sur le nombre de portes connectées à chaque porte d'une chaîne et sur les longueurs de connexion.

Le bit de poids faible du mot fourni par le convertisseur

vaut t1<sub>pd</sub> - t2<sub>pd</sub>; il peut donc prendre une valeur

inférieure à t1<sub>pd</sub> et t2<sub>pd</sub>. En ce qui concerne les

dispersions ct1<sub>pd</sub> et ct2<sub>pd</sub> sur les temps de propagation,

l'on retrouve la condition (1) avec :

ot<sub>pd</sub> = (ot1<sup>2</sup><sub>pd</sub> + ot2<sup>2</sup><sub>pd</sub>) 1/2. L'on

retrouve également la relation (2) donnant le nombre de bits N.

Les réseaux prédiffusés disponibles actuellement présentent des temps de propagation par porte inférieurs à la nanoseconde et des dispersions inférieures à quelques dizaines de picosecondes. A titre indicatif, le convertisseur de la figure 2 permet dans ces conditions un codage sur 5 bits avec un poids faible égal à 500 ps et une pleine échelle de 16 ns. De plus, et c'est un avantage commun à tous les modes de réalisation de l'invention, le résultat est disponible très rapidement.

Sur la figure 2 sont également représentés des moyens de règlage du convertisseur.

Pour le règlage du zéro, on connecte en amont de chaque chaîne 20, 25 une suite de portes de transmission, respectivement 20a, 25a. Le signal de départ est appliqué sur une borne d'entrée 22a qui est reliée à l'entrée d'un circuit d'aiguillage 24 dont les sorties sont reliées à des entrées respectives des portes 21a de la suite 20a. De même le signal d'arrêt est appliqué sur une borne d'entrée 27a qui est reliée à l'entrée d'un circuit d'aiguillage 28 dont les sorties sont reliées à des entrées respectives des portes 26a de la suite 25a. Chaque circuit d'aiguillage a une entrée de commande permettant de sélectionner une des sorties. Le réglage de zéro est effectué en positionnant les circuits d'aiguillage de manière que la réponse du convertisseur soit égale à zéro lorsque les signaux sd et sa sont appliqués simultanément aux bornes 22a et 27a.

Pour le réglage de la pleine échelle, un circuit de décodage 20b est disposé à l'extrémité de la chaîne 20 opposée à celle d'entrée, ce circuit de décodage 20b ayant des entrées connectées aux sorties non-inverseuses de plusieurs portes 21. Le convertisseur fonctionnant sur N bits, la chaîne 20 comprend au moins 2N portes 21. En fait, le nombre de portes 21 est choisi un peu supérieur à 2N, par exemple égal à 2N + k et le circuit de décodage 20b reçoit les sorties des 2k + 1 dernières portes de la chaîne. Comme déjà indiqué, le temps de propagation par porte, ici t1 pd est fonction de la tension d'alimentation du circuit intégré. Aussi, le circuit de décodage 20b est-il utilisé pour

fournir une grandeur de commande de règlage de la tension d'alimentation, de manière que la pleine échelle soit juste atteinte lorsque deux signaux de référence sd et sa sont appliqués avec un intervalle de temps égal à la pleine échelle, le circuit de codage 29 étant relié aux 2N premières portes de la chaîne 21.

On notera que plusieurs réglages alternés du zéro et de la pleine échelle peuvent être nécessaires.

05

10

15

20

25

30

35

Dans ce qui précède, on a envisagé le cas où la propagation du signal de départ dans une chaîne de portes est stoppée en étant rejointe par la propagation du signal d'arrêt dans une autre chaîne de portes.

La figure 3 illustre un autre mode de réalisation d'un convertisseur selon l'invention dans lequel la propagation du signal de départ dans une chaîne de portes est stoppée par le blocage en parallèle des portes de la chaîne en réponse à la réception du signal d'arrêt.

Le signal de départ sd est reçu à l'extrémité d'entrée 32 d'une chaîne 30 de portes 31 tandis que le signal d'arrêt sa est appliqué sur une borne 37 en parallèle sur les premières entrées de portes 33 associées chacune à une porte 31 respective. Les connexions des portes 31 et 33 sont identiques à celles des portes 21 et 23 du convertisseur de la figure 2, les portes 31 et 33 étant formées sur un même substrat de circuit intégré à partir d'un réseau de portes prédiffusées.

Le franchissement de chaque porte 31 par le signal sd s'accompagne du blocage de la porte 33 associée. Le signal d'arrêt passe à travers les portes 33 non encore bloquées pour bloquer les portes 31 associées et arrêter ainsi la propagation du signal sd. L'état des portes de la chaîne 30 est une fonction linéaire de l'intervalle de temps  $\Delta$  t séparant les instants t1 et t2 de réception des signaux sd et sa. Cet état est lu directement sur les sorties non-inverseuses des portes 31 et converti sous forme d'un mot numérique au moyen d'un circuit de codage 39.

Le bit de poids faible  $\delta t$  du mot fourni par le convertisseur vaut  $t_{\rm pd}$ , c'est-à-dire le temps de propagation par porte de la

chaîne 30. Pour un convertisseur N bits de précision égale au demi-poids faible, la dispersion  $\sigma t_{pd}$  du temps de propagation  $t_{pd}$  doit ici satisfaire la condition :  $\sigma t_{pd} < \delta t/2^{(N+3)}$  (3).

05

On notera que cette condition est moins forte d'un facteur 2<sup>1/2</sup> que la condition (1), du fait qu'il y a une seule propagation dans une seule chaîne. Toutefois, une dispersion supplémentaire est introduite du fait que le verrouillage des portes 31 de la chaîne 30 ne peut être exactement simultané.

## REVENDICATIONS

05

10

15

20

25

30

35

- 1. Convertisseur temps-numérique ultra-rapide, caractérisé en ce qu'il comporte:

- une chaîne (10 ; 20 ; 30) de portes (11 ; 21 ; 31) formées sur un même substrat de circuit intégré pour permettre la propagation le long de la chaîne d'un signal de départ reçu à une extrémité de la chaîne, et

- un circuit de verrouillage (15 ; 23 , 25 ; 33) ayant des sorties connectées aux portes de la chaîne pour pouvoir bloquer l'état de celle-ci à la suite de la réception d'un signal d'arrêt, de sorte que le nombre de portes traversées par le signal de départ est une fonction linéaire du temps écoulé entre la réception du signal de départ et la réception du signal d'arrêt.

- 2. Convertisseur selon la revendication 1, caractérisé en ce que le circuit de verrouillage comprend une deuxième chaîne (5; 25) de portes (16; 26) qui est formée sur un même substrat de circuit intégré et à une extrémité de laquelle est reçu le signal d'arrêt, les deux chaînes (10; 20) (15; 25) formant des trajets parallèles avec liaisons entre les portes (11; 21) de la première chaîne et les portes (16; 26) de la deuxième chaîne de sorte que l'état des portes d'au moins l'une des chaînes est verrouillé lorsque le signal de départ se propageant le long de la première chaîne et le signal d'arrêt se propageant le long de la deuxième chaîne se sont rencontrés.

- 3. Convertisseur selon la revendication 2, caractérisé en ce qu'il comporte des moyens de codage (19, 29) ayant des entrées reliées aux portes d'au moins l'une des chaînes (10, 20) pour fournir une valeur numérique de mesure fonction de l'état de ces portes.

- 4. Convertisseur selon l'une quelconque des revendications 2 et 3, caractérisé en ce que le signal de départ et le signal d'arrêt se propagent dans le même sens, le temps de propagation à travers les portes (21) de la première chaîne étant supérieur au temps de propagation à travers les portes (26) de la deuxième chaîne.

- 5. Convertisseur selon l'une quelconque des revendications 2 et 3, caractérisé en ce que le signal de départ et le signal d'arrêt se propagent en sens opposés.

- 6. Convertisseur selon la revendication 1, caractérisé en ce qu'à chaque porte (21; 31) de la chaîne (20; 30) est associé un circuit respectif (23; 33) formant porte dont une première entrée est reliée à la porte associée de la chaîne pour bloquer ledit circuit (23; 33) en réponse au passage du signal de départ à travers ladite porte (21; 31), dont une seconde entrée est connectée pour recevoir le signal d'arrêt, et dont une sortie est reliée à la porte associée (21; 31) de la chaîne pour bloquer cette porte en réponse au signal d'arrêt lorsque le signal de départ n'a pas encore franchi ladite porte (21; 31).

- 7. Convertisseur selon la revendication 6, caractérisé en ce que le signal d'arrêt est appliqué en parallèle sur les secondes entrées des circuits portes (33) associés aux portes (31) de la chaîne (30).

## RAPPORT DE RECHERCHE EUROPEENNE

EP 85 40 0870

|                                                                            |                                                                                                                                                                                                                   | ERES COMME PERTINEN                                                   | <del></del>                                                           | A. A. C. T. |

|----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------|-------------------------------------------------|

| atégorie                                                                   |                                                                                                                                                                                                                   | c indication, en cas de besoin,<br>es pertinentes                     | Revendication concernée                                               | CLASSEMENT DE LA<br>DEMANDE (Int. Cl.4)         |

| A                                                                          | US-A-4 433 919 * Colonne 2, 1 3, ligne 50; fig                                                                                                                                                                    | igne 18 - colonne                                                     | 1-6                                                                   | G 04 F 10/00<br>H 03 M 1/50                     |

| A                                                                          | US-A-3 423 676 TARCZY-HORNOCH) * Colonne 2, 1 7, ligne 74; fig                                                                                                                                                    | igne 39 - colonne                                                     | 1-7                                                                   |                                                 |

| A                                                                          | US-A-4 439 046<br>* Figure *                                                                                                                                                                                      | (D.R. HOPPE)                                                          | 7                                                                     |                                                 |

| A                                                                          | 1959, pages 31-3<br>R.H. RAGSDALE et                                                                                                                                                                              | 6-6, no. 1, mars<br>4, New York, US;<br>al.: "A                       | 1                                                                     |                                                 |

|                                                                            | chronotron for r<br>neutron time-of-<br>measurements"<br>* Figure 1 *                                                                                                                                             | ·                                                                     |                                                                       | DOMAINES TECHNIQUES RECHERCHES (Int. Ci.4)      |

| A                                                                          | FR-A-2 088 363                                                                                                                                                                                                    | (IBM CORP.)                                                           | 1                                                                     | H 03 K<br>H 03 M                                |

| A                                                                          | US-A-3 638 047                                                                                                                                                                                                    | (L.F. KLEIN)                                                          | 1                                                                     |                                                 |

| A                                                                          | US-A-4 164 666                                                                                                                                                                                                    | (M. HIRASAWA)                                                         | 1                                                                     |                                                 |

|                                                                            |                                                                                                                                                                                                                   | · •• ••                                                               |                                                                       |                                                 |

|                                                                            |                                                                                                                                                                                                                   |                                                                       | ·                                                                     |                                                 |

| Le                                                                         | present rapport de recherche a été ét                                                                                                                                                                             | tabli pour toutes les revendications                                  | -                                                                     |                                                 |

| Lieu de la recherche LA HAYE  Date d'achevement de la recherche 27-08-1985 |                                                                                                                                                                                                                   | EXEL                                                                  | Examinateur<br>MANS U.G.J.R.                                          |                                                 |

| Y: pa<br>au<br>A: ar<br>O: di                                              | CATEGORIE DES DOCUMENT<br>articulièrement pertinent à lui seu<br>articulièrement pertinent en comb<br>utre document de la même catégo<br>rière-plan technologique<br>vulgation non-écrite<br>ocument intercalaire | I E documen date de d binaison avec un D: cité dans orie L: cité pour | t de brevet anté<br>épôt ou après c<br>la demande<br>d'autres raisons |                                                 |