11) Numéro de publication:

0 179 693

**A1**

## DEMANDE DE BREVET EUROPEEN

(21) Numéro de dépôt: 85401860.3

(5) Int. Cl.4: **H 01 L 27/08** H 01 L 21/82, H 01 L 29/78

(22) Date de dépôt: 24.09.85

(30) Priorité: 28.09.84 FR 8414988

(43) Date de publication de la demande: 30.04.86 Bulletin 86/18

(84) Etats contractants désignés: AT DE FR GB IT NL

71) Demandeur: THOMSON-CSF 173, Boulevard Haussmann F-75379 Paris Cedex 08(FR)

(72) Inventeur: Thomas, Gilles THOMSON-CSF SCPI 173, bld Haussmann F-75379 Paris Cedex 08(FR)

(74) Mandataire: Guérin, Michel et al, THOMSON-CSF SCPI 19, avenue de Messine F-75008 Paris(FR)

(54) Structure de circuit intégré comportant des transistors CMOS à tenue en tension élevée, et son procédé de fabrication.

(57) L'invention concerne une structure de circuit intégré et un procédé de fabrication de cette structure.

Cette structure incorpore à la fois des transistors MOS basse tension à canal N et à canal P (MOS N BT et MOS P BT) et des transistors MOS haute tension à canal N et à canal P (MOS N HT et MOS P HT). On forme simultanément des régions P- (20) pour les caissons des MOS N BT, des régions P- (22) incorporant uniquement la source et le canal des MOS N HT, et des régions P<sup>-</sup> (24) incorporant uniquement le drain des MOS P HT.

Ьiд.8

## STRUCTURE DE CIRCUIT INTEGRE COMPORTANT DES TRANSISTORS CMOS A TENUE EN TENSION ELEVEE, ET SON PROCEDE DE FABRICATION

La présente invention concerne les circuits intégrés et plus particulièrement les circuits réalisés selon une technologie CMOS, c'est-à-dire incorporant sur un même substrat semiconducteur à la fois des transistors MOS à canal N et des transistors MOS à canal P. Cette technologie est utilisée notamment pour la réalisation de fonctions logiques et elle permet en particulier d'obtenir des circuits à faible consommation et travaillant à très basse tension (quelques volts).

5

10

15

20

25

Cependant, on désire parfois obtenir une tenue en tension beaucoup plus élevée que celle que permet la technologie normale CMOS; c'est le cas par exemple pour des étages de sortie commandant des dispositifs spéciaux tels que des dispositifs de visualisation alimentés sous une tension de l'ordre d'une centaine de volts.

On a déjà proposé des structures de transistors MOS ayant une tenue en tension améliorée permettant de répondre à cet impératif; ces transistors possèdent une région de drain qui n'est pas immédiatement adjacente à la région de canal (c'est-à-dire la région recouverte par la grille de commande), mais qui en est séparée par une région de même type de conductivité que la région de drain et de dopage beaucoup plus faible; cette région est relativement large (plusieurs microns par exemple entre la région de drain fortement dopée et la région de canal) et elle sert à supporter une partie de la tension appliquée en permettant une extension vers le drain de la charge d'espace qui se développe lorsque le transistor est non conducteur.

Dans les quelques tentatives qui ont pu être faites jusqu'à maintenant pour réaliser sur un même substrat semiconducteur à la fois des transistors CMOS logiques et des transistors MOS haute tension, on a toujours proposé des structures qui ont l'inconvénient

de nécessiter un nombre relativement élevé d'étapes de fabrication et un nombre élevé de masques différents.

Un but de l'invention est de proposer une structure et un procédé de réalisation de cette structure, qui permet une fabrication en un nombre d'étapes peu élevé et avec un nombre de masques également peu élevé, cette structure incorporant des transistors CMOS logiques (basse tension) et des transistors MOS haute tension à canal N et à canal P.

5

10

15

20

25

30

Un autre but de l'invention est de proposer une structure incorporant des transistors CMOS logiques et des transistors CMOS haute tension, cette structure étant telle qu'on puisse y incorporer aussi des transistors bipolaires sans modifier le procédé de fabrication. Il est en effet très souhaitable, dans un processus industriel de fabrication, que les étapes de procédé soient aussi universelles que possible pour qu'un grand nombre de produits très différents les uns des autres puissent suivre dans une large mesure une même chaine de fabrication. Ici, on veut que cela soit possible même si ces produits incorporent des éléments aussi différents que des transistors CMOS logiques (basse tension), des transistors CMOS haute tension et des transistors bipolaires.

La structure de base que l'on propose ici pour la réalisation d'un circuit incorporant des transistors MOS logiques à canal N et à canal P et des transistors MOS haute tension à canal N et à canal P comprend:

- une pastille semiconductrice constituée d'un substrat recouvert d'une couche épitaxiale peu dopée de type N;

- des premières régions de type P, peu dopées, s'étendant à partir de la surface de la pastille semiconductrice sur une partie de la profondeur de la couche épitaxiale, ces régions constituant des caissons dans lesquels sont formés la source, le drain et le canal de transistors MOS basse tension à canal N;

- des régions de type P<sup>+</sup> fortement dopées, moins profondes que les régions de type P<sup>-</sup> peu dopées, s'étendant à partir de la surface de la pastille semiconductrice et constituant la source et le drain des transistors MOS à canal P, basse tension ou haute tension;

- des régions de type N<sup>+</sup> fortement dopées, moins profondes que les régions de type P<sup>-</sup>, s'étendant à partir de la surface de la pastille semiconductrice pour constituer la source et le drain de transistors MOS à canal N, basse tension ou haute tension;

5

10

15

20

25

30

- au moins une seconde région de type P, de même profil de concentration que les premières régions et s'étendant jusqu'à la même profondeur, cette seconde région entourant une région de source de type N<sup>+</sup> et constituant une région de canal d'un transistor MOS haute tension à canal N, transistor qui comporte par ailleurs une région de drain de type N<sup>+</sup> située en dehors de la seconde région et écartée d'elle de telle manière qu'il existe une zone de couche épitaxiale de type N peu dopée, non directement contrôlée par la grille du transistor, entre la région de drain et la seonde région,

- au moins une troisième région de type P, de même profil de concentration que les premières et secondes régions et s'étendant jusqu'à la même profondeur, cette troisième région entourant une région de drain de type P d'un transistor MOS haute tension à canal P dont la région de canal est constituée par une région de couche épitaxiale de type N peu dopée, adjacente à la troisième région, la région de drain de type P de ce transistor étant écartée de la région de canal de telle manière qu'il existe entre elles une zone de la troisième région non directement contrôlée par la grille du transistor, et la région de source de ce transistor étant située en dehors de la troisième région.

Cette structure, dont la caractéristique la plus marquante est le fait que les transistors MOS haute tension, aussi bien à canal N qu'à canal P, sont réalisés à partir de diffusions localisées dans une couche épitaxiée peu dopée et identiques à la diffusion des caissons d'isolement des MOS N basse tension, permet une réalisation qui est très simple et qui rend possible des extensions notamment à des structures où des transistors CMOS et des transistors bipolaires sont combinés sans qu'il soit nécessaire de changer le processus global de traitement des tranches de circuits intégrés.

Le procédé de fabrication selon l'invention se caractérise donc quant à lui par la formation (implantation/diffusion) de régions de type P en une même étape, à partir de la surface de la couche épitaxiée de type N, non seulement aux endroits destinés à former des caissons englobant des transistors MOS à canal N dans leur totalité (source + drain + canal) mais aussi dans des régions à l'intérieur desquelles on ne diffusera ultérieurement que la source (mais pas le drain) de transistors MOS à canal N ou que le drain (mais pas la source) de transistors à canal P.

5

10

15

20

25

30

D'autres caractéristiques et avantages de l'invention apparaîtront à la lecture de la description détaillée qui suit et qui est faite en référence aux dessins annexés dans lesquels :

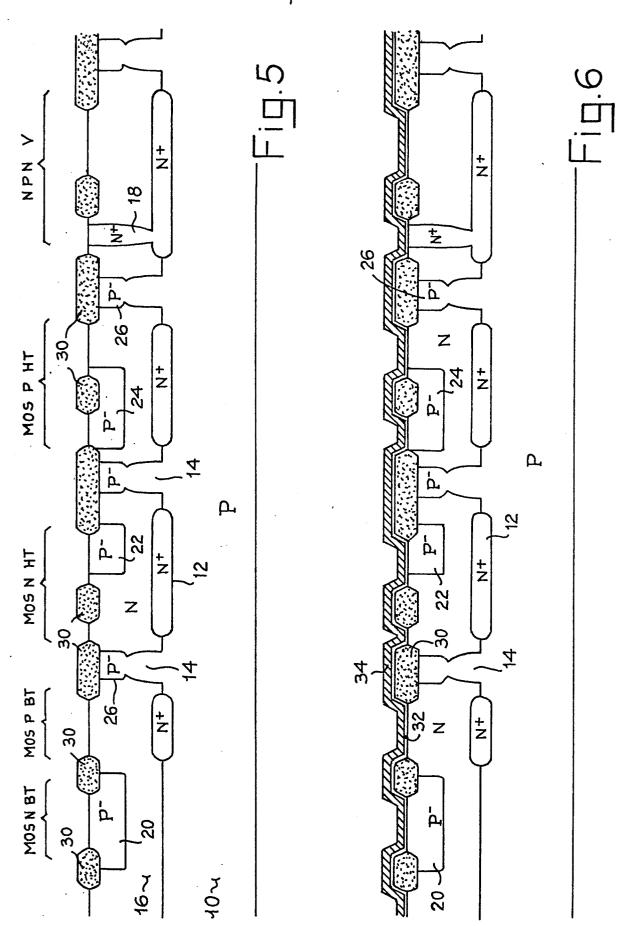

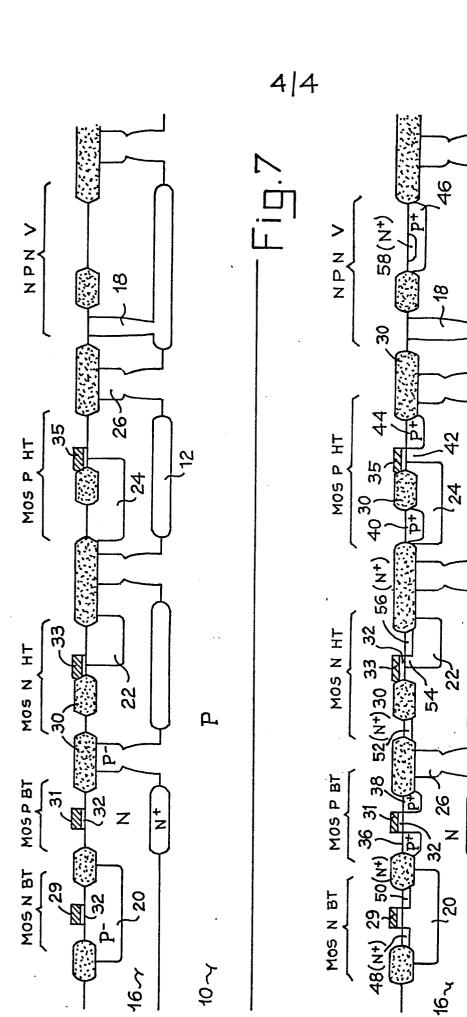

- les figures 1 à 7 représentent les étapes successives du procédé de fabrication selon l'invention;

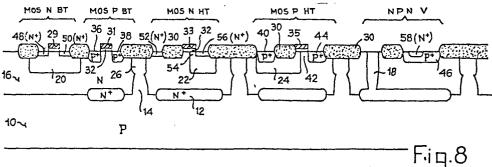

- la figure 8 représente en coupe transversale la structure d'un exemple de réalisation de circuit intégré selon l'invention, avant la mise en place d'interconnexions métalliques superficielles.

Sur ces figures, les échelles horizontales et verticales ne sont pas respectées, pour faciliter la représentation.

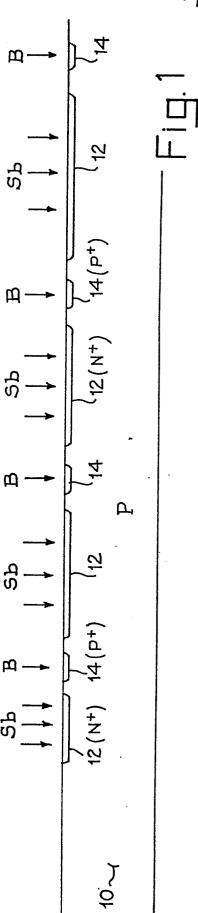

Dans l'exemple de réalisation représenté, on part d'un substrat 10 de silicium de type P, étant entendu que dans certaines applications on pourrait partir de substrats différents; par exemple un substrat P/P<sup>+</sup> c'est-à-dire un substrat de type P, fortement dopé sur sa face arrière seulement (notamment lorsqu'on veut réaliser dans le circuit un transistor de puissance bipolaire PNP vertical dont le collecteur est accessible par la face arrière); ou encore un substrat de type N<sup>+</sup>, fortement dopé sur toute son épaisseur, par exemple si on veut réaliser dans le circuit un transistor bipolaire de puissance NPN vertical dont le collecteur est accessible par la face arrière du substrat.

Sur la face avant du substrat (face supérieure sur les figures), on effectue une première implantation localisée d'une impureté de type N (antimoine par exemple), avec une concentration élevée, pour former localement des régions 12 de type N<sup>+</sup> qui constitueront ultérieurement ce qu'on appelle des couches enterrées.

Cette implantation se fait à travers un masque de résine ouvert seulement aux endroits correspondant aux régions 12.

5

10

15

20

25

30

Cette implantation de type N<sup>+</sup> est suivie ultérieurement d'une croissance épitaxiale de silicium monocristallin sur toute la face supérieure du substrat 10. Toutefois, dans l'exemple de réalisation plus précisément décrit, on prévoit auparavant une étape supplémentaire due au fait que des zones d'isolement par jonction sont prévues entre les diverses zones actives de circuit, par exemple entre les différents transistors MOS qui n'ont pas leurs sources reliées au même potentiel; plus précisément, l'isolement est fait par des murs d'isolement de type P traversant toute la couche épitaxiale depuis sa surface jusqu'au substrat de type P; ces murs sont formés par une double diffusion d'impuretés de type P, à savoir une diffusion remontant par le bas depuis le substrat et un dopage par le haut depuis la surface de la couche épitaxiale. C'est pourquoi, avant l'étape de croissance épitaxiale, on procède à une deuxième implantation ionique sur la surface supérieure du substrat 10, avec une impureté de type P cette fois (par exemple du bore), cette implantation est localisée par un masque de résine ouvert aux endroits où un mur d'isolement est désiré et on obtient alors la structure de la figure 1 avec des régions 12 de type N<sup>+</sup> et des régions 14 de type P+ affleurant à la surface du substrat.

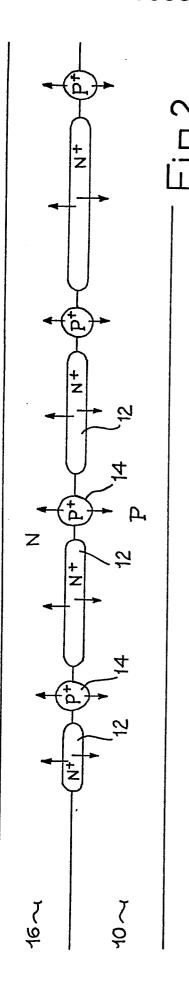

On fait croître alors sur toute la surface supérieure du substrat une couche épitaxiale 16 de silicium monocristallin peu dopé, de type N; pendant la croissance de cette couche, ainsi d'ailleurs que dans certaines étapes ultérieures de traitement thermique, les impuretés implantées précédemment diffusent à la fois vers le substrat 10 et vers la couche épitaxiale 16, comme cela est indiqué sur la figure 2.

Dans les figures suivantes, on a représenté les régions de couche enterrée 12 à cheval sur la frontière entre le substrat de départ de type P et la couche épitaxiale 16 qui le recouvre. Quant

aux régions 14, elles diffusent d'une part vers le bas, réduisant l'influence du NPN latéral parasite formé par les couches enterrées, et d'autre part vers le haut où elles forment la partie inférieure des futurs murs d'isolement.

5

10

15

20

25

30

Dans l'exemple décrit, on a prévu que le circuit intégré comprend non seulement des transistors à effet de champ (MOS) mais aussi un transistor bipolaire NPN vertical dans lequel le courant de collecteur est recueilli par une portion de couche enterrée 12 située en-dessous de ce transistor. Dans ce cas, on crée un puits d'accès 18 à cette couche enterrée; ce puits est une région de type N<sup>+</sup>, fortement dopée, traversant la couche épitaxiale 16 depuis sa surface jusqu'à la couche enterrée. Le mieux est alors de réaliser ce puits d'accès par diffusion profonde de phosphore (prédépot de POCl<sub>3</sub>) immédiatement après la formation de la couche épitaxiale 16. La figure 3 représente la structure du circuit intégré à ce stade de la fabrication.

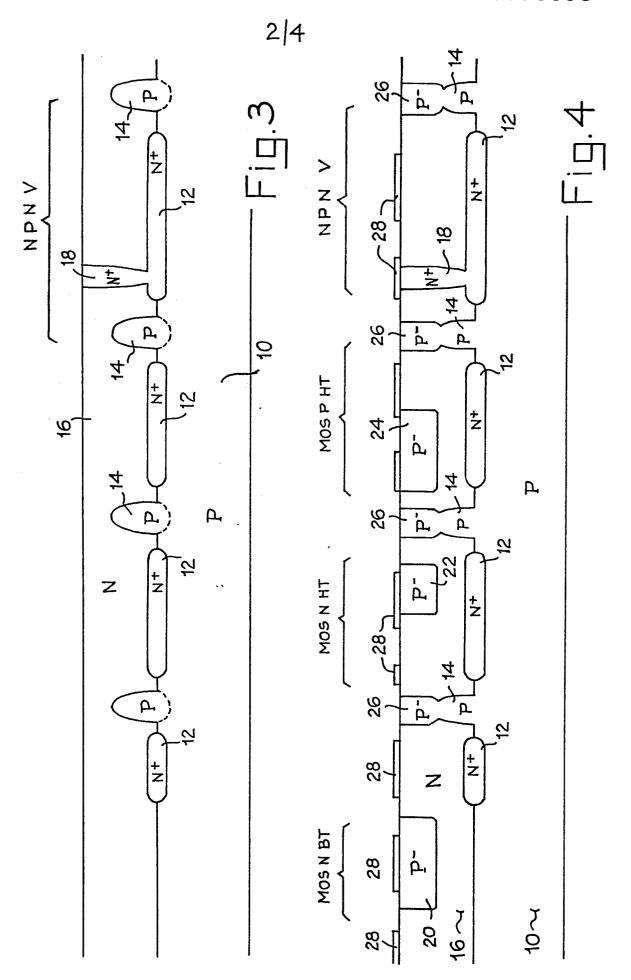

L'étape suivante est une étape fondamentale du procédé. Elle consiste à former localement des régions de type P peu dopées (qu'on désignera par régions P¯), qui s'étendent à partir de la surface de la couche épitaxiale sur une partie de la profondeur de celle-ci (par exemple sur 7 à 8 microns de profondeur pour une couche épitaxiale de 15 microns).

La localisation de ces régions est la suivante :

1°- là où on désire réaliser des transistors MOS à canal N à faible tenue en tension (MOS N BT) notamment pour les fonctions logiques du circuit, on forme une région P 20 qui constitue un caisson fermé dans lequel se situera la totalité d'un transistor MOS à canal N (ou même de plusieurs), c'est-à-dire à la fois la région de source, la région de drain et la région de canal, cette dernière étant constituée par la partie superficielle de la région 20 de type P.

2°- là où on désire réaliser des transistors MOS à canal N à tenue en tension élevée (MOS N HT), par exemple pour des étages de sortie, on forme une région P<sup>-</sup> 22 à l'intérieur de laquelle on diffusera ultérieurement, pour chaque transistor, une seule région

N<sup>+</sup> fortement dopée et moins profonde que la région 22, pour constituer la source du transistor, le canal étant constitué par une portion de cette région 22 (d'où la même tension de seuil pour le NMOS HT et le NMOS BT).

.3°- là où on désire réaliser des transistors MOS haute tension à canal P, on forme une région P<sup>-</sup> 24 à l'intérieur de laquelle on diffusera ultérieurement, pour chaque transistor, une seule région de type P<sup>+</sup> fortement dopée et moins profonde que la région 24, pour constituer le drain du transistor, le canal étant constitué par une portion de la couche épitaxiale 16 de type N.

5

10

15

20

25

30

4°- si l'isolement entre zones actives se fait par jonction (murs d'isolement de type P comme c'est le cas dans l'exemple décrit), on formera une région P 26 à l'endroit de ces murs d'isolement, c'est-à-dire à l'aplomb de chacune des régions diffusées 14, de telle manière que chaque région 14 rejoigne une région 26 correspondante pour compléter le mur d'isolement qui traverse alors la totalité de l'épaisseur de la couche épitaxiale 16.

Ces différentes régions de type P sont formées simultanément par implantation ionique localisée (avec une résine de masquage appropriée déposée et gravée selon un motif correspondant aux régions à former). L'impureté implantée est de préférence du bore avec une dose qui peut-être de l'ordre de 1,5 x 10 13 atomes/cm². Cette implantation est suivie d'un traitement thermique de diffusion pour que les régions P atteignent une profondeur suffisante (dictée essentiellement par la hauteur désirée pour les caissons contenant les transistors MOS à canal N). A titre d'exemple, la concentration superficielle en impuretés de type P dans les régions P devient de l'ordre de 10 16 atomes/cm³ en fin de diffusion.

L'étape suivante consiste à former, par un procédé d'oxydation localisée classique, des régions d'oxyde de silicium épais entourant les zones actives, par exemple entourant chaque transistor MOS.

Ces régions d'oxyde épais serviront notamment de support aux interconnexions métalliques du circuit.

Pour cela, on dépose une couche de nitrure de silicium 28 que l'on grave pour l'éliminer là où on veut faire croître l'oxyde épais; on effectue une implantation d'impuretés de type N (arsenic) à certains endroits délimités par un masque de résine, puis une implantation de type P (bore) à d'autres endroits délimités par un autre masque de résine. Ces implantations dites "de champ", situées ultérieurement sous l'oxyde épais, sont destinées à éviter la mise en conduction des transistors MOS parasites formés sous l'oxyde épais; ces implantations sont classiques et n'ont pas été représentées pour ne pas surcharger les figures. La figure 4 montre la structure intégrée à ce stade de la fabrication.

5

10

15

20.

25

30

On effectue alors un traitement thermique oxydant qui produit la croissance de l'oxyde épais là où il n'y a pas de nitrure après quoi on retire le nitrure. On peut noter que pendant ce traitement thermique se produit une diffusion des impuretés implantées dans les régions P<sup>-</sup> (20, 22, 24, 26)

La figure 5 représente l'état de la structure à la fin de cette étape, avec des zones d'oxyde épais 30 à divers endroits, et plus précisément à des endroits où l'on désire éviter qu'une interconnection métallique ou en silicium polyscristallin, ne passe à proximité immédiate de la surface semiconductrice et n'induise par effet de champ un canal (ou couche d'inversion) indésirable.

Par exemple, une région d'oxyde épais 30 est particulièrement désirable entre la région de drain et la région de canal des transistors MOS haute tension.

En ce qui concerne les transistors bipolaires éventuellement présents, on peut prévoir une région d'oxyde épais 30 entourant le puits d'accès 18 et la région de base de ces transistors.

L'étape suivante consiste à former uniformément sur toutes les surfaces dénudées de silicium monocristallin, entre les régions d'oxyde épais 30, une couche mince d'oxyde de silicium destinée à former l'oxyde de grille des transistors MOS. Cette couche, 32, est formée par oxydation thermique de la tranche semiconductrice.

Après cela, on dépose uniformément, par décomposition chimique en phase gazeuse et à basse pression (à partir de silane), une couche uniforme 34 de silicium polycristallin, de quelques milliers d'angströms (figure 6).

Cette couche est dopée soit "in situ", c'est -à-dire pendant son dépôt, soit après le dépôt, par diffusion de phosphore par exemple (prédépôt de POCl<sub>3</sub>), pour obtenir une conductivité suffisante du silicium polycristallin.

5

10

15

20

25

30

On procède alors à la gravure du silicium polycristallin et de l'oxyde mince, à l'aide d'un plasma de CF<sub>4</sub> par exemple et d'un masque de résine, pour définir d'une part les grilles des différents transistors MOS basse et haute tension, et d'autre part éventuellement un certain nombre d'interconnexions en silicium polycristallin.

La figure 7 représente la structure intégrée à ce stade de fabrication, après enlèvement du masque de résine.

Pour les transistors MOS basse tension à canal N, la grille, 29, reposant sur de l'oxyde mince, passe à l'intérieur de la surface d'un caisson 20 de type P et permet la formation d'une zone de source et d'une zone de drain dans ce caisson de part et d'autre de la grille; pour les transistors MOS basse tension à canal P, la grille 31 passe en dehors d'une région de type P et permet la formation d'une zone de source et d'une zone de drain de part et d'autre de la grille en dehors d'une région de type P; pour les transistors MOS haute tension à canal N, la grille 33 passe à cheval sur la frontière entre une région 22 de type P et la couche épitaxiale, et elle permet la formation d'une zone de source dans cette région 22 d'un côté de la grille, d'une zone de drain en dehors de cette région 22 de l'autre côté de la grille, et d'une zone de canal dans la région 22 sous la grille; enfin, pour les transistors MOS haute tension à canal P, la grille 35 passe à cheval sur la frontière entre la couche épitaxiale et une région 24 de type P, et elle permet la formation d'une zone de source dans la couche épitaxiale en dehors de cette région 24 d'un côté de la grille, d'une zone de drain dans la région 24 de l'autre côté de la grille et d'une zone de canal dans la couche épitaxiale en dehors de la région 24, sous la grille.

Le silicium polycristallin qui subsiste sert alors de masque d'autoalignement pour les étapes d'implantation ionique qui suivent.

5

10

15

20

25

30

La première implantation est une implantation d'impuretés de type P à concentration élevée, destinée à former des régions de source et de drain de type P<sup>+</sup> des transistors MOS à canal P ainsi que les régions de base des transistors bipolaires NPN s'il y a lieu. Pour cela, on dépose et on grave une couche de résine qui masque les zones qui ne doivent pas subir d'implantation de type P<sup>+</sup>, à savoir l'ensemble des transistors MOS à canal N, haute ou basse tension, et le puits d'accès 18 du collecteur des transistors NPN. Pour les transistors MOS à canal P non masqués par la résine, ce sont les régions d'oxyde épais et les grilles de silicium polycristallin qui servent de masque délimitant précisément les régions implantées de type P<sup>+</sup>. L'implantation est effectuée par exemple avec du bore.

Ces régions de type P+ sont respectivement (figure 8):

- des régions 36, constituant le drain de transistors MOS basse tension à canal P, implantées directement dans la couche épitaxiale 16 de type N entre une grille 31 et une région d'oxyde épais 30.

- des régions 38 constituant la source de ces mêmes transistors, également implantées dans la couche épitaxiale de type N entre une grille 31 et de l'oxyde épais 30 ;

- des régions 40 constituant le drain de transistors MOS haute tension à canal P; ces régions 40 sont implantées à l'intérieur des régions 24 de type P, et sont moins profondes qu'elles; on notera d'autre part qu'une distance relativement importante, mais quand même inférieure à la profondeur de la région 24, sépare le bord de la région 40 (du côté du canal) de la région de canal 42 proprement dite; ce qu'on appelle ici région de canal 42 est la région de type N qui est recouverte par la grille de transistor ou plus précisément par la portion de grille qui n'est séparée de la surface semiconductrice

que par une couche d'oxyde mince 32 et qui peut donc contrôler directement la formation d'un canal.

- des régions 44 constituant la source des transistors MOS haute tension à canal P; ces régions sont implantées dans la couche épitaxiale entre la grille 35 et une zone d'oxyde épais,

5

10

15

20

30

- éventuellement des régions 46 constituant la base des transistors bipolaires NPN.

On élimine alors la résine de masquage utilisée pendant l'implantation de type P<sup>+</sup> et l'on effectue un recuit. On dépose et on grave une autre couche de résine en vue d'une implantation (ou diffusion) de type N<sup>+</sup>; cette couche de résine masque les transistors qui ne doivent pas subir cette implantation, à savoir les transistors MOS à canal P (basse tension ou haute tension) et la région de base des transistors NPN. Pour les transistors non masqués, l'oxyde épais 30 et les régions de silicium polycristallin servent de masque délimitant précisément les régions implantées de type N<sup>+</sup>; l'implantation peut être effectuée avec de l'arsenic; une diffusion d'arsenic en ampoule est aussi possible.

Ces régions de type N<sup>+</sup> sont moins profondes que les régions de type P<sup>+</sup> et sont respectivement (figure 8)

- des régions 48 de drain des transistors MOS basse tension à canal N, implantées dans la région 20 de type P entre une grille 29 et une zone d'oxyde épais;

- des régions 50 de source de ces transistors, également 25 implantées dans la région 20 entre une grille 29 et une zone d'oxyde épais;

- des régions 52 de drain des transistors MOS haute tension à canal N, implantées directement dans la couche épitaxiale originelle de type N; ces régions sont espacées, d'une distance relativement importante mais inférieure à l'épaisseur de la coucxhe épitaxiale, de la région de canal proprement dite 54 de ces transistors, c'est-à-dire de la région de type P directement recouverte (à travers de l'oxyde mince 32) par une grille de silicium polycristallin 33. Sur cette

distance, la couche épitaxiale est surmontée d'une zone d'oxyde épais 30. Dans ces conditions, les régions 52 sont entièrement délimitées par de l'oxyde épais 30.

- des régions 56 diffusées dans les régions 22 et constituant les régions de source de transistors MOS haute tension à canal N, l'espace entre le bord d'une région 56 et le bord de la région 22 dans laquelle elle se trouve constituant la région de canal 54 de ces transistors; les régions 56 sont délimitées par les grilles 33 et des zones d'oxyde épais 30.

5

10

15

20

25

30

- éventuellement des régions 58 constituant l'émetteur de transistors bipolaires NPN verticaux, ces régions étant diffusées à l'intérieur des régions de base 46. Le puits d'accès 18 à la couche enterrée peut également subir cette opération d'implantation peu profonde de type N<sup>†</sup>.

Le procédé de fabrication se termine par des étapes classiques non représentées qui sont : un dépôt en phase gazeuse d'une couche isolante d'oxyde de silicium, un fluage de cette couche, une gravure pour ouvrir des contacts, un dépôt métallique (aluminium), une gravure de l'aluminium pour définir un motif d'interconnexions, un dépôt d'une couche isolante de passivation, une gravure de plots de contact pour la connexion aux broches du boîtier, et une encapsulation.

Dans l'exemple de réalisation qui a été décrit, les caissons 20 de type P contenant les transistors MOS basse tension à canal N sont séparés du substrat par une épaisseur de couche épitaxiale de type N. Cependant, on pourrait prévoir qu'une zone 14 de type P a été diffusée avant la croissance épitaxiale à l'endroit du caisson, de sorte que cette zone remonte ensuite jusqu'au caisson qui constitue alors à la fois un caisson de MOS N basse tension et un mur d'isolement. En reliant ainsi le caisson au substrat, on évite l'apparition d'un phénomène de "latch up", c'est-à-dire la formation d'un thyristor parasite NPNP.

Le procédé qui a été décrit est parfaitement compatible avec la formation de transistors bipolaires PNP latéraux (émetteur et collecteur formés en même temps que le drain des transistors MOS à canal P, base formée par la couche épitaxiale).

Enfin, on peut envisager de réaliser, si le substrat de départ est de type N<sup>+</sup>, un élément de puissance qui serait ce qu'on appelle un DMOS vertical, c'est-à-dire un MOS à canal N diffusé dont le drain est constitué par la face arrière N<sup>+</sup> du substrat, la source est constituée par des zones N<sup>+</sup> comme les sources des transistors MOS basse tension à canal N, et la région de canal est diffusée localement avec la diffusion de caisson de type P<sup>-</sup> des transistors MOS basse tension à canal N.

## REVENDICATIONS

- 1. Structure de circuit intégré incorporant des transistors MOS basse tension à canal N et à canal P et des transistors MOS haute tension à canal N et à canal P, comprenant :

- une pastille semiconductrice constituée d'un substrat (10) recouvert d'une couche épitaxiale (16) peu dopée de type N;

- des première régions (20) de type P, peu dopées, s'étendant à partir de la surface de la pastille semiconductrice sur une partie de la profondeur de la couche épitaxiale, ces régions (20) constituant des caissons dans lesquels sont formés la source, le drain et le canal de transistors MOS basse tension à canal N;

- des régions de type P<sup>+</sup> fortement dopées (36, 38, 40, 44), moins profondes que les régions de type P<sup>-</sup>, s'étendant à partir de la surface de la pastille semiconductrice et constituent la source et le drain des transistors MOS à canal P;

- des régions de type N<sup>+</sup> fortement dopées (48, 50, 52, 56), moins profondes que les régions de type P<sup>-</sup>, stétendant à partir de la surface de la pastille semiconductrice et constituant la source et le drain des transistors MOS à canal N,

- caractérisée en ce qu'il est prévu en outre

5

10

20

- au moins une seconde région (22) de type P, de même profil de concentration que les premières régions et s'étendant jusqu'à la même profondeur, cette seconde région entourant une région de source (56) de type N<sup>+</sup> et constituant une région de canal (54) d'un transistor MOS haute tension à canal N, transistor qui comporte par ailleurs une région de drain (52) de type N<sup>+</sup> située en dehors de la seconde région (22) et écartée d'elle de telle manière qu'il existe une zone de couche épitaxiale de type N peu dopée, non directement contrôlée par la grille du transistor, entre la région de drain et la seconde région (22),

- au moins une troisième région (24) de type P, de même profil de concentration que les premières et secondes régions et s'étendant jusqu'à la même profondeur, cette troisième région

entourant une région de drain (40) de type P<sup>+</sup> d'un transistor MOS haute tension à canal P dont la région de canal est constituée par une région (42) de couche épitaxiale de type N peu dopée, adjacente à la troisième région (24), la région de drain (40) de type P<sup>+</sup> de ce transistor étant écartée de la région de canal (42) de telle manière qu'il existe entre elles une zone de la troisième région (24) non directement contrôlée par la grille (35) du transistor, et la région de source (40) de ce transistor étant située en dehors de la troisième région.

5

20

- 2. Structure selon la revendication 1, caractérisée en ce qu'elle comporte des murs d'isolement de type P traversant la couche épitaxiale du haut en bas, la partie supérieure de ces murs étant constituée par des régions (26) de type P formées par la même opération que les premières, secondes et troisièmes régions.

- 3. Procédé de fabrication de circuits intégrés incorporant des transistors MOS à canal N et à canal P dont certains ont une tenue en tension améliorée, caractérisé en ce que

- a) on effectue une implantation ionique localisée d'impuretés de type P à faible concentration dans une couche épitaxiale peu dopée de type N, simultanément dans des régions qui sont

- des première régions (20) constituant des caissons destinés à enfermer source (50), drain (48) et canal de certains transistors MOS à canal N dits transistors MOS N basse tension;

- des secondes régions (22) destinées à enfermer uniquement la source (56) et le canal (54) de transistors MOS à canal N dits transistors MOS N haute tension;

- des troisièmes régions (24) destinées à enfermer uniquement le drain (40) de transistors MOS à canal P dits transistors MOS P haute tension ;

- 30 b) on forme et on grave une couche d'oxyde mince (32) surmontée d'une couche de silicium polycristallin (34) pour former :

- des grilles passant à l'intérieur des premières régions en permettant la formation dans ces régions d'une zone de source (50) et d'une zone de drain (48) de part et d'autre de la grille;

- des grilles venant à cheval sur la frontière entre une deuxième région (22) de type P et la couche épitaxiale (16) de type N, en permettant la formation d'une zone de source (56) dans la deuxième région d'un côté de la grille, d'une zone de drain (52) dans la couche épitaxiale de l'autre côté de la grille, et d'une zone de canal (54) sous la grille dans la deuxième région;

5

10

15

- des grilles venant à cheval sur la frontière entre une troisième région (24) de type P et la couche épitaxiale (16) de type N, en permettant la formation d'une zone de source (44) dans la couche épitaxiale d'un côté de la grille, d'une zone de drain (40) dans la troisième région de l'autre côté de la grille, et d'une zone de canal (42) dans la couche épitaxiale sous la grille;

- c) on implante localement d'une part une impureté de type P et d'autre part une impureté de type N pour former des régions (36, 38, 40, 44) de type P<sup>+</sup> constituant la source et le drain des transistors à canal P et des régions (48, 50, 52, 56) de type N<sup>+</sup> constituant la source et le drain des transistors à canal N, les régions de drain des transistors MOS haute tension étant écartées latéralement des régions contrôlées par la grille de ces transistors.

1/4

ቢ

## RAPPORT DE RECHERCHE EUROPEENNE

Numero de la demande

EP 85 40 1860

| DOCUMENTS CONSIDERES COMME PERTINENTS  Citation du document avec indication, en cas de besoin. Revendication |                                                                                                                                                                                               |                                                                                   | CLASSEMENT DE LA                                                                                          |                                                |

|--------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|------------------------------------------------|

| atégorie                                                                                                     | des partie                                                                                                                                                                                    | s pertinentes                                                                     | concernée                                                                                                 | DEMANDE (Int. Cl.4)                            |

| A                                                                                                            | FR-A-2 449 334<br>INSTRUMENTS)<br>* En entier *                                                                                                                                               | (TEXAS                                                                            | 1-3                                                                                                       | H 01 L 27/08<br>H 01 L 21/82<br>H 01 L 29/78   |

| A                                                                                                            | INTERNATIONAL EL MEETING 1982, 13 1982, pages 77-8 Francisco, US; Val.: "Integrated voltage CMOS tec                                                                                          | -15 décembre<br>60, San<br>7. RUMENNIK et<br>8 high and low                       |                                                                                                           |                                                |

| A                                                                                                            | EP-A-0 070 101                                                                                                                                                                                | (XEROX CORP.)                                                                     |                                                                                                           |                                                |

| A                                                                                                            | FR-A-2 464 561                                                                                                                                                                                | (THOMSON-CSF)                                                                     |                                                                                                           |                                                |

| A                                                                                                            | EP-A-0 020 164 (XEROX CORP.)                                                                                                                                                                  |                                                                                   |                                                                                                           | DOMAINES TECHNIQUES<br>RECHERCHES (Int. Cl. 4) |

| A                                                                                                            | US-A-4 300 150 CORP.)                                                                                                                                                                         | <br>(N.A. PHILIPS                                                                 |                                                                                                           | H 01 L                                         |

|                                                                                                              |                                                                                                                                                                                               |                                                                                   |                                                                                                           |                                                |

|                                                                                                              |                                                                                                                                                                                               |                                                                                   |                                                                                                           |                                                |

|                                                                                                              |                                                                                                                                                                                               |                                                                                   |                                                                                                           |                                                |

|                                                                                                              |                                                                                                                                                                                               |                                                                                   |                                                                                                           |                                                |

| L                                                                                                            | e présent rapport de recherche a été é  Lieu de la recherche  LA HAYE                                                                                                                         | tabli pour toutes les revendications  Date d'achèvement de la rechert  07-01-1985 | che PELSE                                                                                                 | Examinateur<br>ERS L.                          |

|                                                                                                              |                                                                                                                                                                                               |                                                                                   |                                                                                                           |                                                |

| Y : p                                                                                                        | CATEGORIE DES DOCUMEN<br>particulièrement pertinent à lui sei<br>particulièrement pertinent en com<br>jutre document de la même catégi<br>prière-plan technologique<br>livulgation non-écrite | E : docum<br>date de<br>binaison avec un D : cité da                              | ou principe à la ba<br>ent de brevet antér<br>e dépôt ou après ce<br>ns la demande<br>ur d'autres raisons | rieur, mais publié à la<br>ette date           |