11) Numéro de publication:

0 202 166 **A1**

## (12)

### **DEMANDE DE BREVET EUROPEEN**

21) Numéro de dépôt: 86401008.7

51 Int. Cl.4: G09G 1/00

(22) Date de dépôt: 12.05.86

Priorité: 15.05.85 FR 8507412

(43) Date de publication de la demande: 20.11.86 Bulletin 86/47

Etats contractants désignés: DE GB

- (71) Demandeur: OlDonnell, Ciaran 30, rue de la Martinière F-91570 Bièvres(FR)

- 2 Inventeur: OlDonnell, Ciaran 30, rue de la Martinière F-91570 Bièvres(FR)

- (74) Mandataire: Mongrédien, André et al c/o SOCIETE DE PROTECTION DES INVENTIONS 25, rue de Ponthieu F-75008 Paris(FR)

## (54) Circuit de mémoire d'image virtuelle permettant le multifen trage.

© Circuit de mémoire d'image virtuelle permettant le multifenêtrage.

Il comprend une mémoire d'image (4) bidimensionnelle organisée en N pavés élémentaires où N est un nombre entier, lesdits pavés étant rectangulaires et identiques, une table d'indirection (6) constituée d'une mémoire vive contenant une suite de N pointeurs, chaque pointeur notant l'adresse de début d'un pavé de la mémoire d'image, un générateur vidéo (10) pour délivrer un signal vidéo correspondant au contenu de n pavés de la mémoire d'image, où n ≤ N, pour l'affichage sur un écran d'une image composée des n pavés organisés enmatrice, l'adressage desdits pavés étant effectué par le générateur vidéo à travers la table d'indirection, une interface -(12) pour accéder en lecture ou en écriture à la mémoire d'image et à la table d'indirection, l'adressage de la mémoire étant effectué à travers la table d'indirection, le circuit comprenant en outre des bus de données, d'adresse et de commande et un moyen de séquencement.

15

La présente invention a pour objet un circuit de mémoire d'image virtuelle permettant le multi-fenêtrage. Le circuit de l'invention est associé à un écran à adressage par point (en terminologie anglosaxonne "raster screen" ou "bitmap screen") qui utilise un système de coordonnées à deux dimensions.

Le circuit de l'invention comprend une mémoire d'image bidimensionnelle dont l'adressage est réalisé suivant un système de coordonnées semblable à celui utilisé pour l'adressage de l'écran. Cette mémoire a une taille supérieure à la taille de l'écran. Elle peut ainsi mémoriser un ensemble d'images dont quelques unes seulement sont visualisées, en totalité ou en partie, à un instant donné.

La visualisation. ou affichage, d'une image se fait à travers une fenêtre. On définit une fenêtre comme étant une surface de dimension finie et de forme quelconque d'un espace d'affichage bidimensionnel. L'écran est considéré comme une fenêtre rectangulaire sur cette espace d'affichage. On peut définir sur l'espace d'affichage un nombre quelconque de fenêtres, celles-ci pouvant être disjointes, ou se recouvrir, partiellement ou totalement. Ces fenêtres constituent des zones sur lesquelles sont projetées des images contenues dans la mémoire d'image.

L'invention concerne un circuit de mémoire d'image virtuelle. Le qualificatif de "virtuelle" fait référence au fait qu'une image de la mémoire d'image peut être projetée sur une fenêtre disjointe de la fenêtre représentée par l'écran, et ainsi ne pas être visualisée.

Par abus de langage, le terme de fenêtre désigne dans la suite du texte aussi bien une surface finie de l'espace d'affichage que l'image projetée sur cette surface.

Une première méthode de multifenêtrage est décrite dans l'article "WINDX-Windows for the UNIX environment" de Peter Colins présenté à USENIX conference, Salt Lake City, 1984. Dans ce système, la mémoire d'image est divisée en cellules rectangulaires de 8 x 16 points élémentaires d'image. Une page est définie comme un ensemble rectangulaire de cellules. Le contenu d'une page est visualisé à travers une fenêtre d'écran, qui fait correspondre une région rectangulaire de la page à une région rectangulaire de l'écran. Plusieurs fenêtres peuvent être créées simultanément sur l'écran.

Chaque fenêtre est définie par un ensemble de pointeurs désignant des cellules dans une page de la mémoire d'image. L'adressage de la mémoire d'image par le générateur vidéo délivrant le signal vidéo à l'écran est donc réalisé par l'intermédiaire d'une table d'indirection contenant lesdits pointeurs. Cette table d'indirection permet de modifier rapidement une image affichée sur l'écran. En effet, la modification de l'image affichée dans une fenêtre de l'écran est obtenue sans aucun déplacement physique de cellules dans la mémoire d'image, mais simplement par une modification du contenu des pointeurs de la table d'indirection associée à cette fenêtre.

Cette table d indirection permet en outre une meilleure gestion de la mémoire d'image car les zones blanches, en général importantes, que contient une image visualisée, peuvent être représentées dans la mémoire d'image par une seule cellule désignée par chacun des pointeurs qui correspondent à des cellules blanches de l'écran.

L'inconvénient principal de ce système est que le processeur qui gère les accès, en écriture ou en lecture, à la mémoire d'image ne passe pas par la table d'indirection mais adresse au contraire directement la mémoire d'image.

Cette dissymétrie n'est pas satisfaisante car elle complique le traitement de certaines fonctions. Considérons par exemple la fonction de défilement (en terminologie anglo-saxonne "scroll"). Pour réaliser ce défilement sur une image visualisée, c'est-à-dire projetée sur une fenêtre de l'écran, il suffit de mettre à jour le contenu des pointeurs désignant les cellules composant cette image visualisée. Cette opération est rapide et ne nécessite aucun déplacement physique du contenu des cellules de la mémoire. Au contraire, pour réaliser un défilement de la mémoire vue du processeur, il faut déplacer physiquement le contenu des cellules de la mémoire. Ce traitement présente l'inconvénient d'être long et compliqué.

Cette structure présente également le défaut que le processeur ne connaît pas directement l'image visualisée mais doit lire le contenu de la table des pointeurs pour connaître explicitement l'adresse des cellules de la mémoire composant cette image visualisée. Cette étape nécessaire de lecture limite considérablement la rapidité de modification du contenu de l'écran.

On connaît également un circuit de mémoire virtuelle comportant une mémoire d'image et une table d'indirection dans lequel ladite table d'indirection est utilisée uniquement par le processeur. Un

tel circuit de mémoire virtuelle est utilisé dans notamment certains ordinateurs de la Société RID-GE COMPUTERS. L'utilisation d'une table d'indirection par le processeur accédant en lecture et en écriture à la mémoire est donc connue. Cette table d'indirection constitue l'unité de gestion de la mémoire qui réalise une traduction automatique des adresses utilisée dans la plupart des processeurs avancés.

Dans ce circuit, la mémoire d'image accédée par le processeur à travers la table d'indirection est recopiée dans une seconde mémoire qui est adressée uniquement par le générateur vidéo.

Le multifenêtrage n'est pas prévu dans ce circuit. Il serait d'ailleurs délicat à implanter. En effet, les blocs traduits par le mécanisme d'indirection sont des blocs de taille fixe dans une dimension - (page), ce qui correspond à l'utilisation d'une mémoire virtuelle gérant une mémoire de programmes. Chaque élément adressé par cette table d'indirection correspond un certain nombre de lignes entières sur l'écran. Pour réaliser un multifenêtrage,il est nécessaire d'avoir un découpage bidimensionnel, c'est-à-dire un découpage où les dimensions d'un pavé dans les dimensions X et Y sont inférieures à celle d'une ligne de caractères sur l'écran.

Le circuit décrit dans cet article présente un inconvénient analogue à celui du circuit décrit dans l'article précédent, à savoir que la différence entre les modes d'accès du processeur et du générateur vidéo à la mémoire d'image ne permet pas une gestion rapide et efficace par le processeur de l'image affichée sur l'écran.

On connaît également un circuit de mémoire d'image dans lequel l'adressage de la mémoire d'image se fait toujours à travers une table d'indirection. Le processeur et le générateur vidéo accèdent alors à la mémoire d'image de manière symétrique.

Dans ce circuit, la mémoire d'image contient uniquement l'image visualisée et ne permet pas le multifenêtrage. Dans le cas où cette image a un nombre de lignes ou de colonnes qui n'est pas de la forme 2<sup>n</sup>, où n est un entier, un adressage direct de la mémoire par le processeur se traduirait par un gaspillage important de cette mémoire.

Considérons par exemple un écran pouvant afficher 80 lignes de 25 caractères, chaque caractère ayant une taille de 9 x 14 points. La résolution de cet écran est de 720 lignes (80 x 9) et de 350 colonnes (25 x 14). Pour adresser un point d'image de cet écran, il faut donc 10 lignes d'a-

dresses pour sélectionner une des 720 lignes de l'image ( $2^{10} = 1024 > 720$ ) et 9 lignes d'adresses pour sélectionner une des 350 colonnes de l'image ( $2^9 = 512 > 350$ ).

L'affichage d'une image de 80 × 9 × 25 × 14, ou 252000, points nécessite ainsi une mémoire d'image de 1024 × 512, ou 524888 points. Dans ce cas particulier, un adressage direct de la mémoire d'image se traduit par un gaspillage très important de la mémoire puisque plus de la moitié de celle-ci est inutilisée.

La table d'indirection utilisée dans ce circuit connu a pour seul but de limiter le gaspillage de la mémoire en réalisant un transcodage d'adresse. Cette table d'indirection est constituée d'une mémoire morte (ROM) et ne permet donc pas de modifier l'image visualisée par une mise à jour de cette table.

L'invention a pour objet un circuit de mémoire d'image virtuelle palliant notamment les inconvénients des circuits selon l'art antérieur. Une première caractéristique de l'invention réside dans l'adressage symétrique de la mémoire d'image par le processeur et le générateur vidéo. Ceci permet de simplifier la gestion de la mémoire d'image et notamment toute modification par le processeur de l'image affichée sur l'écran grâce à l'identité de l'adressage de la mémoire par le générateur vidéo et le processeur.

L'utilisation d'une table d'indirection constituée d'une mémoire vive constitue la deuxième caractéristique du circuit de l'invention. Cette table d'indirection contient un ensemble de pointeurs dési gnant chacun une zone de la mémoire d'image. La possibilité de modifier le contenu de cette table d'indirection permet d'une part au processeur de créer de multiples fenêtres et d'autre part de modifier les fenêtres, visibles ou non visibles sur l'écran, ou de déplacer les fenêtres visibles sur l'écran, sans avoir recours à un déplacement physique du contenu de la mémoire d'image. Cette table d'indirection permet également de limiter le gaspillage de la mémoire lorsque le nombre de lignes ou de colonnes de l'image affectée n'est pas une puissance de 2.

De manière précise, l'invention a pour objet un circuit de mémoire d'image virtuelle comprenant:

-une mémoire bidimensionnelle organisée en N pavés élémentaires, ou N est un nombre entier, lesdits pavés étant rectangulaires et identiques,

-une table d'indirection constituée d'une mémoire vive contenant une suite de N pointeurs, chaque pointeur notant l'adresse de début d'un pavé de la mémoire,

-un générateur vidéo pour délivrer un signal vidéo correspondant au contenu de n pavés, ou  $n \le N$ , pour l'affichage d'une image composée desdits n pavés organisés en matrice, l'adressage desdits n pavés par le générateur vidéo étant effectué à travers la table d'indirection, et

-une interface pour accéder en lecture et en écriture à la mémoire et à la table d'indirection, l'adressage de la mémoire étant effectué à travers la table d'indirection.

L'interface reçoit des ordres de lecture ou d'écriture d'un processeur extérieur. Elle constitue notamment un tampon pour stocker les signaux délivrés par le processeur tant que l'accès à la mémoire d'image ou à la table d'indirection n'est pas autorisé, par exemple lorsque l'accès est demandé par le générateur vidéo. Elle peut comprendre une unité de gestion de la mémoire adressable par le processeur (mémoire d'image et mémoire centrale).

Selon un mode de réalisation particulier du circuit de l'invention, les n pavés élémentaires visualisés sur l'écran correspondent aux n premiers pointeurs de la table d'indirection. Le générateur vidéo n'adresse que ces n pointeurs. L'adressage est réalisé périodiquement pour le rafraîchissement de l'image.

Par n premiers pointeurs de la table d'indirection, on entend les pointeurs contenus dans les n adresses les plus basses de la table d'indirection.

De manière préférée, le circuit de l'invention comprend en outre un moyen disposé entre, d'une part, le générateur vidéo et l'interface et, d'autre part la table d'indirection, ledit moyen recevant les adresses délivrées par ledit générateur vidéo et ladite interface et décomposant chaque adresse en un partie haute représentant l'adresse de début d'un pavé de la mémoire d'image et en une partie basse représentant un index pour désigner un mot de ce pavé, la partie haute d'une adresse étant reçue par la table d'indirection et la partie basse par la mémoire d'image.

Selon un mode de réalisation préféré, le moyen disposé d'une part entre le générateur vidéo et l'interface et d'autre part la table d'indirection comprend un premier registre d'adresses ligne et un premier registre d'adresses colonne pour recevoir les adresses délivrées par ledit générateur vidéo, un second registre d'adresses ligne et un second registre d'adresses colonne pour recevoir les adresses délivrées par ladite interface et des moyens pour concaténer les parties hautes des adresses délivrées par un registre d'adresses ligne et un registre d'adresses colonne et pour concaténer les parties basses des adresses

délivrées par un registre d'adresses ligne et un registre d'adresses colonne, l'adresse résultant de la concaténation des parties hautes des adresses étant appliquée à la table d'indirection et l'adresse résultant de la concaténation des parties basses des adresses étant appliquée à la mémoire d'image.

Les caractéristiques et avantages de l'invention ressortiront mieux de la description qui va suivre, donnée à titre illustratif mais non limitatif, en référence aux dessins annexés, sur lesquels :

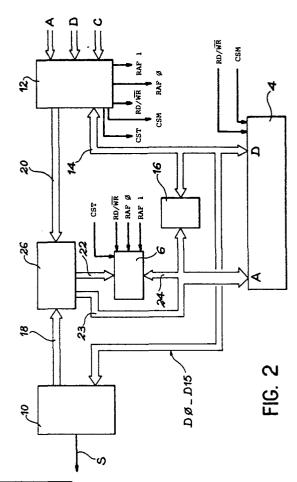

-la figure 1 illustre la correspondance entre un pavé de la mémoire d'image et une zone de l'écran de visualisation par l'intermédiaire des pointeurs de la table d'indirection,

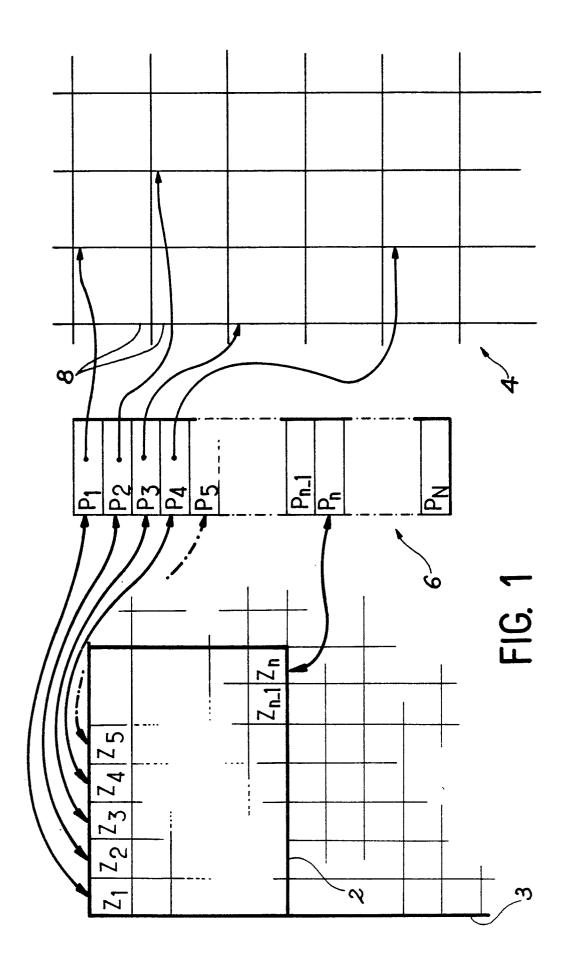

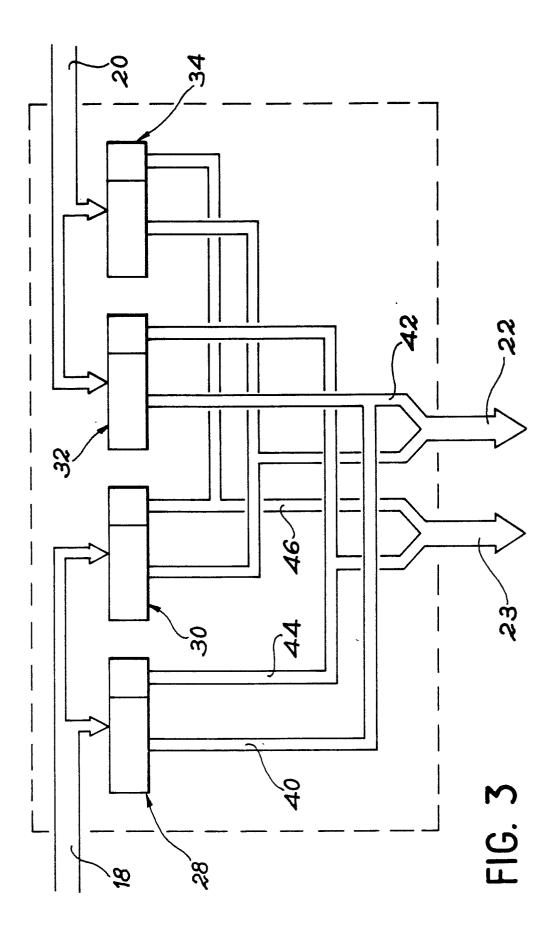

-la figure 2 représente schématiquement un mode de réalisation du circuit de l'invention,

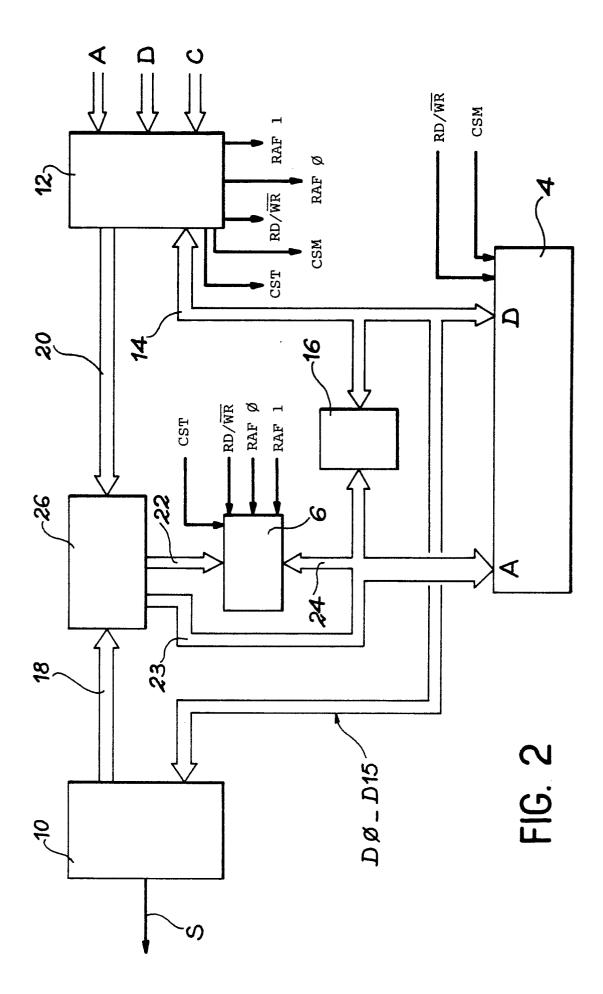

-la figure 3 représente un mode de réalisation du moyen 26 du circuit de la figure 2,

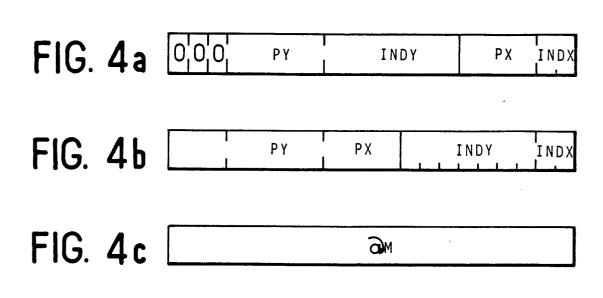

-les figures 4a, 4b et 4c illustrent respectivement les formats d'une adresse virtuelle délivrée par le générateur vidéo, de l'adresse correspondante délivrée par le moyen 26 et de l'adresse reçue par la mémoire d'image,

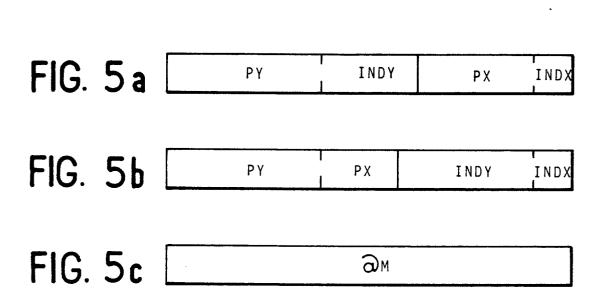

-les figures 5a, 5b et 5c illustrent respectivement les formats d'une adresse virtuelle délivrée par l'interface, de l'adresse correspondante délivrée par le moyen 26 et de l'adresse reçue par la mémoire d'image, et

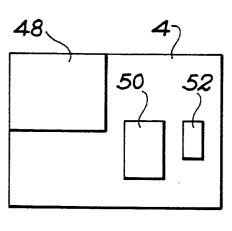

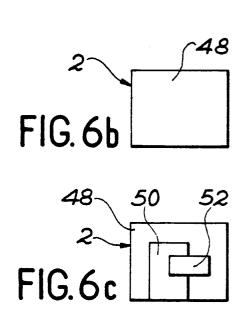

les figures 6a, 6b et 6c illustrent le multifenêtrage au moyen du circuit de l'invention.

La figure 1 illustre la correspondance entre les pavés élémentaires de la mémoire d'image et les zones rectangulaires de l'éçran. Cet écran 2 est com posé d'un ensemble de n zones rectangulaires identiques notées Z<sub>1</sub>, Z<sub>2</sub>, ..., Z<sub>n</sub> La taille d'une zone correspond à la taille d'un pavé élémentaire de la mémoire d'image.

L'écran 2 est un sous-ensemble d'un espace bidimensionnel 3 comportant N zones rectangulaires identiques ou N ≧ n. Les zones de cet espace qui ne sont pas affichées, c'est-à-dire qui ne correspondent pas à l'écran sont utilisées pour créer des fenêtres virtuelles. Un point de l'espace 3 est repéré par une adresse virtuelle.

55

La mémoire d'image 4 est composée d'un ensemble de pavés rectangulaires identiques 8. Cette mémoire d'image est de type bidimensionnel, c'est-à-dire que l'image mémorisée dans un pavé élémentaire est représentée de la même manière que lorsqu'elle est visualisée dans une zone de l'écran 2. Ceci signifie que deux points élémentaires se trouvant sur l'écran dans deux lignes successives et sur une même colonne, sont mémorisés dans la mémoire 4 dans deux lignes successives et dans une même colonne d'un pavé élémenlaire 8.

Cette structure bidimensionnelle présente l'avantage, sur une mémoire linéaire, de simplifier certaines fonctions telles que le défilement d'une image dans un pavé ou dans une fenêtre.

L'adressage de chaque pavé élémentaire 8 de la mémoire 4 est réalisé par un ensemble de pointeurs formant une table d'indirection 6. Chaque pointeur comporte deux champs d'adresses qui désignent les coordonnées du premier mot de la première ligne d'un pavé élémentaire.

Un ensemble de n pointeurs déterminés parmi les N pointeurs de la table d'indirection sont associés aux zones  $Z_1,\ Z_2,\ ...,\ Z_n$  de l'écran 2. Ces pointeurs sont par exemple les n premiers pointeurs de la table d'indirection, c'est-à-dire les pointeurs correspondant aux n premières adresses de cette table. Les autres pointeurs désignent des pavés élémentaires non visibles sur l'écran. La création, le déplacement ou l'effacement d'une fenêtre sur l'écran s'effectuent ainsi simplement par une mise à jour du contenu de la table d'indirection.

A titre d'exemple de réalisation, l'écran 2 peut être composé de 2304 lignes, de 1728 points d'image chacun. Il peut être découpé en 972 zones de 64x64 points d'image chacune, soit 36 rangées de 27 zones chacune. La taille de la mémoire est par exemple de 1024 Kmots de 16 bits chacun. chaque point d'image étant codé sur un bit. Cette mémoire est découpée en 4096 pavés élémentaires constitués chacun de 64 lignes de 4 mots. Dans ce mode de réalisation, la table d'indirection comporte 4096 adresses, chacune contenant un pointeur désignant un pavé élémentaire de la mémoire. Les 1152 premières adresses, par exemple, correspondent aux pavés élémentaires visualisés sur l'écran ; les autres pointeurs correspondent à la zone virtuelle contenant les fenêtres non visualisées.

On a représenté sur la figure 2 un dessin schématique d'un circuit de mémoire d'image virtuelle conforme à l'invention. Ce circuit comprend principalement la mémoire d'image 4, la table d'indirection 6, un générateur vidéo 10, une interface 12 et un moyen 26. Il comprend également un bus de données 14 auquel sont reliés la mémoire d'image 4, le générateur vidéo 10, l'interface 12 et, à travers un verrou 16, la table d'indirection 6. Il comprend enfin plusieurs bus d'adresses 18, 20, 22 et 24 reliant respectivement l'interface 12 au moyen 26, le générateur vidéo au moyen 26, le moyen 26 à la table d'indirection 6, et la table d'indirection 6 à la mémoire d'image 4.

Conformément à l'invention, l'adressage de la mémoire d'image 4 par le générateur vidéo 20 et l'interface 12 se fait par l'intermédiaire de la table d'indirection 6.

Le moyen 26 reçoit des adresses virtuelles délivrées par le générateur vidéo 10 et l'interface 12, c'est-à-dire des adresses exprimées selon l'espace bidimensionnel d'affichage. L'interface 12 délivre des adresses virtuelles désignant n'importe quel élément d'image de l'espace d'affichage. Au contraire, les adresses délivrées par le générateur vidéo ne peuvent désigner que les éléments d'image correspondant à l'écran, c'est-à-dire à une fenêtre déterminée de l'espace d'affichage.

Les adresses reçues par le moyen 26 sont décomposées en une adresse haute et une adresse basse, la première désignant un numéro de zone de l'espace d'affichage et la seconde désignant un mot dans cette zone. L'adresse haute est transmise, par le bus 22, à la table d'indirection 6 qui délivre à la mémoire d'image 4 l'adresse physique du pavé correspondant à cette zone. L'adresse basse est transmise directement à la mémoire d'image 4 par le bus 23 ; elle constitue un index d'adresse de la zone et du pavé.

On décrira un mode de réalisation du moyen 26 en référence à la figure 3. On va d'abord indiquer le fonctionnement du circuit de la figure 2 en mode rafraîchissement dans lequel l'accès à la mémoire d'image est réalisé par le générateur vidéo 10, et en mode traitement, dans lequel l'accès à la mémoire d'image est réalisé, en lecture et en écriture, par l'interface 12.

En mode rafraîchissement, le générateur vidéo 10 délivre successivement les adresses virtuelles des mots dont les coordonnées sont contenues dans les limites de l'écran. A chaque adresse virtuelle correspond, par la table d'indirection 6, une adresse physique de la mémoire d'image 4. Le mot contenu à cette adresse est reçu par le générateur vidéo 10 par le bus de données 14. Les mots ainsi reçus de la mémoire d'image sont ensuite émis sous forme d'un signal vidéo S vers un moyen de visualisation.

5

10

15

20

25

35

En mode traitement, l'interface 12 délivre une adresse virtuelle sur le bus d'adresse 20. Cette adresse virtuelle peut désigner un mot quelconque de l'espace d'affichage, correspondant à l'écran ou à une fenêtre non visualisée.

L'interface 12 peut également adresser la table d'indirection 6. La sélection de la mémoire d'image 4 ou de la table d'indirection 6 est assurée par des signaux de sélection CSM ou CST émis par l'interface 12.

Lorsque la mémoire d'image 4 est sélectionné" (signal CSM validé), l'interface 12 peut lire ou écrire dans la mémoire d'image, la transmission des données étant réalisée par le bus de données 14. Lorsque la table d'indirection 6 est sélectionnée (signal CST validé), l'adresse virtuelle délivrée par l'interface 12 sert à désigner un pointeur de la table d'indirection, la transmission des données étant réalisée par les bus 14 et 24, le verrou 16 étant passant.

La modification du contenu de la table d'indirection 6 par l'interface 12 permet de modifier l'organisation des fenêtres et notamment l'image visualisée sur l'écran très simplement, sans qu'il soit nécessaire de déplacer physiquement des données dans la mémoire d'image. De plus, le générateur vidéo 10 et l'interface 12 accédant la mémoire d'image de la même manière, une modification du contenu de la table d'indirection est transparente pour le générateur vidéo.

On a indiqué sur la figure 2 les principaux signaux de commande émis par l'interface 12. Ce sont CSM et CST pour sélectionner respectivement la mémoire d'image et la table d'indirection, RD/WR pour indiquer si l'accès est en lecture ou en écriture, RAF0 et RAF1 qui commande le remplacement du dernier mot adressé par le générateur vidéo respectivement par la valeur "0" ou la valeur "1".

Le processeur adresse la mémoire centrale et la mémoire d'image de manière classique par l'intermédiaire d'une unité de gestion de mémoire. La mémoire centrale contient des programmes et des données ; elle est unidimensionnelle. La mémoire d'image contient des éléments d'image ; elle est bidimensionnelle. L'accès aux deux mémoires n'est donc pas identique.

Dans le cas de la mémoire centrale, l'adressage par l'unité de gestion de mémoire est direct. Dans le cas de l'adressage de la mémoire d'image, il faut rendre l'adresse bidimensionnelle. Pour cela, il convient d'échanger les bits de rangs N,N+1,...,N+L+1 de l'adresse avec les bits de rangs M,M+1,...,M+L+1, où N, M et L sont tels que 2<sup>N</sup> est l'entier le plus proche, par valeur supérieure, de la longueur en mots d'une ligne sur

l'écran, 2<sup>M</sup> est la hauteur en lignes d'un pavé et 2 <sup>L</sup> est la longueur en mots d'un pavé. Par exemple, pour des pavés de 64 <sup>x</sup> 64 et des lignes comprenant 54 mots de 32 bits, on a N=5, M=6 et L=1.

Deux structures sont alors possibles selon que la mémoire centrale et la mémoire d'image sont deux zones d'un même circuit de mémoire ou selon qu'elles sont constituées de circuits indépendants.

Dans le premier cas, l'unité de gestion de mémoire est reliée directement au circuit de mémoire et un moyen de permutation conditionné est disposé entre le processeur et l'unité de gestion de mémoire. Ce moyen de permutation est conçu pour être transparent pour le signal d'adresse reçu ou pour échanger des bits de ce signal d'adresse comme on l'a indiqué plus haut.L'état du moyen de permutation peut êtrè commandé simplement par l'état d'un bit inutilisé de l'adresse virtuelle. Ce moyen de permutation peut être réalisé par deux multiplexeurs commandés simultanément dont le premier reçoit les bits de rangs N,N+1,...,N+L+1 sur une première entrée et les bits de rangs M,M+1,...,M+L+1 sur une seconde entrée, et dont le deuxième reçoit les bits de rang M,M+1,...,M+L+1 sur une première entrée et les bits N,N+1,...,N+L+1 sur une seconde entrée. Les autres bits d'adresse ne sont pas affectés par le moyen de permutation.

Dans ce mode de réalisation, l'interface 12 peut comprendre en série le moyen de permutation conditionné et l'unité de gestion de mémoire ; le bus d'adresse 20 est alors également relié directement à la mémoire centrale.

Dans le second cas, l'unité de gestion de mémoire est reliée en entrée directement au processeur. Sa sortie d'adresse est reliée directement à la mémoire centrale et est reliée à la mémoire d'image par un moyen opérant une permutation fixe entre les bits de rangs N,N+1,...,N+L+1 et les bits de rang M,M+1,...,M+L+1. Ce moyen de permutation peut n'être que virtuel, la permutation consistant seulement à modifier les connexions des lignes d'adresse du bus 20 sur les broches d'entrée du moyen 26.

Dans ce second mode de réalisation, l'interface 12 comprend uniquement une unité de gestion de mémoire. Le bus 20 est relié à la mémoire centrale sans permutation de lignes d'adresse et au moyen 26, pour l'adressage de la mémoire d'image, avec permutation de certaines lignes d'adresse.

La figure 3 illustre un mode de réalisation du moyen 26. Celui-ci comprend deux registres d'adresses 28 et 30 recevant les adresses virtuelles de ligne et de colonne délivrées par le générateur vidéo 10, et deux registres d'adresses 32 et 34

recevant les adresses virtuelles de ligne et de colonne délivrées par l'interface 12. Les adresses reçues par chaque registre comporte une partie haute et une partie basse.

Les parties hautes des adresses de ligne sont délivrées par le registre 28 ou par le registre 32 sur un bus d'adresse 40. De même les parties hautes des adresses de colonnes sont délivrées par le registre 30 ou par le registre 34 sur un bus d'adresse 42. Les adresses présentes sur ces bus 40, 42 sont concaténées pour constituer une adresse d'accès à la table d'indirection 6. Le bus d'adresse 22 résulte de la juxtaposition des bus d'adresse 40, 42

De la même manière, les parties basses des adresses de ligne sont délivrées par les registres 28 et 32 sur un bus d'adresses 44, et les parties basses des adresses de colonne sont délivrées par les registres 30 et 34 sur un bus d'adresse 46. Ces parties basses d'adresses de ligne et de colonne constituent un index pour désigner un mot du pavé de la mémoire sélectionné par les parties hautes des adresses de lignes et de colonnes. Le bus 23 délivrant cet index à la mémoire d'image 4 résulte de la juxtaposition des bus d'adresse 44, 46.

On a représenté respectivement sur les figures 4a à 4c et 5a à 5c les formats des adresses délivrées par l'interface et par le générateur vidéo.

A titre d'exemple, on a considéré une mémoire d'image de 4 Mo organisée en mots de 32 bits. Cette mémoire est découpée en pavés de 128 x 128 bits; un pavé est donc représenté par 128 lignes de 4 mots. L'écran a une résolution de 2304 lignes de 1728 points d'images. L'image affichée sur l'écran est donc composée de 2304/128 = 18 rangées de 1728/128 = 13,5, soit 14 pavés.

Les figures 4a, 4b et 4c illustrent respectivement le format de l'adresse délivrée par le générateur vidéo, et les adresses reçues par la table d'indirection et la mémoire d'image.

L'adresse délivrée par le générateur vidéo comporte 4 champs : un champ PY indiquant un numéro de rangée de pavé, un champ INDY indiquant un numéro de ligne dans un pavé, un champ PX indiquant un numéro de pavé dans une rangée de pavés, et un champ INDX indiquant un numéro de mot dans une ligne d'un pavé.

Les champs PY et INDY sont reçus dans le registre 28 et les champs PX et INDX par le registre 30. Les champs INDY et INDX comportent respectivement 7 bits (pour 128 lignes) et 2 bits - (pour 4 mots par ligne). Les champs PY et PX comportent respectivement 8 et 4 bits. Parmi ceux-ci, seuls les 5 bits de poids faible de PY sont

utilisés, afin d'adresser l'une des 18 rangées de l'écran. Les 4 bits de poids faible de PX sont utilisés, afin d'adresser l'un des 14 pavés d'une rangée de pavés de l'écran.

Les champs PX et PY sont concaténés pour former une adresse de sélection dans la table d'indirection. Le contenu de cette adresse est concaténé avec les champs INDY et INDX pour constituer l'adresse physique @M d'un mot de la mémoire d'image (figure 4c).

L'adresse délivrée l'interface par décompose en 4 champs comme l'adresse délivrée par le générateur vidéo. Ces 4 champs représentés sur la figure 5a sont identiques à ceux de la figure 4, la 35 seule différence étant que les trois bits de poids fort de PY ne sont pas nécessairement nuls. Dans le cas où ils sont nuls, l'adresse délivrée par l'interface est une adresse correspondant à un mot affiché sur l'écran. Plus précisément, lorsque les trois bits de poids forts de PY sont nuls, l'interface accède à l'une des n premières adresses de la table d'indirection, ce qui correspond à l'un des pavés projetés sur l'écran. Si l'un de ces trois bits est non nul, l'adresse délivrée par l'interface correspond à un mot quelconque de la mémoire. Ce mot peut être affiché sur l'écran car la table d'indirection n'étant pas utilisée de manière bijective, un pointeur de l'une des n premières adresses et un pointeur d'une autre adresse peuvent désigner un même pavé. Pour l'interface, c'est-à-dire pour le processeur, toutes les fenêtres sont virtuelles ; lors des accès, elle ignore si tout ou partie de la fenêtre qu'elle adresse est visible ou non. En général, l'accès aux n premières adresses de la table d'indirection n'est réalisé que pour mettre à jour les pointeurs après une modification de l'organisation d'une fenêtre par ou (défilement, exemple) après réorganisation de la présentation des fenêtres sur l'écran.

Les champs PY et INDY sont reçus dans le registre d'adresses 32 et les champs PX et INDX dans le registre 34. Les champs PX et PY sont regroupés (figure 5b) pour former une adresse d'accès à la table d'indirection. Le contenu de cette adresse est concaténé avec les champs INDY et INDX pour constituer l'adresse physique @M d'un mot de la mémoire d'image (figure 5c).

Le circuit de l'invention permet de créer, modifier ou effacer très facilement des fenêtres sur l'écran. On a représenté sur la figure 6a la mémoire d'image 4 du circuit de l'invention. Cette mémoire comprend trois fenêtres 48, 50 et 52.

5

10

La fenêtre 48 représente l'image affichée sur l'écran. Cette fenêtre est composée de n pavés rectangulaires identiques de la mémoire d'image, chaque pavé étant repéré par un pointeur de la table d'indirection. Les pavés affichés sur l'écran sont, par exemple, ceux désignés par les n premiers pointeurs de la table d'indirection.

Les fenêtres 50 et 52 sont également composés chacune d'un ensemble de pavés rectangulaires identiques de la mémoire d'image, chaque pavé étant repéré par un pointeur de la table d'indirection.

Si ces pointeurs ne sont pas parmi les n premiers pointeurs de la table d'indirection, les fenêtres 50 et 52 ne sont pas affichées sur l'écran. Seule apparaît la fenêtre 48. C'est le cas représenté sur la figure 6b.

En revanche, si le contenu de n premiers adresses de la table d'indirection est modifié de sorte que certains des pointeurs désignent les zones de la mémoire d'image composant les fenêtres 50 et 52, ces fenêtres apparaissent sur l'écran. C'est le cas représenté sur la figure 6c.

On note dans ce cas qu'une fenêtre peut être représentée avec une forme différente dans la mémoire d'image et sur l'écran. En effet, chaque fenêtre est composée de pavés rectangulaires indépendantes associés chacune à un pointeur. Chaque pavé d'une fenêtre peut ainsi être projeté sur l'écran indépendamment des autres pavés de la fenêtre. Une fenêtre constituée de pavés contigus de la mémoire d'image peut ainsi apparaître sous forme de zones disjointes sur l'écran et inversement un ensemble de pavés disjoints de la mémoire d'image peut être visualisé sur l'écran sous la forme d'un rectangle.

#### Revendications

1. Circuit de mémoire d'image virtuelle caractérisé en ce qu'il comprend :

-une mémoire d'image (4) bidimensionnelle organisée en N pavés élémentaires où N est un nombre entier, lesdits pavés étant rectangulaires et identiques,

-une table d'indirection (6) constituée d'une mémoire vive contenant une suite de N pointeurs, chaque pointeur notant l'adresse de début d'un pavé de la mémoire d'image,

-un générateur vidéo (10) pour délivrer un signal vidéo correspondant au contenu de n pavés de la mémoire d'image, où  $n \le N$ , pour l'affichage sur un

écran d'une image composée des n pavés organisés en matrice, l'adressage desdits pavés étant effectué par le générateur vidéo à travers la table d'indirection.

-une interface (12) pour accéder en lecture ou en écriture à la mémoire d'image et à la table d'indirection, l'adressage de la mémoire étant effectuée à travers la table d'indirection,

-le circuit comprenant en outre des bus de données, d'adresses et de commandes et un moyen de séquencement.

Circuit selon la revendication 1, caractérisé en ce que les n pavés affichés sur l'écran sont ceux indiqués par les n premiers pointeurs de la table d'indirection.

3. Circuit selon l'une quelconque des revendications 1 et 2, caractérisé en ce qu'il comprend en outre un moyen (26) disposé entre d'une part le générateur vidéo (10) et l'interface (12) et, d'autre part, la table d'indirection (6), ledit moyen recevant les adresses délivrées par ledit générateur vidéo et ladite interface et décomposant chaque adresse en une partie haute représentant l'adresse de début d'un pavé de la mémoire d'image et en une partie basse représentant un index pour désigner un mot de ce pavé, la partie haute d'une adresse étant reçue par la table d'indirection et la partie basse par la mémoire d'image.

4. Circuit selon la revendication 3, caractérisé en ce que le moyen (26) disposé d'une part entre le générateur vidéo (10) et l'interface (12) et d'autre part la table d'indirection (6) comprend un premier registre d'adresses ligne (28) et un premier registre d'adresses colonne (30) pour recevoir les adresses délivrées par ledit générateur vidéo, un second registre d'adresses ligne (32) et un second registre d'adresses colonne (34) pour recevoir les adresses délivrées par ladite interface et des moyens (40, 42, 44, 46) pour concaténer les parties hautes des adresses délivrées par un registre d'adresses ligne et un registre d'adresses colonne et pour concaténer les parties basses des adresses délivrées par un registre d'adresses ligne et un registre d'adresses colonne, l'adresse résultant de la concaténation des parties hautes des adresses étant appliquée à la table d'indirection et l'adresse résultant de la concaténation des parties basses des adresses étant appliquée à la mémoire d'image.

5. Circuit selon l'une quelconque des revendica-

55

50

tions 1 à 4, dans lequel l'interface (12) reçoit un signal d'adresse unidimensionnel d'un processeur, caractérisé en ce que l'interface (12) comprend en série un moyen de permutation conditionné et une unité de gestion de mémoire, ledit moyen de permutation étant commandé pour permuter des bits d'adresse afin de rendre ladite adresse bidimensionnelle lorsqu'elle est destinée à la mémoire d'image.

6. Circuit selon l'une quelconque des revendications 1 à 4, dans lequel l'interface (12) reçoit un signal d'adresse unidimensionnel d'un processeur, caractérisé en ce que l'interface (12) comprend une unité de gestion mémoire, ladite interface délivrant sur un bus d'adresse une adresse bidimensionnelle par permutation de lignes d'adresse.

FIG. 6a

# RAPPORT DE RECHERCHE EUROPEENNE

Numéro de la demande

EP 86 40 1008

| DOCUMENTS CONSIDERES COMME PERTINENTS  Citation du document avec indication, en cas de besoin, Revendication |                                                                                                                                                                                    |                                      |                                                          |            | CLASSELLE                                          | IT DE LA |

|--------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|----------------------------------------------------------|------------|----------------------------------------------------|----------|

| Catégorie                                                                                                    | des parties pertinentes                                                                                                                                                            |                                      |                                                          | ncernée    |                                                    |          |

| A                                                                                                            | FR-A-2 535 497<br>* Page 41, rever                                                                                                                                                 | (CADTRAK) adication 1 *              | 1                                                        |            | G 09 G                                             | 1/00     |

|                                                                                                              |                                                                                                                                                                                    |                                      |                                                          |            |                                                    |          |

|                                                                                                              |                                                                                                                                                                                    |                                      |                                                          |            |                                                    |          |

|                                                                                                              |                                                                                                                                                                                    |                                      |                                                          |            | •                                                  |          |

|                                                                                                              |                                                                                                                                                                                    |                                      |                                                          |            |                                                    |          |

|                                                                                                              |                                                                                                                                                                                    |                                      |                                                          |            |                                                    |          |

|                                                                                                              | *                                                                                                                                                                                  |                                      |                                                          |            |                                                    |          |

|                                                                                                              |                                                                                                                                                                                    |                                      |                                                          | -          | DOMAINES TEC                                       |          |

|                                                                                                              |                                                                                                                                                                                    |                                      |                                                          | -          | G 09 G                                             | 1/0      |

|                                                                                                              |                                                                                                                                                                                    |                                      |                                                          |            |                                                    |          |

|                                                                                                              |                                                                                                                                                                                    |                                      |                                                          |            |                                                    |          |

|                                                                                                              |                                                                                                                                                                                    |                                      |                                                          |            |                                                    |          |

|                                                                                                              |                                                                                                                                                                                    |                                      |                                                          |            |                                                    |          |

|                                                                                                              |                                                                                                                                                                                    |                                      |                                                          |            |                                                    |          |

|                                                                                                              |                                                                                                                                                                                    | ,                                    |                                                          |            |                                                    |          |

| Le                                                                                                           | présent rapport de recherche a été é                                                                                                                                               | tabli pour toutes les revendications |                                                          |            |                                                    |          |

|                                                                                                              | Lieu de la recherche<br>LA HAYE                                                                                                                                                    | Date d'achèvement de la reche        |                                                          | SIX G      | Examinateur<br>F.E.E.                              |          |

|                                                                                                              | CATEGORIE DES DOCUMEN                                                                                                                                                              | TS CITES T: théori                   | e ou princi                                              | pe à la ba | se de l'invention<br>ieur, mais publié<br>tte date | à la     |

| Y: pai                                                                                                       | rticulièrement pertinent à lui set<br>rticulièrement pertinent en com-<br>tre document de la même catégo<br>ière-plan technologique<br>rulgation non-écrite<br>cument intercalaire | binaison avec un D : cite da         | nent de bre<br>le dépôt ou<br>ans la dema<br>our d'autre | ande       | tte date                                           |          |