(1) Publication number:

**0 273 821** A3

(12)

## **EUROPEAN PATENT APPLICATION**

21 Application number: 87402872.3

(51) Int. Cl.5: G01R 31/28

22 Date of filing: 15.12.87

3 Priority: 17.12.86 JP 302112/86

Date of publication of application: 06.07.88 Bulletin 88/27

Designated Contracting States:

DE FR GB

Date of deferred publication of the search report: 28.03.90 Bulletin 90/13

- Applicant: FUJITSU LIMITED 1015, Kamikodanaka Nakahara-ku Kawasaki-shi Kanagawa 211(JP)

- Inventor: Yamashita, Koichi 1-8-3, Kurihira Asao-ku Kawasaki-shi Kanagawa 215(JP)

- Representative: Joly, Jean-Jacques et al CABINET BEAU DE LOMENIE 55, rue d'Amsterdam F-75008 Paris(FR)

- Semiconductor integrated circuit with a test function.

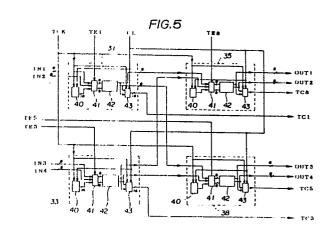

- (57) A semiconductor integrated circuit comprises a plurality of integrated circuit blocks (31 - 39) constituted on a wafer (30), the integrated circuit blocks being arbitrarily electrically connected to each other so as to form a system. Each of the integrated circuit blocks comprises a logical operating circuit (42) for carrying out a logical operation; a pseudorandom pattern generating circuit (40) for generating a pseudo-random pattern signal; switching circuit (41) for selecting either an input signal to be processed by the logical operating circuit or the pseudo-random pattern signal in response to a test enabling signal (TE1 - TE9) which is independently applied to each integrated circuit block so that each integrated circuit block is independently set to either a test mode or a normal mode and for outputting the  $oldsymbol{\triangleleft}$  selected signal to the logical operating circuit; and a data compressing circuit (43) for compressing an output data signal of the logical operating circuit.

EPO FORM 1503 03.82 (P0401)

## **EUROPEAN SEARCH REPORT**

EP 87 40 2872

|                                                |                                                                                                                                                                                                              | DERED TO BE RELEV                                                                                    | AINI                                                                                                                      |                                                |

|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| Category                                       | Citation of document with in of relevant pa                                                                                                                                                                  | ndication, where appropriate,<br>ssages                                                              | Relevant<br>to claim                                                                                                      | CLASSIFICATION OF THE APPLICATION (Int. Cl. 4) |

| Y                                              | ELECTRONIC DESIGN,<br>11th July 1985, pag<br>NL; M. BEEDIE: "Tes<br>tolerance emerge as<br>wafer-scale confere<br>* Page 63, column 1<br>column 2; page 64,<br>39-46 *                                       | es 63-64, Schiphol,<br>ting, fault<br>top issues at<br>nce"<br>, last paragraph -<br>column 2, lines | 1,3,4                                                                                                                     | G 01 R 31/28                                   |

| A                                              | * Page 63, column 3                                                                                                                                                                                          | , lines 28-40 *                                                                                      | 6                                                                                                                         |                                                |

| Y                                              | York, US; D.K. BHAV supercells" * Page 138, paragra division (POLYDIV)                                                                                                                                       | ton, 2nd-5th s 135-139, IEEE, New SAR; "Self-testing ph "Polynomial Scheme" *                        | 1,3,4                                                                                                                     |                                                |

| Α                                              | * Page 138, point "                                                                                                                                                                                          | FSR" *                                                                                               | 7                                                                                                                         |                                                |

| P,X                                            | PROCEEDINGS OF THE INTEGRATED CIRCUITS Portland, 4th-7th M 207-210, IEEE, New YAMASHITA et al.: "170,000-gate FFT pr built-in test circu* Whole article *                                                    | CONFERENCE, ay 1987, pages York, US; K. A wafer-scale ocessor with its"                              | 1-7                                                                                                                       | G 06 F 11/26<br>G 01 R 31/28<br>G 06 F 11/20   |

|                                                | Place of search                                                                                                                                                                                              | Date of completion of the search                                                                     | h                                                                                                                         | Examiner                                       |

| I HE                                           | HAGUE                                                                                                                                                                                                        | 12-12-1989                                                                                           | SARA                                                                                                                      | ASUA GARCIA L.                                 |

| X: part<br>Y: part<br>doc<br>A: tech<br>O: non | CATEGORY OF CITED DOCUMENT<br>ticularly relevant if taken alone<br>ticularly relevant if combined with and<br>ument of the same category<br>anological background<br>written disclosure<br>rmediate document | E : earlier pater after the fill ther D : document c L : document ci                                 | inciple underlying the nt document, but publing date ited in the application ited for other reasons the same patent famil | ished on, or                                   |