1 Numéro de publication:

**0 274 942** A2

## (E)

## DEMANDE DE BREVET EUROPEEN

2 Numéro de dépôt: 87402822.8

(5) Int. Cl.4: G09G 3/20

② Date de dépôt: 11.12.87

© Priorité: 16.12.86 FR 8617575

Date de publication de la demande: 20.07.88 Bulletin 88/29

Etats contractants désignés:

DE GB IT

Demandeur: THOMSON-CSF 173, Boulevard Haussmann F-75379 Paris Cédex 08(FR)

2 Inventeur: Bouron, Jean-Pierre

THOMSON-CSF SCPI 19, avenue de Messine

F-75008 Paris(FR)

Inventeur: Giroux, Daniel

THOMSON-CSF SCPI 19, avenue de Messine

F-75008 Paris(FR)

Inventeur: Rousseau, Pierre

THOMSON-CSF SCPI 19, avenue de Messine

F-75008 Paris(FR)

Mandataire: Trocellier, Roger et al THOMSON-CSF SCPI 19, avenue de Messine F-75008 Paris(FR)

- Système de visualisation sur écran plat matriciel avec affichage protégé des données primordiales pour l'exploitation.

- Système permettant d'assurer une grande sécurité d'exploitation par une protection poussée de l'affichage des données primordiales. Il comporte un écran plat (5) matriciel, par exemple à cristaux liquides, avec des circuits d'adressage pour obtenir une image entrelacée type télévision. Les circuits sont divisés en plusieurs blocs aussi bien pour l'adressage des colonnes paires et impaires que celui des lignes paires et impaires afin de produire une image à haute résolution. Les moyens processeurs graphiques utilisés comportent deux sousensembles (21 et 22), un pour chaque image, chacun d'eux ayant au moins un générateur de symboles(211), associé à une mémoire d'image (212).

L'invention s'applique notamment en avionique pour assurer la sécurité de vol.

Xerox Copy Centre

## SYSTEME DE VISUALISATION SUR ECRAN PLAT MATRICIEL AVEC AFFICHAGE PROTEGE DES DONNEES PRIMORDIALES POUR L'EXPLOITATION

10

20

La présente invention concerne des systèmes de visualisation d'informations par affichage sur écran plat de type à adressage matriciel.

L'invention s'applique notamment dans le domaine avionique pour l'affichage de données de pilotage. La visualisation peut être du type tête haute ou tête basse.

La quantité d'informations à afficher sur les appareils de visualisation équipant le tableau de bord des aéronefs modernes devient de plus en plus importante, l'instrumentation électromécanique conventionnelle disparaissant. Un certain nombre des informations à visualiser sont essentielles pour la sécurité de vol ou l'exploitation et doivent donc être sûres et toujours visualisées, ou visualisables.

Le but de l'invention est de satisfaire à ces impératifs en mettant en oeuvre une structuration particulière du système de visualisation.

Suivant l'invention il est proposé de réaliser un système de visualisation sur écran plat matriciel comportant, un dispositif de visualisation composé de l'écran plat et de moyens d'adressage matriciel commandés pour obtenir une image résultant d'une image paire et d'une image impaire entrelacées, ces moyens comportant quatre groupes de circuits pour l'adressage respectivement des lignes et colonnes paires formant l'image paire et des lignes et colonnes impaires formant l'image impaire, des moyens processeurs graphiques pour élaborer les signaux vidéo à visualiser par adressage des colonnes et des signaux de balayage par adressage lignes, le système étant caractérisé en ce que les moyens processeurs graphiques sont répartis en deux sous-ensembles, un premier sousensemble permettant d'élaborer l'image paire et un deuxième sous-ensemble permettant d'élaborer l'image impaire.

Les avantages qui en résultent se traduisent au niveau de la sécurité renforcée par une probabilité réduite de visualiser les informations erronées, la structure proposée permettant la détection de telles informations par observation de l'écran. En ce sens la structure utilisée assure un haut niveau de sécurité compatible avec les exigences sévères en matière de certification de navigabilité. Un autre avantage résulte de la disponibilité continuelle des informations essentielles, la solution mise en oeuvre permettant de protéger l'affichage de ces données en les reproduisant après une panne et ainsi de garder en fonctionnement un affichage au moins restreint à ces informations essentielles pour l'exploitation. Il en résulte également une diminution des coûts de maintenance par réduction des déposes d'équipement.

Il est connu par le brevet français FR-A-2 571 571 de réaliser un générateur d'images qui, grâce à une mémoire d'image, peut commander des visualisations utilisant des balayages différents, soit le balayage cavalier produit directement par un générateur de symboles, soit d'autres types de balayage par l'intermédiaire de la mémoire d'image tel que le balayage tramé ou entrelacé dit de télévision, ou le balayage matriciel.

Les particularités et avantages de l'invention apparaîtront dans la description qui suit donnée à titre d'exemple à l'aide des figures annexées qui représentent :

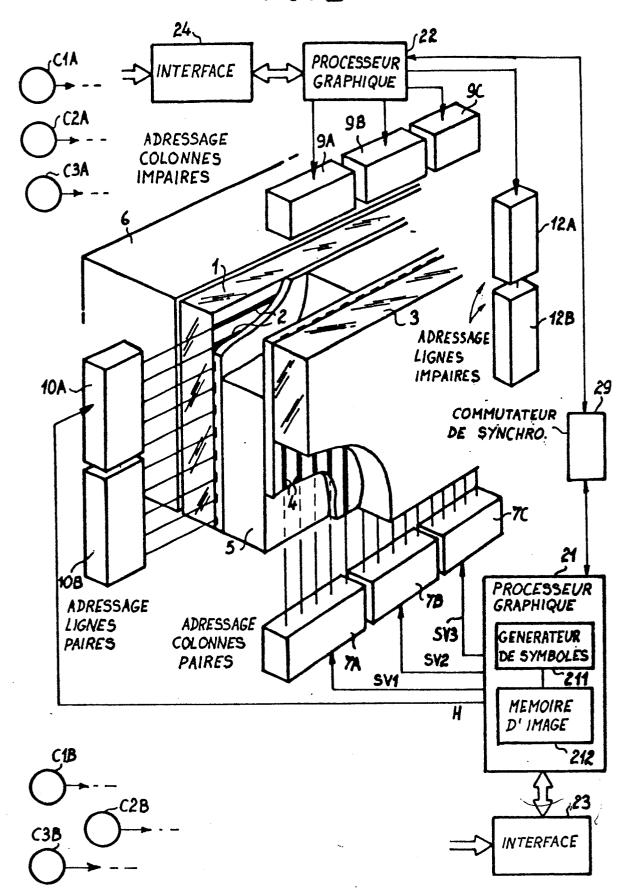

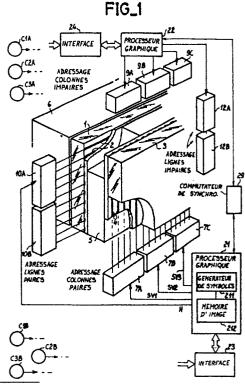

- Fig.1, un schéma général d'un système de visualisation conforme à l'invention ;

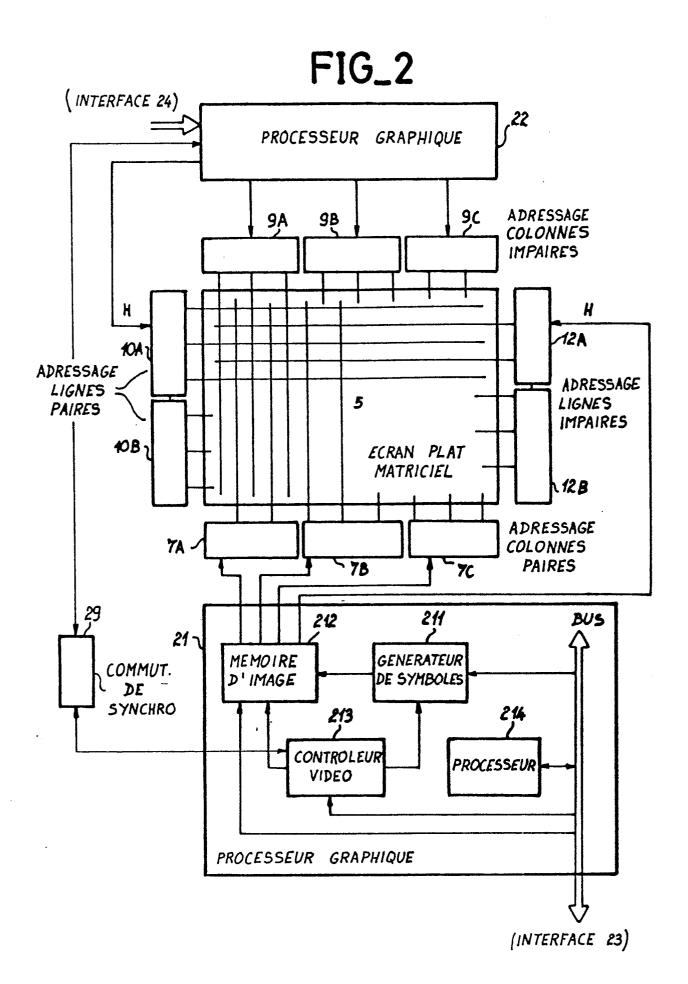

- Fig.2, un premier mode de réalisation du système ;

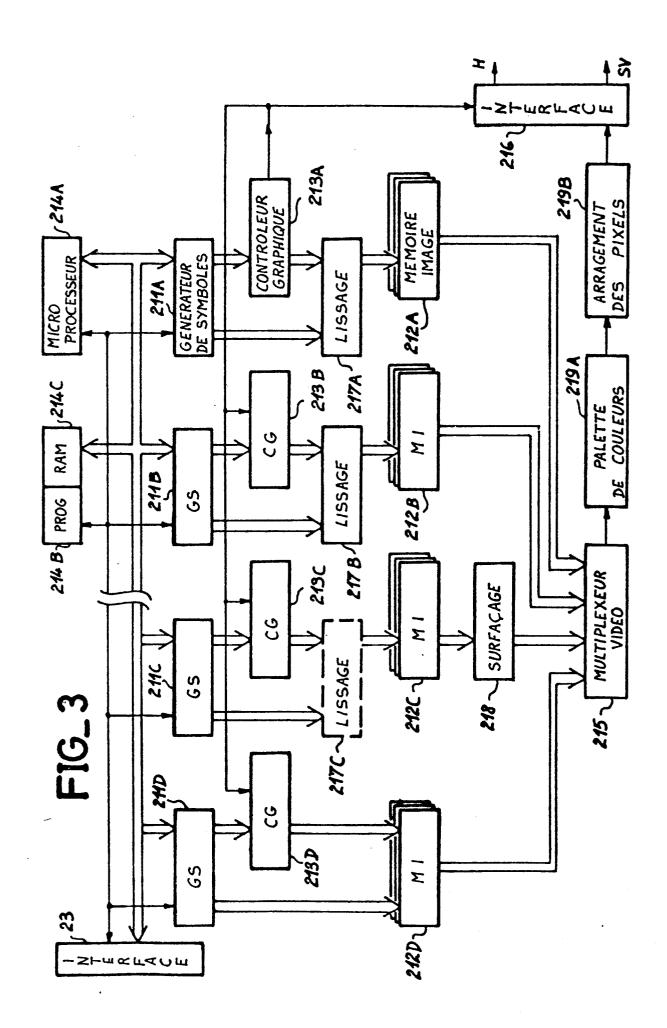

- Fig.3, un deuxième mode de réalisation du système ;

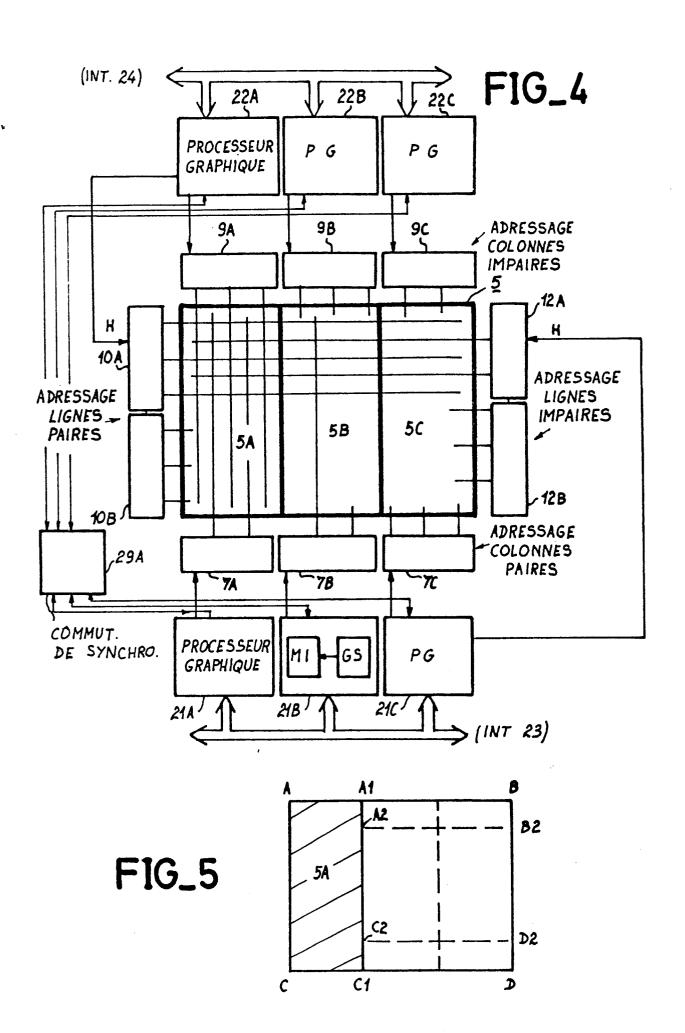

- Fig.4, un troisième mode de réalisation du système ;

- Fig.5, un schéma illustrant la protection de l'affichage dans un système selon la figure 4.

En se reportant à la figure 1 on distingue la structure de l'écran plat qui est rappelée brièvement. Il se compose essentiellement d'une plaque de fond 1, en verre ou en céramique, sur laquelle sont disposées parallèlement les unes aux autres des électrodes transparentes 2 correspondant aux lignes de l'écran ; une plaque avant 3 également transparente, en verre ou en silice, qui forme la face antérieure de l'écran et sur laquelle est disposé un autre réseau d'électrodes 4 perpendiculaire au premier et correspondant aux colonnes. Entre les deux plaques faiblement espacées, et au contact des deux réseaux d'électrodes formant la matrice, un matériau électro-optique 5 solide, liquide ou gazeux, sur lequel se forme l'image. Pour la formation de couleurs on notera que les lignes ainsi que les colonnes peuvent être réparties successivement correspondant aux couleurs rouge vert et bleu de manière à produire les teintes désirées ou, par commande simultanée, une image monochrome en noir et blanc.

Les électrodes lignes 2 et colonnes 4 sont reliées à des circuits intégrés de commande, ou circuits d'adressage (appelés drivers en anglais) qui leur envoient des signaux électriques. L'adressage des points de l'écran se fait ligne à ligne, à une cadence telle que tous les points sont atteints à chaque renouvellement d'image ; en général cette cadence est de 50 à 60 Hz.

Suivant le matériau électro-optique, en réponse aux signaux électriques de commande, apparaît en

chaque point adressé une réaction qui se traduit par un changement d'aspect. Celui-ci peut revêtir deux formes différentes, soit une émission de lumière, soit un changement du pouvoir de réflexion ou de transmission de la lumière. Pour les systèmes qui modulent la transmission de la lumière un dispositif d'éclairage 6, placé à l'arrière produit la luminance nécessaire pour assurer la visualisation des données affichées sur l'écran.

Les matériaux correspondant au premier cas sont à base de dispositifs actifs tels que les écrans à plasma, les écrans luminescents ou à diodes électro-luminescentes, les écrans VFD (Vacum Fluorescent Display), etc ...

Les matériaux correspondant au deuxième cas sont à base de dispositifs passifs. Les plus connus sont constitués par des cristaux liquides qui peuvent être de plusieurs types : cholestériques, nématiques, smectiques, ferro-électriques, etc ...

Ces différents matériaux peuvent être répertoriés selon deux familles. Une première famille regroupe les dispositifs actifs dans lesquels chaque éléments d'image est mis en série avec un élément non linéaire du type varistance (VRD), transistors couche mince (TFT), diodes tête-bêche. La seconde famille fait appel à des matériaux possédant un effet électro-optique à mémoire ; on peut citer les cristaux liquides smectiques A fonctionnant suivant un mode mixte thermique et électrique et les cristaux liquides smectiques ferro-électriques.

Dans l'état présent de la technique l'invention s'applique plus particulièrement et avantageusement à des réalisations d'écran plat à cristaux liquides et à effet électro-optique nématique en hélice qui, associés à une matrice active à TFT et à des filtres colorés, permettent de réaliser des écrans plats matriciels couleur à haute résolution capables, notamment, de visualiser toutes les informations de pilotage d'un aéronef moderne.

Les écrans de visualisation à cristaux liquides dits LCD (Liquid Cristal Display) à haute résolution comportent deux groupes de circuits pour adresser les lignes et colonnes paires relatives à l'élaboration d'une image dite paire et deux autres groupes pour adresser les lignes et les colonnes impaires relatives à l'élaboration d'une image dite impaire. Ce principe de fonctionnement ressemble à celui de la télévision où l'image est formée de deux demi-trames entrelacées. Mais, contrairement à la télévision où les deux demi-trames sont tracées successivement dans le temps, les images paires et impaires sont tracées simultanément, tous les points de l'image étant atteints à chaque renouvellement d'image. Ces quatre groupes sont visibles sur la figure 1, on a représenté les connexions aux électrodes des deux groupes relatives à une image paire; les connexions des deux autres groupes n'ont pas été figurées pour simplifier la représentation. Pour obtenir une image à haute résolution ces quatre groupes présentent une partition supplémentaire des circuits. Ainsi, dans l'exemple représenté, chaque groupe d'adressage des colonnes est divisé en trois circuits 7A, 7B, 7C pour les colonnes paires, 9A, 9B, 9C pour les colonnes impaires et chaque groupe d'adressage des lignes est divisé en deux blocs 10A et 10B pour les lignes paires, 12A et 12B pour les lignes impaires. Les valeurs de partition 2 et 3 considérées ont été prises à titre d'exemple non limitatif.

Les raisons de cette partition résultent de plusieurs facteurs qui sont : le faible pas de la connectique qui impose que les lignes et colonnes soient entrelacées du point de vue connexion avec les circuits d'adressage ; le coût élevé des circuits d'adressage qui ont un grand nombre de sorties ; le fait que l'adressage des points est tel que, à chaque ligne, trois colonnes peuvent ainsi être adressées simultanément ce qui diminue la bande passante du signal vidéo.

Un ensemble processeur graphique annexe élabore les signaux vidéo SV1, SV2, SV3, qui sont appliqués respectivement aux différents circuits d'adressage colonnes 7 et 9, et un signal d'horloge H qui incrémente les compteurs lignes situés dans les circuits d'adressage lignes 10 et 12.

Conformément à l'invention cet ensemble processeur graphique annexe se compose d'un premier processeur graphique 21 qui élabore les signaux destinés aux circuits 7 et 10 qui permettent de former l'image paire, et un deuxième processeur graphique 22 qui produit les signaux pour les circuits 9 et 12 servant à obtenir l'image impaire. Chacun de ces processeurs comportent comme indiqué pour le bloc 21 au moins un circuit générateur de symboles 211 associé à une mémoire d'images 212. Les signaux de commande et ceux correspondant aux informations à visualiser parviennent aux processeurs 21 et 22 à travers des circuits d'interface, respectivement 23 et 24. Des circuits indiqués par des cercles peuvent être par exemple des capteurs dont les signaux sont à traduire par une symbologie déterminée. On peut considérer, par exemple, que le circuit C2A concerne un détecteur d'altitude dont le signal est après traitement appliqué via l'interface 24 au processeur 22. Un autre dispositif de mesure d'altitude C2B distinct du précédent est utilisé pour fournir la même information à travers l'interface 23 au processeur 21. Cette redondance avec des sources multiples différentes pour traduire la même information à visualiser est fréquente sur des matériels aéroportés, ou autres, pour des raisons de sécurité ; elle est utilisée dans le système proposé lorsqu'il s'agit d'une information classifiée primordiale pour

l'exploitation et dont la visualisation est à préserver.

Chaque processeur graphique comporte, outre le générateur de symboles et la mémoire d'image, les éléments essentiels indiqués sur la figure 2 à savoir un circuit contrôleur vidéo 213 qui gère les accès du générateur de symboles à la mémoire d'image et fournit les signaux de balayage de l'écran pour effectuer une lecture en mode télévision ; le circuit 214 représente un circuit de gestion et de calcul tel un ensemble à microprocesseur qui reçoit par un bus et l'interface 23 non figuré les informations à visualiser sur l'écran.

Le tracé des deux images paires et impaire devant se faire simultanément les sous-ensembles 21 et 22 sont coordonnés du point de vue synchronisation ; l'un des circuits contrôleurs vidéo, 213 par exemple, est déclaré maître et fournit les signaux de synchronisation à l'autre contrôleur vidéo qui est déclaré esclave.

Les signaux de synchronisation sont : un signal d'horloge à la cadence point et les signaux de synchronisation de ligne et d'image.

La figure 2 représente l'organisation la plus simple envisagée qui utilise les deux processeurs graphiques 21 et 22 et qui qui permet, en cas de panne d'une voie, le maintien d'affichage de l'image avec une résolution moitié par l'autre voie. Les informations peuvent donc ainsi être toujours disponibles et exploitables. Cette solution présente également une certaine souplesse les deux voies correspondant à l'image paire et à l'image impaire peuvent être rendues dissymétriques, les informations provenant comme il a été dit de sources de données différentes, la différence peut également être apportée au niveau du générateur de symboles, le générateur 211 en 21 étant différent de celui utilisé en 22. Ainsi en cas de panne, ou d'erreur sur les informations visualisées, les deux images entrelacées deviennent différentes ce qui alerte visuellement l'exploitant qui ne peut plus faire confiance aux informations visualisées. Ceci entraîne de la part de l'exploitant, le pilote à bord d'un aéronef, une procédure de vérification et de contrôle sur d'autres instruments disponibles pour la même information de manière à éliminer, le cas échéant, la voie défaillante et reconfigurer sa visualisation sur la voie restante.

La reconfiguration va entraîner, si nécessaire, un changement de l'attribution maître-esclave du contrôleur vidéo restant.

Cette reconfiguration peut se faire simplement par un dispositif commutateur mécanique actionné par l'opérateur. Il peut être envisagé aussi de programmer la commande de ce commutateur pour répondre automatiquement aux différents cas de figure.

Il est possible d'utiliser comme générateurs de

symboles des processeurs spécialisés dans le traitement du signal dit DSP (abréviation de Digital Signal Processor). Ces processeurs graphiques permettent de calculer le tracé des symbologies à stocker dans les mémoires d'images. A titre d'exemple de processeur on peut citer le TMS 320 10 ou le TMMS 320 20 de Texas et ADSP 2100 de Analog Device.

Suivant un autre mode de réalisation indiqué à la figure 3 pour l'un des processeurs graphiques, par exemple le processeur 22, chaque processeur au lieu de comporter un seul générateur de symboles en comporte plusieurs qui travaillent en parallèle, chacun d'eux étant associé à sa mémoire d'images. Dans cet exemple il y a quatre générateurs de symboles 211A à 211D et leurs circuits associés composés des mémoires d'images 212A à 212D et des contrôleurs graphiques 213A à 213D. Le processeur 214, est détaillé par ces éléments principaux un micro processeur 214A, une mémoire programme 214B et une mémoire de données 214C. Les bus de programme et de données sont représentés. La chaîne A est maître et impose aux autres chaînes esclaves B, C, D les synchronisations des modes écriture et lecture (synhronisation pixel, lignes et trames). Les signaux vidéo délivrés par les mémoires d'images sont appliqués à un multiplexeur vidéo 215, puis à travers un circuit d'interface de sortie 216 sont envoyés, ainsi que le signal horloge, aux circuits d'adressage colonnes paires et aux circuits d'adressage lignes paires comme indiqué sur les figures précédentes.

Les circuits complémentaires représentés sont réalisés selon des techniques connues et comportent des circuits de lissage 217A, 217B, 217C, un circuit de surfaçage 218, un circuit palette de couleur 219A et un circuit à rangement de pixels 219B. A titre d'exemple, on considère que la chaîne maître A produit la symbologie relative à l'image statique, la chaîne B la symbologie relative à l'image dynamique, la chaîne C la symbologie de surface et la chaîne D est relative à des symboles provenant d'un radar météo. Le circuit de lissage 217C n'est pas obligatoire.

On rappelle ci-après les fonctions de ces différents circuits :

Le circuit de lissage 217A,B ou C donne au tracé visualisé un aspect analogique. Il supprime en particulier les marches d'escalier qui sont dues à la discrétisation de la mémoire image et de l'écran 5. Le lissage est obtenu en pondérant le niveau du signal vidéo despoints de l'image par lesquels passe le tracé ainsi que celui des points adjacents. Le circuit de lissage peut, par exemple, être constitué par un ensemble de mémoires mortes qui, en fonction de la position et de la direction du tracé, fournissent les coefficients à appliquer

sur les points du tracé.

Le circuit de surfaçage 218 permet de remplir avec une certaine couleur l'intérieur de surfaces. Les codes de couleurs des points de chaque surface sont mémorisés dans la mémoire image.

Le circuit palette de couleurs 219A permet de coder les niveaux des vidéo R,V,B à partir des codes de couleurs fournis par la mémoire image. Le transcodage est obtenu par une table qui peut être chargée dynamiquement par le processeur. Ceci permet d'avoir une infinité de couleurs.

Le long d'une ligne se balayage, contrairement à une visualisation à tube à masque où les trois vidéo R.V.B sont envoyées simultanément sur chaque point, une seule des trois vidéo est envoyée sur chaque point de l'écran 5. Le circuit d'arrangement des pixels 219A à partir de la connaissance de la répartition des points de couleur de l'écran (mémorisée en mémoire morte par exemple) assure la sélection de la bonne vidéo vers l'écran 5.

Les avantages de ce mode de réalisation à plusieurs générateurs de symboles pour chaque image sont les suivants : partage des taches de tracé ; structure modulaire qui permet d'adapter le nombre de générateurs de symboles à la charge de tracé pour une visualisation donnée ; protection de la visualisation des données essentielles en cas de panne d'une chaîne. Ainsi, si par exemple les données essentielles sont produites par des générateurs de symboles de la chaîne maîtresse A et de la chaîne esclave B, et si la chaîne B tombe en panne, il est possible d'avoir une programmation prévue en conséquence pour faire produire par le générateur 213A de la chaîne A les données qui font défaut dans la chaîne B. Dans le cas précédent figure 2, chacun des processeurs 21 et 22 comportait les données essentielles dans un seul générateur de symboles, la panne de l'un d'eux se traduisant par une atténuation de l'image visualisée. On entend par panne une panne de voie qui peut se traduire à partir de la mémoire d'images et en amont jusqu'à la formation du signal, par exemple jusqu'au niveau du capteur 2A, ou 2B, qui avait été considéré.

Pour l'exemple envisagé on remarquera que la technique d'élaboration d'images vidéo synthétique développée dans le brevet FR-A-2 571 571 déjà cité, qui détermine une découpe de l'image mémorisée en zones en affectant à chaque zone une mémoire de rafraîchissement périodique déterminée adaptée au caractèristiques d'évolution des éléments se trouvant dans cette zone, peut s'appliquer aux deux chaînes A et B puisque l'une est relative aux éléments statiques et l'autre aux éléments dynamiques.

La figure 4 représente un troisième mode de réalisation suivant lequel l'écran de visualisation 5

est divisé en plusieurs bandes par exemple en trois bandes verticales 5A, 5B, 5C. Chaque bande est contrôlée à travers les circuits d'adressage colonnes associés 9A, 9B, 9C, 11A, 11B, 11C par un couple de processeurs graphiques 21A et 22A pour la première bande 5A, 21B et 22B pour la deuxième bande 5B et 21C et 22C pour la troisième bande 5C. Chaque processeur comporte comme symbolisé dans le bloc 21B un générateur de symboles et une mémoire d'image associés. Suivant ce mode de réalisation les deux processeurs graphiques associés à une bande tracent toutes les informations à visualiser dans cette bande.

Le circuit commutateur de synchronisation 29A est dérivé de celui 29 de la figure 2 ; il regroupe les différents commutateurs utiles pour effectuer les reconfigurations nécessaires en cas de pannes de voie, chaque voie correspondant à une bande de l'écran et aux processeurs graphiques associés.

Dans la variante de réalisation figure 4 il n'est pas exclu d'avoir plusieurs générateurs de symboles dans chacun des processeurs graphiques, comme dans lemode décrit à l'aide de la figure 3.

Les avantages de ce troisième mode de réalisation sont que, en cas de panne d'une voie, soit au niveau du générateur de symboles, des circuits d'adressage colonnes ou même de l'écran, ou encore en amont du processeur, le traitement et la visualisation des informations essentielles perdues peut être pris en compte par une autre voie ou par plusieurs des autres voies. On peut ainsi présenter avec les éléments restants une image complète avec un format réduit exploitable par le pilote.

La figure 5 illustre le cas où la voie correspondant à la bande 5A tombe en panne. La programmation est telle que la symbologie qui existait dans cette bande de surface A A1 C C1 se trouve reportée au niveau de l'ensemble restant délimité par la surface A1 B C1 D de l'écran avec une compression dans le sens des lignes. La programmation peut également être prévue pour conserver une homothétie à la nouvelle figure en réduisant également la hauteur de l'image; dans ces conditions, l'image complète se produit dans la surface A2 B2 C2 D2 indiquée avec une réduction d'un tiers par rapport au cas où tout l'écran est visualisé.

## Revendications

- 1. Système de visualisation sur écran plat matriciel comportant :

- un dispositif de visualisation composé dudit écran plat (1 à 6) et de moyens d'adressage matriciel (7, 9, 10, 12) pour obtenir une image résultant d'une image paire et d'une image impaire entrelacées,

15

30

40

50

55

ces moyens comportant de quatre groupes de circuits pour adresser respectivement les lignes et colonnes paires formant l'image paire et les lignes et colonnes impaires formant l'image impaire, ;

- des moyens processeurs graphiques pour élaborer les signaux vidéo à visualiser par adressage des colonnes et des signaux de balayage appliqués aux lignes,

caractérisé en ce que les moyens processeurs graphiques sont répartis en deux sous-ensembles, un premier sous-ensemble (21) qui est relatif à l'élaboration de l'image paire et un deuxième sous-ensemble (22) relatif à l'image impaire.

- 2. Système selon la revendication 1, caractérisé en ce que chacun des sous-ensembles processeurs graphiques (21,22) comporte au moins un générateur de symboles (211) associé à une mémoire d'images (212).

- 3. Système selon la revendication 2, caractérisé en ce que les moyens processeurs graphiques comportent des moyens de synchronisation pour effectuer l'adressage matriciel, lesdits sous-ensembles étant coordonnés, l'un (21) jouant le rôle de maître et l'autre (22) étant assujeti au rôle d'esclave.

- 4. Système selon la revendication 3, caractérisé en ce qu'il comporte un moyen commutateur (29,29A) interconnecté sur des connexions de synchronisation entre lesdits sous-ensembles et permettant de connecter le rôle de maître lorsque cette fonction n'est plus assurée à la suite d'une panne.

- 5. Système selon la revendication 4, caractérisé en ce que chaque sous-ensemble processeur graphique (21,22) comporte, en outre, un processeur de gestion et de contrôle (214) et un circuit contrôleur vidéo (213) lequel est connecté au dit moyen commutateur (29,29A) pour fournir les signaux de synchronisation dans le cas de la fonction maître ou pour les recevoir dans le cas d'une fonction esclave.

- 6. Système selon l'une quelconque des revendications 2-à-5, caractérisé en ce que chaque sous-ensemble processeur graphique (21,22) comporte plusieurs générateurs de symboles (211A à 211D) travaillant en parallèle, chacun d'eux étant associé à une mémoire d'image (212A à 212D) pour y stocker les données correspondantes, les mémoires d'images étant connectées à un circuit multiplexeur vidéo (215).

- 7. Système selon l'une quelconque des revendications précédentes, appliqué à une visualisation à haute résolution, chacun des groupes (7,9,10,12) de circuits d'adressage étant composé de plusieurs circuits comprenant : <u>m</u> circuits d'adressage (10A,10B) des lignes paires, <u>m</u> circuits d'adressage

(12A,12B) des lignes impaires, <u>n</u> circuit d'adressage (7A,7B,7C) des colonnes paires et <u>n</u> circuits d'adressage (9A,9B,9C) des colonnes impaires.

8. Système selon la revendication 7, caractérisé en ce qu'il comporte autant de sousensembles processeurs graphiques (21A,21B...,22A,22B,...) qu'il y a de circuits d'adressage de colonnes (7A,7B...,9A,9B,...), afin de contrôler l'image de l'écran (5) sous forme de n bandes successives (5A,5B,...).

FIG\_1