11 Veröffentlichungsnummer:

**0 290 829** A2

(12)

## EUROPÄISCHE PATENTANMELDUNG

(21) Anmeldenummer: 88106346.5

(51) Int. Cl.4: G08G 1/09

2 Anmeldetag: 21.04.88

(30) Priorität: 15.05.87 DE 3716285

(43) Veröffentlichungstag der Anmeldung: 17.11.88 Patentblatt 88/46

Benannte Vertragsstaaten:

AT CH DE FR LI NL

Anmelder: Blaupunkt-Werke GmbH Robert-Bosch-Strasse 200 D-3200 Hildesheim(DE)

© Erfinder: Hegeler, Wilhelm Grosse Venedig 23 D-3200 Hildesheim(DE)

Vertreter: Eilers, Norbert, Dipl.-Phys. Blaupunkt-Werke GmbH Robert-Bosch-Strasse 200 D-3200 Hildesheim(DE)

## (54) Anordnung zur Decodierung von Signalen.

5) Bei einer Anordnung zur Decodierung von Signalen, die zusätzlich zu weiteren Signalen als Modulation von Radiowellen empfangen werden und deren jeweilige Frequenz eine bestimmte Information darstellt, wird ein Zeitbasissignal konstanter Frequenz erzeugt, aus dem mit Hilfe eines Mikroprozessors ein Referenzsignal mit steuerbarer Frequenzund Phasenlage abgeleitet wird. Ein Ausgangssignal wird abgeleitet, wenn eine Übereinstimmung des Referenzsignals mit dem empfangenen Signal bezüglich der Phase und der Frequenz vorliegt. Das Zeitbasissignal kann vorzugsweise aus der Instruktionsfrequenz des Mikroprozessors dadurch abgeleitet werden, daß mindestens im zeitlichen Mittel gleichlange Programmschleifen durchlaufen werden. Zur Ableitung der Referenzfrequenz dient ein Register, das um veränderbare Werte inkrementiert wird. Bei zwei überlagerten Signalen wird das eine nach Oder Frequenz, das andere nach dem Tastverhältnis

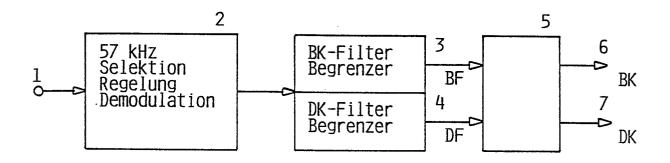

5 eines binären Signals ausgewertet. 6 3 BK-Filter 57 kHz Selektion Begrenzer BF BK Regelung 7 Demodulation 4 DK-Filter Begrenzer DK DF

Fig.1

15

25

Die Erfindung betrifft eine Anordnung nach der Gattung des Hauptanspruchs.

Insbesondere zur Steuerung von Rundfunkempfängern zum Empfang von Verkehrsinformationen ist es bekannt, einen mit zusätzlichen Signalen modulierten Hilfsträger auszuwerten. So ist beispielsweise ein erstes Signal vorhanden, welches aus einer vorgegebenen Frequenz zwischen 20 und 60 Hz besteht und zur Kennzeichnung des geographischen Bereiches dient, für den die erwartete Information gilt. Neben dieser sogenannten Bereichskennung kann von Zeit zu Zeit ein weiteres Signal als sogenannte Durchsagekennung empfangen werden, z. B. eine Frequenz von 125 Hz. Diese Durchsagekennung dient dazu, über eine in Betriebsbereitschaft befindliche Empfangseinrichtung für den modulierten Hilfsträger die Wiedergabeeinrichtung der Durchsage der Verkehrsinformation einzuschalten. Derartige Systeme und zugehörige Sende-und Empfangseinrichtungen, insbesondere Anordnungen zur Decodierung der Signale, sind in der Literatur eingehend beschrieben.

Die erfindungsgemäße Anordnung hat die Aufgabe, möglichst schnell zu erkennen, ob und welche der Bereichs-oder Durchsagekennfrequenzen vorliegt oder ob eine bestimmte vorher eingegebene Bereichskennfrequenz empfangen wird. Außerdem soll die Bereichskennung auch während des Vorliegens einer Durchsagekennung erkannt werden können. Erkennen bedeutet in diesem Zu-Erzeugen entsprechender sammenhang das Schaltsignale, welche an andere Gruppen eines Radiogerätes weitergeleitet werden und dort Funktionen auslösen, wie beispielsweise: Suchlaufstart, NF-Lautstärkesteuerung, Anzeige des Bereichs sowie der Durchsage mit Hilfe von Anzeigelampen oder alphanumerischen Anzeigevorrichtungen.

Die erfindungsgemäße Anordnung ist dadurch gekennzeichnet, daß ein Zeitbasissignal mit einer konstanten Frequenz erzeugt wird; daß mit Hilfe eines Mikroprozessors aus dem Zeitbasissignal ein Referenzsignal mit steuerbarer Frequenz-und Phasenlage abgeleitet wird; daß die Frequenz-und die Phasenlage des Referenzsignals durch einen Phasen-und/oder Frequenzvergleich mit dem empfangenen Signal gesteuert wird und daß ein Ausgangssignal abgeleitet wird, wenn eine Übereinstimmung des Referenzsignals mit dem empfangenen Signal bezüglich der Phase und der Frequenz vorliegt.

Mit einer praktisch ausgeführten erfindungsgemäßen Anordnung kann ein Erkennen einer Bereichskennfrequenz innerhalb von weniger als 200 ms erreicht werden, während eine Durchsagekennung innerhalb von 800 ms erfolgt. Selbst während einer Durchsage kann eine Bereichskennung innerhalb von weniger als 500 ms erkannt werden.

Durch die in den Unteransprüchen aufgeführten Maßnahmen sind vorteilhafte Weiterbildungen und Verbesserungen der im Hauptanspruch angegebenen Erfindung möglich. Besonders günstig ist es, das Zeitbasissignal aus der Instruktionsfrequenz des Mikroprozessors abzuleiten.

Eine Weiterbildung der Erfindung besteht darin, daß zur Erzeugung des Referenzsignals im Takt des Zeitbasissignals der Inhalt (P) eines L Bit breiten Akkumulators um eine Zahl (dP), welche wesentlich kleiner als 2<sup>L</sup> ist, verändert wird und daß die höchstwertige Stelle (MSB) des Akkumulators das Referenzsignal bildet. Hierdurch ist eine besonders günstige und wenig Aufwand erfordernde Ableitung des Referenzsignals möglich.

Eine andere Weiterbildung ermöglicht einen besonders günstigen Phasen-und Frequenzvergleich dadurch, daß das Referenzsignal und ein gegenüber diesem um 90° phasenverschobenes Referenzsignal jeweils mit dem zu decodierenden Signal exklusiv-oder-verknüpft wird und daß die Ergebnisse der Exklusiv-oder-Verknüpfungen jeweils einem Integrator zugeführt werden.

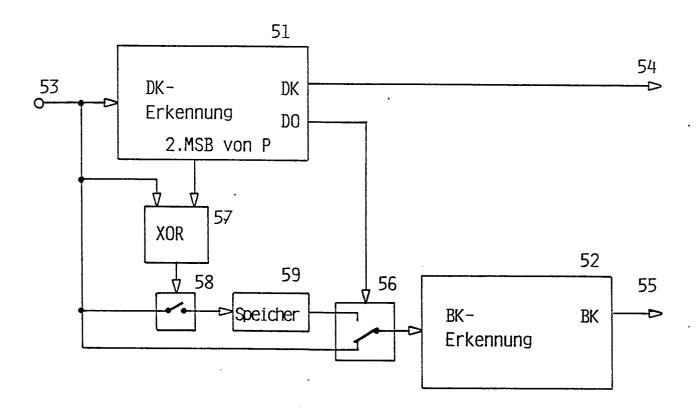

Schließlich ermöglicht eine andere Weiterbildung der Erfindung eine einfache Decodierung des Bereichskennsignals bei gleichzeitigem Auftreten des Durchsagekennsignals dadurch, daß je eine Einrichtung (51, 52) zur Decodierung des ersten und des zweiten Signals vorgesehen ist, daß der Einrichtung (52) zur Decodierung des ersten Signals das erste Signal nur zugeführt wird, wenn das zweite Signal nicht vorhanden ist, und daß bei Vorhandensein des zweiten Signals der Einrichtung (52) zur Decodierung des ersten Signals ein Hilfssignal zugeführt wird, welches durch Vergleich des zugeführten zweiten Signals und des zur Decodierung des zweiten Signals abgeleiteten Referenzsignals gewonnen wird.

Ausführungsbeispiele der Erfindung sind in der Zeichnung an Hand mehrerer Figuren dargestellt und in der nachfolgenden Beschreibung näher erläutert. Es zeigt:

Fig. 1 ein stark vereinfachtes Blockschaltbild einer Anordnung zur Demodulation, Selektion und Decodierung von Verkehrsfunkkennsignalen gemäß der Erfindung,

Fig. 2 ein Signalflußdiagramm einer erfindungsgemäßen Anordnung,

Fig. 3 Tabellen zur Darstellung einzelner Signalverarbeitungsabläufe,

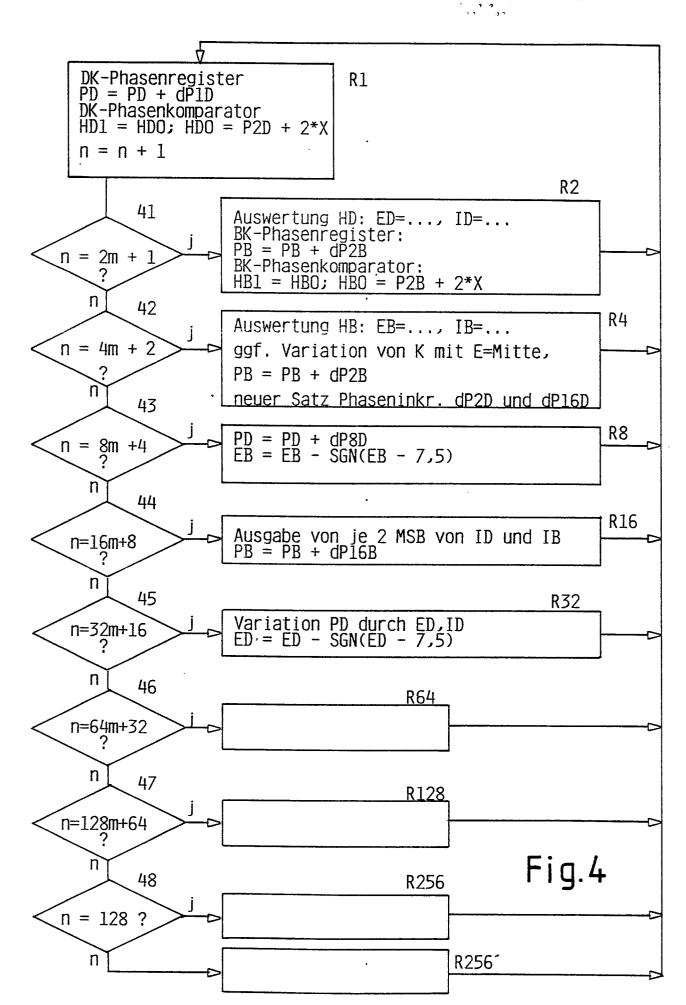

Fig. 4 eine schematische Darstellung eines für den Mikroprozessor vorgesehenen Programms und

2

35

4

Fig. 5 ein Signalflußdiagramm einer erfindungsgemäßen Anordnung, bei welcher zunächst eine Erkennung des Durchsagekennsignals und dann eine Erkennung des Bereichskennsignals erfolgt.

Der Anordnung nach Fig. 1 wird bei 1 das vom Demodulator eines nicht dargestellten Empfängers erzeugte Multiplexsignal MPX zugeführt, welches die Audiosignale sowie den amplitudenmodulierten Hilfsträger mit einer Frequenz von 57 kHz umfaßt. In einer Schaltung 2 wird mit Hilfe eines Bandpasses, einer an sich bekannten Regelschaltung sowie eines Amplitudendemodulators der Hilfsträger demoduliert. Der Ausgang der Schaltung 2 ist mit je einer Filter-und Begrenzerschaltung 3, 4 verbunden. Dabei dient die Filter-und Begrenzerschaltung 3 zur Berechnung und Selektion des Bereichskennsignals BK, während die Filter-und Begrenzerschaltung 4 das Durchsagekennsignal DK begrenzt selektiert. Beide Filter-und Begrenzerschaltungen 3, 4 geben bei Auftreten eines Bereichskenn-bzw. Durchsagekennsignals ein Signal BF bzw. DF mit der entsprechenden Frequenz ab. Aus diesen Signalen wird in einem Decoder 5 jeweils bei Vorhandensein der Kennsignale ein Schaltsignal BK bzw. DK erzeugt.

Gemäß einer Ausgestaltung der Erfindung können die Signale BF bzw. DF ohne vorherige Frequenzselektion bearbeitet werden. Außerdem ist bei bekannten Schaltungen eine 4-Bit-Quantisierung der als Sinusschwingung übertragenen Kennsignale erforderlich, während bei der erfindungsgemäßen Anordnung eine Binärisierung mit einer Schaltschwelle möglich ist.

Bei der erfindungsgemäßen Anordnung erfolgt die Decodierung des Durchsagekennsignals in ähnlicher Weise wie diejenige des Bereichskennsignals. Die auf das das Signalflußdiagramm gemäß Fig. 2 Bezug nehmenden Erläuterungen gelten daher größtenteils auch für die Decodierung des Durchsagekennsignals. Es folgt zunächst eine allgemeine Beschreibung der Anordnung nach Fig. 2; Einzelheiten werden im Zusammenhang mit den Figuren 3 bis 5 erläutert.

Bei 11 wird das Eingangssignal X, welches das binärisierte Ausgangssignal der Schaltung 2 (Fig. 1) ist, zur Verfügung gestellt, während bei 12 eine Zeitbasisfrequenz F0 erzeugt wird. Ein 8-Bit-Register 13 wird im Takt der Zeitbasisfrequenz F0 jeweils um eine Zahl dP, welche eine Funktion von K ist, inkrementiert.

Auf den Maximalwert erfolgt in an sich bekannter Weise der Wert 0. Für eine besondere Behandlung des Überlaufs sind keine Vorkehrungen getroffen. Aus dem Inhalt P des Registers 13 werden die beiden höchstwertigen Stellen P2 über 14 weitergeleitet und bei 15 mit dem Eingangssignal X verarbeitet. Dabei wird ein Signal H gebildet, wel-

ches aus dem Rest einer Division der Summe aus P2 + 2 \* X durch vier besteht. Bei 16 werden zwei zeitlich aufeinander folgende Werte des Signals H, nämlich die Signalwerte H0 und H1 gespeichert. Aus diesen werden Signale E und I gewonnen. E ist proportional dem Integral über dem Phasenfehler, wahrend I ein Maß für die Sicherheit der Erkennung darstellt.

Die Auswertung der Signale E und I erfolgt bei 17, wonach eine Phasenvariation 18 zum Einrasten des Referenzsignals gesteuert wird.

Es wird zwischen einer aktiven und einer passiven Bereichskennung unterschieden. Bei der aktiven Bereichskennung wird ein Wert K vorgegeben, der einer der Bereichskennfrequenzen zugeordnet ist. Es werden dann nur Bereichskennsignale mit dieser Frequenz ausgewertet und beispielsweise ein Suchlauf nur bei Sendern angehalten, welche dieses Bereichskennsignal senden.

Bei der passiven Bereichskennung wird lediglich festgestellt, ob der gerade empfangene Sender ein Bereichskennsignal sendet und welche Frequenz dieses Bereichskennsignal aufweist. Entsprechend ist bei dem Signalflußdiagramm nach Fig. 2 vorgesehen, daß entweder eine Selektion des Wertes K bei 19 durch den Bediener oder daß bei 20 eine von der Auswertung 17 gesteuerte Variation des Wertes K erfolgen kann. Bei 21 ist der Wert K abgelegt, aus welchem bei 22 diejenige Zahl dP gebildet wird, welche im Register 13 im Takt der Frequenz F0 dem Registerinhalt hinzuaddiert wird. Da der Inhalt des Registers 13 die Bedeutung einer Phase hat, ist der Wert dP auch als Phaseninkrement aufzufassen.

Wegen der systembedingten Quantisierung vollführen die Phase und damit das Signal E auch bei eingerasteter Regelschleife Regelschwingungen. Zur Bedämpfung dient die später erläuterte Funktion 23.

Zur schnellen und sicheren Erkennung ist eine Abtastung der Eingangssignale mit einer Frequenz von mindestens 1,3 kHz erforderlich. Diese Frequenz wird durch periodisches Durchlaufen von Programmteilen mit definierter Anzahl von Befehlen erzeugt. Da jedoch die einzelnen Funktionen (siehe Signalflußdiagramm Fig. 2) verschieden häufig ausgeführt zu werden brauchen, wird ein erster Programmteil R1 bei jedem Programmlauf durchlaufen, während weitere Programmteile abwechselnd durchlaufen werden.

Eine derartige Folge von Programmläufen ist tabellarisch in Fig. 3a dargestellt. Bei dem ersten Programmlauf werden nacheinander die Programmteile R1 und R2 durchlaufen, bei dem zweiten Programmlauf die Programmteile R1 und R4, bei dem dritten Programmlauf wieder die Programmteile R1 und R2, bei dem vierten Programmlauf die Programmteile R1 und R8 usw. Die ver-

schiedenen Programmteile dürfen in einem gewissen Maße unterschiedlich lang sein. Wichtig ist, daß jeder immer gleich lang ist. Damit entsteht eine im zeitlichen Mittel konstante Wiederholfrequenz aller Programmteile, die z. B. für den Programmteil R1 2,7 kHz, für R2 1,35 kHz, für R4 0,67 kHz usw. beträgt.

Das Inkrementieren des Registers 13 (Fig. 2) erfolgt nun für die Durchsagekennung im Programmteil R1, also mit einer Frequenz von 2,7 kHz. Für die Bereichskennung wird ein entsprechendes Register im Programmteil R2 inkrementiert. Damit in den häufig auftretenden Programmteilen R1 und R2 Rechenzeit eingespart wird, wird in diesen Programmteilen mit geringer Genauigkeit - beispielsweise 4 Bit - inkrementiert (dP2), während in seltener durchlaufenden Programmteilen eine Feinkorrektur mit dP16 vorgenommen wird.

Damit stehen für die Bereichskennung und für die Durchsagekennung mit Hilfe einer Phasenregelschleife Referenzfrequenzen zur Verfügung, die im zeitlichen Mittel konstant sind und ohne großen Aufwand auf eine Genauigkeit von 1/10000 eingestellt werden können. Sie können ferner leicht durch Änderung der Inkremente oder durch direkte Variation des Registerinhalts P geändert werden.

Die beiden höchstwertigen Bits P2 von P durchlaufen periodisch den Zahlenbereich 0, 1, 2, 3 und markieren damit eine Vierphasenschablone im Zeitbereich. Diese wird an das Eingangssignal X dadurch angelegt, daß ein Signal H = P2 + 2X mod 4 gebildet wird. Dieses ist in Fig. 3b für eine Probe von X, die mit dem Sollwert übereinstimmt, dargestellt. H nimmt in diesem Fall die Werte 1 oder 2 ein. Eine Abweichung vom Sollwert ergibt für H 0 oder 3. Für ein jeweils um 90° voreilendes und um 90° nacheilendes Eingangssignal X ist die Bildung von H in den Figuren 3c und 3d dargestellt.

Der Übersichtlichkeit halber wurde bei den Figuren 3b bis 3d eine Abtastfrequenz gewählt, welche geringer als die erwähnte Frequenz von 2,7 kHz ist. Bei einem realen Verhältnis zwischen der Frequenz des Eingangssignals X und der Abtastfrequenz ergeben sich die in Fig. 3e dargestellten Verhältnisse. Als Beispiel ist hierfür ein um 18° voreilendes Eingangssignal X angenommen.

In einem Programmteil, der halb so häufig durchlaufen wird wie die Ableitung von H, werden aus jeweils zwei aufeinander folgenden Werten H0 und H1 durch Integration die Werte E und I gewonnen. E kann Werte zwischen 0 und 15 einnehmen, wozu ein 4-Bit-Register genügt, während I großer als 0 ist und größere Werte annehmen kann als E. Wegen der erforderlichen Schnelligkeit wird jedoch I ebenfalls in einem 4-Bit-Register behandelt und in einem weniger häufig durchlaufenden Programmteil um weitere Registerstellen ergänzt.

I enthält die Information über die Sicherheit der Erkennung. Nach zwei Abtastwerten mit richtiger Phasenlage (H = 1 oder 2) wird I um 1 inkrementiert. Nach zwei Abtastwerten mit falscher Phasenlage (H = 0 oder 3) wird I um 2 dekrementiert, wobei I nicht kleiner als 0 werden kann. I kann daher nur bei überwiegend richtiger Phase von 0 hochlaufen.

E enthält die Information über die Richtung einer eventuellen notwendigen Frequenz-bzw. Phasenkorrektur. Diese Information ist im höchstwertigen Bit (MSB) von E enthalten. Außerdem liefert E eine Aussage über die Notwendigkeit einer solchen Korrektur, welche dann gegeben ist, wenn der Absolutwert von (E - 7,5) größer als eine Funktion von I (z. B. 1 + I/4) ist. Fig. 3f zeigt die Bildung von E und I aus den beiden aufeinander folgenden Werten HO und H1.

Die Phasenkorrektur von P2 wird in einem weniger häufig durchlaufenden Programmteil vorgenommen, wobei das höchstwertige Bit von E bzw. das Vorzeichen von (E - .7,5) die Richtung der Korrektur bestimmt und der Betrag der Korrektur von I abhängt. Bei großem I wird die Phase nurschwach variiert, da in diesem Fall die Phasenregelschleife schon gut eingerastet ist. Bei kleinem I erfolgt jedoch eine starke Phasenvariation, woraus die zum schnellen Einrasten erforderliche große Fangbreite der Phasenregelschaltung resultiert.

Diese starke Variation bei kleinem I löst auch das Problem des labilen Gleichgewichtes in der Gegenphase, bei der H die Werte 0 und 3 liefert und E zunächst keine sinnvolle Richtungsinformation enthält.

I läuft jedoch schnell nach 0 und die dadurch bedingte starke Variation der Phase, die in ihrer Richtung zufällig ist, hebt diesen Zustand auf.

Die Phase und damit auch E vollführen auch bei eingerasteter Phasenregelschleife immer Regelschwingungen, die wegen der systembedingten Quantisierung nie ganz abklingen. E schwingt dabei um seinen "Mittelwert" von 7,5. Zur Bedämpfung dieser Regelschwingungen wird E periodisch dadurch zur Mitte gezogen, daß jeweils E = E - SGN (E - 7,5) gesetzt wird (SGN = Vorzeichen). Dieses erfolgt bei 23 im Signalflußdiagramm gemäß Fig. 2.

Das Einrasten der Phasenregelschleife bedeutet, daß eine Durchsagekennung bzw. eine Bereichskennung entsprechend der vorgewählten Frequenz (aktive Bereichskennung) vorliegt. Bei der aktiven Bereichskennung wird eine Zahl K (K = 0...5 entsprechend den Bereichen A bis F bei dem in Europa eingeführten Verfahren oder K = 0 bis 9 entsprechend den Bereichen 0 bis 9 bei einem in den USA angewandten Verfahren) angewählt. Dieses kann über einen Datenbus oder durch eine

30

40

Tasteneingabe erfolgen. Für das jeweils vorgewählte K wird ein entsprechender Satz von Inkrementen dP1 und dP16 für die Variation der Phase bereitgehalten.

Bei der passiven Bereichskennung besteht die Aufgabe, für die Frequenz des Eingangssignals einen entsprechenden Wert für K zu finden. Die zum Einrasten erforderliche Phasen-bzw. Frequenzkorrektur wird hier nicht - wie oben beschrieben - durch eine von I abhängige Änderung der Phase vorgenommen. Bei der passiven Bereichskennung dient dieser Mechanismus nur - schwach dosiert - zur Feinkorrektur der Phase. Es wird vielmehr die Zahl K variiert, wenn E, das Integral über dem Phasenfehler, ein gewisses von I abhängiges Maß überschreitet. Hierfür gilt: wenn ABS (E - 7,5) größer gleich 1 + INT (I/4), dann K = K + SGN (E - 7,5) wobei K = 0...5.

Durch die damit verbundene Frequenzänderung gelangt K schnell (besonders bei kleinem I) in die Nähe des richtigen Wertes. Trotzdem reicht diese Operation nicht zum schnellen Einrasten der Phasenregelschleife aus. Da diese Operation im Programmteil R4 abläuft, benötigt K zum Durcheilen seines Zahlenbereichs ein gewisse Zeit. Bis zum Erreichen des richtigen Wertes würde der Phasenfehler zunächst immer größer werden, und müßte dann durch Überschwingen von K über den richtigen Wert hinaus wieder abgebaut werden, was zu nicht endenden Regelschwingungen führen würde oder sogar zum Nichteinrasten, wenn der Phasenfehler dabei 180° überschreitet.

Eine Dämpfung dieser Regelschwingungen ist erforderlich, damit das Einschwingen in kürzester Zeit erfolgt. Dazu wird eine zusätzliche Steuerung der Phase proportional zu E oder zur Änderung von K bzw. der Frequenz eingeführt. Zunächst wird bei jeder Änderung von K E auf einen Mittelwert gesetzt. Damit wird der Integrator weitgehend ausgeschaltet. Außerdem wird die Phase um einen bestimmten Wert verändert, so daß die gewünschte Bedämpfung erreicht wird. Durch das Zurücksetzen von E zur Mitte bei einem Wechsel von K wird jedoch der Phasenfehler nicht aufgehoben. Bei dem folgenden K würde dieser Phasenfehler E wieder in dieselbe Richtung treiben. Aus diesem Grunde wird zugleich mit K auch die Phase um einen empirisch ermittelten Wert geändert, so daß dann der Phasenfehler ungefähr verschwindet. wenn das neue K dem richtigen Wert entspricht.

Durch diese direkte Phasenänderung wird zwar einerseits die Änderung von K verzögert, andererseits ermöglicht gerade sie das unmittelbare Einrasten der Phasenregelschleife auch bei völlig falschem K, da die dann erforderliche starke Phasenänderung fast ausschließlich über diesen Mechanismus erfolgt.

Beim Erreichen des richtigen Wertes von K ist

diese Phasenänderung gewissermaßen ein "Phasenkredit". Die Phasenregelschleife soll bei der neuen Frequenz eine Chance zum Einrasten erhalten und nicht zu stark mit Phasenfehlern aus der Vergangenheit belastet sein.

Ist dabei die Phase weitgehend richtig, wächst der Wert I an und erhöht damit die Schwelle, die für eine erneute Änderung von K durch E überschritten werden muß. So wird der richtige Wert K mit hoher Wahrscheinlichkeit beibenalten, nachdem er gefunden wurde.

Wie bereits erwähnt, stellt I ein Maß für die Erkennungssicherheit dar, seine beiden nöchstwertigen Bits werden daher über einen Datenbus ausgegeben, wobei die Zahl 0 keine Erkennung, die Zahl 3 sichere Erkennung und die Zahlen 1 und 2 entsprechende Mittelwerte darstellen.

Ohne weitere Maßnahmen wird jedoch der Wert 3 bei den niederfrequenten Bereichskennsignalen A. B schneller erreicht als bei den höherfrequenten D, F. Dieses hat verschiedene Gründe, beispielsweise darin, daß die Startbedingungen für die unteren Bereiche besser sind, daß durch anfangs vorhandene Phasenfehler dem Hochlaufen von I eine Welligkeit überlagert ist, welche sich bei dem Bereichskennsignal A stärker bemerkbar macht und durch Phasenfehler, welche bei höheren Bereichskennfrequenzen ebenfalls stärker ins Gewicht fallen.

Um die Erkennungszeit für alle Bereiche ungefähr gleich zu machen, werden nicht die beiden höchstwertigen Bits von I direkt verwendet, sondern für K größer gleich 1 wird zunächst zu den vier höchstwertigen Bits von I der Wert K - 1 hinzuaddiert bevor die beiden höchstwertigen Bits als Bereichserkennungssicherheit ausgegeben werden. Dadurch wird bei F der Zustand "keine Erkennung" der "1" zugeordnet. Entsprechendes gilt für die Bereiche 0 bis 9 bei dem in den USA angewandten Verfahren.

Fig. 4 stellt ein Flußdiagramm eines zum Betrieb einer erfindungsgemäßen Anordnung vorgesehenen Programms dar. In den einzelnen Programmteilen durchgeführte Funktionen sind der Übersichtlichkeit halber nur angegeben, soweit es zur Erläuterung der Erfindung erforderlich ist. Dabei sind die Größen, die sich auf die Durchsagekennung beziehen, durch ein "D" ergänzt, während "B" Bereichskennung bedeutet.

Der Programmteil R1 wird bei jedem Programmlauf durchlaufen und enthält einen 8 Bit breiten Programmzähler, bei dem eine Zählvariable n bei jedem Programmlauf um 1 erhöht wird. Im Programmteil R1 wird das Phasenregister für die Durchsagekennung inkrementiert und der Phasenvergleich für die Durchsagekennung dadurch vorgenommen, daß die Werte HD1 und HD0 abgeleitet werden, wie es bereits im Zusammenhang mit

40

30

35

den Figuren 2 und 3 beschrieben wurde.

An den Programmteil R1 schließt sich eine Verzweigung 41 an, bei welcher geprüft wird, ob n ungeradzahlig ist. Ist dieses der Fall, so durchläuft das Programm den Programmteil R2, in welchem das Phasenregister für die Bereichskennung inkrementiert wird und der Phasenvergleich für die Bereichskennung vorgenommen wird.

Ist n geradzahlig, so wird bei der Verzweigung 42 geprüft, ob n = 4 m + 2 ist. Dabei ist m wie auch bei der Verzweigung 41 und den folgenden Verzweigungen eine beliebige ganze positive Zahl einschließlich 0. An den Ja-Ausgang der Verzweigung 42 schließt sich der Programmteil R4 an, in welchem die Auswertung von H wie im Zusammenhang mit Fig. 3, insbesondere der Tabelle nach Fig. 3f, beschrieben wurde. Gegebenenfalls wird K variiert und E in die Mitte gesetzt. In Abhängigkeit von K wird ein neuer Satz von Inkrementen abgerufen.

Auf den Nein-Ausgang der Verzweigung 42 folgt eine weitere Verzweigung 43, in welcher geprüft wird, ob n = 8m + 4 ist. Zutreffendenfalls wird ein Programmteil aus R8 durchlaufen, in welchem einerseits eine Feinjustierung der Inkrementierung für die Durchsagekennung erfolgt und andererseits für die Bereichskennung E auf einen Mittelwert gesetzt wird.

In ähnlicher Weise erfolgen Verzweigungen des Programms bei 44 bis 48, so daß Programmteile R16, R32, R64, R128, R256 und R256 jeweils in seltenerer Folge durchlaufen werden.

Nach der Demodulation des 57 kHz Hilfsträgers wird - wie eingangs erläutert - eine Binärisierung vorgenommen. Das somit erhaltene Rechtecksignal weist die Frequenz der jeweiligen Kennung, also die der Bereichskennung oder diejenige der Durchsagekennung auf. Wird sowohl eine Bereichskennung als auch eine Durchsagekennung übertragen, so weist bei dem in den USA angewandten Verfahren wegen der Amplitudenabsenkung der Bereichskennung das binäre Signal die Frequenz der Durchsagekennung auf, während sich die Bereichskennung als Tastverhältnismodulation bemerkbar macht. Mit der im Zusammenhang mit den Figuren 2 bis 4 beschriebenen Anordnung wird jedoch nur die Frequenz des binären Signals ausgewertet, so daß bei gleichzeitigem Vorliegen der Bereichskennung und der Durchsagekennung zunächst nur die Durchsagekennung erkannt wird.

Das in Fig. 5 dargestellte System ermöglicht die Erkennung einer zusätzlich zur Durchsagekennung empfangenen Bereichskennnung. Es wird dabei von zwei Funktionsblöcken 51, 52 ausgegangen, die in der bisher beschriebenen Weise jeweils die Erkennung der Durchsagekennung und die Erkennung der Bereichskennung ermöglichen. Das binäre Eingangssignal wird über einen Eingang 53

beiden Funktionsblöcken 51, 52 zugeführt. Dem Funktionsblock 51 kann ein Signal DK am Ausgang 54 entnommen werden, welches das Vorhandensein einer Durchsagekennung angibt, während am Ausgang 55 bei Vorhandensein einer Bereichskennung ein Signal BK ansteht.

Dem Funktionsblock 51 wird ferner ein Signal D0 entnommen, welches einen Umschalter 56 derart steuert, daß bei Nichtvorhandensein einer Durchsagekennung der Eingang des Funktionsblocks 52 direkt mit dem Eingang 53 verbunden ist. Ist jedoch eine Durchsagekennung vorhanden, so wird mit Hilfe des Umschalters 56 anstelle des binären Eingangssignals ein intern erzeugtes Eingangssignal zur Erkennung der Bereichskennung herangezogen. Die Umschaltung erfolgt nicht erst, wenn die Durchsagekennung mit Sicherheit erkannt ist, wenn also das Signal DK über den Ausgang 54 abgegeben wird, sondern bereits bei einem niedrigeren Wert D0 des Integrators i für die Durchsagekennung.

Wenn also bereits eine gewisse Wahrscheinlichkeit für das Vorliegen einer Durchsagekennung vorhanden ist, wird dem Funktionsblock 52 das intern erzeugte Signal zur Bereichskennung zugeführt. Dieses wird dadurch abgeleitet, daß das Referenzsignal für die Durchsagekennung bzw. ein daraus abgeleitetes Signal mit dem tastverhältnismodulierten Eingangssignal verglichen wird. Dazu sind verschiedene Verfahren möglich, von denen eines in Fig. 5 dargestellt ist. Es setzt voraus, daß das binäre Eingangssignal mit einer genügend hohen Frequenz abgetastet wird. Dieses ist bei der im Zusammenhang mit den Figuren 2 bis 4 erläuterten Anordnung mit einer Frequenz von 2,7 kHz gegeben. Die schwache Phasenverschiebung der Flanken des Durchsagekennungssignals werden dann mit genügender Wahrscheinlichkeit erkannt, nämlich mindestens einmal in jeder Halbwelle.

Dazu wird das binäre Eingangssignal in einer Exklusiv-Oder-Verknüpfung 57 mit einer aus den beiden höchstwertigen Bits von P (nämlich dem Inhalt des Phasenregisters 13 (Fig. 2)), das hier als Sollwert für die Phase der Durchsagekennung dient, abgeleiteten Rechteckfolge der Frequenz des höchstwertigen Bits verglichen. Bei Nichtübereinstimmung wird angenommen, daß es sich um eine durch eine Bereichskennung verursachte Flankenverschiebung handelt. Über eine Torschaltung 58 wird der dann vorliegende Wert des Eingangssignals in einen Speicher 59 übernommen. Da die besagte Phasenverschiebung im Takt des Bereichskennsignals erfolgt, liegt am Ausgang des Speichers 59 ein Signal mit der Bereichskennfrequenz an, das wie bereits erläutert im Funktionsblock 52 ausgewertet werden kann.

6

20

25

35

## Ansprüche

1. Anordnung zur Decodierung von Signalen, die zusätzlich zu weiteren Signalen als Modulation von Radiowellen empfangen werden und deren jeweilige Frequenz eine bestimmte Information darstellt,

dadurch gekennzeichnet,

daß in ihr ein Zeitbasissignal konstanter Frequenz erzeugt wird; daß ein Mikroprozessor aus dem Zeitbasissignal ein Referenzsignal mit steuerbarer Frequenz-und Phasenlage ableitet; daß eine Phasen-und/oder Frequenzvergleichsstufe die Frequenz-und die Phasenlage des Referenzsignals in Abhängigkeit von dem empfangenen Signal steuert und ein Ausgangssignal abgibt, wenn eine Übereinstimmung des Referenzsignals mit dem Signal bezüglich der Phase und der Frequenz vorliegt.

2. Anordnung nach Anspruch 1, dadurch gekennzeichnet,

daß das Zeitbasissignal aus der Instruktionsfrequenz des Mikroprozessors abgeleitet wird, derart, daß mindestens im zeitlichen Mittel gleichlange Programmschleifen durchlaufen werden.

3. Anordnung nach Anspruch 2, dadurch gekennzeichnet,

daß der Mikroprozessor nach einem Programm arbeitet, welches mindestens zur Erzeugung des Zeitbasissignals und zur Ableitung des Referenzsignals einschließlich einer Frequenz-und Phasenregelung dient, und daß die mittlere Durchlaufzeit des Programms konstant ist.

4. Anordnung nach einem der vorhergehenden Ansprüche,

dadurch gekennzeichnet,

daß zur Erzeugung des Referenzsignals im Takt des Zeitbasissignals der Inhalt (P) eines L-Bit-breiten Akkumulators um eine Zahl (dP), welche wesentlich kleiner als 2<sup>L</sup> ist, verändert wird und daß die höchstwertige Stelle (MSB) des Akkumulators das Referenzsignal bildet.

5. Anordnung nach Anspruch 4, dadurch gekennzeichnet,

daß ein um 90° phasenverschobenes Referenzsignal dadurch abgeleitet wird, daß die höchstwertige Stelle und die zweithöchstwertige Stelle des Akkumulators exklusiv-oder-verknüpft werden.

6. Anordnung nach Anspruch 4, dadurch gekennzeichnet,

daß die Zahl (dP) in einer vorgegebenen Beziehung zu einer Kennzahl (K) steht, deren Werte vorgegebenen Frequenzen des zu decodierenden Signals zugeordnet sind und daß die Kennzahl (K) selbsttätig variiert wird bis ein Signal empfangen wird, dessen Frequenz der Kennzahl (K) zugeordnet ist.

7. Anordnung nach Anspruch 6, dadurch gekennzeichnet,

daß die Zahl (dP1D, dP2B) innerhalb eines häufig wiederholten Programmteils dem Akkumulatorinhalt hinzuaddiert wird und eine weitere Zahl (dP8D, dP16B) innerhalb seltener durchlaufener Programmteile hinzuaddiert wird.

8. Anordnung nach einem der vorhergehenden Ansprüche,

dadurch gekennzeichnet,

daß das Referenzsignal und ein gegenüber diesem um 90° phasenverschobenes Referenzsignal jeweils mit dem zu decodierenden Signal exklusivoder-verknüpft wird und daß die Ergebnisse der Exklusiv-oder-Verknüpfungen jeweils einem Integrator zugeführt werden.

9. Anordnung nach einem der vorhergehenden Ansprüche zur Decodierung von zwei Signalen verschiedener Frequenz, wobei das erste Signal ausgewählte Frequenzen innerhalb eines ersten Frequenzbereichs einnehmen und das zweite Signal ausgewählte Frequenzen innerhalb eines zweiten Frequenzbereichs einnehmen kann, und wobei ferner das erste Signal oder das zweite Signal einzeln auftreten kann, das zweite Signal jedoch zusätzlich zum ersten Signal auftreten kann, wobei die Amplitude des ersten Signals abgesenkt wird,

dadurch gekennzeichnet,

daß je eine Einrichtung (51, 52) zur Decodierung des ersten und des zweiten Signals vorgesehen ist, daß den Einrichtungen (51, 52) zur Decodierung ein binäres Signal zuführbar ist, das die Frequenz des zweiten Signals und ein vom ersten Signal abhängiges Tastverhältnis aufweist, daß der Einrichtung (52) zur Decodierung des ersten Signals das binäre Signal nur zugeführt wird, wenn das zweite Signal nicht vorhanden ist, und daß bei Vorhandensein des zweiten Signals der Einrichtung (52) zur Decodierung des ersten Signals ein Hilfssignal zugeführt wird, welches durch Vergleich des zugeführten binären Signals und eines zur Decodierung des zweiten Signals abgeleiteten Referenzsignals gewonnen wird.

10. Anordnung nach Anspruch 9, dadurch gekennzeichnet,

daß eine Einrichtung (57, 58) zum Abtasten des binären Signals zu denjenigen Zeitpunkten vorgesehen ist, bei denen das binäre Signal bei Nichtvorhandensein des ersten Signals Flanken aufweist.

7

50

Fig.1

Fig. 2

R:-Nr. 1961

| Programmlauf | 1. | 2. | 3. | 4. | 5. | 6. | 7. | 8.  |   |

|--------------|----|----|----|----|----|----|----|-----|---|

| Programmteil | R1  |   |

| Programmteil | R2 | R4 | R2 | R8 | R2 | R4 | R2 | R16 | а |

| Phase von X    | Soll      | voreilend | nacheilend |

|----------------|-----------|-----------|------------|

| P2=2 MSB von P | 01230     | 01230     | 01230      |

| Χ              | 10011     | 00110     | 11001      |

| Н              | 2 1 2 1 2 | 0 1 0 1 0 | 2 3 2 3 2  |

|                | Ь         | С         | d          |

X eilt um 18° vor:

| P2         | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 2 | 2 | 2 | 2 | 2 | 3 | 3 | 3 | 3 | 3 | 0 | 0 | 0 | 0 | 0 |

|------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Soll von X | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| Χ          | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

| Н          | 2 | 2 | 2 | 2 | 0 | 1 | 1 | 1 | 1 | 1 | 2 | 2 | 2 | 2 | 0 | 1 | 1 | 1 | 1 | 1 | 2 | 2 | 2 | 2 | 0 |

6

| H1= | 0 ,            | ł              | 2              | . 3            |

|-----|----------------|----------------|----------------|----------------|

| 0 . | I=I-2<br>E=E+1 | E=E+1          |                | I=I-2          |

| 1   | E=E+1          | I=[+]<br>E=E+1 | [=[+ <u>]</u>  |                |

| 2   |                | I=[+1          | I=I+1<br>E=E-1 | E=E-1          |

| 3   | I=I-2          |                | E=E-1          | I=I-2<br>E=E-1 |

Fig.3

Fig. 5