n Publication number:

**0 323 919** A1

(12)

## **EUROPEAN PATENT APPLICATION**

(a) Application number: 89300154.5

(51) Int. Cl.4: G 08 C 25/00

22 Date of filing: 09.01.89

3 Priority: 08.01.88 GB 8800411

43 Date of publication of application: 12.07.89 Bulletin 89/28

(B4) Designated Contracting States:

AT BE CH DE ES FR GB GR IT LI LU NL SE

(7) Applicant: SOLRO LIMITED

Tameway Tower P.O. Box 90 Bridge Street

Walsall, WS1 1WX (GB)

(2) Inventor: Gunton, Bruce Stanley

11 Asphodel Badgers Bank Road

Sutton Cold Field West Midlands B74 4ES (GB)

(A) Representative: Frankland, Nigel Howard et al FORRESTER & BOEHMERT Widenmayerstrasse 4/I D-8000 München 22 (DE)

(54) A remote control apparatus.

A remote control apparatus comprises a transmitter to transmit coded signals, and a receiver to receive and decode the signals. The receiver is associated with a plurality of control elements each adapted to be activated in response to the decoding of a predetermined respective signal, and each adapted to remain activated while the receiver continues to receive a signal from the transmitter. Each control element is associated with timing means so that whenever a control element is activated the control element remains activated for at least a period of time as determined by the timing arrangement. This may prevent inadvertent "drop-out" due to voltage drop caused by a power surge. Also each control element is adapted to inhibit operation of the other control element while the first element is actuated and for a brief period of time after the first control element has ceased being actuated.

EP 0 323 919 A1

#### Description

#### A remote control apparatus

5

15

20

25

30

35

45

This invention relates to a remote control apparatus, and more particularly, but not exclusively, to a remote control apparatus for controlling a winch, such as a winch mounted on a motor vehicle.

According to this invention there is provided a remote control apparatus comprising a transmitter adapted to transmit coded signals, and a receiver adapted to receive said signals, decoding means to decode the signals, and a plurality of control elements each adapted to be activated in response to the decoding of a predetermined respective signal, and each adapted to remain activated while the receiver continues to receive a signal from the transmitter.

The control elements may control such functions as the winding in and winding out of a winch, or may control the setting and unsetting of an alarm.

Preferably the decoding means comprise a plurality of decoding elements each adapted to respond to a predetermined respective coded signal, each control element being activated by a respective decoding element.

Conveniently each control element controls a relay.

Preferably, each control element is associated with a timing arrangement so that whenever a control element is activated the control element remains activated for at least a period of time as determined by the timing arrangement.

This invention also relates to a remote control apparatus comprising a transmitter adapted to transmit coded signals and a receiver adapted to receive said signals, decoding means to decode the received signals and a plurality of control elements, each activated in response to the reception of a predetermined coded signal, each control element being associated with a timer so that whenever a control element is activated by a coded signal it remains activated for a period of time determined by

Preferably each control element is adapted to inhibit each other control element when it is actuated.

Conveniently each control element is also adapted to inhibit each other control element for a predetermined period of time after the first said control element has ceased to be activated.

Advantageously each control element comprises a circuit consisting of a plurality of interconnected logic gates, said timing arrangement being associated with selected gates and being adapted to maintain a predetermined logic signal on at least one selected input of at least one gate to maintain at least said gate in a predetermined condition for said period of time as determined by the timing arrangement to maintain the control element activated for said period of time.

Preferably each control element comprises two NOR gates, the output of the first NOR gate being an input of the second NOR gate, the output of the second NOR gate being the controlling signal generated by the control element, the output of the second NOR gate being fed via a capacitor, which comprises the timing arrangement, to an input of the first NOR gate to maintain the first NOR gate in such a condition that the respective control element is maintained activated for said period of time as determined by the timing arrangement.

Conveniently each control element comprises a circuit consisting of a plurality of interconnected logic gates, the output of at least one selected gate of each control element being fed to an input of at least one selected gate of the other control element in order to inhibit the other control element when the first said control element is actuated.

Preferably timing means are provided associated with said connections between selected gates of each control element in order to maintain the inhibition of said other control element for a predetermined period of time after the first said control element has ceased to be activated.

Advantageously each control element comprises two NOR gates, the output of the first NOR gate being an input of the second NOR gate, the output of the second NOR gate being the controlling output signal of the control element, the output of the second NOR gate being fed to an input of the second NOR gate of the other control element.

Conveniently the output of said second NOR gate is also supplied to charge a capacitor which is connected to the said input of the second NOR gate of the other control element so that when there is an output on the said second NOR gate of the first control element, so that the first control element is activated, the second NOR gate of the other control element is inhibited, thus preventing the other control element from being activated, the second NOR gate remaining inhibited until the capacitor is at least partly dis charged.

Preferably the coded signals comprise pulse coded signals.

The transmitter may be a radio transmitter, an infra-red transmitter, or an ultra-sonic transmitter.

If it is a radio transmitter it is preferred that said radio transmitter comprises an oscillator, amplifier means to amplify the output of the oscillator, and code generating means generating pulses, the pulses controlling the supply of power to the amplifying means so that the signal from the oscillator is only amplified in accordance with the code generated by the code generator.

Preferably the code generating means comprises an integrated circuit, at least two switch means being connected to the integrated circuits which can be selectively operated to cause the integrated circuit to generate either a first code or a second code.

The apparatus may control a winch.

Preferably the apparatus further incorporates a bi-stable memory element to control an alarm, the bi-stable element being controllable from the transmitter.

In one embodiment two further decoding elements control the said bi-stable element.

Preferably the two further decoding elements serve to alter the condition of the bi-stable memory element, the condition of the memory element determining if the alarm is set or un-set.

Alternatively the said bi-stable memory element is adapted to be triggered in response to signals generated by said control elements, manual switch means being provided to activate either the alarm or an arrangement controlled by the control elements.

In order that the invention may be more readily understood, and so that further features thereof may be appreciated, the invention will now be described by way of example with reference to the accompanying drawings in which:

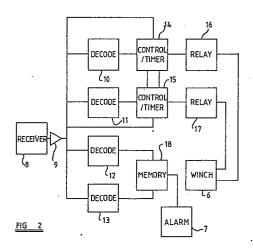

FIGURE 1 is a block diagram of a remote control apparatus in accordance with the invention,

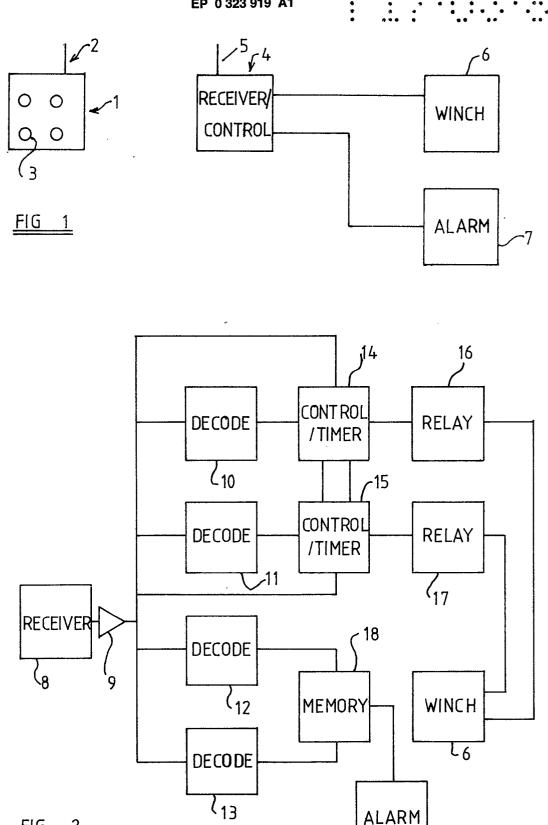

FIGURE 2 is a block diagram of the receiver, alarm and winch, mounted on a motor vehicle,

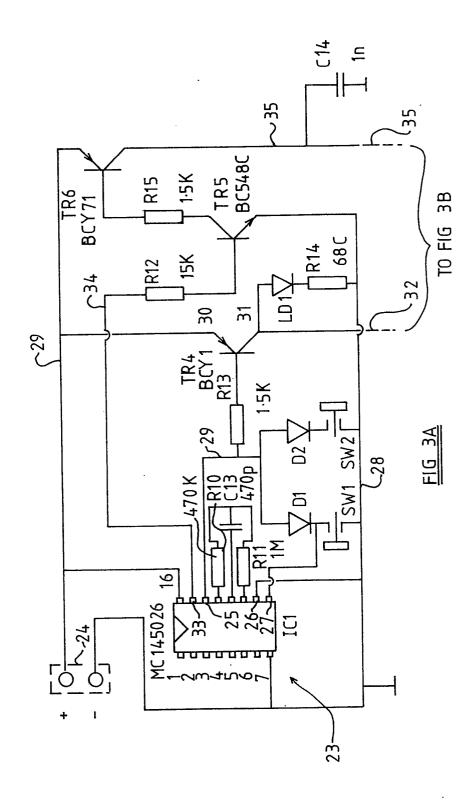

FIGURE 3 is a circuit diagram of an alternative transmitter, and

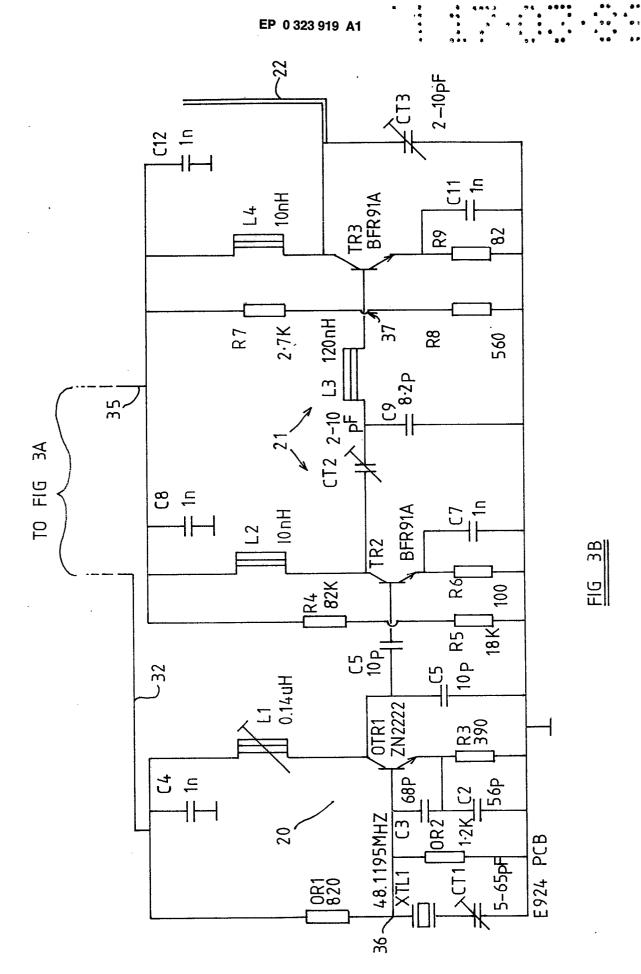

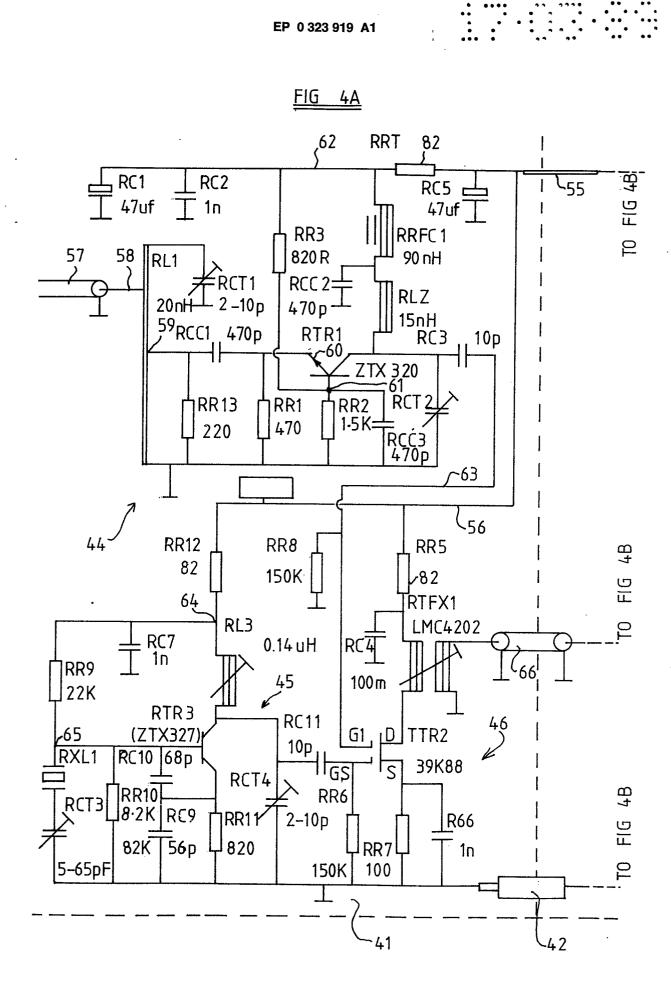

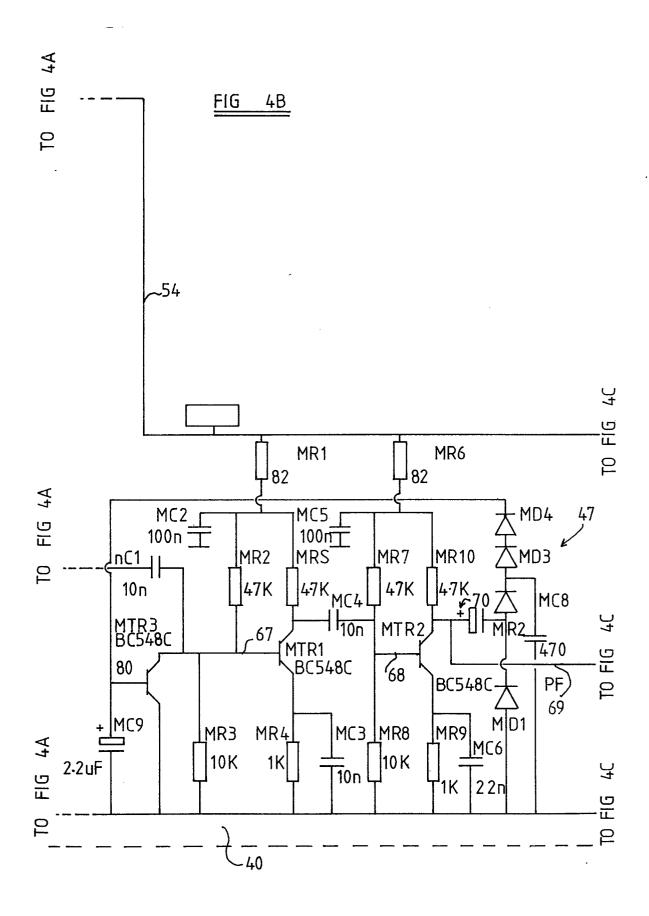

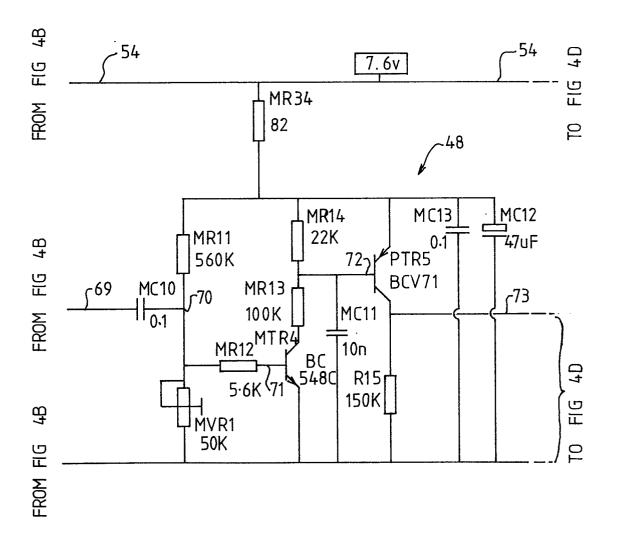

FIGURE 4 is a circuit diagram of an alternative receiver.

One example of a remote control apparatus in accordance with the invention is intended to control a winch mounted on a motor vehicle and also to control an alarm device on the vehicle. Thus the remote control apparatus comprises a hand held battery powered radio transmitter 1, having a transmitting aerial 2. The transmitter 1 has a plurality of control buttons 3, each of which may be pressed to send a separate command. In this embodiment four buttons are shown which may be pressed to make a winch wind in, to make the winch pay out, to set an alarm and to un-set an alarm.

Signals transmitted by the transmitter 1 are received by a receiver/control device 4, mounted on the motor vehicle which has an aerial 5, and which is connected to a winch 6 and an alarm 7.

The transmitter is adapted to transmit signals of a single frequency, the signals being coded, so that a different signal is transmitted whilst each different button 3 is pressed down. The signals may be pulse coded signals, each signal thus comprising a number of pulses of different lengths and/or with different time spacings between the pulses.

Referring now to Figure 2, the receiver/control device 4 comprises a radio receiver 8 adapted to receive the signals transmitted by the transmitter 1. The output from the receiver 8, which may be filteredand processed in other ways, is amplified by an amplifier 9, and is then fed to a plurality of decoding elements 10, 11, 12 and 13. Each decoding element is adapted to decode the signal transmitted when a respective one of the four buttons 3 is pressed.

The decoding elements 10 and 11 are each connected to a respective control element 14 or 15, and thus the appropriate control element is activated whenever the appropriate button is pressed. Each control element 14, 15 is connected to, and controls, a respective relay 16, 17, which cause the winch 6 to wind in or to wind out.

Thus, when an appropriate button 3 on the transmitter 1 is pressed a coded signal is transmitted by the transmitter, and is received by the receiver 8, and is amplified, and decoded by the appropriate decoding element 10, thus activating the appropriate decoding element and the respective relay which will cause the winch to operate as desired.

When the relay is activated and the winch starts, or stops, operating there a various surge currents and noise, which might cause an interruption in the received signal from the transmitter. Thus the control elements 14 and 15 each incorporate a timing arrangement adapted to maintain the respective relay in the actuated condition for at least a predetermined period of time, such as 200 milliseconds after the decoder element has decoded the appropriate signal and activated the control element.

Also each control element 14, 15 is adapted when actuated, to inhibit the other control element, and to keep the other control element inhibited for a period of time, such as three seconds, after the first control element ceases to be activated. This prevents problems that may arise if someone presses two of the buttons 3 simultaneously. Also this prevents the winch from being moved immediately from a condition in which it is winding in to a condition in which it is winding out (or vice versa) which can cause very large current flows to arise which can damage the winch.

When the winch is paying out, if the operator moves with the end of the winch cable the transmitter will move further away from the receiver, and thus the strength of the received signal may diminish and the received signal may be corrupted. Each control element 14, 15, thus directly receives the output of the amplifier 9 and will not de-activate the respective relay 16,17 when once activated, until the signal from the amplifier 9 ceases. Thus, even if the signal is corrupted, the winch wil keep operating once it has been started, provided that the operator keeps pressing the appropriate button 3.

The two decoding elements 12, 13 are connected to a memory 18 which is a bi-stable memory. The state of the memory determines whether the alarm 7 is set or un-set. It will be appreciated that a signal decoded by one decoding element, such as the element 12 will thus set the alarm, and a signal received by the other decoding element, such as element 13, will un-set the alarm.

The alarm may be of any convenient form, providing protection for the vehicle on which the winch is fitted, but it is preferred that the alarm includes a circuit which passes through the winch, for example passing through the electric plug that connects the winch to the power supply, so that if the winch is disconnected from the vehicle the alarm will operate. The alarm may be a visible and/or an audible alarm.

In an alternative embodiment of the invention, which will now be described, the transmitter is only provided with two control buttons, and the receiver is provided with an adjustable switch which can be manually operated to determine which function the two control buttons on the transmitter will control.

65

40

45

50

Referring now to Figure 3 of the accompanying drawings the circuit diagram of such a transmitter is shown.

The essential components of the circuit are mounted on a printed circuit board E924PCB.

The transmitter effectively comprises an oscillator arrangement 20 which is adapted to run continuously when an appropriate switch is pressed, and an amplifier arrangement 21 which amplifies signals from the oscillator and feeds them to an amtenna wire 22, the amplifier being adapted to be activated for only brief successive periods of time, thus effectively coding the transmitted signal. The amplifier arrangement 21 is thus controlled by a code generator arrangement 23.

The board is provided with terminals 24 to be connected to an appropriate battery. Connected directly to the terminals 24 are the power input terminals of integrated circuit IC1 (MC145026). This is an integrated circuit having eight pins which can be selectively connected to ground, to a positive potential, or left floating, which then cause the integrated circuit to generate particular distinctive codes when an enable pin 25 is connected to earth.

Various other pins are associated with a resistive and compacitive bridge R10,C13, R11. The pin 26 is connected to earth. The pin 27 is a coding pin, and it can be seen that this pin is connected to the junction between the diode D1 and switch SW1. The diode D1 and Switch SW1 are connected in parallel with a second diode D2 and second switch SW2 between the earth rail 28 and the two diodes D1,D2 are connected to a lead 29 which is connected to the enable pin 25. The lead 29 is also connected by means of resistor R13 to the base of transistor TR4 (BCY71), the collector 30 of which is connected to the positive rail 29 and the emitter 31 of which is connected to a light emitting diode LD1 which is connected in series with a resistor R14 to the earth rail 28, the emitter 31 also being connected by means of a lead 32 to the oscillator arrangement 20. The integrated circuit 1Cl has an output pin 33 which is conected to lead 34.

It is to be appreciated that when the switch SW1 is depressed, the coding pin 27 is effectively earthed, and also the enable pin 25 is effectively earthed through the lead 29 and the diode D1. The integrated circuit IC1 thus generates a predetermined code which appears at the pin 33 and passes through lead 34. Simultaneously, however, the base of the transistor TR4 is reduced to earth, thus opening the switch that is effectively constituted by the transistor TR4. Power from positive rail 29 thus passes through the light emitting diode LD1, providing a visual indicating to the operator of the switch that the switch has been operated correctly, and also power is supplied, whilst the switch SW1 is depressed, through the lead 32 to the oscillator circuit 20.

A similar situation exists if switch SW2 is pressed only this time there is no earth signal present on the pin 27 and thus the integrated cirucit IC1 generates a different code.

The coded signal on line 34 passes through resistor R12 to the base of amplifying transistor TR5 (BC540C) and again the relevant signal passes

through resistor R15 to the base of transistor TR6 (BCY71), the output of which is on line 35. The collector of transistor TR6 is connected to the positive rail, and the emitter is connected to line 35. The line 35 is connected to one terminal of a capacitor C14, the other terminal of which is connected to earth. The line 35 leads to the amplifier arrangement 21.

The oscillator circuit 20 receives power through the line 32. The line 32 is effectively connected to one terminal of a capacitor C4 the other terminal of which is connected to earth. The line 32 is connected, through resistor 0R1 to one terminal 36 of an oscillating crystal XTL1. The other terminal of the crystal is connected by means of an adjustable capacitor CT1 to earth. Connected in parallel with the crystal and the variable capacitor is a resistor 0R2 and a capacitor bridge C3 C2 comprising two capacitors in series. The terminal 36 is connected to the base of a transistor OTR1 (2N2222) the collector of which is connected by means of an adjustable inductance L1 to the line 32 and the emitter of which is connected to the node between the two capacitors C2 C3 and also connected by means of resistor R3 to earth. The collector of the oscillating transistor 0TR1, which effectively forms the output of the oscillator circuit, is connected to one terminal of capacitor C6, the other terminal of which is connected to earth, and to one terminal of capacitor C5 the other terminal of which is connected to the amplifying arrangement 21.

It will be readily understood that when power is supplied through the lead 32 the crystals XTL1 will oscillate, and the transistor 0TR1 will provide an output comprising an oscillating signal. The selected frequency of oscillation for the crystal is 48.1195MHz.

The terminal of the capacitor C5 connected to the amplifying arrangement 21 is initially connected to the node point between two resistors R4,R5 which are effectively connected between the line 35 and earth. The node point is also connected to the base of a first amplifying transistor TR2 the collector of which is connected to the line 35 by means of an inductance L2, and the emitter of which is connected to a resistor R6 and a capacitor C7 which are connected in parallel to the earth rail.

The line 35 is effectively connected to one plate of a capacitor C8 the other plate of which is connected to earth. The collector of the transistor TR2 and the inductance L2 is connected by means of an adjustable capacitor C2, and an inductance L3 to a further node 37 between two resistors R7,R8 which are connected between the line 35 and earth. A capacitor C9 is con nected between the junction between the capacitor C2 and the inductance L3 and earth.

The transistor TR2 (BFR91A) and the associated circuitry just described effectively comprise a first amplifier stage.

The node 37 is connected to the base of a second amplifying transistor TR3 (BFR91A) the collector of which is connected by means of an inductance L4 to the line 35 and the emitter of which is connected to earth through the parallel connection of resistor R9

and capacitor C11. The collector of transistor TR3 is connected directly to the antenna wire 22, and is also connected by means of an adjustable capacitor CT3 to earth. A capacitor C12 is connected between the lead 35 and earth.

It will be appreciated that when the switch SW1 is depressed, the light emitting diode LD1 will emit light and also power will be supplied through the lead 32 to the oscillator arrangement 20. The oscillator will be activated, and will generate continuous oscillations which are supplied, via capacitor C5, to the amplifier arrangement 21. However, whilst the button SW1 is depressed the integrated circuit IC1 will generate a predetermined pulse code, which may be a code defined by the pulse width of succeeding pulses. This code is generated on pin 33 and is thus amplified by transistors TR5 and TR6. Thus power is supplied to the amplifier circuit 21 through the lead 35 only in accordance with the code. When power is supplied to the amplifier arrangement 21 the oscillations present at capacitor C5 are amplified by the two-stage amplifier constituted by the two transistors TR2 and TR3 and the amplified signal is supplied to the antenna wire and is thus transmitted.

When the switch SW2 is pressed a similar situation exists, only in this case the integrated circuit IC1 generates a different code, and thus this different code is transmitted.

When either the button SW1 or the button SW2 is released the light emitting diode LD1 is extinguished and also the supply of power to the oscillator circuit 20 and the to the amplifier 21 is terminated.

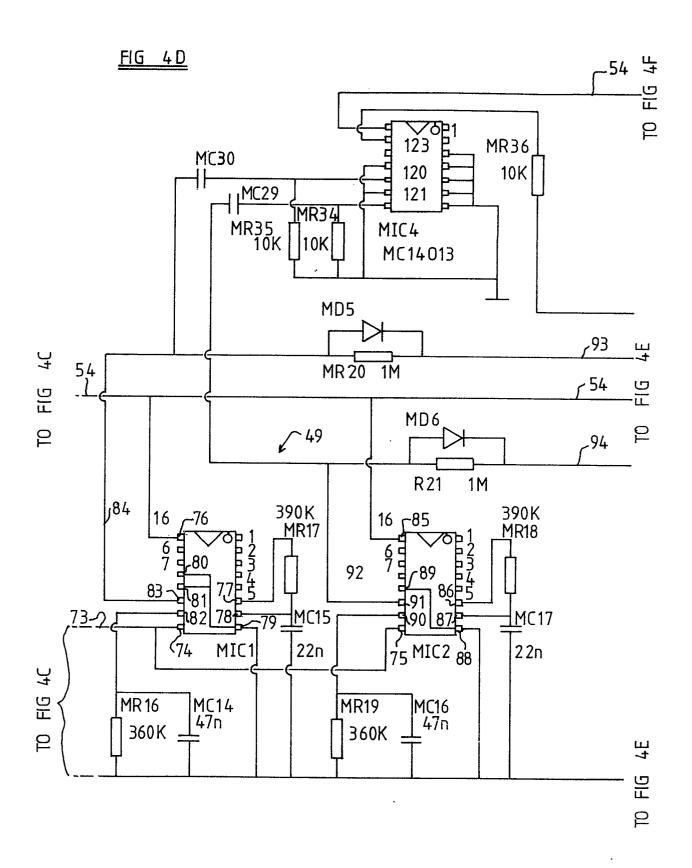

Figure 4 illustrates a receiver intended for use with the transmitter illustrated in Figure 3.

The receiver comprises various components, the majority of which are mounted on a main printed circuit board 40 (E825), but some of which are mounted on a so-called piggy-back board 41 (E526) which is mounted, by means of pillars, on the main board. One of the pillars 42 acts to establish an earth link between the two boards, and various other links exist between the boards in question.

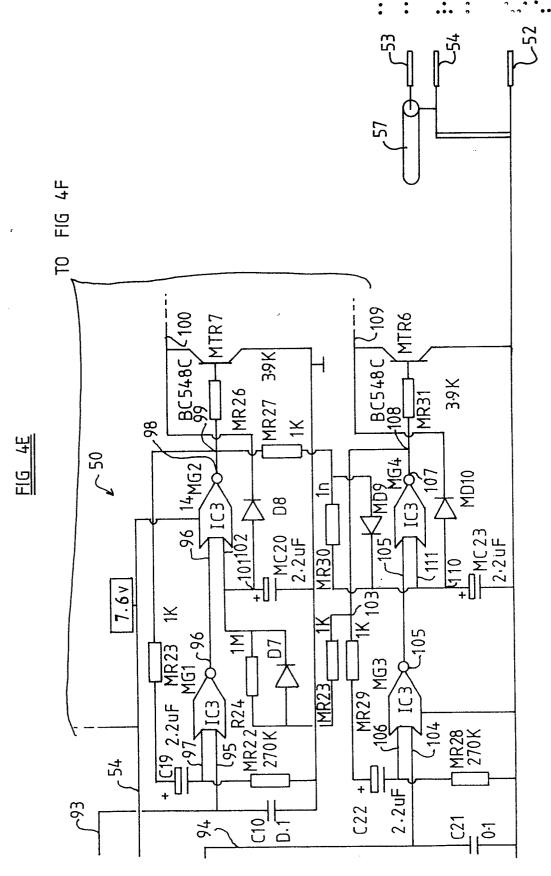

The illustrated receiver circuit is adapted to be connected to any appropriate voltage between 10 and 28 volts and incorporates a power supply regulator 43 which is adapted to supply 12 volts on one lead and 7.6 volts on another lead, regardless of the input voltage. The receiver includes an initial signal receiving and amplifying arrangement 44 and an oscillator arrangement 45. Signals from the amplifying arrangement 44 and the oscillating arrangement 45 are mixed in a mixing arrangement 46 on the super-heterodyne principle. This occurs on the piggy-back board 41. Subsequently the signals are transferred to an amplifying arrangement 47 on the main board, and the signal is demodulated in a demodulating stage 48, the signal then being fed to a decoding arrangement 49. The decoding arrangement effectively comprises two circuits each responsive to a predetermined code. When a circuit receives the predetermined code it provides an appropriate output signal. the output signals are fed to a logic arrangement 50 which comprises two identical circuits which are mutually interconnected. These identical circuits comprise control elements

which control relays. Thus the effect of the logic arrangement is such that when one predetermined code is detected, an appropriate output signal is generated, which may control a relay which actuates a winch or the like, causing the winch to winch in, whereas when the other predetermined code is detected another solenoid is activated which causes the winch to winch out. The interconnection between the various components of the logic arrangement 50 are such that once a signal has been received to commence winching, the winching operation will be commenced and maintained for a predetermined period of time even if the supply voltage drops due to, for example, a load applied to the battery supplying the system as a result of the commencement of the winching operation. Also the arrangement will be such that winching in cannot be commenced until a predetermined period of time has elapsed subsequent to winching out.

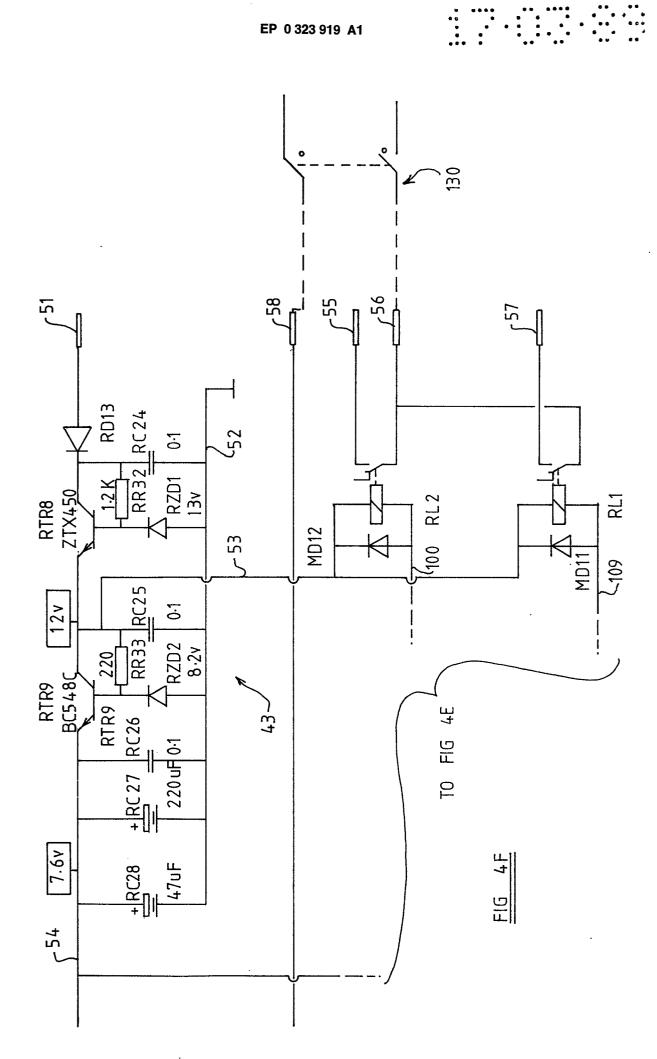

It can be seen that the main board 40 is provided with terminal 51 adapted to be connected to a battery having a potential between 10 volts and 28 volts and a terminal 52 adapted to be connected to ground. Also the board is provided with a terminal 53 to be connected to the core of a co-axial wire extending from a receiving aerial to the board, and a terminal 54 to be connected to the screen of the aerial. Furthermore the board is provided with further terminals comprising terminals 55,56,57, terminal 56 being adapted to be connected to a common power input for a winch, term inal 55 being adapted to be connected to the "in" terminal of the winch and terminal 57 being adapted to be connected to the "out" terminal of the winch. A further terminal 58 is adapted to be connected to an arm/disarm relay present on an alarm device.

The terminal 51 is connected to a power regulating arrangement 43. The terminal 51 is thus conected through a diode RD13 to the collector of a transistor RTR8 (ZTX450) the base of which is connected through a Zener diode RZD1 having a 13 volt nominal voltage, to an earth rail 52. The node between the diode RD13 and the transistor RTR8 is connected through a capacitor RC24 to the earth rail 52 and through a resistor RR32 to the base of the transistor RTR8.

The voltage present on the emitter of the transistor RTR8 is supplied, at a nominal 12 volts, to line 53 and is also supplied to the collector of a further transistor RTR9 (BC548C) the base of which is connected through a Zener diode RZD2 having a nominal voltage of 8.2 volts to the earth rail 52. The collector of the transistor RTR9 is connected to earth through a capacitor RC25 and is also connected to the base of the transistor RTR9 through resistor RR33. The emitter of the transistor RTR9 supplies a nominal 7.6 volts to the line 54, the voltage supplied to this line being smoothed by capacitors RC26, RC27 and RC28 which are connected in parallel between the line 54 and the earth line 52.

It will thus be appreciated that if a voltage between 10 and 28 volts is applied to the terminal 51 a regulated voltage of a nominal 12 volts will be present on the line 53 and a regulated and smoothed voltage of 7.6 volts will be present on the line 54. The

30

line 54 effectively comprises the positive rail for the components on the board 40, and, via a wire link 55 is also connected to the positive rail 56 present on the piggy-back board. The voltage of 12 volts present on the line 53 is provided mainly to drive solenoid relays, as will be described hereinafter.

The terminals 53,54, which are to be connected to the aerial, are connected by means of a co-axial link 57 to the circuitry present on the piggy-back board 41. The screen of the co-axial link 57 is connected to earth, but the core 58 is connected to a tap provided part way along an inductor RL1, adjacent one end of the inductor which is connected by means of an adjustable capacitance RCT1 to earth. The other end of the inductor RL1 is connected directly to earth, whereas a central tap 59 is connected to one terminal of a capacitator RCC1 and to one terminal of a resistor RR13 which is connected to earth. The other terminal of the capacitor RCC1 is connected to a resistor RR1 which is connected to earth and the said other terminal of capacitor RCC1 is also connected to the emitter 60 of a transistor RTR1 (ZTX320) the base of which is connected to a node 61. The node 61 is connected by the parallel connection of a resistor RR2 and a capacitor RCC3 to earth. The node is also connected by means of a resistor RR3 to a line 62. The line 62 is connected to earth by the parallel connection of capacitors RC2 and RC1, and is also connected through resistor RR4 and via a capacitor RC5 which acts as a smoothing capacitor to the line 56 which supplies the voltage of 7.6 volts. The line 62 is also connected to the collector of the transistor RTR1 by a serial connection of inductances RRFC1 and RLZ, the central node of which is connected to earth by means of a capacitor RCC2.

The collector of the transistor RTR1 is also connected to earth by means of a variable capacitor RCT2 and to an output coupling capacitor RC3.

The transistor RTR1 acts as a signal amplifying transistor, and the described reactive components constitute a tuning circuit which would, of course, be tuned to the frequency of transmission of the transmitter. It will thus be appreciated that the signal passing through the capacitor RC3 to the line 63 is effectively the desired input signal which has been appropriately amplified.

The crystal oscillator circuit 45 is very similar to the crystal oscillator circuit present in the transmitter. The crystal oscillator circuit receives power from the line 56 through resistor RR12 and associated node 64. The node 64 is connected to earth through capacitor RC7 and is also connected through resistor RR9 to a further node 65. The node 65 is connected to one terminal of the oscillating crystal RXTL1, the other terminal of which is connected through an adjustable capacitor RCT3 to earth. The node 65 is also connected to earth by means of a resistor RR10 and by the two serial capacitors RC10,RC9 connected in parallel with resistor RR10. The node 65 is also connected to the base of a transistor RTR3 (ZTX327). The collector of transistor RTR3 is connected to node 64 by means of an adjustable inductance RL3, and is also connected to earth by means of an adjustable capacitor RCT4. The emitter of transistor RTR3 is connected to earth by means of a resistor RR11 and is also connected to the node between the capacitors RC9 and RC10.

The described arrangement produces oscillations corresponding to the oscillations generated by the oscillator present in the transmitter, but at a slightly different frequency and these oscillations are fed through a capacitor RC11 to a gate G2 formed on a field effect transistor TTR2 (39K88). The gate G2 of the transistor TTR2 is connected to earth by means of a resistor RR6. The field effect transistor is a two-gate transistor and gate G1 is connected to line 63 which receives the amplified input signals. The line 63 is connected to earth through a resistor RR8.

It will be appreciated, therefore, that the two gates of the field effect transistor TTR2 respectively receive the amplified desired input signal and oscillations from the oscillator circuit 45. The field effect transistor thus acts as a super-heterodyne mixer, producing an output signal of an appropriate form

The source of the field effect transistor TTR2 is connected to earth by the parallel connection of a resistor RR7 and a capacitor RC6. The drain is connected through one winding of an inductive signal transfer device or transformer RTFX1 (LMC4202) and through a resistor RR5 to the line 56 which supplies the potential of 7.6 volts. The node between the resistor RR5 and the transformer RTFX1 is connected to earth by means of a capacitor RC4.

The output coil of the transformer RTFX1, which may have a gain of only one, is connected by means of a co-axial link 66 to the main board 40.

The signal from the co-axial link 66 passes through an isolating capacitor MC1 to the base 67 of an intermediate frequency amplifying transistor MTR1. The emitter of the transistor MTR1 is connected to earth by the parallel connection of a resistor MR4 and capacitor MC3 and the collector is connected by means of a resistor MR5 and a resistor MR1 in series to the line 54. The node between the resistors MR5 and MR1 is connected by a resistor MR2 to the base 67 of the amplifying transistor MTR1 and by means of a capacitor MC2 to earth. The output of the amplifying transistor MTR1 present on the collector thererof passes through capacitor MC4 to the base 68 of second amplifying transistor MTR2 (BC548C). The base 68 of transistor MTR2 is connected to earth through resistor MR8.

The emitter of transistor MTR2 is connected to earth by the parallel connection of a resistor MR9 and capacitor MC6. The collector of transistor MTR2 is connected by the series connection of resistors MR10 and MR6 to the rail 54. The node between the resistors MR6 and MR10 is connected by resistor MR7 to the base 68 of the transistor MTR2 and is also connected by means of capacitor MC5 to earth. The output of the second amplifying transistor MTR2 is provided on lead 69.

The output present on the collector of transistor MTR2 is also supplied to one terminal of an electrolytic capacitor 70 forming part of an automatic gain control arrangement. The other terminal of the capacitor 70 is connected to the node between two

65

40

diodes MD1,MD2 forming part of a serial connection of four diodes, the connection incorporating diodes MD3 and MD4. Diode MD1 is connected to the earth rail. The node between diodes MD2 and MD3 is connected by means of a capacitor MC8 to the earth rail. The diode MD4 is connected to the base 80 of a transistor MTR3 (BG548C) the emitter of which is connected to earth and the collector of which is connected to the base 67 of the transistor MTR1. The base 67 of a transistor MTR1 is connected to earth by means of resistor MR3. The base 80 of transistor MTR3 is connected to earth by means of electrolytic capacitor MC9.

The transistors MTR1,MTR2 serve as a two-stage intermediate frequency amplifier, provided with an automatic gain control formed by the diodes MD1,MD2,MD3,MD4, and the associated transistor MTR3

The output signal comprises an amplified signal present on the line 69 which is then passed to the demodulating arrangement 48 through a coupling capacitor MC10 which is connected to a node .70 between a variable resistor MVR1 which is connected to earth and a series connection of two resistors MR11 and MR34 which connect to the rail 54 supplying the voltage of 7.6 volts. The node 70 is also connected, by means of resistor MR12 to the base 71 of a transistor MTR4 (BC548C), the emitter of which is connected to earth and the collector of which is connected by resistors MR13,MR14 in series and through the resistor MR34 mentioned above to the rail 54. The node between resistors MR14 and MR13 is connected via capacitor MC11 to earth and is also connected to the base 72 of a second amplifying transistor MTR5 (BCV71) the collector of which is firstly connected to the rail 54 through the resistor MR34 mentioned above and is secondly connected to earth by the parallel connection of two transistors MC13 and MC12. The emitter of transistor MTR5 is connected by means of resistor R15 to earth and also provides an output on output line 73 which passes to the decoding arrangement 49.

The transistors MTR4 and MTR5 serve to demodulate the signal supplied on line 69 and thus the output signal present on line 73 is effectively a square wave signal, the width of each cycle of the square wave signal being dictated by the width of a pulse transmitted by the transmitter.

It can be seen that the line 73 is connected to pin 74 of integrated circuit MIC1 and to corresponding pin 75 of integrated circuit MIC2. Integrated circuit MIC1 and integrated circuit MIC2 are both MC145028.

Integrated circuit MIC1 has terminal 76 thereof connected to the line 54 supplying a potential of 7.6 volts, terminal 77 thereof connected to earth through the serial connection of resistor MR17 and capacitor MC15 and terminal 78 thereof connected to the node between resistor MR17 and capacitor MC15. Terminal 79 is connected to earth and is also connected to coding terminals 80,81. The terminal 82 is connected to earth by the parallel connection of resistor MR16 and capacitor MC14. When wired in this way the circuit will provide a predetermined output an output

terminal 83, which is connected to line 84 when an appropriate pulse coded signal is received on input pin 74.

Integrated circuit MIC2 is wired in a similar, but slightly different way. Terminal 85 is connected to the rail 54 supplying potential of 7.6 volts. Terminal 86 is connected to earth through the serial connection of resistor MR18 and capacitor MC17. The node between resistor MR18 and capacitor MC17 is connected to terminal 87. Terminal 88 is connected to earth and is also connected to the single terminal 89. Terminal 90 is connected to earth by the parallel connection of resistor MR19 and capacitor MC16.

When an appropriately coded signal is received on pin 75, an output is provided on terminal 91 which leads to line 92.

It will thus be appreciated that when one predetermined signal is received, corresponding to depression of the switch SW1 of the transmitter, an output is provided on line 84, whereas when another predetermined coded signal is provided, corresponding to depression of switch SW2, an output is provided on line 92.

Line 84 passes the serial connection of diode MD5 and resistor MR20 to become line 93. Line 92 passes the serial connection of diode MD6 and resistor R21 to become line 94.

The lines 93 and 94 are fed to a logic arrangement 50 which is exemplified in a single integrated circuit MC14001B, but which is illustrated in a logic form.

Line 93 is fed to one input 95 of a NOR gate MG1 which is adapted to provide a low output at an output 96 in response to a high signal appearing on either the input 95 or a second input 97. The output of the NOR gate MG1 is connected to one input of a second NR gate MG2 of a similar design, having an output 98. The output 98 is connected to a node 98 which in turn is connected through a resistor MR26 to the base of a transistor MTR7 (BC548C). The emitter of transistor MTR7 is connected to earth and the collector is connected to a line 100 which extends to a parallel connection between a diode MD12 and the windings of a relay RL2 which actuates a switch to establish a connection between the common terminal 56 and the "in" terminal 55. The parallel connection between the diode MD12 and the coil of the relay RL2 extends to the line 53 which carries a nominal potential of 12 volts.

The collector of the transistor MTR7 is also connected by means of a diode MD8 to a node 101 between a capacitor MC20 which is connected to earth and a second input 102 of the gate MG2. The node 101 is also connected by means of resistor R24 in parallel with di ode D7, this parallel connection being in series with a further resistor MR23 to a node 103

The line 94 is fed to a similar circuit arrangement and is thus fed to one input 104 of a NOR gate MG3 which is adapted to provide a low output at an output 105 in response to a high signal appearing on either the input 104 or a second input 106. The output 105 of the NOR gate MG3 effectively forms the input 105 of a second NOR gate MG4 of corresponding design. The NOR gate MG4 has an output 107 which is connected to a node 108 which in turn is

connected through a resistor MR31 to the base of a transistor MTR6 (BC548C). The emitter of the transistor MTR6 is connected to earth and the collector is connected to a line 109 which extends to a parallel connection between a diode MD11 and the windings of a relay RL1 which actuates a switch to establish a connection between the common terminal 56 and the "out" terminal 57. The parallel connection between the diode MD11 and the coil of the relay RL1 extends to the line 53 which carries a potential of 12 volts.

13

The collector of the transistor MTR6 is also connected by means of a diode MD10 to a node 110 between a capacitor MC23 which is connected to earth and a second input 111 of the NOR gate MG4. The node 110 is also connected by means of a resistor MR30 in parallel with a diode MD9, this parallel connection being in series with a further resistor MR27 to the above-mentioned node 99.

Input 104 to the NOR gate MG3 is connected to earth through capacitor C21. Input 106 to NOR gate MG3 is connected to a node between a resistor R28 which extends to earth, and the serial connection of cap acitor C22 and resistor MR29 which extends to the above-mentioned node 103.

Initially the inputs 91, 95, 106 and 104 of the two NOR gates MG1 and MG3 are all low, and consequently the outputs 96 and 105 are high. Thus the inputs 96 and 105 of the NOR gates MG2 and MG4 are high, thus making the outputs 98 and 107 low. Since a logic low is applied to the bases of the transistors MTR7 and MTR6 both of these transistors are effectively switched off and no current flows through the coils of the relays RL2 or RL1. Capacitors MC20,MC23 are discharged, and since the signals at nodes 99,108 are low, a logic low is applied to inputs 102, 111 of the NOR gates MG2.MG4.

If an appropriate signal is decoded by the integrated circuit M1C1 a signal is supplied to the line 84, and immediately passes through the diode MD5, to the line 93 and to the input 95 of the NOR gate MG1. This signal also serves to charge capacitor C10. Since a logic high is placed on the input 95 a logic low is provided at the output 96. Thus a logic low is applied to input 96 of the second NOR gate MG2. As is clear from the above explanation a logic low is present on the input 102 to the logic NOR gate MG2, and thus both the inputs to the gate comprise a logic low. Consequently the output of the gate 98 becomes a logic high. This high effectively serves to switch on the transistor MTR7 A current flow passes thus established from the line 53, supplying potential of 12 volts, through the windings of the relay RL2, and through the controlled current path of the transistor MTR7 to earth. Consequently the relay is energised thus effecting an electrical connection between the common terminal 56 and the winding in terminal 55. Power is thus supplied to a winch or the like to effect winding in. This supply of power may well come from the battery that is connected to the terminal 51, thus temporarily draining the battery as the initial surge of current flows through the motor in the winch. This drain on the battery may cause the potential provided by the

voltage regulator 43 to fluctuate. Consequently the signal provided from M1C1 through the line 84 and the line 93 may tend to drop. Of course, if the signal does drop the described arrangement may effectively switch off the transistor MTR7, causing the winch immediately to cease operation.

However, the illustrated embodiment has means to prevent such an event occuring. It is to be noted that the node 99 is connected by means of the resistor MR25 to the capacitor C19. Thus, when the node 99 initially goes high, the capacitor C19 will charge up. This will effectively maintain a high on the second input 97 of the logic gate MG1 at least until the capacitor C19 discharges through the resistor MR22 which is a very high value resistor. Consequently, when the NOR gate MG1 is initially made to provide a low output, a feed-back is applied to the gate MG1 to maintain it in that condition for at least a brief period of time. The period of time that it is maintained in condition is dependent upon the time constant established by the capacitor C19 and the resistor MR22.

Also if the signal present on line 93 drops, due to potential fall as a consequence of a power surge, the capacitor C10 must first discharge before the signal on input 95 charges.

It can be seen that the node 99 is also connected by means of the resistor MR30, the resistor MR19 diode MD9 to the capacitor MC23, which is also connected to the second input of the second NOR gate MG4. Thus, whilst the node 99 is maintained with a logic high, the capacitor MC23 is remained in a charged state. Once the node 99 goes to a logic low, and the relay RL2 closes, the capacitor MC23 must become at least partially discharged, removing the logic high that is applied to the input 110 from the charge present on capacitor MC23 before the logic gate MG4 can enter a condition in which the output 108 thereof has a logic high. Thus there is always a pause of a predetermined minimum length between switching off the relay RL2 and activating the relay RL1

It can be seen that whilst means have been described which ensure that when a logic high is applied to the NOR gate MG1, there is an immediate feed-back to maintain logic gate MG1 in the desired condition, similar means exist with regard to logic gate MG3, as constituted by the resistor MR29, the capacitor C22 and the further resistor MR28 which correspond, of course, to the resistor MR25, the capacitor C19 and the resistor MR22. Similarly it is to be noted that whilst it is not possible to make the NOR gate MG4 have a logic high output very switfly after switching off the relay RL2, by virtue of the capacitor MC23, the capacitor MC20 associated with the logic gate MG2 provides a similar feature, so that the relay RL2 cannot be switched on too rapidly after switching off the relay RL1.

It is to be noted that the lead 84 is connected, via a coupling capacitor MC30 to an input terminal 120 on an integrated circuit IC4 (MC14013). A resistor MR35 also serves to connect this pin 120 to earth. Similarly the lead 84 is connected by means of a coupling capacitor MC29 to a pin 121 on the integrated circuit MIC4, and again the pin 21 is connected to earth by a

65

50

55

15

20

25

30

35

40

45

resistor MR34. Various remaining pins of the circuit are connected to earth and one pin is connected to the power supply through the line 54. The integrated circuit MIC4 provides an output from pin 123.

The integrated circuit MIC4 is really a bi-stable or "flip-flop" circuit which is caused to change state upon receipt of signals on the pins 120 and 121, changing to or maintaining a first state on receipt of a signal through pin 120, and changing to or maintaining a second state on receipt of a signal through pin 121. Each time the circuit changes state an output pulse passes from the pin 123, through a resistor MR36 to the terminal 58.

It is intended that the apparatus as described is to be utilised in conjunction with a two-pole switch arrangement 130. One pole of the switch is connected between the common terminal 56 and the power supply and the other pole of the switch is connected between the terminal 58 and an alarm. The arrangement is such that when one pole of the switch is opened the other pole of the switch is closed and vice versa. As illustrated the pole associated with the terminal 58 is closed and the pole associated with the terminal 56 is opened. It will be appreciated that in this particular situation, the opening and closing of the relays RL1,RL2 will not have any effect since no power will be supplied to the winch, since the supply of power to the "common" terminal is broken. However, whenever a signal pulse is generated on the line 84, by the circuit MIC1 detecting the appropriate code, an appropriate pulse will be generated by the circuit MIC4 which will cause an alarm connected to the terminal 58 by means of the switch 130 to be armed. Similarly if a pulse is generated on the lead 92 as a result of integrated circuit MIC2 detecting an appropriate coded signal, a further pulse will be generated by the integrated circuit MIC4 which will cause the alarm to disarm itself. Thus by operating the switching arrangement 130 appropriately, the control transmitter can be used to transmit pulses which either arm and disarm an alarm device, or which cause a winch to winch in and out.

Whilst the embodiment of the invention illustrated in Figures 3 to 4 has been described with reference to a particular example in which only two switches are provided at the transmitter to generate two coded pulses, it is to be appreciated that a transmitter may be provided having more than two switches so connected to the integrated circuit IC1 that whenever any switch is depressed, the integrated circuit IC1 is enabled and a specific and unique code is passed from the integrated circuit to the amplifying transistors TR5,TR6, while simultaneously causing the light emitting diode LD1 to be illuminated. Of course, a plurality of detecting circuits similar to the circuits MIC1,MIC2 would need to be provided, and the logic arrangement 50 would be more complex, but work on the same principles as those outlined above with appropriate RC networks ensuring that no relay could drop out immediately after being activated due to the results of power surge, and also means to ensure that no device operated could be caused to reverse immediately.

While the invention has been described with reference to embodiments which incorporate a radio transmitter and receiver it is to be understood that alternative embodiments of the invention may use infra red or ultrasonic transmitters and receivers. The invention may be of benefit not only in controlling winches, but may be used to control cranes or any other device or arrangement powered by a motor or the equivalent.

### Claims

- 1. A remote control apparatus comprising a transmitter adapted to transmit coded signals, and a receiver adapted to receive said signals, decoding means to decode the signals, and a plurality of control elements each adapted to be activated in reponse to the decoding of a predetermined respective signal, and each adapted to remain activated while the receiver continues to receive a signal from the transmitter.

- 2. A remote control apparatus according to Claim 1 wherein the decoding means comprise a plurality of decoding elements each adapted to respond to a predetermined respective coded signal, each control element being activated by a respective decoding element.

- 3. A remote control apparatus according to any one of the preceding Claims wherein each control element is associated with a timing arrangement so that whenever a control element is activated the control element remains activated for at least a period of time as determined by the timing arrangement.

- 4. A remote control apparatus comprising a transmitter adapted to transmit coded signals and a receiver adapted to receive said signals, decoding means to decode the received signals and a plurality of control elements, each activated in response to the reception of a predetermined coded signal, each control element being associated with a timer so that whenever a control element is activated by a coded signal it remains activated for a period of time determined by the timer.

- 5. A remote control appratus according to any one of the preceding Claims wherein each control element is adapted to inhibit each other control element when it is actuated, and for a predetermined period of time after it has ceased to be activated.

- 6. A remote control apparatus according to Claim4 or 5 wherein each control element comprises a circuit consisting of logic gates, selected gates being associated with said timing arrangement adapted to maintain predetermined logic signals on selected inputs of the gates to maintain the gates in a predetermined condition for predetermined periods of time.

- 7. A remote control apparatus according to

65

Claim 6 wherein each control element comprises two NOR gates, the output of the first NOR gate being an input of the second NOR gate, the output of the second NOR gate being fed via a capacitor to an input of the first NOR gate to maintain the first NOR gate in such a condition that the respective control element is activated for said predetermined period of time.

- 8. A remote control apparatus according to Claim 6 wherein the output of the second NOR gate is supplied to charge a capacitor which is connected to an input of the second NOR gate of another control element so that when there is an output on the said second NOR gate of the first control element when the first control element is activated, the second NOR gate of the other control element is inhibited.

- 9. A remote control apparatus according to

any one of the preceding Claims wherein the coded signals comprise pulse coded signals.

10. A remote control apparatus according to Claim 9 wherein the transmitter comprises a radio transmitter, said transmitter comprising a oscillator, amplifier means to amplify the output of the oscillator and code generating means generating pulses, the pulses controlling the supply of power to the amplifying means so that the signal from the oscillator is only amplified in accordance with the code generated by the code generator.

11. A remote control apparatus according to any one of the preceding Claims further incorporating a bi-stable memory element to control an alarm the bi-stable element being controllable from the transmitter.

FIG 2

ALARM

FIG 4C

# EUROPEAN SEARCH REPORT

EP 89 30 0154

|                                                                                                                                                                                                                                     |                                                                                                                     |                                                                           |                                                                                                                                                                                                                                                              | EP 69 30 01                                                                |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|--|

| ]                                                                                                                                                                                                                                   | DOCUMENTS CONSIDE                                                                                                   | ERED TO BE RELEVAN                                                        | NT                                                                                                                                                                                                                                                           |                                                                            |  |

| ategory                                                                                                                                                                                                                             | Citation of document with indic<br>of relevant passag                                                               |                                                                           | Relevant<br>to claim                                                                                                                                                                                                                                         | CLASSIFICATION OF THE APPLICATION (Int. Cl. 4)                             |  |

| X<br>A                                                                                                                                                                                                                              | EP-A-0 195 665 (LATII<br>LTD)<br>* Page 1, lines 13-35<br>1-11; page 5, lines 3<br>lines 6-11; figure 2             | MER ELECTRONICS<br>; page 2, lines<br>D-35; page 6,                       | 1-4,6,7                                                                                                                                                                                                                                                      | G 08 C 25/00                                                               |  |

| X                                                                                                                                                                                                                                   | PATENT ABSTRACTS OF JA<br>52 (E-7)[534], 18th AA<br>E 7; & JP-A-55 21 655<br>K.K.) 15-02-1980<br>* Whole document * | pril 1980, page 49                                                        | 1-4                                                                                                                                                                                                                                                          |                                                                            |  |

| A                                                                                                                                                                                                                                   | US-A-4 081 608 (I.E. * Abstract; column 1, column 2, lines 20-23                                                    | lines 13-51;                                                              | 1,2,9,                                                                                                                                                                                                                                                       |                                                                            |  |

| A                                                                                                                                                                                                                                   | US-A-3 810 098 (J.M. * Column 2, lines 19-1ines 37-50 *                                                             |                                                                           | 1-4,10                                                                                                                                                                                                                                                       |                                                                            |  |

| Α                                                                                                                                                                                                                                   | US-A-4 087 078 (M. JORAKU)                                                                                          |                                                                           | 4,5                                                                                                                                                                                                                                                          | TECHNICAL FIELDS<br>SEARCHED (Int. Cl.4)                                   |  |

|                                                                                                                                                                                                                                     | * Column 2, lines 14-64 - column 3, line 2 58 - column 7, line 4                                                    | O; column 6, line                                                         |                                                                                                                                                                                                                                                              | G 08 C 25/00<br>G 08 C 19/28<br>B 66 D 1/46<br>B 66 D 1/48<br>B 66 C 13/44 |  |

| - "                                                                                                                                                                                                                                 | The present search report has been                                                                                  | drawn up for all claims                                                   |                                                                                                                                                                                                                                                              |                                                                            |  |

|                                                                                                                                                                                                                                     | Place of search                                                                                                     | Date of completion of the search                                          |                                                                                                                                                                                                                                                              | Examiner                                                                   |  |

| THE HAGUE 06-03-1989                                                                                                                                                                                                                |                                                                                                                     | 06-03-1989                                                                | DHEERE R.F.B.M.                                                                                                                                                                                                                                              |                                                                            |  |

| CATEGORY OF CITED DOCUMENTS  X: particularly relevant if taken alone Y: particularly relevant if combined with another document of the same category A: technological background O: non-written disclosure P: intermediate document |                                                                                                                     | E : earlier patent after the filing r D : document cite L : document cite | T: theory or principle underlying the invention E: earlier patent document, but published on, or after the filing date D: document cited in the application L: document cited for other reasons  &: member of the same patent family, corresponding document |                                                                            |  |

EPO FORM 1503 03.82 (P0401)