Numéro de publication:

**0 329 528** A1

12

## **DEMANDE DE BREVET EUROPEEN**

(a) Numéro de dépôt: 89400355.7

(s) Int. Cl.4: **G 09 G 3/36**

22 Date de dépôt: 08.02.89

30 Priorité: 15.02.88 FR 8801741

43 Date de publication de la demande: 23.08.89 Bulletin 89/34

Etats contractants désignés:

CH DE FR GB IT LI NL

(7) Demandeur: COMMISSARIAT A L'ENERGIE ATOMIQUE 31/33, rue de la Fédération F-75015 Paris (FR)

72 Inventeur: Clerc, Jean-Frédéric 7 Rue Casimir Brenier F-38120 Saint-Egrève (FR)

> Sarrasin, Denis 28 Rue du Grand-Français F-38140 Rives-sur-Fure (FR)

Mandataire: Mongrédien, André et al c/o BREVATOME 25, rue de Ponthieu F-75008 Paris (FR)

Procédé de commande d'un écran d'affichage matriciel et dispositif pour la mise en oeuvre de ce procédé.

Procédé de commande d'un écran d'affichage matriciel permettant d'ajuster son contraste dans le cas d'un écran à cristaux liquides et sa luminosité dans le cas d'un écran fluorescent à micropointes, consistant à appliquer sur des conducteurs lignes périodiquement des signaux d'adressage VI ayant pendant une certaine durée une valeur Vmax en valeur absolue, à appliquer sur des conducteurs colonnes des signaux de commande. On applique sur les conducteurs lignes des signaux d'adressage dont les durées pendant lesquelles ils ont une valeur Vmax se recouvrent partiellement, pour deux lignes consécutives.

Dispositif pour la mise en oeuvre de ce procédé. Application à la réalisation d'afficheurs pour la visualisation d'images fixes ou animées.

## PROCEDE DE COMMANDE D'UN ECRAN D'AFFICHAGE MATRICIEL ET DISPOSITIF POUR LA MISE EN OEUVRE DE CE PROCEDE

5

15

20

25

30

45

55

La présente invention a pour objet un procédé de commande d'un écran d'affichage matriciel permettant d'ajuster son contraste dans le cas d'un écran à cristaux liquides et sa luminosité dans le cas d'un écran fluorescent à micropointes et un dispositif pour la mise en oeuvre de ce procédé.

1

L'invention s'applique notamment à la réalisation d'afficheurs à cristaux liquides de type multiplexé ou non multiplexé ou bien d'écrans fluorescents à micropointes (notés EFM dans la suite de la description), permettant la visualisation d'images fixes ou animées.

Divers types de procédés de commande sont connus pour des écrans d'affichage matriciels.

Les écrans matriciels d'affichage comportent une cellule d'affichage munie de conducteurs lignes et de conducteurs colonnes croisés, un pixel de l'écran étant associé à chaque croisement de ces conducteurs.

On trouve une description d'un EFM dans la demande de brevet français n° 87 15432 du 6 novembre 1987. Dans un EFM les lignes correspondent aux grilles et les colonnes aux cathodes.

Pour les écrans à cristaux liquides, le matériau d'affichage est contenu dans la cellule d'affichage. Les écrans à cristaux liquides peuvent être commandés de manière multiplexée ou non multiplexée.

De facon plus détaillée, dans le cas d'un écran d'affichage de type multiplexé, les conducteurs lignes et colonnes sont constitués par des électrodes lignes et colonnes disposées respectivement sur les parois internes de la cellule, un pixel étant défini par la zone de recouvrement d'une électrode ligne et d'une électrode colonne.

Dans le cas d'un écran d'affichage de type non multiplexé, les conducteurs lignes et colonnes sont constitués par des lignes d'adressage et des colonnes de commande qui sont par exemple disposées sur une des parois de la cellule et reliées par l'intermédiaire de transistors à des électrodes points, une électrode continue étant disposée sur l'autre paroi de la cellule. Selon un autre exemple de ce type d'écran les lignes d'adressage et les colonnes de commande peuvent être disposées respectivement sur les parois internes de la cellule, les lignes étant reliées par l'intermédiaire de transistors à des électrodes points et les colonnes étant reliées à des colonnes d'électrodes. Dans ces deux derniers cas, un pixel est défini par la zone de recouvrement d'une électrode point avec l'électrode continue ou avec une électrode colonne.

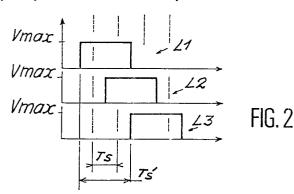

On envoie sur les différents conducteurs lignes des signaux d'adressage et sur les conducteurs colonnes des signaux de commande. Un exemple, purement illustratif et nullement limitatif, est donné figure 1. décrivant de tels signaux dans le cas d'un écran d'affichage matriciel à cristaux liquides commandé par la technique dite de multiplexage direct.

Pour des raisons de simplicité, ne nuisant en aucune façon à la description, on se limite dans cet

exemple à un écran possédant neuf pixels, c'està-dire trois conducteurs lignes L1, L2, L3, et trois conducteurs colonnes C1, C2, C3.

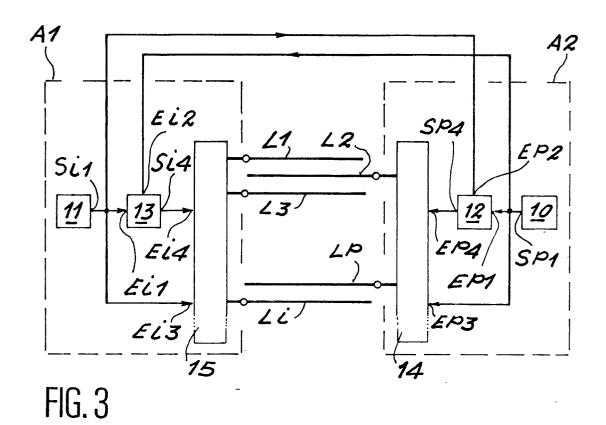

Les tensions VI appliquées aux conducteurs lignes sont périodiques, de période T dit temps de trame ou temps de balayage. Pour chaque conducteur ligne, la tension VI est égale à une tension Vrnax pendant un temps Ts dit de sélection de ligne, elle est nulle par exemple, en dehors de ce temps Ts sur le reste du temps T. Chaque ligne est ainsi portée successivement pendant un temps Ts à la valeur Vmax. On a représenté figure 1A un cycle d'adressage des conducteurs lignes. La figure 1B décrit un exemple de séquence des tensions de commande Vc appliquées sur les conducteurs colonnes. Selon le motif à afficher les tensions appliquées aux conducteurs colonnes seront positives ou négatives.

Les valeurs des tensions appliquées aux conducteurs lignes et aux conducteurs colonnes dépendent de la nature de l'affichage utilisé.

Quand la tension appliquée à un conducteur ligne est en phase avec la tension appliquée sur un conducteur colonne, le pixel correspondant à leur croisement est éteint (noir, par exemple). Si les deux tensions sont en opposition de phase, le pixel considéré est allumé (blanc par exemple).

Lorsque la ligne L1 est sélectée autrement dit lorsqu'elle est portée à Vmax pendant Ts, la tension sur la colonne C1 est positive, dans l'exemple proposé. Les deux tensions ligne et colonne sont en phase et le pixel correspondant au croisement du conducteur ligne L1 avec le conducteur colonne C1 est noir. Lorsque la ligne L2 est sélectée, la tension sur la colonne C1 est négative, dans l'exemple proposé. Les deux tensions ligne et colonne sont en opposition de phase et le pixel correspondant au croisement du conducteur ligne L2 avec le conducteur colonne C1 est blanc. L'état de chaque pixel se déduit de manière identique.

La figure 1C donne l'affichage de l'écran pour les tensions lignes et colonnes proposées figures 1A et 1B. Les pixels notés N sont noirs, ceux notés B sont blancs.

Pour l'affichage d'une information donnée, à chaque période T correspondante, les tensions lignes et colonnes ont leur polarité inversée pour n'appliquer au matériau d'affichage que des signaux de valeurs moyennes nulles.

Dans le cas d'un écran à cristaux liquides de type non multiplexé ou d'un EFM, les signaux de sélection des conducteurs lignes sont les mêmes que ceux représentés figure 1A mais ils ne subissent pas d'inversion de polarité. Par contre les signaux appliqués aux conducteurs colonnes sont indifféremment de polarité positive ou négative, leur amplitude dépend uniquement de la tension nécessaire à l'effet électrooptique utilisé.

Dans tous les cas, le temps de sélection de ligne Ts dépend du nombre de conducteurs lignes à

5

25

30

sélecter par la formule Ts=T/M où M est le nombre total de conducteurs lignes et T est le temps de trame. On comprend que plus M augmente plus le temps de sélection Ts est court.

On définit le taux de multiplexage TM comme étant le rapport entre le temps de trame T et le temps de sélection d'un conducteur ligne Ts. TM = T/Ts

On constate que pour les écrans connus TM = M. Lorsque le nombre de conducteurs lignes croît, le taux de multiplexage suit cette croissance et le temps Ts diminue entraînant une diminution du contraste d'un écran à cristaux liquides et de la luminosité d'un EFM.

Le nombre de lignes couramment utilisé dans des écrans d'affichage matriciels à cristaux liquides est environ cent. Il est donc largement inférieur au nombre de signaux lignes disponibles en vidéo qui est égal à, par exemple, environ deux cent quatre vingt en sortie d'un magnétoscope.

L'invention propose un procédé de commande d'un écran d'affichage matriciel qui permet l'utilisation d'un grand nombre de lignes sans perte de contraste ou de luminosité ou encore, à nombre de lignes égal à celui des écrans de l'art antérieur, une amélioration du contraste ou de luminosité.

Cette amélioration ne peut s'interpréter indépendamment de phénomènes liés à la physiologie de l'oeil ; elle correspond à un effet de moyenne des informations contenues sur l'écran sur un temps de trame.

Dans ce procédé, les temps de sélection des conducteurs lignes adjacents peuvent se recouvrir. Le réglage du recouvrement permet d'utiliser un écran soit en mode graphique ou texte, soit en mode vidéo pour la visualisation d'une image animée. Dans le premier cas, le recouvrement doit être nul ou faible; le contraste ou la luminosité est limité, mais la résolution effective est alors maximale. Dans la seconde utilisation, le nombre élevé de lignes évite l'aspect mosaïque sur l'écran, désagréable à l'oeil. Le recouvrement peut atteindre jusqu'à la moitié des temps de sélection de deux lignes adjacentes pour un contraste ou une luminosité fort. La résolution effective est alors réduite mais cela n'est pas gênant pour une image animée (image naturelle).

Par ce procédé, si l'on se réfère à l'exemple se rapportant à l'art antérieur, le taux de multiplexage TM est maintenant inférieur ou égal au nombre de conducteurs lignes. A taux de multiplexage égal on peut donc augmenter le nombre de conducteurs lignes et améliorer par là le contraste ou la luminosité de l'écran.

De manière plus précise, l'invention a pour objet un procédé de commande d'un écran d'affichage matriciel, cet écran comportant des conducteurs lignes et des conducteurs colonnes, ce procédé consistant à :

- appliquer sur les conducteurs lignes périodiquement des signaux d'adressage VI ayant pendant une certaine durée une valeur Vmax en valeur absolue,

- appliquer sur les conducteurs colonnes des signaux de commande,

- ce procédé étant caractérisé par le fait qu'on applique sur les conducteurs lignes des signaux

d'adressage dont les durées pendant lesquelles ils ont une valeur Vmax, se recouvrent partiellement, pour deux lignes consécutives.

Selon une autre caractéristique de ce procédé de commande la durée pendant laquelle les signaux d'adressage VI ont une valeur Vmax est réglable.

L'invention a aussi pour objet un dispositif pour la mise en oeuvre du procédé de commande d'un écran d'affichage. Le dispositif comprend :

- un circuit d'adressage A1 relié par des connexions aux conducteurs lignes Li, i étant un entier impair tel que 1≦i≦M, M étant le nombre de conducteurs lignes,

- un circuit d'adressage A2 relié par des connexions aux conducteurs lignes Lp, p étant un entier pair, tel que  $2 \le p \le M$ .

Le circuit d'adressage A2 comprend :

- un circuit réalisant une fonction horloge délivrant des signaux sur une sortie Sp1,

- un circuit réalisant une fonction de verrouillage relié par une entrée Ep1 à la sortie Sp1 du circuit réalisant la fonction horloge et délivrant des signaux sur une sortie Sp4,

- un circuit de commande relié par une entrée Ep4 à la sortie Sp4 du circuit réalisant une fonction de verrouillage et par une entrée Ep3 à la sortie Sp1 du circuit réalisant une fonction horloge et délivrant des tensions VI sur les conducteurs lignes Lp qui lui sont connectés.

Le circuit d'adressage A1 a une structure identique au circuit d'adressage A2. Le circuit d'adressage A1 comprend :

- un circuit réalisant une fonction horloge délivrant des signaux sur une sortie Si1,

- un circuit réalisant une fonction de verrouillage relié par une entrée Ei1 à la sortie Si1 du circuit réalisant la fonction horloge et délivrant des signaux sur une sortie Si4,

- un circuit de commande relié par une entrée Ei4 à la sortie Si4 du circuit réalisant une fonction de verrouillage et par une entrée Ei3 à la sortie Si1 du circuit réalisant une fonction horloge et délivrant des tensions VI sur les conducteurs lignes Li qui lui sont connectés.

Le circuit réalisant une fonction de verrouillage dans le circuit d'adressage A2 est aussi relié par une entrée Ep2 à une sortie Si1 du circuit réalisant une fonction horloge dans le circuit d'adressage A1, le circuit réalisant une fonction de verrouillage dans le circuit d'adressage A1 étant aussi relié par une entrée Ei2 à la sortie Sp1 du circuit réalisant une fonction horloge dans le circuit d'adressage A2.

Les circuits de commande des circuits A1 et A2 sont par exemple respectivement du type registre à décalage doté d'une fonction de verrouillage.

De cette façon, ces circuits de commande portent les conducteurs lignes qui leur sont connectés selon l'état de leur fonction de verrouillage :

- soit collectivement à un potentiel de référence correspondant au potentiel de verrouillage ;

- soit sélectivement en fonction des niveaux logiques présents respectivement dans les registres à décalage au potentiel de référence (état 0) ou au potentiel de sélection ligne (état 1).

- La fonction de verrouillage est appelée en termi-

65

15

20

25

30

45

nologie anglosaxonne fonction "enable".

D'autres caractéristiques et avantages de l'invention ressortiront mieux de la description qui va suivre, donnée à titre purement illustratif et nullement limitatif, en référence aux figures annexées, dans lesquelles :

- les figures 1A à 1C, déjà décrites et relatives à l'art antérieur, illustrent un procédé de commande classique d'un écran d'affichage matriciel:

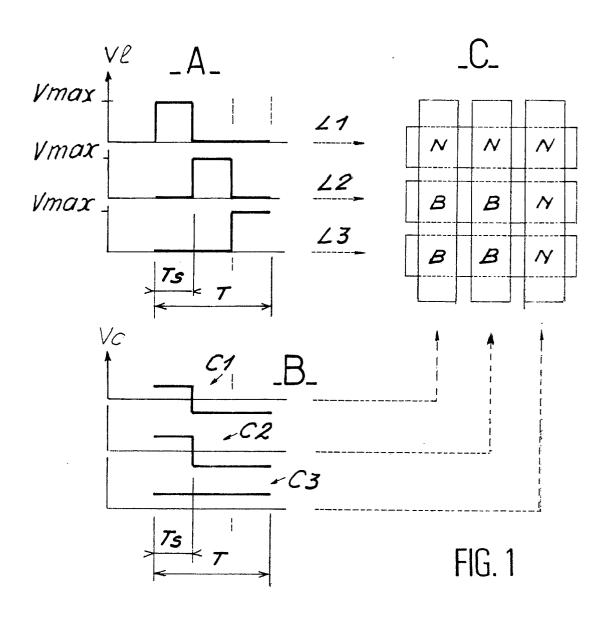

- la figure 2 représente une séquence de commande selon l'invention de trois conducteurs lignes dans le cas d'un recouvrement fort entre les temps de sélection;

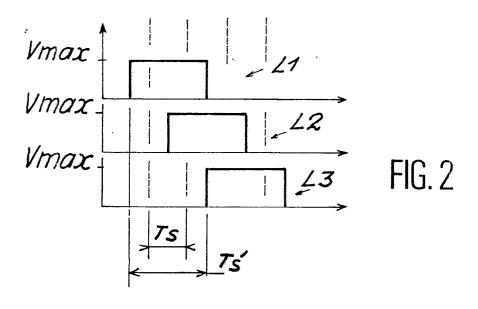

- la figure 3 représente un dispositif permettant de mettre en oeuvre le procédé selon l'invention ;

- la figure 4 représente les diagrammes temporels des signaux délivrés par les différents éléments d'un dispositif selon l'invention;

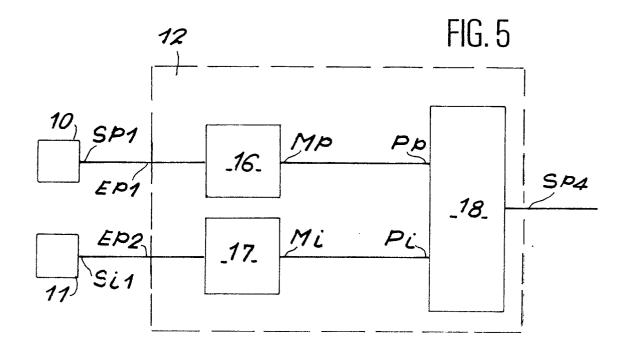

- la figure 5 représente un exemple de réalisation d'une fonction "enable" ;

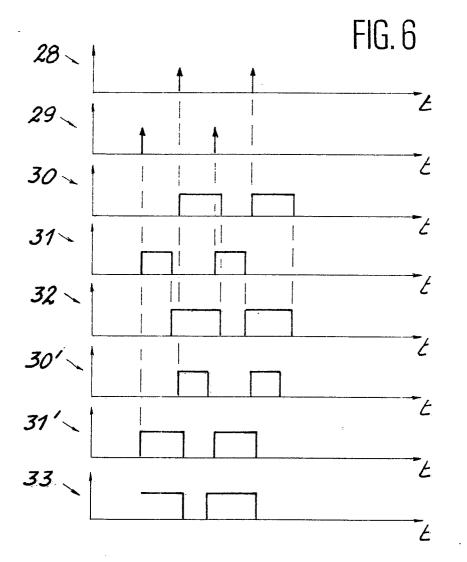

- la figure 6 représente un exemple de diagrammes temporels des signaux délivrés par les différents éléments permettant de réaliser les fonctions "enable".

La figure 2 représente une séquence de commande selon l'invention de trois conducteurs lignes, L1. L2 et L3 dans le cas d'un recouvrement fort entre les temps de sélection. Ce cas limite, où le temps de sélection Ts' est égal à deux fois le temps de sélection Ts correspondant à un recouvrement nul, illustre bien le procédé selon l'invention. Cet exemple, restreint pour des raisons de simplicité de description à trois conducteurs lignes, ne limite en rien le nombre de conducteurs lignes qu'il est possible de sélecter par ce procédé. Par ailleurs, cet exemple est valable aussi bien pour un écran à cristaux liquides de type multiplexé ou non multiplexé que pour un EFM.

La tension VI appliquée sur un conducteur ligne est égale, pendant le temps de sélection Ts', à la tension Vmax et est inférieure à Vmax (elle est par exemple nulle) pendant le reste du temps de trame.

Le temps total d'écriture d'une trame est égal à : (MxTs) + (Ts'-Ts).

M est le nombre total de lignes ; Ts est le temps de sélection d'un conducteur ligne correspondant à un recouvrement entre les temps de sélection de deux conducteurs lignes nul ; Ts' est le temps de sélection effectif des conducteurs lignes. Ce temps d'écriture est supérieur ou égal à un temps de trame T du temps Ts'-Ts, le temps (Ts'-Ts) est pris sur le temps pendant lequel le signal vidéo n'est porteur d'aucune information, ce temps est communément appelé temps de retour de trame.

L'allongement et le recouvrement des temps de sélection des conducteurs lignes entraînent un moyennage du signal lumineux d'un conducteur ligne à l'autre. La brillance moyenne de l'écran est améliorée et les contours de l'image visualisée en sont adoucis.

La figure 3 représente un dispositif permettant de mettre en oeuvre le procédé selon l'invention. Le dispositif comprend un circuit d'adressage A1 relié

par des connexions aux conducteurs lignes Li, i étant un entier impair tel que 1≦i≦M et un circuit d'adressage A2 relié par des connexions aux conducteurs lignes Lp, p étant un entier pair tel que 2≤p≤M. Le circuit d'adressage A2 comprend un circuit 10 réalisant une fonction horloge délivrant des signaux sur une sortie Sp1, un circuit 12 réalisant une fonction "enable" relié par une entrée Ep1 à la sortie Sp1 de la fonction horloge 10 et délivrant des signaux sur une sortie Sp4. Une fonction "enable" a pour effet de verrouiller la sortie du circuit auguel elle est reliée à un potentiel de référence (ou potentiel de verrouillage), le potentiel de référence est par exemple nul. C'est par son intermédiaire que le temps de sélection des conducteurs lignes est ajusté. Une description d'une réalisation d'une telle fonction, appliquée au dispositif selon l'invention, est donnée plus loin. Le circuit d'adressage A2 comprend aussi un circuit de commande 14 formé par un registre à décalage doté de la fonction "enable" paire relié par une entrée Ep4 à la sortie Sp4 du circuit réalisant la fonction "enable" 12 et par une entrée Ep3 à la sortie Sp1 du circuit réalisant la fonction horloge 10 et délivrant des tensions VI sur les conducteurs lignes Lp de numéro pair qui lui sont connectés.

Le circuit d'adressage A1 à une structure identique au circuit d'adressage A2. Ses connexions sont affectées de l'indice "i" (impair) au lieu de l'indice "p" (pair) des connexions du circuit A2, le circuit réalisant la fonction horloge 11 impaire ayant pour homologue pair le circuit réalisant la fonction horloge 10, le circuit réalisant la fonction "enable" impaire et le circuit de commande du circuit d'adressage A1 portant les références respectivement 13 et 15 et ayant pour homologues les circuits 12 et 14. Le circuit de commande 15 est formé par un registre à décalage doté de la fonction "enable" impaire.

En outre, le circuit réalisant la fonction "enable" 12 est aussi relié par une entrée Ep2 à la sortie Si3 du circuit réalisant la fonction horloge 11. De même, le circuit réalisant la fonction "enable" 13 est relié par une entrée Ei2 à la sortie Sp3 du circuit réalisant la fonction horloge paire 10.

Les diagrammes temporels des signaux délivrés sur les différentes sorties des éléments constituant les circuits d'adressage sont représentés figure 4.

Les signaux 20 délivrés sur la sortie Sp1 du circuit réalisant la fonction horloge 10 paire sont représentés accompagnés des états respectifs des diffèrentes cases du registre à décalage 14 obtenus après chaque impulsion du signal d'horloge paire. Les signaux 21 sont délivrés par le circuit horloge 11 impaire sur la sortie Si1 de ce circuit. Ces signaux sont accompagnés des états respectifs des différentes cases du registre à décalage 15 obtenus après chaque impulsion du signal d'horloge impaire.

La figure 4 présente un exemple où sont représentés les états des registres à décalage délivrant des tensions VI sur trois conducteurs lignes de numéro pair L2, L4, L6 et trois de numéro impair L1, L3, L5. A chaque impulsion d'horloge, l'état 1 qui correspond à la tension VI=Vmax en sortie du registre à décalage avance d'une case dans le

registre, l'état 0 correspondant à la tension VI=0V par exemple. Les conducteurs lignes de numéro pair sont adressés successivement par l'application d'une tension VI=Vmax. Il en est de même pour les conducteurs lignes de numéro impair. Les signaux 22, 23 sont délivrés respectivement par les sorties Sp4 et Si4 des fonctions "enable" paire et impaire. Ce sont des tensions ayant la forme de créneaux périodiques. L'état haut d'un créneau correspond à la tension VI=Vmax, l'état bas correspond à la tension VI=0V, par exemple. Les signaux 22 et 23 sont déphasés, le déphasage est constant : les lignes paires et impaires sont adressées alternativement.

Les signaux 25, 26, 27 correspondent aux tensions VI délivrées par les registres à décalage sur les connexions des conducteurs lignes L1, L2 et L3. Ce sont des créneaux périodiques dont la période est le temps de trame.

Cet exemple de séquence de commande est donné dans le cas d'un recouvrement fort entre les temps de sélection des conducteurs lignes.

Selon le mode de commande proposé, le circuít A1 qui adresse les lignes Li comporte, dans le registre 15, autant de niveaux logiques (1 ou 0) que de lignes. A chaque instant, un seul des niveaux logiques est à 1, tous les autres sont à zéro. Si le niveau logique 1 est, à l'instant considéré, associé à la ligne Li, il sera, après un coup d'horloge décalé et associé à la ligne Li+1.

Un registre à décalage doté de la fonction verrouillage ne sélecte la ligne correspondant au niveau logique 1, c'est-à-dire dans le cas considéré porte cette ligne au potentiel Vmax que si la fonction "enable" présente par exemple l'état haut et ne sélecte aucune ligne si la fonction "enable" présente par exemple l'état bas. Lorsque la fonction "enable" est à l'état bas, toutes les lignes sont au potentiel de verrouillage. Lorsque la fonction "enable" est à l'état haut, une ligne (associée au niveau logique 1 dans le registre à décalage) est au potentiel Vmax, les autres lignes (associées au niveau logique 0 dans le registre à décalage) sont au potentiel de verrouillage. Le circuit A2 a le même fonctionnement.

La figure 5 présente un exemple d'un circuit 12 réalisant une fonction "enable". Ce circuit 12 est commandé par les deux circuits réalisant des fonctions horioges 10, 11. Les entrées Ep1 et Ep2 du circuit 12 sont reliées respectivement aux sorties Sp1 et Si1 des horloges 10 et 11. Cet exemple correspond à la fonction "enable" faisant partie du circuit d'adressage des conducteurs lignes de numéro pair. Les entrées Ep1 et Ep2 sont en fait les entrées respectives de deux monostables à capacité variable 16, 17. Les sorties respectives Mp, Mi des deux monostables sont reliées à deux entrées Pp, Pi d'un circuit logique 18. La sortie de ce circuit 18 est la sortie Sp4 du circuit 12 réalisant la fonction "enable".

La figure 6 représente le diagramme temporel des signaux issus des sorties des différents éléments permettant de réaliser les fonctions "enable".

Les impulsions d'horloge 28, 29 sont les signaux délivrés par les circuits réalisant les fonctions horloges 10, 11 sur les entrées Ep1 et Ep2 du circuit

12. Les monostables à capacité variable 16, 17 transforment respectivement ces impulsions en signaux rectangulaires 30, 31 dont la largeur dépend de la valeur de leur capacité.

Les fronts de descentes des signaux rectangulaires 31 commandent la montée des signaux rectangulaires 32 délivrés sur la sortie Sp4 du circuit 12, les fronts de descente des signaux rectangulaires 30 commandent la descente des signaux rectangulaires 32. Ainsi, la largeur des signaux 30, 31 commande la largeur des signaux rectangulaires délivrés sur la sortie Sp4. En ajustant la valeur des capacités variables des monostables 16, 17, on peut donc décider de la largeur des signaux délivrés sur la sortie Sp4 et par là du temps de recouvrement entre les temps de sélection des conducteurs lignes.

Le circuit 18 est formé par tout ensemble d'éléments connus comportant des portes logiques, permettant à partir des signaux 30, 31 d'obtenir les signaux 32.

Le circuit 13 est réalisé de la même façon que le circuit 12, à partir de deux monostables à capacités variables et d'un circuit logique, les entrées des monostables étant reliées respectivement aux circuits 10 et 11.

Les signaux 30' et 31' représentent un exemple de signaux de sortie des monostables du circuit 13. Les signaux 30' et 31' sont des signaux rectangulaires obtenus de manière analogue aux signaux 30, 31 à partir des impulsions d'horloge respectives 28, 29. Les signaux 33 représentent les signaux rectangulaires résultants, obtenus sur la sortie Si4 du circuit 13 de manière analogue à la génération des signaux 32 obtenus sur la sortie Sp4 du circuit 12.

Sur les figures, les recouvrements du temps de sélection d'une ligne avec le temps de sélection de la ligne précédente et celui de la ligne suivante sont identiques, mais bien entendu ils peuvent être différents. Pour réaliser des recouvrements différents, il suffit d'avoir des fonctions "enable" paire et impaire qui ont des signaux rectangulaires de durées différentes.

## Revendications

- 1. Procédé de commande d'un écran d'affichage matriciel, cet écran comportant des conducteurs lignes et des conducteurs colonnes, ce procédé consistant à :

- appliquer sur les conducteurs lignes périodiquement des signaux d'adressage VI ayant pendant une certaine durée une valeur Vmax en valeur absolue,

- appliquer sur les conducteurs colonnes des signaux de commande,

- ce procédé étant caracterisé par le fait qu'on applique sur les conducteurs lignes des signaux d'adressage dont les durées pendant lesquelles ils ont une valeur Vmax se recouvrent partiellement, pour deux lignes consécutives.

- 2. Procédé de commande d'un écran d'affichage selon la revendication 1, caractérisé par le fait que la durée pendant laquelle les signaux

65

60

5

10

15

20

d'adressage VI ont une valeur Vmax est réglable.

- 3. Dispositif pour la mise en oeuvre du procédé de commande d'un écran d'affichage selon la revendication 1 caractérisé en ce qu'il comprend :

- un circuit d'adressage A1 relié par des connexions aux conducteurs lignes Li, i étant un entier impair tel que 1≦i≦M, M étant le nombre de conducteurs lignes,

- un circuit d'adressage A2 relié par des connexions aux conducteurs lignes Lp, p étant un entier pair tel que  $2 \le p \le M$ ,

- et en ce que le circuit d'adressage A2 comprend :

- un circuit (10) réalisant une fonction horloge délivrant des signaux sur une sortie Sp1,

- un circuit (12) réalisant une fonction de verrouillage relié par une entrée Ep1 à la sortie Sp1 du circuit (10) réalisant la fonction horloge et délivrant des signaux sur une sortie Sp4,

- un circuit de commande (14) relié par une entrée Ep4 à la sortie Sp4 du circuit (12) réalisant une fonction de verrouillage et par une entrée Ep3 à la sortie Sp1 du circuit (10) réalisant une fonction horloge et délivrant des tensions VI sur les conducteurs lignes Lp qui lui

sont connectés,

et en ce que le circuit d'adressage A1 comprend :

- un circuit (11) réalisant une fonction horloge délivrant des signaux sur une sortie Si1,

- un circuit (13) réalisant une fonction de verrouillage relié par une entrée Ei1 à la sortie Si1 du circuit (11) réalisant une fonction horloge et délivrant des signaux sur une sortie Si4,

- un circuit (15) de commande relié par une entrée Ei4 à la sortie Si4 du circuit (13) réalisant une fonction de verrouillage et par une entrée Ei3 à la sortie Si1 du circuit (11) réalisant une fonction horloge et délivrant des tensions VI sur les conducteurs lignes Li qui lui sont connectés.

et en ce que le circuit (12) réalisant une fonction de verrouillage dans le circuit d'adressage A2 est aussi relié par une entrée Ep2 à une sortie Si1 du circuit (11) réalisant une fonction horloge dans le circuit d'adressage A1, le circuit (13) réalisant une fonction de verrouillage dans le circuit d'adressage A1 étant aussi relié par une entrée Ei2 à la sortie Sp1 du circuit (10) réalisant une fonction horloge dans le circuit d'adressage A2.

30

25

35

40

45

50

55

60

FIG. 4

21

20

23

23

25

26

27

## RAPPORT DE RECHERCHE EUROPEENNE

EP 89 40 0355

| Catégorie                                                                    | Citation du document avec indice<br>des parties pertinen                                                 | ation, en cas de besoin,<br>tes       | Revendication concernée  | CLASSEMENT DE LA<br>DEMANDE (Int. Cl.4)            |

|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|---------------------------------------|--------------------------|----------------------------------------------------|

| A,P                                                                          | EP-A-O 256 548 (CANON * Page 3, colonne 3, l colonne 5, ligne 6; pa ligne 32 - page 6, col figures 1-5 * | igne 54 - page 4,<br>ge 5, colonne 7, | 1                        | G 09 G 3/36                                        |

| A                                                                            | DE-A-3 401 073 (CANON<br>* Page 17, ligne 1 - p                                                          | K.K.)<br>age 23, ligne 16             | 1                        |                                                    |

| A                                                                            | EP-A-0 197 742 (INTER<br>ELECTRIC CORP.)<br>* Page 12, ligne 5 - p                                       |                                       | 1                        | ·                                                  |

| A                                                                            | US-A-4 044 346 (AKAHA * Revendication 1; col - colonne 4, ligne 17                                       | onne 3, ligne 48                      | 1                        |                                                    |

| A                                                                            | EP-A-0 206 178 (CASIO LTD)                                                                               | COMPUTER CO.,                         |                          | DOMAINES TECHNIQUES RECHERCHES (Int. Cl.4)  G 09 G |

| Le pre                                                                       | ésent rapport a été établi pour toutes le                                                                | es revendications                     |                          |                                                    |

| Lieu de la recherche  LA HAYE  Date d'achèvement de la recherche  11-05-1989 |                                                                                                          | TIBAL                                 | Examinateur  JX M.J.P.G. |                                                    |

- X : particulièrement pertinent à lui seuI

Y : particulièrement pertinent en combinaison avec un autre document de la même catégorie

A : arrière-plan technologique

O : divulgation non-écrite

P : document intercalaire

- E: document de brevet antérieur, mais publié à la date de dépôt ou après cette date

D: cité dans la demande

L: cité pour d'autres raisons

- & : membre de la même famille. document correspondant