11) Publication number:

**0 332 714** A1

(12)

# **EUROPEAN PATENT APPLICATION**

(21) Application number: 88100516.9

(51) Int. Cl.4: G05F 3/26

(2) Date of filing: 15.01.88

③ Priority: 12.03.88 US 3526

Date of publication of application: 20.09.89 Bulletin 89/38

② Designated Contracting States:

DE FR GB NL

- 71 Applicant: TEKTRONIX, INC.

Howard Vollum Park 14150 S.W. Karl Braun

Drive P.O. Box 500

Beaverton Oregon 97077(US)

- inventor: Metcalf, Michael H.

14304 S.W. Stallion Drive

Beaverton Oregon 97005(US)

Inventor: Taylor, Stewart S.

16927 N.W. Hazelgrove Court

Beaverton Oregon 97006(US)

- Representative: Baillie, Iain Cameron et al c/o Ladas & Parry Isartorplatz 5

D-8000 München 2(DE)

- Temperature compensated current source.

- whose magnitude is substantially independent of changes in temperature. In each of three embodiments (50, 100, 120), one or more bipolar transistors are employed to provide a compensating current which is dependent on the base-to-emitter voltages, V<sub>BE</sub>, of such bipolar transistors. The compensating current changes with temperatures so as to offset changes in the uncompensated output current so that the total output current is substantially independent of V<sub>BE</sub>. The three embodiments employ current mirror circuits (10, 122) that provide a current source of simple circuit design that is operable with the use of a single power supply at a relatively low voltage.

EP 0 332 714 A

#### TEMPERATURE COMPENSATED CURRENT SOURCE

10

15

25

30

### Technical Field

The present invention relates to current sources and, in particular, to a method and circuit for stabilizing with changes in temperature the output current developed by a current source.

## Background of the Invention

A "current mirror" circuit is one simple form of current source that is typically implemented as an integrated circuit. A current mirror circuit employing bipolar transistors suffers, however, from the disadvantage of providing an output current whose magnitude is uncertain and remains substantially constant over only a relatively narrow range of operating temperatures. The reason is that the output current depends on the base-to-emitter voltage of at least one transistor used in the current mirror circuit whose voltage varies with different integrated circuits and changes in temperature. A current source of this type is, therefore, undesirable for use in applications that require an output current of predictable magnitude or an output current whose magnitude remains constant over a wide range of operating temperatures.

A current source of conventional design which includes a special "bias" operational amplifier provides an output current of constant magnitude that is independent of temperature. This type of current source is undesirable because the operational amplifier employs many transistor deivces, which constitute a circuit of complex design that is difficult to implement with a single power supply, particularly at a relatively low voltage (e.g., + 5 volts).

#### Summary of the Invention

An object of the present invention is, therefore, to provide a current source that is suitable for implementation as an integrated circuit and develops an output current whose magnitude remains constant with changes in temperature.

Another object of the invention is to provide such a current source that is of simple design and is operable with the use of a single power supply at a relatively low voltage.

A further object of the invention is to provide such a current source which is implemented with bipolar transistors but whose output current is independent of the base-to-emitter voltages of such transistors.

Still another object of the invention is to pro-

vide in a current source that employs a current mirror circuit, a method for stabilizing the output current with changes in temperature.

Yet another object of the invention is to provide an electrical circuit for implementing such method of stabilizing the output current with bipolar transistors

Additional objects and advantages of the present invention will be apparent from the following detailed description of preferred embodiments thereof, which proceeds with reference to the accompanying drawings.

## Brief Description of the Drawings

Fig. 1 is an electrical circuit diagram of a prior art current source employing a current mirror circuit.

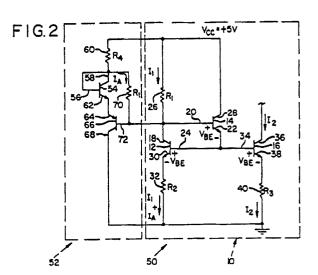

Fig. 2 is an electrical circuit diagram of a first preferred embodiment of the current source of the present invention.

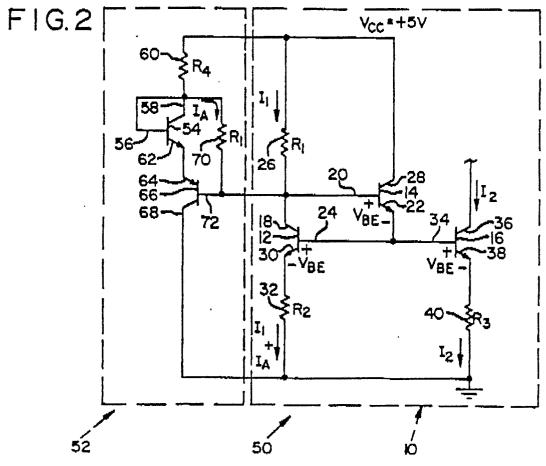

Fig. 3 is an electrical circuit diagram of a second preferred embodiment of the current source of the present invention.

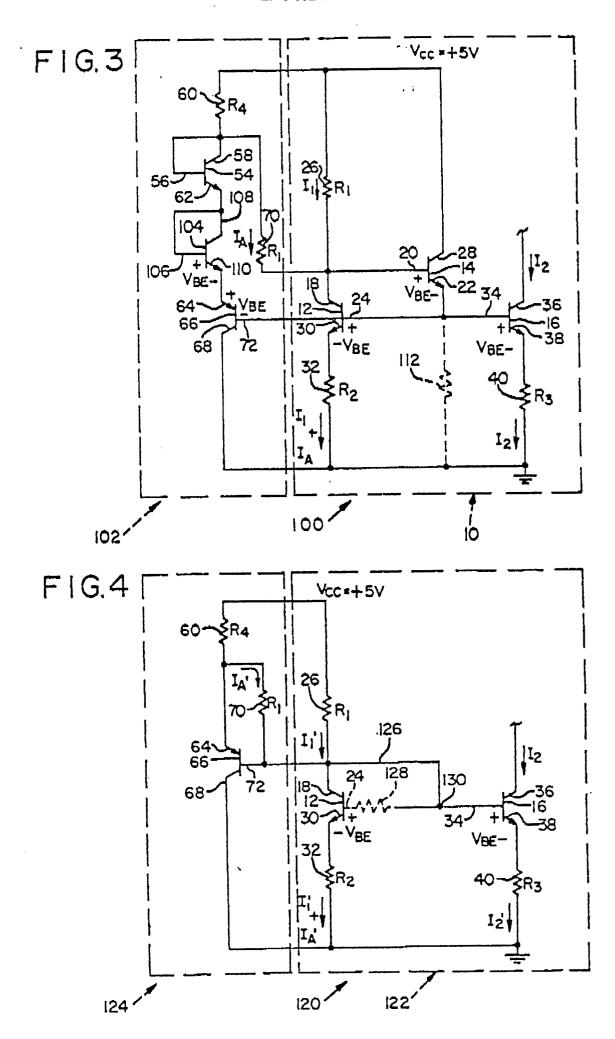

Fig. 4 is an electrical circuit diagram of a third preferred embodiment of the current source of the present invention.

### Detailed Description of Preferred Embodiments

With reference to Fig. 1, a prior art current source 10 of the current mirror type includes NPN transistors 12, 14, and 16 of essentially identical design. The collector terminal 18 of transistor 12 is connected to the base terminal 20 of transistor 14, and the emitter terminal 22 of transistor 14 is connected to the base terminal 24 of transistor 12. Interconnecting transistors 12 and 14 in this manner forces the collector-to-base voltage of transistor 12 to equal the base-to-emitter voltage,  $V_{\text{BE}}$ , of transistor 14. Collector terminal 18 of transistor 12 is connected through a resistor 26 of value " $R_1$ " to a collector bias voltage  $V_{CC}$  = +5 volts. The collector terminal 28 of transistor 14 is directly connected to V<sub>CC</sub>. The emitter terminal 30 of transistor 12 is connected through a resistor 32 of value "R2" to ground. The reference current I1 flowing through resistor 32 is determined by application of Kirchoff's voltage law and can be expressed as:

$I_1 = (V_{CC} - 2V_{BE})/(R_1 + R_2).$

The above equation is correct under the assumptions that the base-to-emitter voltages of transistors

45

25

30

12 and 14 are equal and that the collector and emitter currents of transistor 12 are equal. The above equation indicates that the current  $I_1$  is dependent on the magnitude of  $V_{BE}$ , the temperature coefficient of which is approximately -2 mV/ $^{\circ}$  C.

The emitter terminal 22 of transistor 14 and base terminal 24 of transistor 12 are connected to the base terminal 34 of transistor 16, which provides the output current for current source 10. The output current l2 flows from the collector terminal 36 to the emitter terminal 38 of transistor 16 through a resistor 40 of value "R<sub>3</sub>" to ground. Collector terminal 36 of transistor 16 which is biased to a voltage of sufficient magnitude to ensure proper operation of transistor 16 can be connected, for example, to an emitter-coupled differential amplifier or the emitter terminal of an emitter-follower transistor. The output current I2 flowing through transistor 16 is determined by application of Kirchoff's voltage law and can be expressed as:  $I_2 = I_1 \times R_2 R_3$ .

The above equation is correct under the assumptions that the base-to-emitter voltages of transistors 12 and 16 are equal and that the collector and emitter currents of transistor 16 are equal. The above equation indicates that the output current l2 of current source 10 is directly proportional to the reference current, which is function of  $V_{\text{BE}}$ . The dependence of the output current  $I_2$  on  $V_{\text{BE}}$  is undesirable because its value varies with changes in temperature and is unpredictable, usually to within 100 mV for different integrated circuits in which current sources of this type are typically incorporated. The output current l2 is, therefore, constant only for operating temperatures within a relatively small range and predictable only to the extent to which the value of VBE is known.

With reference to Fig. 2, a current source 50 constitutes a first preferred embodiment of the present invention which includes the prior art current source 10 of Fig. 1 and a compensating circuit 52. Compensating circuit 52 develops a current  $I_A$  which flows from collector terminal 18 to emitter terminal 30 of transistor 12 and reduces the dependence of the reference current  $I_1$  on the base-to-emitter voltages of the transistors employed in current source 50.

Compensating circuit 52 includes a diode-connected NPN transistor 54 whose base terminal 56 and collector terminal 58 are connected to a resistor 60 fo value "R $_{\rm 4}$ " which is connected to V $_{\rm CC}$ . The emitter terminal 62 of transistor 54 is connected to the emitter terminal 64 of a PNP transistor 66 whose collector terminal 68 is connected to ground. Transistor 66 is preferably a substrate PNP transistor when current source 50 is implemented in integrated circuit form. A resistor 70 of value "R $_{\rm 1}$ " is connected between the collector terminal

58 of transistor 54 and the base terminal 72 of transistor 66. The voltage drop across resistor 70 determines the value of the compensating current  $I_A$ , which flows through resistor 70. The value  $R_4$  of resistor 60 is chosen so that the current flowing through resistor 60 is greater than  $I_A$ . Transistors 54 and 66 and resistor 60 are chosen to provide approximately the same base-to-emitter voltages,  $V_{BE}$ , as those of transistors 12, 14, and 16; therefore, the magnitude of the compensating current  $I_A$  can be expressed as 2 x  $V_{BE}/R_1$ . Since substantially all of the compensating current  $I_A$  flows into collector terminal 18 of transistor 12, the total current flowing through resistor 32 equals the sum of  $I_1 + I_A$ , which can be expressed as:

$I_1 + I_A = (V_{CC} - 2 \times V_{BE})/(R_1 + R_2) + 2 \times V_{BE}/R_1$ . =  $V_{CC}/(R_1 + R_2)$ .

The above equation shows that the total current  $l_1$  +  $l_A$  flowing through resistor 32 is independent of  $V_{BE}$ . The output current  $l_2$  can be expressed as:

$$\begin{split} I_2 &= (I_1 + I_A) \times R_2 \cdot R_3 \\ &= V_{CC} \times R_3 \cdot (R_1 + R_2) \times R_1 \end{split}$$

The above equation indicates that the output current  $I_2$  of current source 50 is also independent of  $V_{\text{BE}}$ .

It will be appreciated that replacing transistor 54 with a short circuit conductor between resistor 60 and emitter terminal 64 of transistor 66 and changing the value of resistor 70 to  $R_1/2$  provide the same reference current  $I_1$  and output current  $I_2$  as those calculated above.

With reference to Fig. 3, a current source 100 constitutes a second preferred embodiment of the present invention which includes the prior art current source 10 of Fig. 1 and a compensating circuit 102. Compensating circuit 102 develops a current I<sub>A</sub> which flows from collector terminal 18 to emitter terminal 30 of transistor 12 and reduces the dependence of the reference current I<sub>1</sub> on the base-to-emitter voltages of the transistors employed in current source 100. Compensating circuit 102 is identical with compensating circuit 52 of Fig. 2, with the exception that a diode-connected NPN transistor 104 is positioned between transistors 54 and 66.

The base terminal 106 and collector terminal 108 of transistor 104 is connected to emitter terminal 62 of transistor 54, and the emitter terminal 110 of transistor 104 is connected to emitter terminal 64 of transistor 66. The voltage drop across resistor 70 determines the value of the compensating current  $I_A$ , which flows through resistor 70. Transistor 104 and resistor 60 are chosen to provide approximately the same base-to-emitter voltage,  $V_{BE}$ , as those of transistors 12, 14, 16, 64; 66; therefore, the magnitude of the compensating current  $I_A$  can be expressed as 2 x  $V_{BE}/R_1$ . Since the currents  $I_1$  and  $I_A$  have the same values as those of the corresponding ones of current source 50 of Fig.

15

25

30

35

45

50

55

2. the output current  $l_2$  flowing through resistor 40 has the same value as that derived above for current source 50. The output current  $l_2$  is, therefore, independent of  $V_{BE}$ . A resistor 112 (shown in phantom) positioned between base terminal 34 of transistor 16 and ground may be necessary to provide a conduction path for a portion of the current flowing from base terminal 72 of transistor 66 to ensure such current does not exceed the sum of the currents flowing through base terminal 24 of transistor 12 and base terminal 34 of transistor 16.

With reference to Fig. 4, a current source 120 constitutes a third preferred embodiment of the present invention which includes a prior art current source 122 and a compensating circuit 104. Current source 122 is identical with current source 10 of Fig. 1, with the exception that a conductor 126, which provides a short circuit connection between collector terminal 18 and base terminal 24 of transistor 12, replaces transistor 14. An optional resistor 128 (shown in phantom) can be positioned between base terminal 24 of transistor 12 and a junction node 130 to compensate for  $\beta_F$  dependence of transistors 12 and 16 on the output current l2. The reference current l1' flowing through transistor 12 is determined by application of Kirchoff's voltage law and can be expressed as:

$$I_{1'} = (V_{CC} - V_{BE})/(R_1 + R_2).$$

The above equation is correct under the assumption that the collector and emitter currents of transistor 12 are equal. The output current  $I_2$ , flowing through resistor 32 is determined by application of Kirchoff's voltage law and can be expressed as:  $I_{2'} = I_1 \times R_2 \cdot R_3$ .

The above equation is correct under the assumptions that  $\beta_F$  equals  $\infty$  and the base-to-emitter voltages of transistors 12 and 16 are equal.

Compensating circuit 124 develops a current IA', which flows from collector terminal 18 to emitter terminal 30 of transistor 12 and offsets the dependence of current l<sub>1</sub> on the base-to-emitter voltages of the transistors employed in current source 122. Compensating circuit 124 is identical with compensating circuit 52 of Fig. 2, with the exception that a short circuit replaces diode-connected transistor 104. The voltage across resistor 70 is the base-to-emitter voltage, VBE, of transistor 66, which provides the compensating current IA' of value V<sub>BF</sub>:R. Since substantially all of the compensating current IA' flows into collector terminal 18 of transistor 12, the current flowing through resistor 32 equals the sum of  $l_{1'} + l_{A'}$ , which can be expressed as:

$$I_{1'} + I_{A'} = (V_{CC} - V_{BE})/(R_1 + R_2) + V_{BE}/R_1$$

=  $V_{CC}(R_1 + R_2)$ .

The above expression shows that the composite current  $I_{1'}$  +  $I_{A'}$  has the same value as  $I_{1'}$  of Fig. 2.

The reason is that the effect of removing transistor 14, which affects the value of  $l_1$ , offsets the effect of removing transistor 54, which affects the value of  $l_A$ . The output current  $l_{2'}$  can be expressed as:

$$I_2 = (I_{1'} + I_{A'}) \times R_2/R_3$$

$$= V_{CC} \times R_{3}/(R_1 + R_2) \times R_1.$$

The above expression indicates that the output current  $l_{2}$  of current source 120 is also independent of  $V_{BE}$  and is the same as the output current  $l_{2}$  of current source 50 of Fig. 2.

It will be appreciated that the three preferred embodiments described above can operate with the use of a single power supply having a magnitude as low as about 3 volts.

It will be obvious to those having skill in the art that many changes may be made in the above-described details of the preferred embodiments of the present invention without departing from the underlying principles thereof. The scope of the present invention should be determined, therefore, only by the following claims.

#### Claims

1. In a controlled current source having a current mirror circuit that includes a first transistor for providing a reference current from which an output current is derived at a particular temperature, the first transistor having a first junction of semiconductor materials across which develops a potential difference that changes with temperature and thereby changes the magnitude of the output current, a method of stabilizing the magnitude of the output current with respect to said changes in temperature, comprising:

introducing a compensating current flow through the first transistor, the compensating current changing with temperature to offset corresponding changes in the reference current, thereby to provide a generally temperature-invariant output current

- 2. The method of claim 1 in which the compensating current is derived from a second transistor having a second junction of semiconductor materials across which develops a potential difference that is substantially identical with and changes in a manner similar to that of the first transistor, thereby to provide an output current that is essentially independent of the potential difference across the first transistor.

- 3. The method of claim 1 in which the first transistor is of the bipolar type whose base-emitter junction constitutes the first junction, and in which the compensating current is introduced so that it flows through the first transistor to offset changes in the reference current with temperature.

- 4. The method of claim 3 in which the compensating current is derived from a second transistor of the bipolar type having a second base-emitter junction of semiconductor materials across which develops a potential difference that is substantially identical with that of the first bipolar transistor.

- 5. A temperature compensated current source, comprising:

a current mirror circuit including a first transistor having a first junction of semiconductor materials across which develops a potential difference that changes with temperature;

reference current means for causing a reference current to flow between the first junction and a load impedance, the reference current having a magnitude that depends on the potential difference across the first junction; and

compensating current means for causing a compensating current to flow across the first transistor, the compensating current changing with temperature so that it offsets corresponding changes in the reference current, thereby to provide through the load impendance a generally temperature-invariant current.

- 6. The current source of claim 5 in which the reference current means comprises a second transistor having a second junction of semiconductor materials across which develops a second potential difference and a resistor electrically connected to the second transistor, the resistor conducting a current of changing magnitude in response to changes in the magnitude of the second potential difference to thereby provide through the load impendance a current whose magnitude is substantially independent of the first potential difference.

- 7. The current source of claim 5 in which the reference current means comprises a second transistor having a second junction of semiconductor materials across which develops a second potential difference and a resistor electrically connected to the second transistor, the resistor conducting a current of changing magnitude in response to changes in the magnitude of the second potential difference.

- 8. The current source of claim 7 in which the first potential difference and the second potential difference are substantially equal, and substantially all of the current flowing through the resistor constitutes the compensating current.

10

15

20

25

30

35

40

50

## **EUROPEAN SEARCH REPORT**

EP 88 10 0516

|         | DOCUMENTS CONSIDE                                                                                               |                                    | 1                    | CL ACCIPICATION OF THE                        |

|---------|-----------------------------------------------------------------------------------------------------------------|------------------------------------|----------------------|-----------------------------------------------|

| ategory | Citation of document with indica<br>of relevant passag                                                          |                                    | Relevant<br>to claim | CLASSIFICATION OF THE APPLICATION (Int. Cl.4) |

| А       | US-A-4 325 017 (SCHAD<br>* Abstract; figures 5,<br>7 - column 5, line 48                                        | 6; column 4, line                  | 1-8                  | G 05 F 3/26                                   |

| A       | GB-A-2 118 336 (BURR * Figure 2; page 2, li 3, lines 9-11 *                                                     | BROWN RESEARCH)<br>nes 32-48; page | 1-8                  |                                               |

| A       | US-A-4 503 381 (BOWEF<br>* Figure 2; column 3,<br>4, line 15; claim 1 *                                         |                                    | 1-4                  |                                               |

| Α       | PATENT ABSTRACTS OF JA<br>12 (P-421)[2069] 17th<br>JP-A-60-168 223 (NIPPO<br>31-08-1985<br>* Abstract; figure * | January 1986; &                    | 1,5                  |                                               |

|         |                                                                                                                 |                                    |                      | TECHNICAL FIELDS<br>SEARCHED (Int. Cl.4)      |

|         |                                                                                                                 |                                    |                      | G 05 F 3/00                                   |

|         | The present search report has been                                                                              | drawn up for all claims            |                      |                                               |

|         |                                                                                                                 | Date of completion of the search   | ľ                    | Examiner<br>ARY F.M.                          |

| 1111    | E HAGUE                                                                                                         | 06-04-1988                         | CLEA                 | VIV. I . I'I.                                 |

EPO FORM 1503 03.82 (P0401)

X: particularly relevant if taken alone

Y: particularly relevant if combined with another document of the same category

A: technological background

O: non-written disclosure

P: intermediate document

after the filing date

D: document cited in the application

L: document cited for other reasons

&: member of the same patent family, corresponding document