11 Veröffentlichungsnummer:

**0 349 793** A2

# (12)

# EUROPÄISCHE PATENTANMELDUNG

(21) Anmeldenummer: 89110522.3

(51) Int. Cl.4: H03M 1/20

(22) Anmeldetag: 10.06.89

3 Priorität: 14.06.88 DE 3820174

(43) Veröffentlichungstag der Anmeldung: 10.01.90 Patentblatt 90/02

Benannte Vertragsstaaten: **DE FR GB**

71) Anmelder: Philips Patentverwaltung GmbH Wendenstrasse 35 Postfach 10 51 49 D-2000 Hamburg 1(DE)

⊗ DE

Anmelder: N.V. Philips' Gloeilampenfabrieken Groenewoudseweg 1 NL-5621 BA Eindhoven(NL)

⊗ FR GB

Erfinder: Pichlik, Herbert, Dipl.-Ing. (FH)

Hersbrucker Strasse 3

D-8503 Altdorf/b.Nürnberg(DE)

Vertreter: Peuckert, Hermann, Dipl.-Ing. et al Philips Patentverwaltung GmbH Wendenstrasse 35 Postfach 10 51 49 D-2000 Hamburg 1(DE)

### Schaltungsanordnung zur Analog-Digital-Umsetzung.

Zur Analog-Digital-Umsetzung sind Schaltungsanordnungen mit einem analogen Subtrahierer, dessen Subtraktionseingang das Ausgangssignal eines

Digital-AnalogWandlers zugeführt ist, mit einem

Analog-Digital-Wandler, welcher mit dem Ausgang

des analogen Subtrahierers verbunden ist und mit

einer Steuervorrichtung und einer Schaltungseinheit

zur Fehlerkorrektur, bekannt. Mit der neuen Schaltungsanordnung soll in zwei Wandlungsschritten eine

höhere Auflösung erreicht und die Wandlungszeiten

verkürzt werden.

Hierzu besteht der analoge Subtrahierer aus mindestens zwei Differenzverstärkern und einem analogen Multiplexer, wobei die Ausgänge der Differenzverstärker mit Eingängen des analogen Multiplexers verbunden sind.

EP 0

#### Schaltungsanordnung zur Analog-Digital-Umsetzung

25

40

Die Erfindung betrifft eine Schaltungsanordnung zur Analog-Digital-Umsetzung mit einem analogen Subtrahierer, dessen Subtraktionseingang mit einem Ausgang eines Digital-Analog-Wandlers gekoppelt ist, mit einem Analog-Digital-Wandler, welcher mit dem Ausgang des analogen Subtrahierers verbunden ist und mit einer Steuervorrichtung und einer Schaltungseinheit zur Fehlerkorrektur.

1

Eine Schaltungsanordnung zur Analog-Digital-Umsetzung ist z.B. aus US 4,618,850 bekannt. Eine, mit einem Sample-and-Hold-Glied abgetastete, analoge Spannung ist einem ersten Eingang eines Subtrahierers zugeführt. Der Ausgang des Subtrahierers ist mit einem Analog-Digital-Wandler mit 4-Bit-Auflösung verbunden. Der aus vier Bit bestehende digitale Ausgangswert des Analog-Digital-Wandlers ist einem ersten Eingang eines digitalen Addierers zugeführt. Der Ausgangswert des Addierers wird in einem Summenregister zwischengespeichert und über ein Ausgangsregister ausgegeben. Der Ausgang des Summenregisters ist mit dem Eingang eines Digital-Analog-Wandlers, dessen Auflösung fünf Bit beträgt, verbunden. Der Ausgang des Digital-Analog-Wandlers ist mit einem zweiten Eingang des analogen Subtrahierers verbunden. Der analoge Subtrahierer bildet die Differenzspannung zwischen den an seinem ersten Eingang und an seinem zweiten Eingang anliegenden analogen Spannungen.

Durch die Steuervorrichtung wird zu Beginn einer Analog-Digital-Umsetzung das Summenregister auf den Wert Null zurückgesetzt. Hierdurch ist der Ausgangswert des Digi tal-Analog-Wandlers Null, so daß die am ersten Eingang des analogen Subtrahierers anliegende Spannung unverändert den Analog-Subtrahierer passiert. Der Analog-Digital-Wandler quantisiert diese Spannung und erzeugt einen entsprechenden digitalen Wert. Dieser Wert wird im Summenregister gespeichert und dem Digital-Analog-Wandler zugeführt. Wegen der groben Quantisierung und eventuellen Linearitätsfehlern des Analog-Digital-Wandlers in dem ersten Wandlungsschritt weicht die analoge Ausgangsspannung des Digital-Analog-Wandlers von der analogen Eingangsspannung ab. Der analoge Subtrahierer bildet die Differenzspannung, welche in einem zweiten Wandlungsschritt ein zweites Digitalwort erzeugt. Das erste und das zweite Digitalwort werden in dem Addierer zu einem Wert mit der Datenbreite fünf Bit zusammengesetzt. Digitaler Addierer und Summenregister bilden eine Schaltungseinheit zur Fehlerkorrektur, mit welcher Quantisierungsfehler des Analog-Digital-Wandlers kompensiert werden. Auf diese Weise wird mit einem n-bit-Analog-Wandler und einem n+1-bit-DigitalAnalog-Wandler in zwei aufeinanderfolgenden Schritten ein n + 1-bit genaues Ergebnis erzielt.

Aufgabe der Erfindung ist es, eine Schaltungsanordnung zur Analog-Digital-Umsetzung der eingangs genannten Art anzugeben, mit welcher in zwei Wandlungsschritten eine höhere Auflösung erreicht wird und die Schaltungsanordnung so auszugestalten, daß die Wandlungszeiten verkürzt werden.

Diese Aufgabe wird dadurch gelöst, daß der analoge Subtrahierer aus mindestens zwei Differenzverstärkern und einem analogen Multiplexer besteht, wobei die Ausgänge der Differenzverstärker mit Eingängen des analogen Multiplexers verbunden sind.

Vorteilhafte Ausgestaltungen ergeben sich aus den Unteransprüchen.

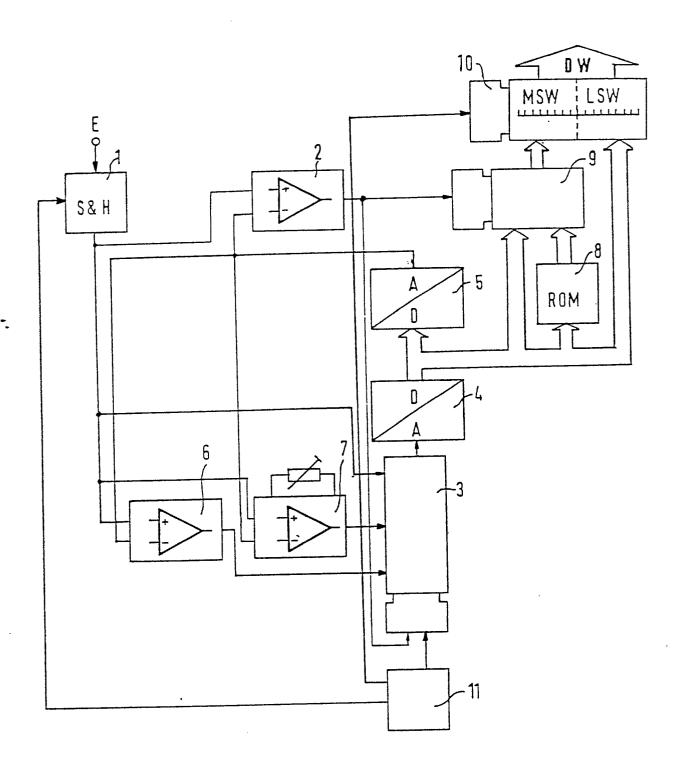

Die Erfindung wird nun anhand eines in der Zeichnung dargestellten Ausführungsbeispieles näher beschrieben und erläutert.

Eine am Eingang E eines Sample-and-Hold-Gliedes 1 anliegende Spannung wird in zwei Wandlungsschritten in einen Digitalwert DW umgesetzt. Hierzu ist eine Steuervorrichtung 11 mit einem Steuereingang des Sample-and-Hold-Gliedes 1 verbunden. Zu Beginn jedes ersten Wandlungsschrittes wird durch einen Steuerimpuls das abgetastete Eingangssignal an den Ausgang des Sample-and-Hold-Gliedes 1 durchgeschaltet. Unabhängig vom weiteren zeitlichen Verlauf des Eingangssignales wird dieser an den Ausgang des Sample-and-Hold-Gliedes durchgeschaltete Spannungswert, im folgenden als Abtastspannung bezeichnet, während der zwei Wandlungsschritte konstant gehalten.

Die Abtastspannung ist einem ersten Eingang eines Komparators 2, einem ersten Eingang eines Analog-Multiplexers 3 und jeweils ersten Eingängen eines ersten und eines zweiten Differenzverstärkers 6 und 7 zugeführt. Die Ausgänge der Differenzverstärker 6 und 7 sind mit zweiten und dritten Eingängen des Analog-Multiplexers 3 verbunden. Das Ausgangssignal des Komparators 2 ist einem ersten Steuereingang des Analog-Multiplexers 3 und einem Steuereingang eines Digital-Multiplexers 9 zugeführt. Das Ausgangssignal des Analog-Multiplexers 3 ist einem Analog-Digital-Wandler 4 zugeführt. Der Analog-Digital-Wandler 4 wandelt das vom Analog-Multiplexer 3 durchgeschaltete Analog-Signal in einen Binärwert. Der im Ausführungsbeispiel verwendete Analog-Digital-Wandler hat eine Auflösung von acht Bit. Als maximale Eingangsspannung wird im folgenden jene Spannung bezeichnet, welche gerade den größten Binärwert des Analog-Digital-Wandlers erzeugt. Als

10

20

Auflösespannung wird im folgenden jene Eingangsspannungsdifferenz des Analog-Digital-Wandlers 4 bezeichnet, bei der sich der ausgegebene Binärwert des Analog-Digital-Wandlers 4 gerade um ein LSB (Last significant bit) ändert.

Der Binärwert ist einem Digital-Analog-Wandler 5, einem Festwertspeicher 8 und dem Digital-Multiplexer 9 zugeführt.

Ein weiterer Ausgang der Steuerschaltung 11 ist einem zweiten Steuereingang des Analog-Multiplexers 3 zugeführt. Unabhängig vom Zustand des vom Komparator 2 stammenden Steuersignales wird der Analog-Multiplexer 3 durch das von der Steuerschaltung 11 stammende Steuersignal so angesteuert, daß beim ersten Wandlungsschritt stets die Abtastspannung dem Eingang des Analog-Digital-Wandlers 4 zugeführt ist. Der in diesem ersten Wandlungsschritt vom Analog-Digital-Wandler 4 abgegebene Binärwert wird im folgenden als Grobwert bezeichnet. Durch den Digital-Analog-Wandler 5 wird der Grobwert des Abtastsignales in eine analoge Spannung zurückgewandelt, welche im folgenden als rückgewandelte Spannung bezeichnet wird.

Bei einer Änderung des binären Eingangswertes des Digital-Analog-Wandlers 5 um den Binärwert Eins ändert sich die Ausgangsspannung des Digital-Analog-Wandlers 5 um einen bestimmten analogen Spannungswert. Der Digital-Analog-Wandler 5 wurde im Ausführungsbeispiel so gewählt, daß dieser Spannungswert genau der Auflösespannung des Analog-Digital-Wandlers 4 entspricht. Auf diese Weise entspricht die rückgewandelte Spannung nach dem ersten Wandlungsschritt in etwa der Abtastspannung. Die Span nungsdifferenz zwischen diesen beiden Spannungen wird im folgenden als Quantisierungsfehler bezeichnet. Dieser Quantisierungsfehler entsteht aus der auf acht Bit begrenzten Auflösung des Analog-Digital-Wandlers 4. Der Quantisierungsfehler liegt daher in einem Spannungsbereich zwischen der halben negativen Auflösespannung und der halben Positiven Auflösespannung des Analog-Digital-Wandlers 4. Durch Nichtlinearitäten der beiden Wandler kann der Quantisierungsfehler jedoch auch größer sein.

Die rückgewandelte Spannung ist zweiten Eingängen der Differenzverstärker 6 und 7 zugeführt. Die Differenzverstärker bilden die Differenz zwischen dem ihren ersten Eingängen zugeführten Abtastwert und der ihren zweiten Eingängen zugeführten zurückgewandelten Spannung, wodurch an ihren Ausgängen eine Spannung erzeugt wird, welche proportional zu dem Quantisierungsfehler ist. Im Ausführungsbeispiel beträgt die Verstärkung der Differenzverstärker 6 und 7 zweihundertsechsundfünfzig. Dieser Verstärkungsfaktor entspricht zwei hoch acht, also der Anzahl der Bitkombinationen, in die der Analog-DigitalWandler 4 eine Ein-

gangsspannung aufzulösen vermag. Durch die Verstärkung um das zweihundertsechsundfünfzigfache ist gewährleistet, daß der absolut größte auftretende Quantisierungsfehler maximal den Wert der Auflösespannung erreichen darf, ohne daß der verstärkte Quantisierungsfehler die maximale Eingangsspannung des Analog-Digital Wandlers 4 überschreitet.

Der zweite Differenzverstärker 7 ist mit einer Schaltung zur Einstellung einer konstanten Offsetspannung versehen. Die am Differenzverstärker eingestellte Offsetspannung entspricht genau der Auflösespannung des Analog-Digital-Wandlers 4 und ist so gepolt, daß die Ausgangsspannung des zweiten Differenzverstärkers 7 um das Zweihun dertsechsundfünfzigste dieses Spannungswertes erhöht wird. Bei negativen Quantisierungsfehlern wird auf diese Weise am Ausgang des zweiten Differenzverstärkers 7 eine positive Ausgangsspannung erzeugt.

Ist die Abtastspannung etwas größer als die rückgewandelte Spannung, so ist der Quantisierungsfehler positiv und der Komparator 2, dessen zweitem Eingang die rückgewandelte Spannung zugeführt ist, erzeugt ein positives Ausgangssignal. Ist die rückgewandelte Spannung jedoch kleiner als die Abtastspannung, so ist der Quantisierungsfehler und somit auch die Ausgangsspannung des ersten Differenzverstärkers 6 negativ und der Komparator 2 erzeugt ein negatives Ausgangssignal. Durch ein Steuersignal der Steuervorrichtung 11 wird im zweiten Wandlungsschritt stets einer der beiden Differenzverstärker 6 beziehungsweise 7 über den analogen Multiplexer 3 zum Analog-Digital-Wandler 4 durchgeschaltet. Die Auswahl zwischen diesen beiden Differenzverstärkern erfolgt mittels dem Ausgangssignal des Komparators 2 und zwar so, daß stets das Ausgangssignal desjenigen Verstärkers durchgeschaltet wird, welches in einem Spannungsbereich zwischen Null Volt und der maximalen Eingangsspannung aus Analog-Digital-Wandler 4 entspricht, liegt.

Auf diese Weise werden sowohl der vervielfachte Quantisierungsfehler vom ersten Differenzverstärker 6 als auch der vervielfachte und vorzeichenkorrigierte Quantisierungsfehler vom zweiten Differenzverstärker 7 gleichzeitig erzeugt. Die Auswahl zwischen diesen beiden Spannungen wird über den Analog-Multiplexer 3 vorgenommen. Im Gegensatz zu Schaltungskonzepten, bei welchen zunächst der Binärwert des Quantisierungsfehlers bzw. ein entsprechend korrigierter Binärwert berechnet wird und dann erst von einem Digitalwert in eine Analogspannung gewandelt wird, entfällt bei diesem Konzept diese Berechnungszeit. Die Schaltzeit des Komparators 2 und des Analog-Multiplexers 3 sind gegenüber dieser Berechnungszeit verhältnismäßig gering und ermöglichen

6

auf diese Weise ungefähr eine Halbierung des Zeitintervalles, welches zwischen Ausgabe des ersten Binärwertes und Beginn des zweiten Wandlungsschrittes wegen der Einschwingzeiten der diversen Bauelemente eingehalten werden muß. Auf diese Weise wird eine erhebliche Verkürzung der Wandlungszeit erreicht.

Im zweiten Wandlungsschritt wird der verstärkte Quantisierungsfehler in einen zweiten Binärwert umgesetzt. Dieser zweite Binärwert wird im folgenden als Feinwert bezeichnet.

Grobwert MSW und Feinwert LSW werden in einem Register 10 zu einem digitalen Wert DW mit sechzehn bit Datenbreite zusammengesetzt. War der Quantisierungsfehler positiv, so können Grobwert und Feinwert einfach zusammengesetzt werden. War der Quantisierungsfehler hingegen negativ, so muß der Grobwert zunächst um ein Bit vermindert werden. Damit diese Subtraktion nicht zusätzliche Verzögerungen erzeugt, wird der korrigierte Grobwert mittels eines Festwertspeichers 8 gebildet. Hierzu ist der Binärwert des ersten Wandlungsschrittes mit Adresseingängen des Festwertspeichers verbunden. In den auf diese Weise adressierbaren Speicherplätzen ist jeweils die um den Zahlenwert eins verminderte Adresse gespeichert. Lediglich dieser unter der Adresse Null gespeicherte Wert hat auch den Wert Null. Mittels dem Ausgangssignal des Komparators 2 wird durch den Digital-Multiplexer 9 entweder der Binärwert des ersten Wandlungsschrittes oder der Ausgangswert des Festwertspeichers 8 ausgewählt. Dies bietet den Vorteil, daß sofort nach der Feststellung, ob der Grobwert korrigiert werden soll oder nicht, bereits beide Werte zur Auswahl am Eingang des digitalen Multiplexers 9 zur Verfügung stehen. Da die Schaltzeit des Digital-Multiplexers 9 gering gegenüber der Berechnungszeit des Korrekturwertes ist, führt auch dies zu spürbaren Zeiteinsparungen.

Bei dem geschilderten Ausführungsbeispiel können Quantisierungsfehler maximal bis zur Auflösung des Analog-Digital-Wandlers berücksichtigt werden. Werden Wandler eingesetzt, deren Quantisierungsfehler maximal das Doppelte der Auflösespannung erreichen können, so sind ein dritter und ein vierter Differenzverstärker sowie drei weitere Komparatoren vorzusehen. Der Verstärkungsfaktor dieser Differenzverstärker ist dann ebenfalls gleich dem Verstärkungsfaktor der anderen Differenzverstärker zu wählen. Die Offsetspannung des dritten Differenzverstärkers muß dann mit einer Offsetspannung abgeglichen werden, die die Ausgangsspannung des dritten Differenzverstärkers um das zweihundertsechsundfünfzigfache der Auflösespannung erhöht, während die Offsetspannung des vierten Differenzverstärkers so eingestellt werden muß, daß die Ausgangs spannung dieses Differenzverstärkers um das einhundertachtundzwanzigfache, entsprechend zwei hoch sieben, der Auflösespannung erhöht wird. Weiterhin ist der digitale Multiplexer als Vielfachmultiplexer auszulegen, wobei an die zwei weiteren Eingänge zwei weitere Festwertspeicher angeschlossen werden müssen, welche eine Addition um den Zahlenwert Eins bzw. eine Subtraktion um den Zahlenwert Zwei bewirken. Die Umschaltspannungen der Komparatoren liegen dann jeweils um eine Auflösespannung auseinander und steuern den Analog-Multiplexer als auch den Digital-Multiplexer.

### 15 Ansprüche

1. Schaltungsanordnung zur Analog-Digital-Umsetzung mit einem analogen Subtrahierer, dessen Subtraktionseingang mit einem Ausgang eines Digital-Analog-Wandlers gekoppelt ist, mit einem Analog-Digital-Wandler, welcher mit dem Ausgang des analogen Subtrahierers verbunden ist und mit einer Steuervorrichtung und einer Schaltungseinheit zur Fehlerkorrektur,

#### dadurch gekennzeichnet,

daß der analoge Subtrahierer mindestens zwei Differenzverstärker (6, 7) und einen analogen Multiplexer (3) enthält, wobei die Ausgänge der Differenzverstärker mit Eingängen des analogen Multiplexers (3) verbunden sind.

2. Schaltungsanordnung nach Anspruch 1, dadurch gekennzeichnet,

daß mindestens ein Differenzverstärker eine Anordnung zur Offsetkorrektur aufweist, zur Addierung einer vorgebbaren Offsetspannung zur Ausgangsspannung des Differenzverstärkers.

3. Schaltungsanordnung nach Anspruch 2, dadurch gekennzeichnet,

daß die Offsetspannung so gewählt ist, daß sich die Ausgangsspannungen der Differenzverstärker (6, 7) jeweils um ein ganzzahliges Vielfaches der Auflösespannung des Digital-Analog-Wandlers (5) unterscheiden.

4. Schaltungsanordnung nach einem der Ansprüche 1, 2 oder 3,

## dadurch gekennzeichnet,

daß der Ausgang des Analog-Digital-Wandlers (4) direkt mit einem ersten Eingang eines digitalen Multiplexers (9) und über die Schaltungseinheit zur Fehlerkorrektur (8) mit einem zweiten Eingang des digitalen Multiplexers (9) gekoppelt ist.

5. Schaltungsanordnung nach einem der Ansprüche 1 oder 4,

### dadurch gekennzeichnet,

daß sowohl der Steuereingang des analogen und des digitalen Multiplexers (3, 9) mit der Steuervorrichtung (11) und mit dem Ausgang mindestens eines Komparators (2) verbunden sind. 6. Schaltungsanordnung nach Anspruch 5, dadurch gekennzeichnet,

daß der eine Eingang des einen Komparators (2) mit einem Sample-and-Hold-Glied (1) und der andere Eingang des Komparators (2) mit dem Ausgang des Digital-Analog-Wandlers (5) verbunden sind.