(1) Publication number:

**0 350 610** A2

## (12)

## **EUROPEAN PATENT APPLICATION**

21 Application number: 89109885.7

(1) Int. Cl.4: H01L 21/331

22) Date of filing: 01.06.89

3 Priority: 14.07.88 US 219020

Date of publication of application: 17.01.90 Bulletin 90/03

Designated Contracting States:

CH DE ES FR GB IT LI NL SE

Applicant: International Business Machines Corporation Old Orchard Road Armonk, N.Y. 10504(US)

Inventor: Burghartz, Joachim N.

81 Morningside Drive

Croton-on-Hudson, N. Y. 10520(US)

Inventor: Ginsberg, Barry J.

3489 Old Yorktown Road

Yorktown Heights, N.Y. 10598(US)

Inventor: Mader, Siegfried R.

9 Darby Avenue

Croton-on-Hudson, N.Y. 10520(US)

(24) Representative: Gaugel, Heinz, Dipl.-Ing. IBM Deutschland GmbH Schönaicher Strasse. 220

D-7030 Böblingen(DE)

Bipolar transistor having self-aligned emitter-base and method of forming same using selective and non-selective epitaxy.

57 Bipolar transistors having self-aligned emitterbase regions and a method of forming such transistors using selective and non-selective epitaxy are disclosed. A substrate (12) of semiconductor material of a first conductivity type, a portion of which forms a collector region is provided. A first layer (18) of semiconductor material of a second conductivity type is deposited on said substrate, a portion of which forms an intrinsic base region. Over a portion of said first layer (18) an element (30) of insulating material is formed. Said intrinsic base region is formed below said element (30) and the remainder ef said first layer forms an extrinsic base region. A second layer (32) of semiconductor material of said second conductivity type is deposited on said first Olayer (18). A portion of said second layer laterally overgrows onto a portion of an upper surface (33) of usaid element (30) defining an aperture (29) and leaving an exposed region (31) on the upper surface (33). The second layer (32) forms a portion of the

extrinsic base region. On said second layer (32) a layer (42) of insulating material is formed which narrows said aperture (29) and said exposed region (31) of said element (30). Said narrowed exposed region (31) of said element (30) is removed to expose a portion (50) of said first layer (21) below said aperture (29) and an emitter region (54) of said first conductivity type is formed in said first layer (21) through said aperture (44).

FIG. 7

## BIPOLAR TRANSISTOR HAVING SELF-ALIGNED EMITTER-BASE AND METHOD OF FORMING SAME USING SELECTIVE AND NON-SELECTIVE EPITAXY

This invention relates to the manufacture of bipolar transistors, and more particularly, to the method of forming the emitter window for a bipolar transistor having self-aligned emitter-base regions.

1

In the manufacture of bipolar transistors, much is research has been directed to increasing transistor speed. One approach to increasing the speed is by means of the transistor geometry. For high speed bipolar transistors, the two critical dimensions are the emitter stripe width and the base thickness. The emitter stripe width is defined by the lateral dimension of the emitter region, while the base thickness is defined by the vertical dimension of the base region. It is desirable to manufacture transistors with both the emitter strip width and the base thickness as small as possible so as to reduce the base resistance for the reason that base resistance is a major impediment to the speed of a transistor. Moreover, the ratio of the length to the width of the emitter should be as large as possible and since the emitter length is determined by other manufacturing constraints, the emitter stripe width is the only dimension that can be adjusted to reduce the base resistance.

In the manufacture of conventional bipolar transistors, the emitter window which defines the stripe width is located and sized by the use of photolithography. A photolithographic mask is positioned onto a layer of polysilicon which has been epitaxially grown onto a single crystal silicon substrate, and an emitter window is then etched through the polysilicon to expose regions of the single crystal silicon. Experience shows that etching an emitter opening into an extrinsic base polysilicon layer without overetch into an intrinsic base region is very difficult. The photolithographic method for defining the emitter window has a size limitation in that, typically the smallest emitter stripe width that can be obtained is approximately 0.7 microns. In addition, the use of photolithography masking techniques results in inaccuracies due to improper alignment with the intrinsic base resulting in poor reproducibility.

Various techniques have been employed to define the emitter window in an attempt to overcome the prior art deficiencies. In U.S. Patent 4,499,657, photolithography is used to define both the emitter and base windows simultaneously thereby reducing some of the misalignment effects. The emitter stripe width is limited to the range between 0.5 to 2 microns.

U.S. Patent 4,504,332 discloses a self-alignment technique for manufacturing a bipolar transistor. A thermal oxide layer, silicon nitride layer and

a boron oxide layer are successively deposited onto a single crystal silicon substrate. Conventional photolithographic techniques are used to etch a window for the formation of both the base and the emitter. A layer of silicon is epitaxially grown over the entire substrate with polysilicon being formed on the insulating layer and single crystal being formed on the exposed region of the substrate. The polysilicon regions are doped to form external base regions. A conformal layer of thermal oxide is deposited over the poly and single crystal silicon regions and the thermal oxide is etched to expose the single crystal. An internal base region is formed by implantation and the emitter region is formed by diffusion from a conformal doped oxide layer. Contact holes are then etched in the oxide layer for the emitter, base and collector. While the emitter and base are self-aligned, the process steps are numerous and complicated. In addition, the emitter window is defined by conventional photolithographic techniques and therefore, the width is limited in size.

This invention is directed to a method for fabricating bipolar transistors wherein the emitter window is defined by the use of selective epitaxial growth of silicon. The inventive method of the present invention results in a transistor having a much narrower emitter stripe width than heretofore possible in the prior art. The emitter stripe width of the transistor of the present invention may be less than 0.5 microns, and can be on the order of 0.1 micron.

The inventive method for fabricating a bipolar transistor comprises the steps of providing a substrate of semiconductor material of a first conductivity type, and depositing by nonselective epitaxy a first layer of semiconductor material of a second conductivity type on the substrate. An element of insulating material is formed over a portion of the first layer, and a second layer of semiconductor material of the second conductivity type is deposited onto said first layer by selective epitaxy. The selective epitaxy results in a portion of the second layer laterally overgrowing onto a portion of an upper surface of the element. An aperture is thereby formed in the second layer leaving an exposed region on the upper surface of the element. A layer of insulating material is formed on the second layer which narrows the aperture and reduces the exposed region of the element. The exposed region of said element is removed to expose a portion of the first layer and a region of the first conductivity type is formed in said first layer through the aperture.

35

In accordance with one embodiment of the invention, an npn transistor is formed wherein the substrate of semiconductor material, such as silicon, having an n-type conductivity is provided with a mesa-like portion surrounded by recessed oxidation isolation regions. A first layer of silicon having a p-type conductivity is deposited over the mesalike portion and the isolation regions by the use of a conventional non-selective epitaxial growth technique. The deposition results in regions of polycrystalline silicon being formed over the isolation regions of the substrate and a region of single crystal silicon being formed over the mesa-like portion. The element of insulating material is formed over a portion of the single crystal region and includes at least a layer of silicon nitride. An oxide layer, such as silicon dioxide, may be provided between the nitride layer and the first layer of silicon.

A second layer of silicon of a p-type conductivity is deposited on the single crystal and polycrystalline silicon regions of the first layer. The deposition of the second layer of silicon results in polysilicon being deposited over the polysilicon in the first layer and single crystal silicon being deposited over the single crystal silicon in the first layer. The second layer of silicon is deposited by a selective epitaxial technique so that a portion of the single crystal material laterally overgrows onto a portion of the nitride resulting in an aperture leaving an exposed region on the surface of the nitride. A layer of insulating material is formed on the second layer of silicon by a high pressure thermal oxidation. The portion of the thermal oxide covering the walls of the aperture narrows the aperture and consequently reduces the width of the exposed region of the nitride. The narrowed exposed region is thereafter removed to expose a portion of the single crystal region of the first layer of silicon.

A region of n-type conductivity is formed in the exposed portion of said single crystal region to form the emitter of the transistor. The area of the single crystal material below the emitter region forms an intrinsic base and the mesa-like region forms the collector of the transistor. The emitter is formed by conventional techniques, such as, depositing a region of undoped polysilicon into the aperture, implanting n-type dopant and annealing to outdiffuse the dopant into the single crystal region. The portions of the single and polycrystalline regions adjacent the intrinsic base and insulating element form extrinsic base regions. Metallic contacts are formed to contact the extrinsic base, the collector and the polysilicon emitter to complete the transistor.

Thus, in accordance with the invention, the window for forming the emitter region is formed by the selective epitaxial growth of semiconductor ma-

terial. The term selective growth as herein employed refers to substantially uniform growth of silicon along surfaces of silicon and in which the silicon overgrows onto a portion of an insulating element. A selective epitaxial growth technique is preferrably utilized with growth conditions such that equal growth rates in both the vertical and horizontal directions for the region of overgrowth is provided. The overgrowth is controlled and stopped to form the desired emitter stripe width. A high pressure thermal oxidation layer is deposited on the selective epitaxial layer to insulate the polysilicon emitter from the extrinsic base regions which also has the effect of further reducing the size of the emitter stripe width. The formation of the emitter window by this method provides for the self-aligned formation of the intrinsic base and emitter. The prior art limitations of the photolithographic techniques for forming the emitter window are substantially avoided by the present invention. The adjustment of the size of the emitter window by the selective epitaxial growth and the readjustment of that window by the spacer thermal oxide allows for very good reproducibility. The completely single crystalline extrinsic base allows for a minimal depth of the emitter window and therefore a very low emitter resistance. In addition, the resistance of the polysilicon extrinsic base can be further lowered by silicide formation. The oxide spacer prevents tunneling between the high doped outdiffusions of the emitter and the extrinsic base.

Ways of carrying out the invention are described in detail below with reference to drawings which illustrate specific embodiments, in which:

Figs. 1-7 are schematic sectional views illustrating steps of manufacturing a bipolar transistor according to an embodiment of the invention.

Fig. 8 is a schematic sectional view of a bipolar transistor of another embodiment of the invention.

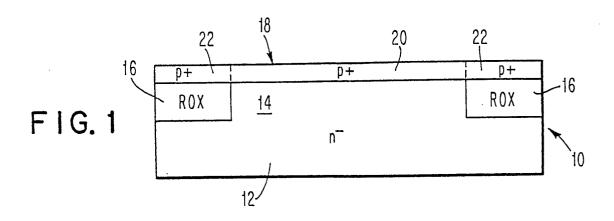

Referring now to the drawings, Figure 1 depicts a structure 10 that includes a single crystal silicon substrate 12 having a mesa-like portion 14 surrounded by isolation regions 16. The mesa-like portion is doped with a first conductivity type. The illustrative embodiment shown in the drawings is of an npn transistor, however, it should be understood that the method of the invention may also be utilized to form a pnp transistor. The mesa-like region 14 is typically lightly n-doped by conventional diffusion or implantation techniques and region 16 are well known recessed oxide regions. A non-selective epitaxial layer 18 of semiconductor material is grown on the substrate 12 by conventional epitaxial growth techniques. The silicon grows in a single crystalline form in region 20 above the single crystalline mesa-like region 14 and polysilicon is grown in regions 22 above the

20

35

40

recessed oxide regions 16. In the drawing, the broken lines indicate the interface of the single crystal and polycrystalline regions. The layer 18 is p-doped typically in the range of 2 x  $10^{18}$  cm<sup>-3</sup> The doping of the layer 18 may be provided simultaneously with the epitaxial growth or the dopant may be subsequently implanted into the layer. Layer 18, typically is in the range between 50 and 100 nm thick.

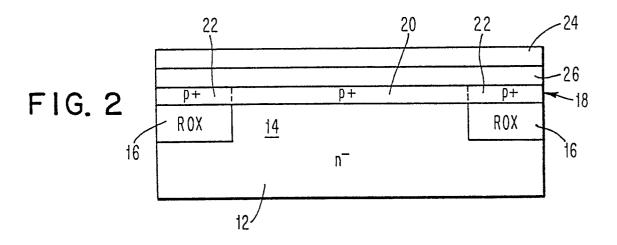

An insulating element is formed on the layer 18 by depositing at least a barrier layer 24, typically of silicon nitride on the layer 18. In the illustrative embodiment shown in Figure 2, a thermal oxide layer 26, typically of silicon dioxide, is first deposited on the layer 18 and the silicon nitride layer 24 is then deposited on the oxide layer 26. The oxide layer 26 is typically in the range of 4 nm thick and the nitride layer 24 is typically in the range of 30 nm. The nitride layer may be deposited by a low pressure chemical vapor deposition (LPCVD) technique.

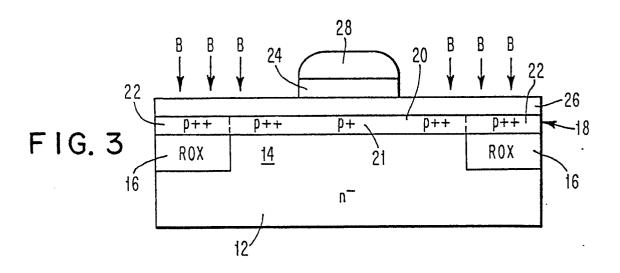

As shown in Figure 3, a resist 28 is placed on the nitride layer 24 over the mesa-like region 14. The width of the resist 28 will define the insulating element of the final structure and should be provided larger than the desired emitter stripe width. Reactive ion etching is then utilized to etch away the nitride layer and exposed the oxide layer 26. Optionally, a very shallow implantation of boron may be made through the oxide layer 26 to highly dope the portions of the silicon layer 18, typically in the range of 2x10<sup>19</sup> cm<sup>-3</sup>, on both sides of the nitride layer 24. The additional doping lowers the resistance of these regions, which form part of the extrinsic base of the transistor. The p+ region 21 below the nitride element 24 forms the intrinsic hase.

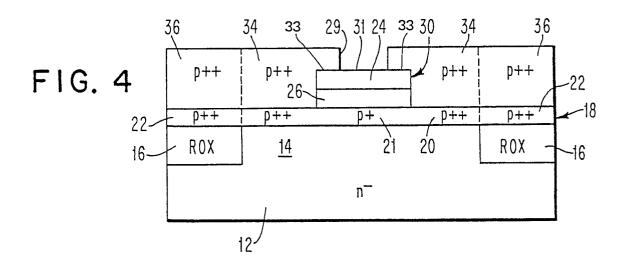

As shown in Figure 4, the oxide layer 26 is then removed by a wet etch such as dilute HF, the resist is removed and the surface of the structure is cleaned. Thus, an insulating element 30 is formed from the remaining portions of layers 24 and 26. Thereafter, selective expitaxy is used to grow a second layer 32 of highly p-doped silicon which selectively overgrows a portion of the insulating element 30. The second layer 32 of silicon grows with single crystal regions 34 over the single crystal region 20 of layer 18 and polysilicon regions 36 over the polysilicon regions 22 of layer 18. Regions 34 and 36, together with the highly p-doped region of layer 18, forms the extrinsic base of the transistor.

The growth of layer 32 initially grows to the thickness of the insulating element 30 and then overgrows onto the element 30 to form an aperture 29 leaving an exposed portion 31 of an upper surface 33 of the element 30. In a preferred embodiment, the selective epitaxial technique results

in equal growth rates in the vertical and horizontal directions. It is known that when the pattern formed by the element 30 is parallel to the (100) crystalline axis, equal growth rates will result. In addition, it is known that the growth rate in the (100) direction is much higher than in the (110) direction. Thus, after reaching the upper surface 33 of the insulating element 30, the layer 32 grows an equal amount laterally along the surface 33 as it grows vertically above surface 33. Thus, a rectangular emitter hole is possible even if the lithography pattern defined by the insulating element 30 is circular in shape. An example of selective epitaxial techniques that may be employed are as shown by Ginsberg, et al., Lower Temperature Selective Epitaxy Using SiCl<sub>4</sub> at Reduced Pressure, Extended Abstracts, 10th Conference on Chemical Vapor Deposition, Electro Chemical Society, Honolulu, Hawaii, 1987, pp. 991, 992.

The selective epitaxial layer 32 is typically grown to a thickness between 100 and 300 nm. Preferrably, the growth temperatures are maintained at 875 °C or lower. Techniques have now been shown in which the epitaxial growth is performed at temperatures below 700 °C. In the practice of the invention, it is desirable to keep the growth temperatures as low as possible to avoid damage to the intrinsic base formed below the insulating element 30. The selective epitaxial growth of layer 32 is deposited under growth conditions that may be easily controlled to provide the aperture 29 with a desired width. The width of the aperture 29 may be less than 0.5 microns, and may be as low as 0.1 micron.

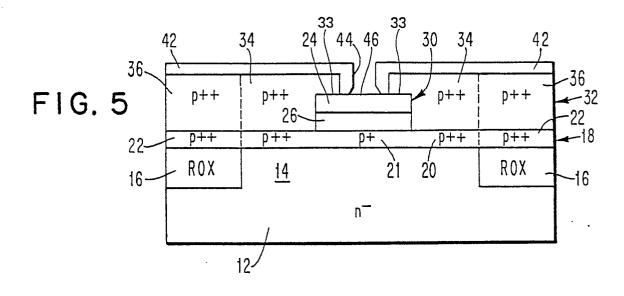

As shown in Figure 5, a thermal oxide layer 42 is deposited onto the selective epitaxy layer 32. The layer 42 isolates the extrinsic base regions from a subsequent polysilicon emitter formation. In addition, the width of the aperture 29 of Figure 4 will be reduced by the deposition of thermal oxide layer 42. The layer 42 is formed preferrably by a high pressure low temperature oxidation process. The layer 42 contacts a portion of the exposed region 31 of the element 30. Thermal oxidation is preferrably performed in temperatures between 700° and 800°C to prevent the intrinsic base region 21 from diffusing out. During the thermal oxidation, the nitride layer 24 acts as an oxide barrier to prevent oxidation of the intrinsic base region 21. The thermal oxide layer 26 functions to relieve distortion that would be present if the nitride layer was directly contacting the layer 18. The oxide layer 42 is typically grown to a thickness of 100 to 200 nm. The layer 42 results in a much narrower aperture 44 and a reduced exposed region 46.

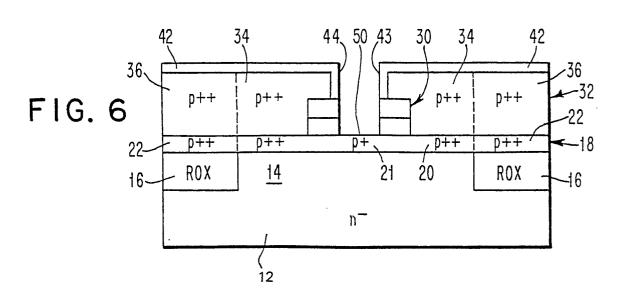

Thereafter, as shown in Figure 6, the exposed portion 46 of the nitride layer is selectively etched

10

typically by a dry etch process and a portion of the oxide layer 26 is removed by a wet etch process to form a trench 43 in the element 30 and expose a region 50 contiguous with the single crystal intrinsic base region 21. A small portion of the thermal oxide layer 42 is also removed within the aperture 44 so that the side edges of the layer 42 and the element 30 are coextensive thereby forming an insulating extension of the trench 43.

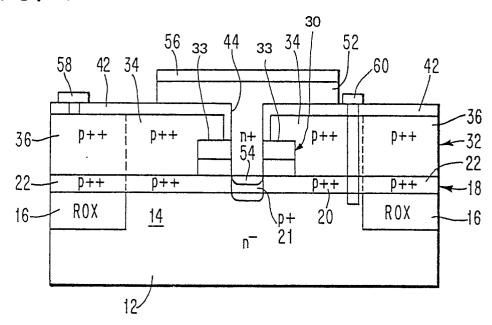

As shown in Figure 7, a conductive element of polysilicon is deposited within the trench 43 and aperture 44 to contact the region 50 and extend over the layer 42. The region of polysilicon 52 is implanted with a dopant, typically arsenic, and heated to diffuse an n-type region 54 into the single crystal region 21 to form the emitter. A portion of the intrinsic base 21 diffuses into the single crystal region 14 in a like amount. A metallic contact 56 is formed on the element 52 as the emitter contact and contacts 58 and 60 are deposited as base and collector contacts, respectively.

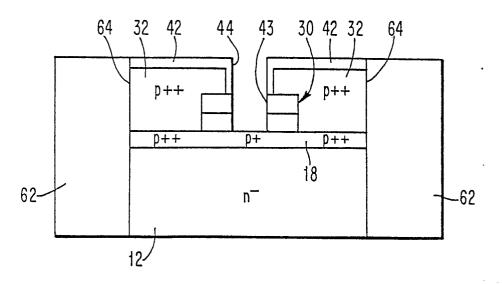

In an alternative embodiment, as shown in Figure 8, isolation regions 62 are formed after the formation of the emitter window 43, 44. In Figure 8, like parts are indicated by like numerals used in Figures 1-7. After the emitter window is defined as described above, trenches 64 are formed and filled with appropriate isolation material to form isolation regions 62. In this embodiment, the layers 18 and 32 are completely single crystal silicon because the substrate 12 is initially provided without isolation regions. Isolation regions 60 may be filled with any insulating material such as an oxide or a nitride or it may also be filled by polysilicon. The emitter regions may then be formed by typical diffusion techniques.

In accordance with the method of the invention, the emitter region 54 and intrinsic base region 21 are formed in a self-aligned manner by use of selective epitaxy to define the emitter window 43, 44. In addition, the vertical spacer provided by layer 42, between the extrinsic base regions 34 and the emitter region 54 prevents tunneling between the high doped outdiffused emitter 54 and the extrinsic base. Thus, optical lithography is no longer necessary to define the emitter window. Optical lithography is only used to define the pattern for forming the insulating element on which the selective epitaxy is grown. The selective epitaxy results in an emitter stripe width in the submicron range which may be less than 0.5 microns and as low as 0.1 micron. The width may be further reduced by the deposition of the insulating laver. Thus, there is no longer a need to etch a whole stack of polysilicon to implant the base and emitter.

While the invention has been particularly shown and described with respect to preferred embodiments thereof, it will be understood by those skilled in the art that the foregoing and other changes in form and details may be made therein without departing from the spirit and scope of the invention which should be limited only by the scope of the appended claims.

## Claims

1. A method for fabricating a bipolar transistor comprising the steps of:

providing a substrate (12) of semiconductor material of a first conductivity type a portion of which forms a collector region;

depositing a first layer (18) of semiconductor material of a second conductivity type on said substrate (12), a portion of which forms an intrinsic base region;

forming an element of insulating material (30) over a portion of said first layer (18), said intrinsic base region being formed below said element (30) and the remainder of said first layer forming an extrinsic base region;

depositing a second layer (32) of semiconductor material of said second conductivity type on said first layer (18), a portion of said second layer laterally overgrowing onto a portion of an upper surface (33) of said element (30) defining an aperture (29) and leaving an exposed region (31) on the upper surface (33), the second layer (32) forming a portion of the extrinsic base region;

forming a layer (42) of insulating material on said second layer (32) which narrows said aperture (29) and said exposed region (31) of said element (30); removing said narrowed exposed region (31) of said element (30) to expose a portion (50) of said first layer (21) below said aperture (29); and forming an emitter region (54) of said first con-

forming an emitter region (54) of said first conductivity type in said first layer (21) through said aperture (44).

- 2. The method of claim 1 wherein the substrate (12) is provided with a mesa-like region (14) of said first conductivity type surrounded by isolation regions (16).

- 3. The method of claim 2 wherein the deposition of the first (18) and second layers (32) of semiconductor material of said second conductivity type are formed with single crystal material (20, 34) over said mesa-like portion (14) and polycrystalline material (22, 36) over said isolation regions (16).

- 4. The method of claim 2 and 3 wherein the element of insulating material (30) is formed over a portion of said single crystal material (20).

- 5. The method of one or more of the preceding claims 1 to 4 wherein the step of depositing a first layer (18) of semiconductor material comprises non-selectively epitaxially growing said first layer (18).

45

- 6. The method of one or more of the preceding claims 1 to 5 wherein the step of forming an element of insulating material (30) includes forming at least an oxidation barrier layer (24).

- 7. The method of claim 6 wherein the step of forming an element of insulating material (30) includes forming an oxide buffer layer (26) disposed between said first layer (18) and said oxidation barrier layer (24).

- 8. The method of claims 6 and 7 wherein said oxidation barrier layer (24) comprises silicon nitride and said oxide buffer layer (26) comprises silicon dioxide.

- 9. The method of one or more of the preceding claims 1 to 8 wherein the step of depositing said second layer (32) of semiconductor material comprises selectively epitaxially growing said second layer (32).

- 10. The method of claim 9 wherein the selective epitaxial deposition is performed under conditions whereby the width of said exposed region (31) on said upper surface (33) of said element (30) is 0.1 microns or less than 0.5 microns.

- 11. The method of one or more of the preceding claims 1 to 10 wherein said element (30) has edges bounded in the (100) crystallographic direction, and said selective epitaxial layer (36) laterally overgrows said element (30) an amount equal to the vertical growth above said element thereby forming a substantially rectangular aperture (29).

- 12. The method of one or more of the preceding claims 1 to 11 wherein the step of forming a layer of insulating material (42) on said second layer (32) comprises depositing a thermal oxide layer under high pressure conditions.

- 13. The method of one or more of the preceding claims 1 to 12 wherein the step of forming said emitter region (54) includes providing a conductive element (52) within said aperture (44) through which said emitter region (54) is outdiffused.

- 14. The method of one or more of the preceding claims 1 to 13 wherein the semiconductor material of the substrate (12) and the first (18) and second (32) layers is silicon.

- 15. The method of one or more of the preceding claims 1 and 5 to 14 further including forming isolation regions within said substrate (12) and first (18) and second (32) layers of semiconductor material on both sides of and spaced from said emitter region (54).

- 16. A bipolar transistor preferably manufactured as described in one or more of the preceding claims 1 and 5 to 15 comprising:

- a single crystal semiconductor substrate (12) of a first conductivity type, a portion of which forms a collector region;

- a layer of semiconductor material (18, 32) of a second conductivity type disposed on said sub-

- strate (12), a portion of which forms an intrinsic base region (21);

- an element of insulating material (30) disposed over a portion of said layer of semiconductor material (18), said intrinsic base region (21) being formed below said element (30) and the remainder (20) of said layer forming an extrinsic base region; a trench (44) formed in said element (30) the bottom (50) of which is contiguous with said layer of semiconductor material (18);

- an emitter region (54) of said first conductivity type extending from the bottom (50) of said trench (44) and disposed within said layer of semiconductor material (18); and

- a conductive element (52) extending into said trench (44) contacting said emitter region (54), said conductive element (52) being disposed in insulated spaced relationship with said extrinsic base region (34).

- 17. The bipolar transistor of claim 16 wherein said insulated spaced relationship between said conductive element (52) and said extrinsic base region (34) is provided by a layer of insulating material (42) covering said layer of semiconductor material (32), said layer of insulating material (42) being coextensive with said trench (43) forming an insulating extension of said trench (43).

- 18. A bipolar transistor preferably manufactured as described in one or more of the preceding claims 1 to 14 comprising:

- a semiconductor substrate (12) of a first conductivity type having a mesa-like portion (14) which is surrounded by isolation regions (16);

- an element of insulating material (30) containing an aperture (29) being disposed over a portion of said mesa-like portion (14), said aperture (29) defining two upper surfaces (33) of said element (30);

- a layer of semiconductor material (18, 32) of a second conductivity type disposed over said substrate (12) and having a first single crystal portion disposed between said element and said mesa-like portion (14), a second single crystal portion (20, 34) in registry with said mesa-like portion (14), and a polycrystalline region (22, 36) extending over said isolation regions (16), said second single crystal portion (34) being laterally overgrown on a portion of each of said upper surfaces (33) of said element (30);

- a layer of insulating material (42) covering exposed surfaces of said layer of semiconductor material (18, 32), the portion of said layer of insulating material covering said laterally overgrown portion being coextensive with said aperture (44) forming an insulating extension of said aperature (44);

- an emitter region (54) of said first conductivity type disposed in said layer of semiconductor material (18) in registry with said aperture (44); and

- a conductive element (52) extending into said ap-

erture (44) and said extension contacting said emitter region (54).

19. The bipolar transistor of one or more of the preceding claims 16 to 18 wherein the layer of semiconductor material of a second conductivity type comprises a layer of non-selective epitaxial silicon (18) deposited on said substrate (12) and a layer of selective epitaxial silicon (32) deposited on said non-selective epitaxial silicon (18), said selective epitaxial silicon (32) laterally overgrowing a portion of said insulating element (30).

20. The bipolar transistor of one or more of the preceding claims 16 to 19 further including a metallic contact (56) attached to said conductive element (52).

FIG. 7

FIG. 8