Europäisches Patentamt

European Patent Office

Office européen des brevets

⑪ Publication number:

0 377 296 A3

⑫

## EUROPEAN PATENT APPLICATION

⑬ Application number: 89313158.1

⑮ Int. Cl.<sup>5</sup>: G06F 12/08

⑭ Date of filing: 15.12.89

⑯ Priority: 04.01.89 US 293221

⑰ Applicant: Compaq Computer Corporation

20555 S.H. 249

Houston Texas 77070(US)

⑰ Date of publication of application:

11.07.90 Bulletin 90/28

⑱ Inventor: Walker, Karl N.

Route 2 Box 186

Hockley Texas 77447(US)

Inventor: Culley, Paul R.

13010 Marron Drive

Cypress Texas 77429(US)

⑲ Designated Contracting States:

DE FR GB IT NL

⑳ Date of deferred publication of the search report:

11.09.91 Bulletin 91/37

⑳ Representative: Brunner, Michael John et al

GILL JENNINGS & EVERY 53-64 Chancery

Lane

London WC2A 1HN(GB)

### ⑳ Programmable option selection and paged memory cache coherency control.

⑳ A cache flush request circuit for a computer system which flushes (72) the cache controller when a circuit board is being configured (62,64,66, 68) or is responding (68,70) to an input/output write opera-

tion (50) is described. The flush operation can be disabled (56,58) for each circuit board location. A cache flush operation can also be directly requested (72,74,76,78,80).

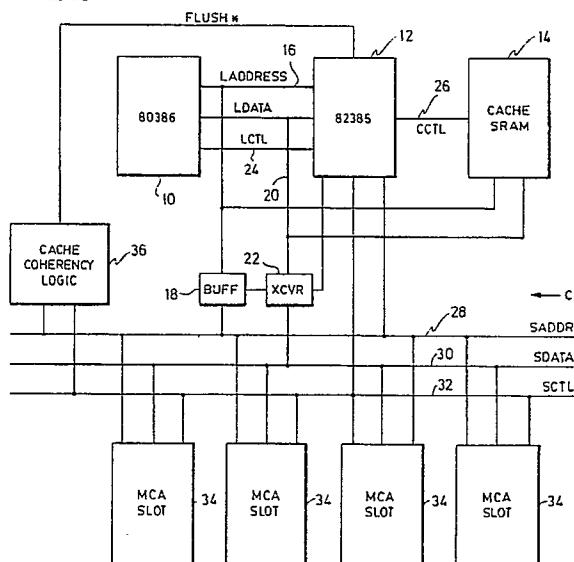

FIG.1

EP 0 377 296 A3

EUROPEAN SEARCH

REPORT

EP 89 31 3158

DOCUMENTS CONSIDERED TO BE RELEVANT

| Category                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Citation of document with indication, where appropriate, of relevant passages                                                                                                                           | Relevant to claim | CLASSIFICATION OF THE APPLICATION (Int. Cl.5) |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------------------------------------|

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | MICROPROCESSORS & MICROSYSTEMS, vol. 12, no. 3, April 1988, pages 147-152; G. LAWS: "Multiprocessing on the Nubus using cache inhibited pages"<br>* Page 150, left-hand column, lines 25-36 *<br>- - -  | 1                 | G 06 F 12/08                                  |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | COMPUTER DESIGN, vol. 26, no. 14, August 1987, pages 89-94; W. VAN LOO: "Maximize performance by choosing best memory"<br>* Page 93, right-hand column, lines 19-41; page 94, upper part *<br>- - - - - | 1                 |                                               |

| <hr/> <p>The present search report has been drawn up for all claims</p> <hr/>                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                         |                   |                                               |

| Place of search                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Date of completion of search                                                                                                                                                                            | Examiner          |                                               |

| The Hague                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 07 June 91                                                                                                                                                                                              | LEDRUT P.         |                                               |

| <p>CATEGORY OF CITED DOCUMENTS</p> <p>X: particularly relevant if taken alone<br/>Y: particularly relevant if combined with another document of the same category<br/>A: technological background<br/>O: non-written disclosure<br/>P: intermediate document<br/>T: theory or principle underlying the invention</p> <p>E: earlier patent document, but published on, or after the filing date<br/>D: document cited in the application<br/>L: document cited for other reasons<br/>&amp;: member of the same patent family, corresponding document</p> |                                                                                                                                                                                                         |                   |                                               |