11) Publication number:

0 416 626 A2

### **EUROPEAN PATENT APPLICATION**

21) Application number: 90117200.7

(51) Int. Cl.<sup>5</sup>: **H01J 1/30**, H01J 9/02

22 Date of filing: 06.09.90

Priority: 07.09.89 JP 233943/89 07.09.89 JP 233945/89 22.08.90 JP 221713/90

43 Date of publication of application: 13.03.91 Bulletin 91/11

Designated Contracting States:

DE FR GB

7 Applicant: CANON KABUSHIKI KAISHA 30-2, 3-chome, Shimomaruko, Ohta-ku Tokyo(JP)

Inventor: Takeda, Toshihiko, c/o Canon Kabushiki Kaisha 30-2, 3-chome, Shimomaruko Ohta-ku, Tokyo(JP) Inventor: Tsukamoto, Takeo, c/o Canon Kabushiki Kaisha

30-2, 3-chome, Shimomaruko

Ohta-ku, Tokyo(JP)

Inventor: Watanabe, Nobuo, c/o Canon

Kabushiki Kaisha

30-2, 3-chome, Shimomaruko

Ohta-ku, Tokyo(JP)

Inventor: Okunuki, Masahiko, c/o Canon

Kabushiki Kaisha

30-2, 3-chome, Shimomaruko

Ohta-ku, Tokyo(JP)

Representative: Pellmann, Hans-Bernd, Dipl.-Ing. et al Patentanwaltsbüro Tiedtke-Bühling-Kinne-Grupe-Pellmann-Grams-Struif Bavariaring 4 W-8000 München 2(DE)

(54) Electron emitting semiconductor device.

(57) An electron emitting semiconductor device comprises a P-semiconductor layer formed on a semiconductive substrate; a Shottky barrier electrode formed on the P-semiconductor layer; plural P<sup>+</sup>-area

units positioned under and facing to the Shottky barrier electrode; and an  $N^{+}$ -area in the vicinity of said  $P^{+}$ -area units.

# FIG.1

EP 0 416 626 A2

#### **ELECTRON EMITTING SEMICONDUCTOR DEVICE**

5

15

25

30

35

40

#### BACKGROUND OF THE INVENTION

#### Field of the Invention

The present invention relates to an electron emitting semiconductor device.

#### Related Background Art

Among conventional electron emitting semiconductor devices, those utilizing avalanche amplification are disclosed for example in the U.S. Patents Nos. 4,259,678 and 4,303,930.

In such electron emitting semiconductor devices, an electron emitting part is constructed by forming a P-semiconductor layer and an N-semiconductor layer on a semiconductor substrate and reducing the work function of the surface of said N-semiconductor layer by depositing cesium or the like, and an inverse bias voltage is applied across the diode composed of said P- and N-semiconductor layers to induce avalanche amplification, whereby electrons are rendered "hot" and emitted from the electron emitting part in a direction perpendicular to the surface of the semiconductor substrate.

However, such conventional electron emitting semiconductor devices have been associated with following drawbacks, because cesium employed in the electron emitting part is chemically very active:

- (1) Extremely high vacuum (1 x  $10^{-10}$  Torr or lower) is required for stable operation;

- (2) Service life and efficiency depend strongly on the level of vacuum; and

- (3) Device cannot be exposed to air.

Also in such conventional electron emitting semiconductor devices, since the electrons which have acquired strong energy by avalanche amplification reach the surface of the electron emitting part through the N-semiconductor layer, a considerable part of said energy is inevitably lost for example by lattice scattering in said N-semiconductor layer. In order to reduce such energy loss, the N-semiconductor layer has to be formed extremely thin (200 Å or less), but formation of such extremely thin N-semiconductor layer with sufficient uniformity and low defect rate is difficult, so that stable preparation of the device is therefore difficult.

#### SUMMARY OF THE INVENTION

The object of the present invention is to pro-

vide an electron emitting semiconductor device not associated with the drawbacks of the prior technology and capable of uniform electron emission over a wide area of arbitrary shape.

The foregoing object can be attained, according to the present invention, by an electron emitting semiconductor device comprising a P-semiconductive layer formed on a semiconductive substrate; a Shottky barrier electrode formed on said P-semiconductor layer; plurality P<sup>+</sup>-area units formed under said Shottky barrier electrode; and an N<sup>+</sup>-area formed in the vicinity of said P<sup>+</sup>-area units.

## BRIEF DESCRIPTION OF THE DRAIWNGS

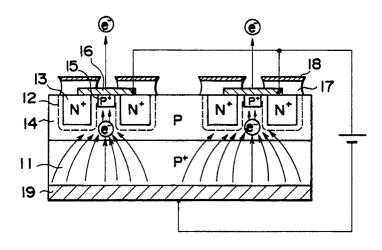

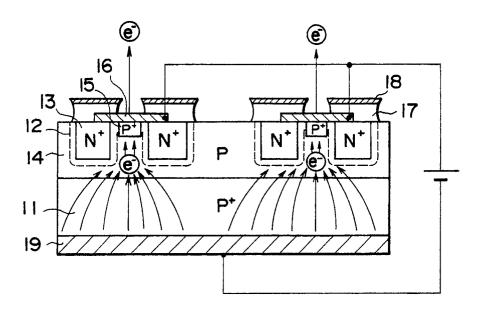

Fig. 1 is a view showing the working principle of the electron emitting semiconductor device of the present invention;

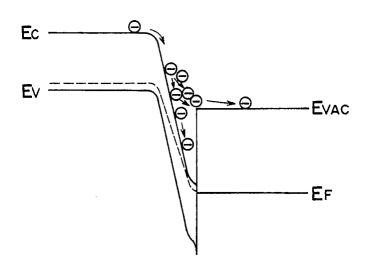

Fig. 2 is a chart showing the energy bands in the vicinity of the surface of the electron emitting semiconductor device of the present invention;

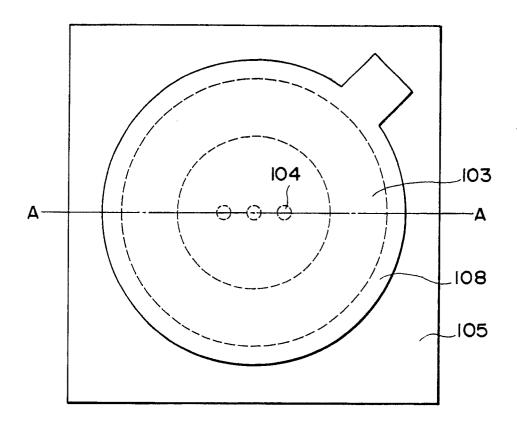

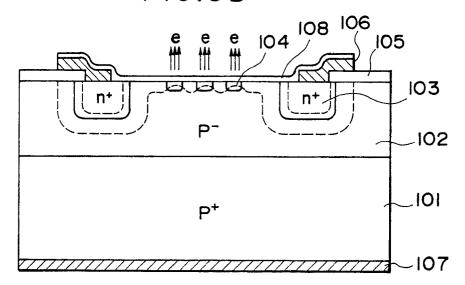

Figs. 3A and 3B are schematic views of an electron emitting GaAs semiconductor device constituting a first embodiment of the present invention:

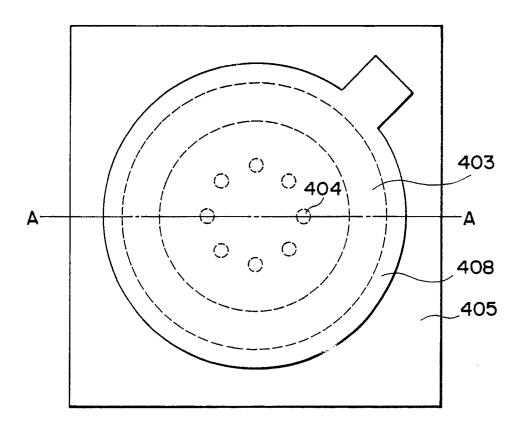

Figs. 4A and 4B are schematic views of an electron emitting GaAs semiconductor device constituting a second embodiment of the present invention:

Fig. 5 is a schematic plan view of an electron emitting semiconductor device constituting a third embodiment of the present invention;

Fig. 6 is a cross-sectional view along a line B - B in Fig. 5;

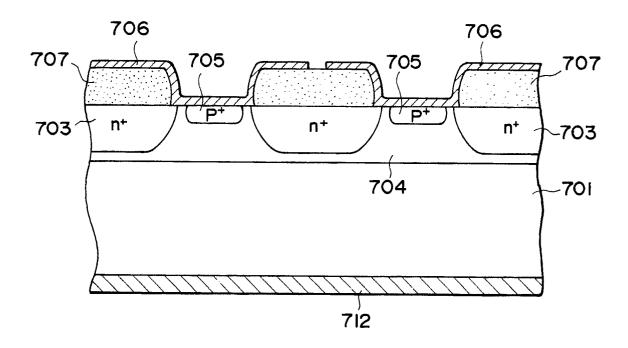

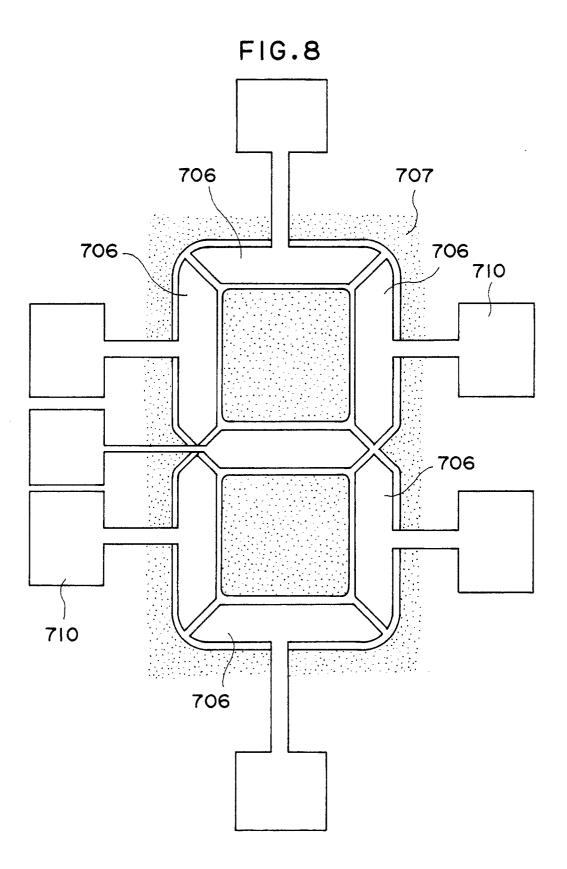

Fig. 7 is a schematic cross-sectional view of a part of an electron emitting semiconductor device constituting a fourth embodiment of the present invention; and

Fig. 8 is a schematic plan view thereof.

# DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

The electron emitting semiconductor device of the present invention, in which a Shottky electrode for a P-semiconductor layer is composed of an area doped with a material for reducing the work function of the surface of the electron emitting part (said material being hereinaffer called work function reducing material), can form the electron emitting part in the direction of cross section of the substrate, and can also have plural electron emitting parts of arbitrary shapes in a single device.

Also since the work function reducing material employed in the present invention is an element extremely stable in the air, the device of the present invention does not require an ultra high vacuum for stable operation, does not show strong dependence of service life and efficiency on the level of vacuum, and can even by exposed to the air. Conventional electron emitting semiconductor devices show a large energy loss in the N-semiconductor layer because of the use of PN junction, so that the material of an extremely low work function has to be used. In practice, therefore, cesium alone has been used for this purpose. On the other hand, the device of the present invention shows a smaller energy loss than in the conventional devices because of the use of a Shottky junction, so that the usable work function reducing materials include metals of groups IA, IIA and IIIA of the periodic table and of lanthanoid, and silicides, borides and carbides of such metals. More specific examples of said material include TiC, ZrC, HfC, LaB<sub>6</sub>, SmB<sub>6</sub>, GdB<sub>6</sub>, WSi<sub>2</sub>, TiSi<sub>2</sub>, ZrSi<sub>2</sub> and GdSi2.

Besides, different from the conventional electron emitting semiconductor devices, the electrons which have acquired high energy by avananche amplification need not go through the N-semiconductor layer for reaching the surface of the electron emitting part. Consequently the device of the present invention is not associated with the difficulty in manufacture such as the necessity of forming an extremely thin N-semiconductor layer, for example 200 Å or less, and can therefore be manufactured in stable manner.

In the following the present invention will be clarified in greater detail, with reference to Figs. 1 and 2.

Fig. 1 is a schematic view of an example of the electron emitting semiconductor device of the present invention, showing the working principle thereof. In Fig. 1, there are shown a semiconductive substrate 11; a depletion layer area 12; an n area 13; a p-semiconductor layer 14; a p area unit 15; a Shottky electrode 16; an n-ohmic electrode 18; and p-ohmic electrode.

The semiconductor material to be employed in the electron emitting device of the present invention can for example be Si, Ge, GaAs, GaP, AlAs, GaAsP, AlGaAs, SiC or BP, but any material that can form p-semiconductor can be used for this purpose, and particularly preferred is a material of indirect transition type with a large band gap.

Fig. 2 shows the energy bands in the vicinity of the surface of the electron emitting semiconductor device of the present invention.

In the following there will be explained the electron emitting process of the electron emitting semiconductor device of the present invention.

Under the application of an inverse bias voltage to a Shottky diode consisting of the p-semiconductor and the work function reducing material, the bottom Ec of the conduction band of the p-semiconductor assumes an energy level higher than the vacuum level Evac of the Shottky electrode. Electrons generated by the avalanche amplification acquire an energy higher than the lattice temperature by an electric field in the depletion layer generated at the interface of the semiconductor and the metal electrode, and are injected into the Shottky electrode consisting of the work function reducing material. Thus said electrons, of which energy is not lost for example by lattice scattering and is therefore higher than the work function of the surface of the Shottky electrode, are emitted into the outer vacuum space from the surface of said Shottky electrode constituting the electron emitting part.

In the electron emitting semiconductor device of the present invention, because of the presence of an N $^{\dagger}$  area in the vicinity of the interface of the work function reducing material in the P-semiconductor substrate, there is generated a depletion layer at the P-N $^{\dagger}$  interface. Consequently the electrons injected from the P $^{\dagger}$ -layer into the P-layer are restricted in their moving path by said depletion layer at the P-N $^{\dagger}$  interface and are concentrated in a p $^{\dagger}$ -area unit provided in the electron emitting part, whereby the current density can be easily increased.

Also in the device of the present invention, since the P<sup>+</sup>-area unit and the N<sup>+</sup>-area constituting the electron emitting part can be formed for example by ion implantation from the surface of the semiconductor substrate in the device manufacturing process, there can be formed plural electron emitting parts of arbitrary shapes, at arbitrary positions on a same plane of a substrate.

Also as desired semiconductive layers can be deposited in succession for example by MBE (molecular beam epitaxy) on a semiconductive substrate, the electron emitting part can be constructed with such successively deposited layer. It is therefore possible to form plural electron emitting parts in a direction perpendicular to the surface of the substrate.

Furthermore, according to the present invention, the plural P\*-area units may be arbitrarily positioned in the P-semiconductor layer, so that an electron beam of an arbitrary shape can be obtained.

#### [1st embodiment]

Fig. 3A is a plan view and Fig. 3B is a crosssectional view along a line A - A in Fig. 3A, both schematically showing an electron emitting GaAs

55

20

25

35

40

semiconductor device constituting an embodiment of the present invention, wherein shown are a  $P^{+}$ -Si substrate 101; a  $P^{-}$ -layer 102; an annular  $N^{+}$ -area 103; a point-shaped  $P^{+}$ -area unit 104; an insulating film 105; ohmic electrodes 106, 107; and a Shottky electrode 108.

In the following there will be explained the method of producing the electron emitting semi-conductor device shown in Figs. 3A and 3B.

- (1) On a  $P^{*}$ -Si substrate 101 doped with As with an impurity concentration of 1 x  $10^{19}$  cm<sup>-3</sup>, a  $P^{-}$ -layer 102 with an As concentration of 3 x  $10^{18}$  was formed by CVD (chemical vapor deposition) or LPE (liquid phase epitaxy).

- (2) Then apertures for the areas 103, 104 were formed by an ordinary photolithographic process, and ion implantations were conducted with  $B^{+}$  ions for the annular  $N^{+}$ -area 103 to obtain an impurity concentration of 1 x  $10^{20}$  cm<sup>-3</sup>, and with As<sup>+</sup> ions for the point-shaped  $P^{+}$ -area units 104 to obtain an impurity concentration of 1 x  $10^{20}$  cm<sup>-3</sup>, and activation was conducted by annealing.

- (3) Then a SiO<sub>2</sub> insulating film 105 was formed by vacuum evaporation, and an aperture was formed therein by a photolithographic process.

- (4) Aluminum was vacuum evaporated on the annular  $N^+$ -area 103 and on the rear surface of the substrate to form ohmic electrodes 106, 107. (5) Then, as the material constituting the Shottky electrode 108, a work function reducing material Ga ( $\phi_{wk} = 3.1$  eV) was deposited by vacuum evaporation in a thickness of 100 Å. Then, a heat treatment for 10 minutes at 350 °C was conducted to form GaSi<sub>2</sub>, forming a satisfacotry Shottky junctions with the point-shaped  $P^+$ -area units 104.

In the electron emitting semiconductor device prepared as explained above, the application of an inverse bias voltage to the Shottky barrier diode 108 induced avalanche amplification at the interface between the Shottky electrode 108 and the point-shaped P<sup>+</sup>-area 104, whereby electrons of high energy were emitted from the GaSi surface.

As explained in the foregoing, in the present embodiment, the presence of the  $P^+$ -area unit for concentrating the electric field and limiting the electron emitting part limits the point of electron emission, so that the distribution of electron emission in a device can be arbitrarily designed by the arrangement of said point-shaped P-area and the size of the  $P^+$ -area unit.

Besides the electron emitting device of the present invention easily allows minituarization or integration of multiple devices because the conventional semiconductor process can be utilized for the preparation.

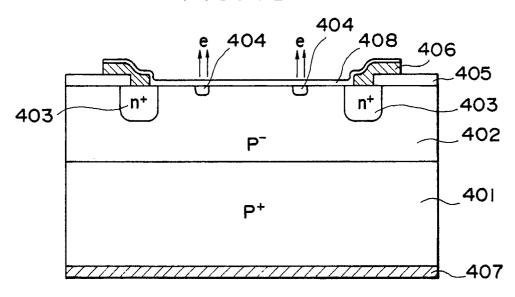

[2nd embodiment]

Fig. 4A is a plan view, and Fig. 4B is a crosssectional view along a line A - A in Fig. 4A, both showing an electron emitting GaAs semiconductor device constituting a second embodiment of the present invention, wherein shown are a P<sup>+</sup>-Si substrate 401; a P<sup>-</sup>-layer 402; an annular N<sup>+</sup>-area 403; a point-shaped P<sup>+</sup>-area unit 404; an insulating film 405; ohmic electrodes 406, 407; and a Shottky electrode 408.

In the following there will be explained the method for producing the electron-emitting semi-conductor device shown in Fig. 4.

- (1) On a  $P^+$ -GaAs substrate 401 with an impurity concentration of 5 x  $10^{18}$  cm<sup>-3</sup>, there was epitaxially grown a  $P^-$ -GaAs layer 402 with an impurity concentration of 1 x  $10^{18}$  cm<sup>-3</sup> by MEB (molecular beam epitaxy) or MO-CVD (metalorganic chemical vapor deposition), employing Be as the P-impurity.

- (2) Maskless ion implantation was conducted with FIB (focused ion beam), employing  $\mathrm{Si2}^+$  for the annular N $^+$ -area 403 with an accelerating voltage of 160 keV and Be $^+$  for the point-shaped P $^+$ -area unit 404 with an accelerating voltage of 40 keV.

- (3) Subsequently  ${\rm SiO_2}$  was deposited by vacuum evaporation on both faces of the substrate 401, and the implanted impurities were activated by annealing for 3 minutes at 850  $^{\circ}$  C.

- (4) Then  $SiO_2$  was entirely removed from the rear face of the substrate, and the interior alone of the annular  $N^+$ -area on the top face was etched to obtain the insulating film 405.

- (5) Then Au-Zn alloy and Au-Ge alloy were deposited by vacuum evaporation respectively on the rear face of the P<sup>+</sup>-substrate 401 and on the n<sup>+</sup>-area of P<sup>-</sup>-GaAs layer 402. After the Au-Ge alloy film on the top face was patterned, heat treatment was applied for 3 minutes at 400 °C to obtain the ohmic electrodes 406, 407.

- (6) Finally LaB<sub>6</sub>. which is a work function reducing material ( $\phi_{WT}$  = 2.6 eV) capable of forming satisfactory Shottky junction to the positive holes of GaAs, was deposited by electron beam evaporation, thereby forming the shottky electrode.

The electron emitting semiconductor device prepared in this manner was placed in a vacuum chamber maintained at  $2 \times 10^{-7}$  Torr, and was given an inverse bias voltage of 7 V, whereupon electron emission of about 1 nA was observed.

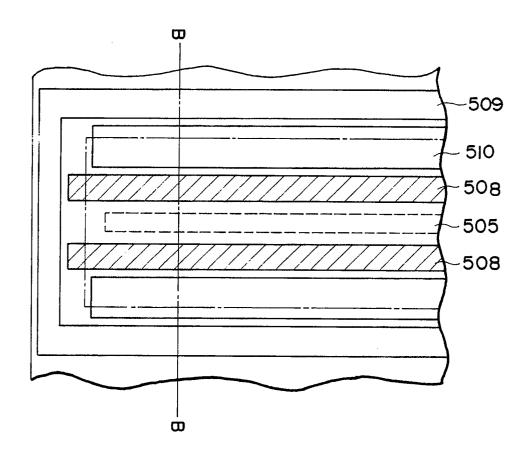

[ 3rd embodiment ]

Fig. 5 is a plan view, and Fig. 6 is a cross-

55

10

15

20

25

35

40

sectional view along a line B - B in Fig. 5, both showing an electron emitting semiconductor device constituiting a third embodiment of the present invention.

In the following there will be explained the method for producing the device shown in Figs. 5 and 6.

- (1) On an insulating Si substrate 511, there were grown a P<sup>+</sup>-layer 513 of an impurity concentration of 1 x 10<sup>19</sup> cm<sup>-3</sup> and a P-semiconductor layer 504 of an impurity concentration of 3 x 10<sup>16</sup> cm<sup>-3</sup> by CVD (chemical vapor deposition) or LPD (liquid phase epitaxy).

- (2) Then apertures for the areas 503, 505, 512 were formed by an ordinary photolithographic process, and As $^{+}$  ions were implanted with an impurity concentration of 1 x  $10^{20}$  cm $^{-3}$  in the P $^{+}$ -area units 505, 512 and were activated by annealing.

- (3) Subsequently a work function reducing material constituting the Shottky electrode 506, for example Gd ( $\phi_{WK}=3.1$  eV), was deposited in a thickness of 100 Å by vacuum evaporation, and a satisfactory Shottky junction was formed by heat treatment for 10 minutes at 350  $^{\circ}$  C.

- (4) Then, the electrode 508 and ohmic electrode 509 were formed by aluminum evaporation on an insulating layer on said Shottky electrode 506.

In the electron emitting semiconductor device prepared as explained above, the application of an inverse bias voltage to the Shottky diode induced avalanche amplification at the interface between the Shottky electrode 506 and the P<sup>+</sup>-area unit 505, whereby electrons of high energy were emitted from the GdSi<sub>2</sub> surface.

As explained in the foregoing, the present embodiment has a line-shaped  $P^*$ -area unit 505 for concentrating the electric field and limiting the electron emitting part as shown in Fig. 5, so that the electron emission can be obtained continuously over a wide area. Consequently it can be utilized as the electron source for flat panel displays or other display devices in which a linear cathode has been employed.

Also the electron emitting semiconductor device of the present embodiment can be made as a large device or in a large area, because it is a silicon device utilizing the conventional semiconductor process.

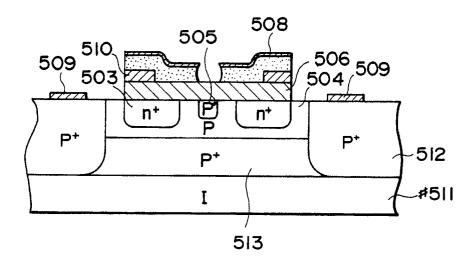

#### [4th embodiment]

In the following there will be explained a fourth embodiment of the present invention, in which the electron emitting semiconductor device of the present invention is applied in a 7-segment image display device, with reference to Figs. 7 and 8.

Fig. 7 is a schematic cross-sectional view of a part of the electron emitting semiconductor device of the present embodiment, and Fig. 8 is a schematic plan view thereof.

In the following there will be explained the method for producing said device shown in Figs.7 and 8

- (1) On a  $P^{+}$ -GaAs substrate 701 of an impurity concentration of 5 x  $10^{18}$  cm<sup>-3</sup>, there was epitaxially grown a P-GaAs layer 704 of an impurity concentration of 1 x  $10^{16}$  cm<sup>-3</sup> by MBE (molecular beam epitaxy) utilizing Be as the P-impurity.

- (2) Then an  $N^{+}$ -layer 703 was formed by maskless ion implantation with an FIB (focused ion beam) of  $Si^{+}$  into the P-GaAs layer 704 with an accelerating voltage of 80 keV and a dose of about  $5 \times 10^{13}$  cm<sup>-2</sup>.

- (3) Then  $P^{+}$ -area units 705 constituting electron emitting areas were formed by ion implantation with an FIB of an accelerating voltage of 50 kV and a dose of about 1 x  $10^{13}$  cm<sup>-3</sup>.

- Said P<sup>+</sup>-area units 705 constitute seven electron emitting areas for displaying the 7-segment image.

- (4) Then a  $SiO_2$  layer was formed by sputter evaporation on the substrate 701 having the N<sup>+</sup>-area 703 and the P<sup>+</sup>-area units 705 thereon, and heat treatment for 3 minutes at 800  $^{\circ}$ C was applied in mixed gas of arsine, N<sub>2</sub> and H<sub>2</sub> to activate the implanted impurities.

- (5) Then  $SiO_2$  on the P $^*$ -area units 705 was removed to expose said area units, and  $LaB_6$  ( $\phi_{WT}$  = 2.6 eV) which is a work function reducing material capable of forming a satisfactory Shottky junction to the positive holes of GaAs was deposited in a thickness of about 200 Å by electron beam evaporation, thereby forming a Shottky electrode independently for each segment

- (6) Finally an ohmic electrode was formed on the rear face of the P<sup>+</sup>-substrate with Au-Zn alloy whereby the electron emitting device was completed.

The electron emitting semiconductor device thus completed was placed in a vacuum container maintained at 1  $\times$  10<sup>-6</sup> Torr, and a fluorescent plate was placed at a distance of 2 mm. By the electron emission from the device, there were observed luminous points corresponding to seven segments of said device. The electron emission was obtained only from segments in which the Shottky electrode was given a positive voltage, so that the display of numerals was possible by the combinations of seven segments.

As explained in the foregoing, the electron emitting device of the present invention is capable

of arbitrarily limiting the electron emitting part, and simultaneously forming plural electron emitting parts on a same substrate.

Furthermore, the electron emitting device of the present invention is capable of electron emission in a direction perpendicualr to the cross section of the substrate, and is also capable of electron emissions in plural independent directions by forming the electron emitting cross sections in plural directions.

Also said device can be easily applied for example to a display, since the shape of the electron emitting part can be controlled by the  $P^+$ -layer embedded in the P-layer.

An electron emitting semiconductor device comprises a P-semiconductor layer formed on a semiconductive substrate; a Shottky barrier electrode formed on the P-semiconductor layer; plural P<sup>+</sup>-area units positioned under and facing to the Shottky barrier electrode; and an N<sup>+</sup>-area in the vicinity of said P<sup>+</sup>-area units.

#### Claims

- 1. An electron emitting semiconductor device comprising a P-semiconductor layer formed on a semiconductive substrate; a Shottky barrier electrode formed on said P-semiconductor layer; plural  $P^*$ -area units positioned under and facing to said Shottky barrier electrode; and an  $N^*$ -area in the vicinity of said  $P^*$ -area units.

- 2. An electron emitting semiconductor device according to claim 1, wherein said Shottky barrier electrode is composed of at least a material selected from Gd, LaB $_6$ , TiC, ZrC, HfC, SmB $_6$ , GdB $_6$ , WSi $_2$ , TiSi $_2$ , ZrSi $_2$  and GdSi $_2$ .

- 3. An electron emitting semiconductor device according to claim 1, wherein said P-semiconductor is composed of at least a material selected from Si, Ge, GaAs, GaP, AlAs, GaAsP, AlGaAs, SiC and BP.

- 4. An electron emitting semiconductor device according to claim 1, wherein said Shottky barrier electrode has a thickness not exceeding 20 nm.

- 5. An electron emitting semiconductor device according to claim 4, wherein said Shottky barrier electrode has a thickness in a range from 5 nm to 15 nm.

- 6. An electron emitting semiconductor device according to claim 1, wherein said  $P^+$ -area unit has an area not exceeding 8000  $\mu$ m<sup>2</sup>.

- 7. An electron emitting semiconductor device according to claim 6, wherein said  $P^+$ -area unit has an area in a range from 1000 to 6000  $\mu$ m<sup>2</sup>.

- 8. An electron emitting semiconductor device according to claim 1, wherein said  $N^{+}$ -area is formed in an annular form arrounding said  $P^{+}$ -area unit.

- 9. An electron emitting semiconductor device hav-

ing a P-semiconductor layer formed on a semiconductor substrate, a Shottky barrier electrode on said P-semiconductor, and a P<sup>+</sup>-area unit under said Shottky barrier electrode, wherein said P<sup>+</sup>-area unit is stripe shaped.

10

- 10. An electron emitting semiconductor device according to claim 9, comprising plural  $N^{\dagger}$ -areas formed across said  $P^{\dagger}$ -area unit so as not to be in contact with said  $P^{\dagger}$ -area unit.

- 11. An electron emitting semiconductor device according to claim 9, wherein said Shottky barrier electrode is composed of at least a material selected from Gd, LaB<sub>6</sub>, TiC, ZrC, HfC, SmB<sub>6</sub>, GdB<sub>6</sub>, WSi<sub>2</sub>, TiSi<sub>2</sub>, ZrSi<sub>2</sub> and GdSi<sub>2</sub>.

- 12. An electron emitting semiconductor device according to claim 9, wherein said P-semiconductor is composed of at least a material selected from Si, Ge, GaAs, GaP, AlAs, GaAsP, AlGaAs, SiC and BP. 13. An electron emitting semiconductor device according to claim 9, wherein said Shottky barrier electrode has a thickness not exceeding 20 nm.

- 14. An electron emitting semiconductor device according to claim 13, wherein said Shottky barrier electrode has a thickness within a range from 5 nm to 15 nm.

- 15. An electron emitting semiconductor device according to claim 9, wherein said  $P^+$ -area unit has an area not exceeding 8000  $\mu m^2$ .

- 16. An electron emitting semiconductor device according to claim 15, wherein said  $P^{\dagger}$ -area unit has an area within a range from 1000 to 6000  $\mu$ m<sup>2</sup>.

55

35

FIG.1

FIG.2

FIG.3A

FIG.3B

FIG.4A

FIG.4B

FIG.5

FIG.6

FIG.7