(1) Publication number:

0 431 417 A3

## **EUROPEAN PATENT APPLICATION** (12)

(21) Application number: 90122384.2

(51) Int. Cl.<sup>5</sup>: **G06F** 7/52

2 Date of filing: 23.11.90

Priority: 04.12.89 US 449366

(43) Date of publication of application: 12.06.91 Bulletin 91/24

Designated Contracting States: DE FR GB IT NL

Bate of deferred publication of the search report: 04.11.92 Bulletin 92/45

71 Applicant: NATIONAL SEMICONDUCTOR **CORPORATION** 2900 Semiconductor Drive P.O. Box 58090 Santa Clara California 95051-8090(US)

(72) Inventor: Avnon, Dror

P.O. Box 3007 Herzlia B 46104(IL) Inventor: Greenfeld Zvi P.O. Box 3007 Herzlia B 46104(IL) Inventor: Yuval, Gideon 613 151st Pace N.E. Bellevue, WA 87007(IL) Inventor: Baydach, Yair P.O. Box 3007

Herzlia B 46104(IL)

(4) Representative: Sparing Röhl Henseler Patentanwälte European Patent Attornevs Rethelstrasse 123 W-4000 Düsseldorf 1(DE)

Method and apparatus for SRT divison using gray coded quotient bit signals.

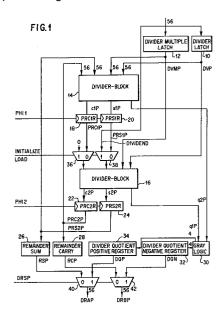

(57) A method and apparatus for performing SRT division, in which Gray coded quotient bit signals are generated during each iteration from a divisor signal having Gray coded bits, and a dividend signal. Preferably, only the two most significant bits of the divisor signal are encoded into Gray code at the start of the division process, and the Gray coded quotient bit signals are decoded after each iteration, or after the final iteration, for use in generating the final quotient. In a preferred embodiment, the invention is a circuit capable of performing both singleprecision and double-precision operations, and includes a pair of alternately operating divider block circuits each for generating a pair of quotient bits during each iteration cycle. The quotient bits emerging from each divider block circuit are decoded, and then shifted into one of two divider result registers depending upon their sign until 56 quotient bits (for double-precision operation) or 28 quotient bits (for single-precision operation) are accumulated in the divider result registers. When sufficient quotient bits have been accumulated, the invention asserts the contents of the divider result registers, a remainder

sum register, and a remainder carry register, as output signals which may be combined to generate a final quotient signal.

## **EUROPEAN SEARCH REPORT**

EP 90 12 2384

| Category                  | Citation of document with indic<br>of relevant passa                                                                                                                             | cation, where appropriate,<br>ges                                      | Relevant<br>to claim                                               | CLASSIFICATION OF THE APPLICATION (Int. Cl. 5) |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|--------------------------------------------------------------------|------------------------------------------------|

| A                         | 17th Annual ACM Comput<br>Conference, February<br>"Binary Division and<br>using Gray Code"<br>* the whole document                                                               | 1989, p441; YUEN:<br>Square-Rooting                                    | 1                                                                  | G 06 F 7/52                                    |

| A                         | IRE TRANSACTIONS ON E COMPUTERS, vol. EC-8, New York, US, pages 4 "Arithmetic Operation Computers Using a Mod Binary Code"  * abstract; pages 454 "Multiplication and Code"      | LECTRONIC December 1959, 49-458; LUCAL: s for Digital lified Reflected | 1                                                                  |                                                |

| A                         | Proceedings, 7th Symp<br>Arithmetic, June 1985<br>64-71; TAYLOR: "Radix<br>With Overlapped Quoti<br>Stages"                                                                      | 5, Illinois, pp.<br>2 16 SRT Dividers<br>ent Selection                 | 1                                                                  |                                                |

|                           | * pages 65-66, paragr                                                                                                                                                            | aph 4 *                                                                |                                                                    | TECHNICAL FIELDS<br>SEARCHED (Int. Cl.5)       |

| A                         | PATENT ABSTRACTS OF J<br>238 (P-231), 26 July<br>125 188 (CANON)<br>* abstract *                                                                                                 | JAPAN, vol. 7, no.<br>1983; & JP-A-58                                  | 1                                                                  | G 06 F                                         |

| A                         | IEEE INT. SYMP. ON CO<br>ARCHITECTURE AND DIGI<br>PROCESSING, 1989, pag<br>YUEN: "Binary division<br>square-rooting using<br>* pages 217,218 *                                   | TAL SIGNAL<br>ges 217-220; C.K.<br>on and                              | 1                                                                  |                                                |

|                           | The present search report has been                                                                                                                                               | n drawn up for all claims                                              |                                                                    |                                                |

|                           | Place of search                                                                                                                                                                  | Date of completion of the search                                       |                                                                    | Examiner                                       |

| THI                       | E HAGUE                                                                                                                                                                          | 12 <b>-</b> 08-1992                                                    | CO                                                                 | HEN B.                                         |

| X : pai<br>Y : pai<br>doc | CATEGORY OF CITED DOCUMENT rticularly relevant if taken alone rticularly relevant if combined with anoth cument of the same category chnological background n-written disclosure | E : earlier patent<br>after the filing                                 | document, but po<br>date<br>d in the applicat<br>d for other reaso | ublished on, or<br>ion<br>ns                   |