(11) Numéro de publication: 0 437 127 A1

(12)

## **DEMANDE DE BREVET EUROPEEN**

(21) Numéro de dépôt : 90403495.6

(51) Int. Cl.<sup>5</sup>: **G06F 11/10**, G06F 7/00

(22) Date de dépôt : 07.12.90

(30) Priorité: 07.12.89 FR 8916174

43 Date de publication de la demande : 17.07.91 Bulletin 91/29

84 Etats contractants désignés : DE FR GB IT NL

71 Demandeur : BULL S.A. 121, Avenue de Malakoff F-75116 Paris (FR) (72) Inventeur: Greiner, Alain 121 avenue de Malakoff F-75764 Paris Cédex 16 (FR)

Mandataire: Fournier, Michel Robert Marie et al

Bull S.A., 121, avenue de Malakoff, PC 8M006

F-75116 Paris (FR)

54) Circuit décaleur avec générateur de bits de parité.

57 L'invention concerne un circuit, dit circuit décaleur, utilisable notamment comme opérateur dans des unités d'arithmétique et de logique d'ordinateurs.

Selon l'invention, le circuit comporte un générateur d'un mot de parité (116) composé des bits de parité de tous les groupes de n bits (par exemple des quartets) qu'il est possible d'extraire des mots d'entrée A et B et une matrice de parité (115) associée à la matrice de décalage (113) pour produire sur des lignes de sortie de parité Q les bits de parité des groupes de n bits consécutifs qui constituent le mot de sortie S.

## CIRCUIT DECALEUR AVEC GENERATEUR DE BITS DE PARITE

5

10

15

20

25

30

35

40

45

L'invention concerne un opérateur appelé circuit décaleur (en anglais : "barrel shifter") utilisable pour effectuer des décalages dans des unités d'arithmétique et de logique d'ordinateurs.

Plus particulièrement, l'invention concerne des circuits décaleurs du type comportant des moyens pour fournir, en fonction de signaux de sélection issus d'un circuit de décodage, un mot de sortie composé de M bits consécutifs extraits d'un mot de base de N1 bits formé par exemple à partir de deux mots d'entrée de N bits chacuns.

Les circuits décaleurs sont couramment utilisés pour effectuer des décalages à droite, à gauche ou circulaires portant sur des mots de N bits selon le mode de chargement. Les décalages à droite sont réalisés en plaçant le mot d'entrée de gauche à zéro, les décalages à gauche en plaçant le mot d'entrée de droite à zéro et les décalages circulaires avec les deux mots d'entrée identiques au mot à décaler.

D'une façon générale, les constructeurs d'ordinateurs cherchent à assurer l'intégrité de leurs systèmes en détectant et en éliminant les signaux binaires et/ou les informations de validité douteuse due à des erreurs logiques ou à un mauvais fonctionnement physique du système.

A cet effet, l'utilisation de bits de parité associés aux données est un moyen commode de détection d'erreur au niveau du traitement de celles-ci, que ce soit au cours d'opérations logiques ou de simples déplacements de données. Pour ce faire, chaque mot de donnée est généralement subdivisé en plusieurs champs ou groupes de bits et on utilise des circuits logiques "OU-exclusif" permettant de calculer le bit de parité associé à chaque groupe. Toutefois, cette opération demande un certain délai pour générer la parité à contrôler, en particulier lorsque la largeur du groupe nécessite plusieurs étages de portes "OU-exclusif" montées en cascade.

En particulier, lorsque des données sont traitées par un opérateur, tel qu'un circuit décaleur, il peut être intéressant de calculer les bits de parité associés à chaque résultat issu de l'opérateur. Ce calcul pourrait être effectué selon la méthode habituelle à partir du résultat lui-même avec toutefois un retard quant au moment où le résultat est véritablement disponible pour la suite du traitement.

L'invention a pour but d'améliorer l'intégrité d'un système utilisant un circuit décaleur du type ci-dessus par la génération de bits de parité sans nuire aux performances de ce circuit. Pour ce faire, selon l'invention, le circuit décaleur comporte des moyens pour former un mot de parité composé des bits de parité de tous les groupes de n bits consécutifs qu'il est possible d'extraire du mot de base et des moyens de sélection commandés par lesdits signaux de sélection pour

produire les bits de parité des groupes de n bits consécutifs qui constituent le mot de sortie (n étant un diviseur de M).

Avantageusement, lesdits moyens de formation du mot de parité sont disposés en parallèle avec ledit circuit de décodage de sorte que le mot de parité et les signaux de sélection soient produits simultanément.

Ainsi donc le temps machine nécessaire au décodage de la valeur de décalage est utilisé pour pré-calculer les valeurs des parités de tous les groupes de bits susceptibles d'être extraits du mot de base pour les rendre prêtes à être fournies avec le mot de sortie.

Selon un premier mode de réalisation de l'invention, le circuit décaleur comporte une matrice de décalage à N1 lignes d'entrée de données et à M lignes de sortie, un circuit de décodage susceptible d'activer en fonction d'un signal de commande représentatif de la valeur de décalage à effectuer, comprise entre 0 et N1 - M, une ligne de sélection correspondante pour fournir sur les lignes de sortie le mot de sortie de données et en ce que ledit circuit décaleur comporte une pluralité de circuits de génération de parité associés aux groupes de n bits qu'il est possible d'extraire des lignes d'entrée (pour former un mot de parité de longueur N1 - n + 1 bits) et un circuit de sélection des bits de parité commandé par le circuit de décodage pour fournir sur des lignes de sortie de parité les parités des groupes de n bits du mot de sortie.

Cet agencement permet d'utiliser un circuit de décodage commun pour la matrice de décalage et les moyens de sélection des bits de parité.

Avantageusement, le circuit de sélection des bits de parité est constitué par une matrice de sélection à N1-n+1 lignes d'entrée de parité et à k lignes de sorties de parité (où k = M/n) commandée à partir du circuit de décodage par les lignes de sélection en fonction de ladite valeur de décalage à effectuer.

Selon un agencement particulier du circuit décaleur selon l'invention, la matrice de sélection de parité est imbriquée dans ladite matrice de décalage, avec des lignes d'entrée de parité (pi) parallèles aux lignes d'entrée de données (di) selon un arrangement de une ligne de parité (pi) associée à une (di + 2) des n lignes d'entrée de données de chaque groupe de n bits consécutifs qu'il est possible d'extraire du mot de base (par exemple pour n = 4, di, di + 1, di + 2 et di + 3), des lignes de sortie de parité (qi') parallèles aux lignes de sortie de données (si) selon un arrangement de une ligne de sortie de parité (qi') associée à une (s(ni' + 2)) des lignes de sortie formant un groupe de n bits consécutifs appartenant au mot de sortie (par exemple pour n = 4, s4i', s4i' + 1, s4i' + 2 et s4i' + 3), chaque ligne de sélection (lj) commandant l'état d'une ligne de sortie (si) à partir de l'état de la ligne d'entrée

10

15

25

30

40

45

de données d(i + j) et l'état d'une ligne de sortie q(i') à partir de l'état de la ligne d'entrée de parité p(ni' + j).

Cet agencement particulier présente un gain en surface très sensible par rapport à l'utilisation de deux matrices distinctes. A titre d'exemple, lorsque les matrices imbriquées incorporent des transistors de commutation dans une puce réalisée en technologie CMOS préchargé, l'augmentation de surface de la matrice par rapport à celle de la matrice de décalage à commutation d'un circuit décaleur simple sans génération de bits de parité est de l'ordre de 15%.

D'autres caractéristiques et avantages de la présente invention, notamment des détails de réalisation en technologie CMOS, apparaîtront plus clairement à la lecture de la description faite ci-après en référence aux dessins ci-ioints dans lesquels :

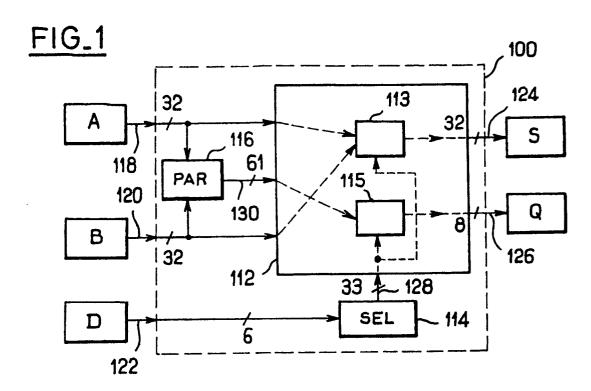

- la figure 1 est une représentation schématique d'un circuit décaleur selon l'invention,

- la figure 2 est une représentation schématique d'un circuit générateur de bits de parité utilisé dans le circuit illustré à la figure 1,

- la figure 3 est un schéma opérationnel illustrant la formation du mot de parité dans le cadre de la présente invention,

- la figure 4 est une représentation schématique des matrices de selection imbriquées utilisées dans le circuit décaleur selon l'invention,

- et la figure 5 est une représentation schématique d'une cellule de commutation réalisée en technologie CMOS et utilisée dans les matrices de selection illustrées à la figure 4.

Selon le mode de réalisation de l'invention ici décrit à titre d'exemple non limitatif, le circuit décaleur 100 de la figure 1 se compose essentiellement d'une double matrice de sélection 112 (incorporant une matrice de sélection du mot décalé 113 et une matrice de sélection des parités 115), d'un circuit de décodage 114 et d'un circuit 116 générateur du mot de parité. Le circuit décaleur 100 comporte deux ensembles ou deux bus de N lignes d'entrée de données 118 et 120 (repérées de do à dN - 1) pour le bus 118 et de dN à d(2N - 1) pour le bus 120), des lignes de commande de décalage 122, un ensemble de M lignes 124 de sortie de données après décalage (repérées de sO à s(M - 1) et un ensemble de k lignes de sortie de parités (repérée de q0 à q(k - 1)).

Ainsi donc, le circuit décaleur présenté est conçu pour générer les parités de k groupes (ou multiplets) de dimension n bits qui constituent après décalage le mot de sortie de dimension M bits. En application courante, la dimension M du mot de sortie est égale à celle N de chacun des mots d'entrée soit M = N, la dimension du mot de base N1 étant alors égale à 2N. A titre d'exemple non limitatif, dans la variante ici décrite du mode de réalisation de l'invention et illustrée à la figure 1, les dimensions des mots d'entrée et de sortie sont de 32 bits (M = N = 32) et la dimension

n du multiplet est de 4 bits (n = 4), la sortie de parité ayant alors une dimension de 8 bits (k = 8). Toutefois l'exemple montré sur les figures 3 et 4 et donné à fin d'illustration a été choisi avec M = N = 8 bits et n = 4 bits (k = 2) pour ne pas surcharger les dessins.

Si l'on considère la figure 1, la concaténation des deux mots d'entrée de dimension N (32) donne la possibilité d'extraire par décalage un nombre L = N1 - M + 1 (33) de groupes distincts de M (32) bits consécutifs et susceptibles de former le mot de sortie, y compris le décalage nul. A cet effet, la matrice de sélection de décalage 113 est contrôlée par L lignes de sélection 128 (repérées de lo à l(N1 - M)) issues des bornes de sortie du circuit de décodage 114. Le circuit de décodage SEL 114 peut être d'un type classique, par exemple à valeur d'entrée codée binaire. Dans ce cas on a un nombre C de lignes de commande de décalage 122 tel que 2<sup>C</sup>. ≥ N1 - M + 1, ces lignes étant associées à un registre D d'entrée de la valeur de décalage.

Comme représentées sur la figure 1, les lignes d'entrée 118 et 120 sont associées à deux registres de données A et B tandis que les lignes de sorties 124 et 126 sont associées à deux registres, l'un S de sortie de données, l'autre Q de sortie de parité.

Les lignes de données 118 et 120 sont également reliées aux bornes d'entrée du circuit PAR 116 de génération du mot de parité. Le circuit PAR est constitué d'un ensemble de circuits élémentaires GP générateurs chacuns d'un bit de parité.

Chaque circuit élémentaire GP est du type à portes "OU-exclusif" (repérées ⊕) à plusieurs entrées, ce qui peut être obtenu par un montage en cascade de plusieurs "OU-exclusif" à 2 entrées, comme montré à la figure 2 qui illustre le cas particulier d'un circuit à 4 entrées destiné à la génération d'un bit de parité par quartet. On rappelle que le bit de parité (repéré pi) prendra la valeur 1 si le nombre de bits de valeur 1 du multiplet considéré est impair et prendra la valeur 0 dans le cas contraire.

La génération du mot de parité dans le circuit 116 est effectuée de la façon suivante illustrée schématiquement à la figure 3. Après concaténation dans un registre approprié des mots d'entrée A et B (dans le même ordre que celui utilisé pour le décalage), on procède à la génération de chaque bit de parité pi de tous les multiplets de bits consécutifs (ici quartets) qu'il est possible d'extraire. Le nombre de multiplets est égal à 2N - N + 1 (pour N1 = 2N), soit à 61 dans l'exemple illustré à la figure 1 et à 13 dans l'exemple illustré aux figures 3 et 4. Cette génération des bits de parité est effectuée dans un registre P par les circuits GP (GPo à GP(2N - n)) en parallèle, de façon quasisimultanée avec les opérations de décodage de la commande de décalage envoyée sur la ligne 122. Les signaux de parité sont fournis à N1 - n + 1 lignes d'entrée 130 (repérée de po à p(2N - n)) de la matrice de sélection de parité 115 avant la validation par un

20

25

40

50

signal d'horloge CK du signal de sélection généré par le circuit de décodage 114.

La matrice de sélection double 112 représentée schématiquement à la figure 4 montre l'imbrication des deux matrices de décalage 113 et de parité 115. La matrice de décalage 113 présente ses lignes d'entrée (do à d7 et d8 à d15) pour les mots A et B, ses lignes de sortie S (so à s7) et ses lignes de sélection (10 à 18). La matrice de parité 115 présente ses lignes d'entrée (po à p12), ses lignes de sortie (q0 à q1) et ses lignes de sélection (10 à 18), ces dernières étant communes et de fait confondues avec celles de la matrice de décalage 113.

Du point de vue topologique, dans un mode de réalisation particulier en technologie CMOS, les lignes de selection L (orientées verticalement sur la figure 4) sont sur la couche métal 1, les lignes de sortie S et Q (orientées horizontalement sur la figure 4) sont sur la couche métal 2 et les lignes de données A, B et P sont agencées en escalier bi-couche pour permettre les croisements, selon une disposition générale de nappes parallèles obliques (couche métal 1 pour le cheminement vertical et couche métal 2 pour le cheminement horizontal au dessus des lignes de selection avec connexion métal inter-couche à chaque changement d'orientation). Par ailleurs, les lignes A et B sont contiguës pour assurer la concaténation des mots A et B, et les lignes P sont imbriquées dans les lignes A et B selon l'agencement représenté à la figure 4. De même, les lignes de sortie S et Q sont disposées en nappes parallèles imbriquées qui recouvrent d'une part les lignes d'entrée A, B et P et d'autre part les lignes de sélection L placées verticalement. Une ligne d'entrée, une ligne de sortie et une ligne de sélection se rejoignent par l'intermédiaire d'une cellule de commutation CC dont le schéma de principe donné à la figure 5 sera présenté ci-après.

Du point de vue fonctionnel, lorsqu'une cellule de commutation CC est validée par la ligne de sélection associée, elle reproduit sur la ligne de sortie associée la valeur logique de la ligne d'entrée associée (ligne oblique). Lorsqu'elle n'est pas validée, la cellule CC est maintenue à l'état de haute impédance.

L'agencement topologique particulier de la figure 4 (lignes de sortie S et de sélection L perpendiculaires, lignes d'entrée en escalier obliques avec de préférence un angle à 45°) présente l'avantage d'optimiser la surface occupée. Ainsi donc la matrice de décalage 113 présente M lignes et 2N - M + 1 colonnes (soit, sur la figure 4 une matrice 3 × 9) et la matrice de parité 115 présente k lignes et 2N + 1 colonnes (soit sur la figure 4 une matrice 2 × 9). Cette topologie est utilisée dans la réalisation pratique de la matrice de sélection double 112 sous forme de microcircuit LSI en technologie CMOS.

D'une façon plus précise, les lignes d'entrée de parité (pi) présentent un agencement en escalier

parallèle à celui des lignes d'entrée de données (di) selon un arrangement de une ligne de parité (pi) associée à une ligne (dans le cas particulier illustré à la figure 4, la ligne (di + 2) par exemple) des n = 4 lignes d'entrée de données de chaque groupe de n bits consécutifs qu'il est possible d'extraire du mot de base (di, di + 1, di + 2 et di + 3).

De même, les lignes de sortie de parité (qi') sont parallèles aux lignes de sortie (si) selon un arrangement de une ligne de sortie de parité (qi') associée à une ligne (dans le cas particulier illustré à la figure 4 où (pi) est associé avec (di + 2), la ligne (s(ni' + 2)) pour respecter la correspondance entre parité et groupe de bits consécutifs) des n = 4 lignes de sortie (sni', sni' + 1, sni' + 2, sni' + 3) formant un groupe de n bits consécutifs appartenant au mot de sortie. Ainsi les lignes de sortie de parité (qi') sont régulièrement espacées toutes les n lignes de sortie (si).

Enfin, chaque ligne de sélection (Ij) commande, par l'intermédiaire de la cellule de commutation CCij, l'état de la ligne de sortie (si) à partir de la ligne d'entrée de données d(i + j) et par l'intermédiaire de la cellule de commutation CC\*i'j, l'état de la ligne de sortie (qi') à partir de la ligne d'entrée de parité p(ni' + j).

La figure 5 représente une cellule de commutation CCij associée à la ligne d'entrée d(i + j), à la ligne de sortie (si) et à la ligne de sélection (lj). Cette réalisation utilise la technologie dite "CMOS préchargée" où chaque ligne horizontale (par rapport à la figure 5) de la matrice correspond à une ligne (s'i) qui est préchargée à une tension positive Vdd pendant la phase dite de précharge du signal d'horloge (signal CK = 0 pendant la phase de précharge). Pendant la phase dite d'évaluation du signal d'horloge CK (signal CK = 1 pendant la phase d'évaluation), cette ligne (s'i) prend un état logique complémentaire à la valeur de sortie (si). Pour ce faire, chaque ligne préchargée (s'i) est reliée à l'entrée 154 d'un inverseur 156, dont la sortie correspond à la ligne de sortie (si). Chaque cellule de commutation CC est principalement constituée de deux transistors NMOS 150 et 152 montés en série. Le drain du transistor 150 est connecté à la ligne préchargée (s'i) directement sur l'entrée 154 de l'inverseur 156, tandis que la source du transistor 152 est connectée à la masse (potentiel de niveau bas) du circuit. La grille 158 du transistor 150 est connectée à la ligne de sélection (lj), plus exactement à la sortie 160 d'une porte ET de validation 162 incorporée dans le circuit de décodage 114. La porte ET 162 reçoit en entrée le signal (l'j) correspondant généré dans le circuit de décodage 114 et le signal d'horloge CK (la validation étant effectuée pendant la phase d'évaluation où CK = 1). La grille 164 du transistor 152 est connectée à la ligne d'entrée de données d(i + j), (par exemple pour un décalage de 5 unités, soit j = 5, la valeur du bit 4 du mot de sortie, soit s4, sera égale à celle du bit de données d9).

20

30

40

45

50

Par ailleurs, un transistor PMOS de précharge 166 est connecté par sa source à une source de tension Vdd et par son drain à la ligne (s'i). Ce transistor PMOS 166 reçoit sur sa grille 168 le signal d'horloge CK.

Dans le cas où la cellule de commutation CC\* appartient à la matrice de parité 115, son schéma électrique de base reste inchangé. Toutefois, la ligne de sélection (lj) est associée à une ligne de sortie (qi'), au travers d'une ligne préchargée (q'i'), et à une ligne de données de parité p(ni' + j), (par exemple pour un décalage de 5 unités (j = 5), la valeur de la parité du quartet 1 (n = 4, i' = 1) du mot de sortie sera celle du bit de parité de la ligne p9).

Les cellules de commutation fonctionnent de la façon suivante : à chaque cycle de l'horloge (non représentée) du circuit décaleur, le signal CK prend successivement une valeur basse (CK = 0 pendant la phase de précharge) puis une valeur haute (CK = 1 pendant la phase d'évaluation). Pendant la phase dite de précharge à CK = 0, le transistor PMOS 152 est rendu passant et l'entrée de l'inverseur 156 est portée au potentiel Vdd. Par ailleurs, la sortie 160 de la porte ET 162 est portée à un niveau bas pendant toute cette phase de précharge. Il en résulte un blocage du transistor NMOS 150. Pendant la phase dite d'évaluation où CK = 1, le transistor PMOS 166 est à nouveau bloqué tandis que le signal CK = 1 est envoyé à l'entrée de toutes les portes ET contrôlant les lignes de sélection en sortie du circuit de décodage 114. Selon la valeur de décalage transmise par la ligne de commande 122, une seule ligne de pré-sélection, par exemple (l'j), sera activée et portée à une valeur haute (l'j = 1). Ainsi donc la sortie 160 de la porte ET correspondante 162 et toute la ligne de sélection correspondante (lj) associée à la colonne (j) des matrices de décalage et de parité commandant les grilles 158 des transistors NMOS 150 est portée à un potentiel haut, ce qui aura pour effet de rendre passant ces mêmes transistors 150 permettant ainsi la lecture de la valeur des signaux d(i + j) et p(ni' + j).

Dans le cas où d(i + j) = 0, la grille 164 du transistor 152 reste à un niveau de tension bas maintenant ce dernier en état bloqué. La ligne (s'i) reste à un niveau haut ce qui donne à la sortie de l'inverseur 156 un signal de sortie au niveau bas (si = 0). A l'inverse, dans le cas où d(i + j) = 1, la grille 164 est portée à un niveau haut ce qui rend passant le transistor 152. Le blocage du transistor 166 et la mise en état passant des deux transistors 150 et 152 fait chuter la tension de la ligne (s'i) qui passe au niveau bas. La sortie de l'inverseur 156 bascule alors au niveau haut (si = 1).

Ainsi donc, au cours de cette phase d'évaluation, toutes les lignes de sorties (si) et (qi') activées par la même ligne de sélection (lj) seront représentatives de valeurs binaires présentes sur les lignes de données et de parité associées. Il est à remarquer que le temps nécessaire au décodage de la valeur de décalage par

le circuit SEL 114 et le temps nécessaire à la génération du mot de parité par le circuit PAR 116 sont du même ordre ; ceci permet d'assurer le synchronisme au niveau de la disponibilité des mots de sortie et des parités des groupes de bits constitutifs de ces mots. En effet toutes les opérations de décalage et de génération des bits de parité des multiplets constitutifs du mot de sortie sont effectuées au cours d'un même cycle d'horloge.

Par ailleurs, l'imbrication des matrices de décalage et de parité permet un gain de place appréciable lors de l'intégration des composants dans une puce. En pratique, la limite physique est imposée par la distance minimale à respecter entre deux lignes parallèles d'interconnexion des transistors au niveau d'une des couches de métallisation de la puce (dans le cas particulier décrit au niveau de la couche métal 1, le positionnement des lignes de la couche métal 2 étant prédeterminé). Par rapport à une puce basée sur une seule matrice de décalage pour deux mots d'entrée de 32 bits et un mot de sortie de 32 bits également (2 × 32 entrées, 32 sorties et 33 sélections), une puce selon l'invention avec génération des bits de parité de chaque quartet du mot de sortie (comportant en plus 61 entrées de parité et 8 sorties de parité) présente une augmentation de la surface active de la matrice de l'ordre de 15%. Toutefois, sans sortir du cadre de l'invention, un autre mode de réalisation de celle-ci (non représenté) présente les deux matrices de commutation de décalage et de parité physiquement distinctes structurées chacune autour d'une puce (ou d'un micro-circuit) spécifique.

## 35 Revendications

- 1. Circuit décaleur du type comportant des moyens (113) pour fournir, en fonction de signaux de sélection issus d'un circuit de décodage (114), un mot de sortie composé de M bits consécutifs extraits d'un mot de base de N1 bits, formé par exemple à partir de deux mots d'entrée de N bits chacuns, caractérisé en ce qu'il comporte des moyens (116) pour former un mot de parité composé des bits de parité de tous les groupes de n bits consécutifs qu'il est possible d'extraire du mot de base et des moyens de sélection (115) commandés par lesdits signaux de sélection pour produire les bits de parité des groupes de n bits consécutifs qui constituent le mot de sortie (n étant un diviseur de M).

- Circuit décaleur selon la revendication 1, caractérisé en ce que lesdits moyens (116) de formation du mot de parité sont disposés en parallèle avec ledit circuit de décodage (114) de sorte que le mot de parité et les signaux de sélection soient produits simultanément.

10

15

20

30

40

45

50

- 3. Circuit décaleur selon l'une des revendications précédentes, caractérisé en ce qu'il comporte une matrice de décalage (113) à N1 lignes d'entrée de données (118, 120) et à M lignes de sortie (124), un circuit de décodage (114) susceptible d'activer en fonction d'un signal de commande représentatif de la valeur de décalage à effectuer, comprise entre 0 et N1 - M, une ligne de sélection (128) correspondante pour fournir sur les lignes de sortie le mot de sortie de données et en ce que ledit circuit décaleur comporte une pluralité (116) de circuits de génération de parité associés aux groupes de n bits qu'il est possible d'extraire des lignes d'entrée (118, 120) (pour former un mot de parité de longueur N1 - n + 1 bits) et un circuit de sélection (115) des bits de parité commandé par le circuit de décodage pour fournir sur des lignes de sortie de parité (126) les parités des groupes de n bits du mot de sortie.

- 4. Circuit décaleur selon la revendication 3, caractérisé en ce que le circuit de sélection (115) des bits de parité est constitué par une matrice de sélection à N1 n + 1 lignes d'entrée de parité (130) et à k lignes de sortie de parité (126) (où M = kn), et commandée à partir du circuit de décodage (114) par les lignes de sélection (lj) en fonction de ladite valeur de décalage à effectuer.

- 5. Circuit décaleur selon la revendication 4, caractérisé en ce que la matrice de sélection de parité (115) est imbriquée dans ladite matrice de décalage (113), avec des lignes d'entrée de parité (pi) parallèles aux lignes d'entrée de données (di) selon un arrangement de une ligne de parité (pi) associée à une (di + 2 par exemple) des n lignes d'entrée de données de chaque groupe de n bits consécutifs qu'il est possible d'extraire du mot de base (par exemple pour n = 4, di, di + 1, di + 2 et di + 3), des lignes de sorties de parité (qi') parallèles aux lignes de sortie de données (si) selon un arrangement de une ligne de sortie de parité (qi') associé à une (la ligne s(ni' + 2)) des lignes de sortie formant un groupe de n bits consécutifs appartenant au mot de sortie (par exemple pour n = 4, s4i', s4i' + 1, s4i' + 2 et s4i' + 3), chaque ligne de sélection (lj) commandant l'état d'une ligne de sortie (si) à partir de l'état de la ligne d'entrée de données d(i + j) et l'état d'une ligne de sortie (qi') à partir de l'état de la ligne d'entrée de parité p(ni' + j).

- 6. Circuit décaleur selon la revendication 5, caractérisé en ce que chaque ligne de sortie (si) ou (qi') regroupe un ensemble de L = N1 m + 1 cellules de commutation CC ou CC\* montées en série sur une ligne (s'i) ou (q'i') préchargée par un circuit

- de précharge (166), par exemple un montage série de deux transistors NMOS (150, 152) respectivement commandés par une ligne d'entrée associée d(i + j) ou p(ni' + j) et une ligne de sélection associée (Ij).

- 7. Circuit décaleur selon l'une des revendications précédentes, caractérisé en ce que le mot de base est formé de deux mots d'entrée de dimension N chacun, en ce que les mots d'entrée et de sortie sont de même dimension 32 et en ce que la dimension n des groupes du mot de sortie dont on génère les parités est égale à 4.