(11) Numéro de publication : 0 441 692 A1

(12)

## **DEMANDE DE BREVET EUROPEEN**

(21) Numéro de dépôt : 91400260.5

(51) Int. CI.5: G09G 3/20

2 Date de dépôt : 04.02.91

30 Priorité: 06.02.90 FR 9001346

(43) Date de publication de la demande : 14.08.91 Bulletin 91/33

84 Etats contractants désignés : CH DE GB IT LI NL

71 Demandeur : COMMISSARIAT A L'ENERGIE ATOMIQUE 31-33, rue de la Fédération F-75015 Paris (FR) 72) Inventeur: Leroux, Thierry 19 Mail Marcel Cachin F-38600 Fontaine (FR)

Mandataire: Mongrédien, André et al c/o BREVATOME 25, rue de Ponthieu F-75008 Paris (FR)

Procédé de commande d'un écran matriciel comportant deux parties indépendantes et dispositif pour sa mise en œuvre.

Pendant une première moitié du temps de trame, les lignes impaires successives de la première partie (10) de l'écran sont sélectionnées simultanément avec les lignes paires successives de la seconde partie (12) de l'écran. Pendant une seconde moitié du temps de trame, les lignes paires successives de la première partie (10) de l'écran sont sélectionnées simultanément avec les lignes impaires successives de la seconde partie (12).

Les informations à afficher lors d'une sélection sont contenues dans des registres (72, 78). Les informations à afficher lors de la sélection suivante sont enregistrées dans des registres-tampon (70, 76) et proviennent d'une source (22) pour les lignes impaires et d'une mémoire (62) pour les lignes paires. Cette mémoire (62) enregistre les informations à afficher sur les lignes paires au fur et à mesure de leur

délivrance par la source (22).

## PROCEDE DE COMMANDE D'UN ECRAN MATRICIEL COMPORTANT DEUX PARTIES INDEPENDANTES ET DISPOSITIF POUR SA MISE EN OEUVRE

5

10

15

20

25

30

35

40

La présente invention a pour objet un procédé de commande d'un écran matriciel comportant deux parties indépendantes et un dispositif pour sa mise en oeuvre. Elle s'applique notamment à tous les écrans matriciels commandés en deux parties indépendantes et en particulier aux écrans vidéo (par exemple, écrans à cristaux liquides ou écrans fluorescents à micropointes).

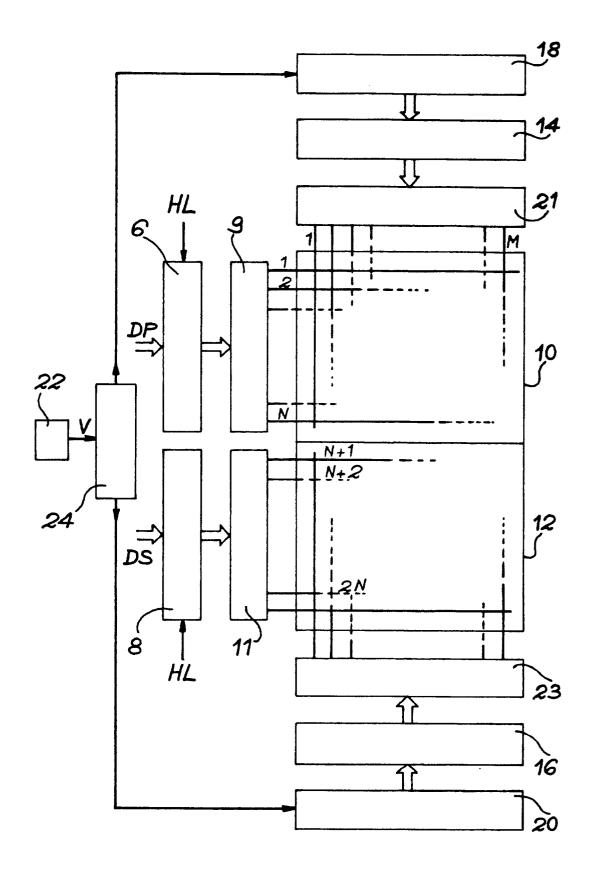

En référence à la figure 1, on décrit un écran matriciel de ce type et conforme à l'art antérieur. Un tel écran se compose d'une première partie 10 et d'une seconde partie 12 indépendantes mais jointives. Chaque partie 10, 12 de l'écran comporte N lignes de commande croisées à M colonnes d'adressage.

Pour l'affichage, les lignes de la première partie 10 sont successivement sélectionnées simultanément aux lignes de la seconde partie 12 : la ligne 1 de la première partie 10 avec la ligne N+1 de la seconde partie 12, la ligne 2 avec la ligne N+2 et ainsi de suite.

La sélection des lignes est effectuée par un premier registre 6 pour la première partie 10 et un second registre 8 pour la seconde partie 12. Des signaux DP pour le registre 6 et DS pour le second registre 8 fournissent les données concernant la ligne à sélectionner. Un signal HL de balayage des lignes commande la sélection des lignes.

Les registres 6 et 8 sont respectivement connectés à des moyens 9 et 11 amplificateurs et adaptateurs d'impédance permettant d'appliquer sur les lignes sélectionnées un potentiel déterminé.

A chaque sélection d'une ligne d'une partie simultanément à une ligne de l'autre partie, les informations à afficher sont contenues codées sous forme binaire dans un premier et un second registres 14, 16 qui permettent l'adressage des colonnes. Les premier et second registres 14, 16 sont connectés à des décodeurs 21, 23 qui permettent l'application sur les colonnes de l'écran des potentiels correspondant aux informations à afficher sur les pixels des lignes sélectionnées. Pendant la durée de cette sélection, les informations à afficher lors de la sélection suivante sont enregistrées dans un premier et un second registres-tampons 18, 20.

Les premier et second registres-tampons 18, 20 sont respectivement reliés aux premier et second registres 14, 16 pour le transfert des informations à afficher.

Pour un signal V du type vidéo fourni par une source 22, les informations à afficher sont délivrées en série, ligne après ligne. Une mémoire intermédiaire 24 est donc nécessaire : à un instant donné, les informations fournies ne concernent qu'une seule ligne alors que deux lignes sont affichées simultané-

ment (et aussi, il est nécessaire de remplir les deux registres-tampons 18, 20).

Cette mémoire 24 enregistre donc les informations à afficher au fur et à mesure de leur arrivée et délivre aux registres-tampon 18, 20 les informations nécessaires à l'affichage. Pour cela, elle doit être capable d'enregistrer les informations à afficher sur toutes les lignes de chaque partie 10, 12 de l'écran. Elle doit donc présenter une capacité minimale de 2N M K bits où : 2N est le nombre de lignes de l'écran, M est le nombre de colonnes, et K est le nombre de bits nécessaire au codage des informations à afficher sur un pixel.

L'importante capacité de la mémoire constitue un inconvénient grave de ce type d'écran connu. En effet, le coût du dispositif croît avec la taille de celle-ci.

La présente invention a pour but de réduire la taille de cette mémoire intermédiaire et ainsi de diminuer le coût de ce type d'écran.

Pour cela, les lignes successives de l'écran étant réparties en lignes paires et impaires successives, l'invention préconise la sélection simultanée d'une ligne d'un premier type de parité de la première partie et d'une ligne d'un second type de parité de la seconde partie. Puis, toutes les lignes du premier type de la première partie et toutes les lignes du second type de la seconde partie ayant été sélectionnées, on sélectionne simultanément une ligne du second type de parité de la première partie et une ligne du premier type de parité de la seconde partie de façon à sélectionner l'ensemble des lignes.

Comme on va le voir plus en détail dans la description qui suit, ce procédé de commande permet de réduire la capacité de la mémoire à N/2 M K bits, c'està-dire de la réduire d'un facteur 4 par rapport à celle des dispositifs de l'art antérieur.

De façon plus précise, l'invention concerne un procédé de commande d'un écran matriciel composé d'une première partie et d'une seconde partie comportant chacune un nombre N pair de lignes, les lignes de chacune des parties étant réparties en lignes d'un premier type de parité et lignes d'un second type de parité successives, caractérisé en ce qu'il consiste à :

pour chaque trame de l'écran,

A) sélectionner, les unes après les autres, les lignes du premier type de parité successives de la première partie ;

sélectionner, les unes après les autres, les lignes du second type de parité successives de la seconde partie,

chaque ligne du premier type de la première partie étant sélectionnée simultanément à une ligne du second type de la seconde partie à laquelle

15

20

25

35

elle est appariée,

B) puis, sélectionner, les unes après les autres, les lignes du second type de parité successives de la première partie,

sélectionner, les unes après les autres, les lignes du premier type de parité successives de la seconde partie,

chaque ligne du second type de la première partie étant sélectionnée simultanément à une ligne du premier type de la seconde partie à laquelle elle est appariée,

C) pour chaque ligne sélectionnée, afficher des informations devant l'être.

On entend par lignes d'un premier type de parité les lignes impaires et par lignes d'un second type de parité les lignes paires ou l'inverse. Dans le cas où le nombre total de lignes de l'écran est impair, pour avoir deux parties comportant un nombre N identique de lignes, on utilise pour une des parties une ligne fictive qui n'est pas affichée mais qui est prise en compte par l'électronique de l'écran au niveau temporel. De même, lorsque la moitié du nombre total de lignes est impaire, on ajoute pour avoir N pair une ligne fictive à chaque partie. On peut donc avoir jusqu'à trois lignes fictives pour un écran.

Selon un mode préféré de réalisation du procédé, lesdites informations à afficher étant délivrées par une source à un rythme régulier et dans un ordre relatif aux lignes successives de l'écran,

D) au fur et à mesure de leur délivrance, on enregistre dans une mémoire les informations à afficher sur les lignes d'un des types de parité de l'écran.

E) parallèlement à chaque sélection d'une ligne de la première partie appariée à une ligne de la seconde partie, chaque sélection débutant de manière synchrone avec la délivrance par la source des informations à afficher sur une ligne de l'autre type de parité de l'écran,

- a) on enregistre dans un premier registre à partir d'un premier registre-tampon les informations à afficher sur ladite ligne sélectionnée de la première partie,

- b) on enregistre dans un second registre à partir d'un second registre-tampon les informations à afficher sur ladite ligne sélectionnée de la seconde partie,

- c) on enregistre les informations délivrées par la source et à afficher sur la ligne dudit autre type de parité de la sélection suivante dans le registre-tampon qui est associé à ladite ligne, d) on transfère à partir de la mémoire les informations à afficher sur la ligne de parité définie en D) de la sélection suivante dans le registretampon qui est associé à ladite ligne.

La présente invention concerne aussi un dispositif pour la mise en oeuvre du procédé comprenant pour adresser les colonnes de l'écran, une source apte à délivrer sur une sortie des informations à afficher.

une mémoire apte à enregister les informations à afficher sur les lignes d'un des types de parité de l'écran, connectée à la sortie de la source,

un moyen pour commander l'écriture ou la lecture de la mémoire, connecté à ladite mémoire.

un moyen pour engendrer des adresses d'écriture et de lecture connecté à ladite mémoire.

un premier moyen d'aiguillage connecté d'une part à la sortie de la source et d'autre part à une sortie de ladite mémoire.

un moyen pour commander l'aiguillage du premier moyen d'aiguillage, connecté au premier moyen d'aiguillage, un second moyen d'aiguillage connecté d'une part à la sortie de la source et d'autre part à la sortie de ladite mémoire,

un moyen pour commander l'aiguillage du second moyen d'aiguillage, connecté au second moyen d'aiguillage, un premier registre-tampon connecté à une sortie du premier moyen d'aiguillage,

un second registre-tampon connecté à une sortie du second moyen d'aiguillage,

un premier registre connecté en entrée à une sortie du premier registre-tampon et apte à délivrer des informations à afficher sur une ligne sélectionnée de la première partie de l'écran.

un second registre connecté en entrée à une sortie du second registre-tampon et apte à délivrer des informations à afficher sur une ligne sélectionnée de la seconde partie de l'écran.

De manière avantageuse, la mémoire est au moins apte à contenir simultanément les informations à afficher sur N/2 lignes de l'écran.

En effet, au cours d'une trame la mémoire enregistre une fois l'information relative aux N lignes d'un des types de parité de l'écran, mais en même temps qu'elle effectue ces opérations d'écriture des informations en provenance de la source, elle transmet, au cours d'opérations de lecture, des informations à l'un ou à l'autre des registres-tampons du dispositif, de sorte qu'à un moment donné, la mémoire ne contient que N/2.M.K bits relatifs aux informations de N/2 lignes.

Selon un mode de réalisation particulier, le moyen de commande d'écriture et de lecture de la mémoire est réalisé par un compteur à deux états binaires présentant une entrée de comptage apte à recevoir un signal impulsionnel de synchronisation de la délivrance des informations à afficher sur une ligne et une deuxième entrée apte à recevoir un signal de remise à zéro, ce compteur délivrant sur une sortie une impulsion à chaque passage à son état initial et sur une autre sortie connectée à la mémoire un signal de commande L/E.

Dans ce mode de réalisation, avantageusement, le moyen pour engendrer des adresses d'écriture et

50

10

20

25

30

35

40

45

de lecture est réalisé par un compteur à N/2 états binaires présentant une entrée de comptage connectée à la sortie du compteur à deux états binaires délivrant des impulsions à chaque passage à son état initial et une deuxième entrée apte à recevoir un signal de remise à zéro, ce compteur délivrant sur une sortie une impulsion à chaque passage à son état initial et sur une autre sortie connectée à la mémoire un signal d'adresse AD.

Selon un mode de réalisation préféré, les premier et second moyens pour commander l'aiguillage des premier et second moyens d'aiguillage sont réalisés par un circuit unique.

Avantageusement, ledit circuit unique est un compteur à deux états binaires présentant une entrée de comptage connectée à la sortie du compteur à N/2 états binaires délivrant sur une sortie une impulsion à chaque passage à son état initial et une deuxième entrée apte à recevoir un signal de remise à zéro, ce compteur délivrant sur une sortie connectée aux premier et second moyens d'aiguillage un signal de commande HB.

Selon un mode de réalisation avantageux pour sélectionner les lignes de l'écran, le dispositif comprend :

au moins un registre présentant une première entrée apte à recevoir un signal d'horloge et une seconde entrée apte à recevoir un signal de donnée.

Selon un mode particulier de réalisation, le dispositif comprend :

un premier registre présentant N étages pour la sélection des N lignes du premier type de parité de la première et la seconde parties de l'écran, et ayant une première entrée apte à recevoir un signal d'horloge et une seconde entrée apte à recevoir un premier signal de donnée (DLI),

un second registre présentant N étages pour la sélection des N lignes du second type de parité de la première et de la seconde parties de l'écran et ayant une première entrée apte à recevoir le signal d'horloge et une seconde entrée apte à recevoir un second signal de donnée (DLP).

De toute façon, les caractéristiques et avantages de l'invention apparaîtront mieux après la description qui suit donnée à titre explicatif et nullement limitatif. Cette description se réfère à des dessins annexés, sur lesquels :

- la figure 1, déjà décrite et relative à l'art antérieur, représente schématiquement un écran matriciel composé de deux parties;

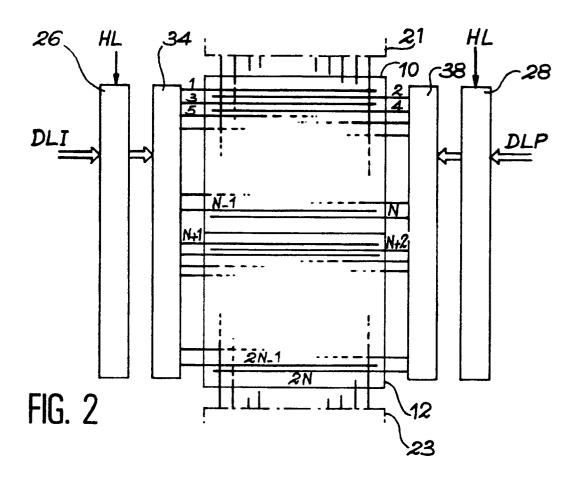

- la figure 2 représente schématiquement un circuit de sélection des lignes d'un écran conforme à l'invention;

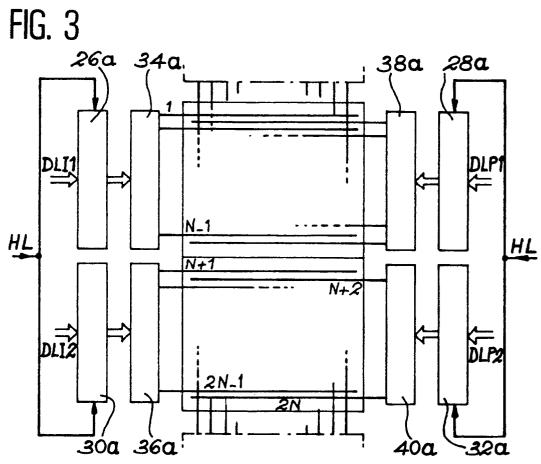

- la figure 3 représente schématiquement une variante de réalisation d'un circuit de sélection conforme à l'invention;

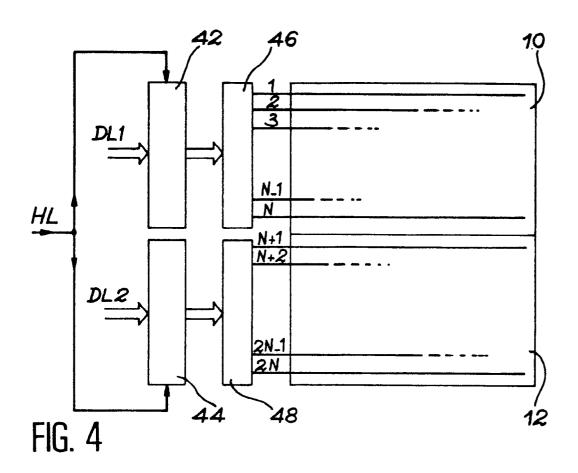

- la figure 4 représente schématiquement une autre variante de réalisation d'un circuit de sélec-

tion conforme à l'invention;

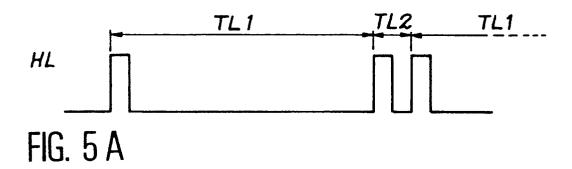

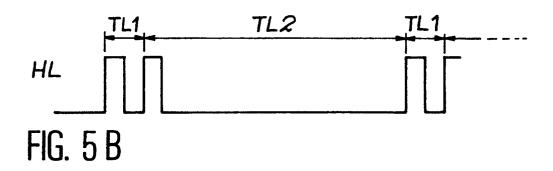

- les figures 5A et 5B représentent schématiquement des signaux d'horloge pour la sélection des lignes dans le cas du circuit de la figure 4;

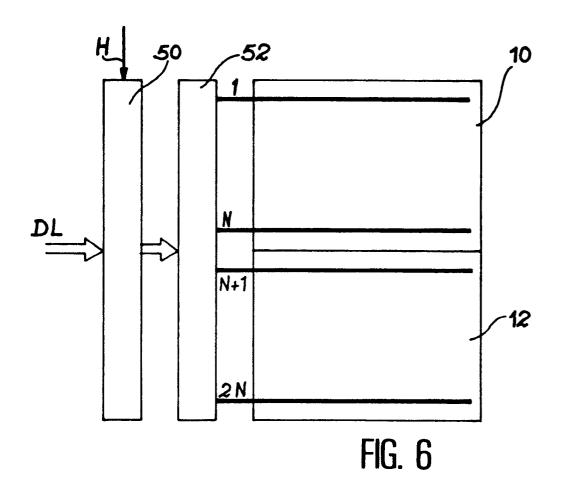

- la figure 6 représente schématiquement une autre variante de réalisation d'un circuit de sélection conforme à l'invention ;

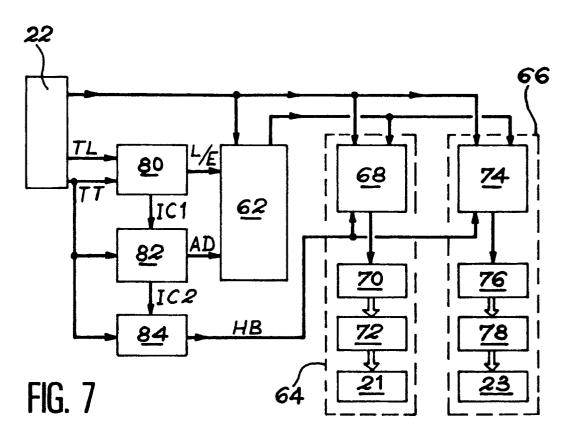

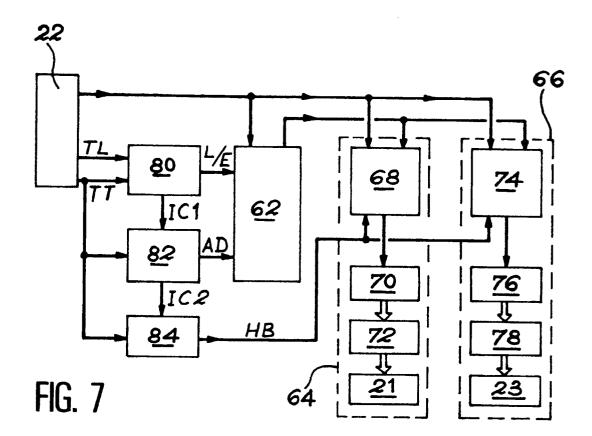

- la figure 7 représente schématiquement un circuit d'adressage des colonnes d'un écran conforme à l'invention.

Les figures 2, 3, 4 et 6 représentent schématiquement différentes variantes d'un circuit pour la sélection d'un écran matriciel ayant deux parties 10, 12 indépendantes mais jointives de manière à assurer la continuité des lignes et des colonnes. L'écran peut être du type à cristaux liquides ou fluorescent à micropointes

Chaque partie 10, 12 comporte un nombre N pair de lignes; pour la première partie 10, ces lignes sont numérotées de 1 à N; pour la seconde partie 12, elles sont numérotées de N+1 à 2N. Les lignes de l'écran sont donc réparties en lignes impaires et paires successives.

Chaque partie de l'écran comporte en outre M colonnes. Les pixels de l'écran sont formés à chaque croisement des lignes et des colonnes.

Selon l'invention, pendant une première moitié du temps de trame, chaque ligne d'un premier type de parité de la première partie 10 de l'écran est sélectionnée simultanément à une ligne d'un second type de parité de la seconde partie 12. Pendant une seconde moitié du temps de trame, chaque ligne du second type de parité de la première partie 10 est sélectionnée simultanément à une ligne du premier type de parité de la seconde partie 12.

Pour plus de clarté dans la description qui suit, on prend à titre d'exemple, comme premier type de parité, la parité impaire et comme second type de parité, la parité paire.

La figure 2 représente schématiquement un écran matriciel comportant deux parties 10, 12 jointives munies d'un circuit de sélection des lignes conforme à l'invention.

Le circuit de sélection comprend deux registres 26, 28 à N étages respectivement alimentés par des signaux de données DLI, DLP concernant les lignes impaires et paires à sélectionner et délivrés par un circuit de commande non représenté. Le registre 26 est connecté à des moyens 34 amplificateurs et adaptateurs d'impédance, eux-mêmes reliés aux lignes impaires de la première partie 10 et de la seconde partie 12.

Le registre 28 est connecté à des moyens 38 amplificateurs et adaptateurs d'impédance, euxmêmes reliés aux lignes paires de la première partie 10 et de la seconde partie 12.

Durant une trame de l'écran toutes les lignes de l'écran sont sélectionnées une fois.

15

35

40

45

A l'origine de chaque trame, les signaux DLI, DLP, respectivement appliqués sur les registres 26, 28 indiquent les lignes à selectionner lors de la première sélection. Ainsi, à titre d'exemple, si les lignes à sélectionner au début du temps trame sont les lignes 1 et N+2, les signaux DLI et DLP correspondent respectivement à des éléments binaires dont seul le premier élément binaire est non nul pour DLI et dont seul le N/2+1 élément binaire correspondant à la ligne N+2 est non nul pour DLP. Les sélections suivantes sont obtenues par décalage des signaux contenus dans les registres par l'application des impulsions d'horloge HL sur des entrées des registres 26 et 28.

Pendant la première moitié d'une trame de l'écran, le registre 26 sélectionne, les unes après les autres, les lignes impaires de la première partie 10. Simultanément, le registre 28 sélectionne, les unes après les autres, les lignes paires de la seconde partie 12.

De cette manière, chaque ligne impaire de la première partie 10 est sélectionnée simultanément à la sélection d'une ligne paire de la seconde partie 12 à laquelle elle est appariée. Par exemple, la ligne numérotée 1 est sélectionnée simultanément avec la ligne numérotée N+2 et ainsi de suite jusqu'à la dernière ligne impaire numérotée N-1 de la première partie 10 sélectionnée simultanément avec la ligne numérotée 2N de la seconde partie 12.

Pendant la seconde moitié d'une trame, le registre 28 sélectionne, les unes après les autres, les lignes paires de la première partie 10.

Simultanément, le registre 26 sélectionne, les unes après les autres, les lignes impaires de la seconde partie 12.

De cette manière, chaque ligne paire de la première partie 10 est sélectionnée simultanément à la sélection d'une ligne impaire de la seconde partie à laquelle elle est appariée. Par exemple, la ligne numérotée 2 est sélectionnée siumultanément avec la ligne numérotée N+1 et ainsi de suite jusqu'à la dernière ligne paire de la première partie 10 numérotée N sélectionnée simultanément avec la ligne numérotée 2N-1 de la seconde partie 12.

La figure 3 représente schématiquement une variante de réalisation d'un circuit de sélection. Cette variante permet la sélection des lignes impaires (respectivement paires) successives de la première partie 10 simultanément avec les lignes paires (respectivement impaires) successives de la seconde partie 12 avec lesquelles elles sont appariées.

Le circuit de sélection comprend encore quatre registres 26a, 28a, 30a, 32a à N/2 étages connectés comme précédemment à des moyens 34a, 38a, 36a, 40a, amplificateurs et adaptateurs d'impédance.

Les quatre registres ne sont pas reliés entre eux mais un signal d'horloge HL identique et appliqué sur une entrée de chacun des registres commande la sélection d'une ligne. Par ailleurs, aprés chaque demi-trame, des signaux de données DLI1, DLP1, DLI2, DLP2 délivrés par un circuit de commande non représenté, sont respectivement appliqués sur les registres 26a, 28a, 30a, 32a. Comme dans le cas de la figure 2, ces signaux de données introduisent dans les étages des registres correspondants des signaux correspondant à des éléments binaires dont seul l'étage correspondant à une ligne à sélectionner contient un élément binaire non nui. Pendant chaque demi-trame, les signaux contenus dans les registres subissent un décalage à chaque impulsion d'horloge de manière à sélectionner les lignes devant l'être.

Pendant une première demi-trame, les registres 26a et 32a (contenant un élément binaire non nul) sélectionnent chacun une ligne alors que les registres 28a et 30a (ne contenant que des éléments binaires nuls) n'en sélectionnent pas ; la situation est inversée lors de la demi-trame suivante.

La figure 4 représente schématiquement une autre variante d'un circuit de sélection conforme à l'invention. Ce dernier est constitué par deux registres 42, 44 à N étages respectivement connectés à des moyens 46, 48 amplificateurs et adaptateurs d'impédance.

Le moyen 46 amplificateur et adaptateur d'impédance est connecté aux lignes de la première partie 10 ; le moyen 48 amplificateur et adaptateur d'impédance est connecté aux lignes de la seconde partie 12.

Des signaux de données DL1 et DL2 délivrés par un circuit de commande non représenté, permettent la sélection des lignes de chaque partie.

Des impulsions d'horloge HL délivrées sur des entrées des registres 42 et 44 commandent les décalages des informations contenues dans les registres 42 et 44 et donc chaque nouvelle sélection d'une paire de lignes.

Ce type de circuit de sélection nécessite des impulsions d'horloge présentant un chronogramme asymétrique.

En effet, les étages des registres alimentés par les signaux DL1 et DL2 permettent, pendant une première moitié de la durée d'une trame, la sélection simultanée d'une ligne impaire de la première partie 10 avec une ligne paire de la seconde partie 12. Pendant la seconde moitié de la durée d'une trame, ils permettent la sélection simultanée d'une ligne paire de la première partie 10 avec une ligne impaire de la seconde partie 12. Pendant chaque demi-trame, les lignes ne devant pas être affichées sont sélectionnées pendant un temps trop court pour être efficace.

Sur la figure 5A, on voit le chronogramme des impulsions d'horloge HL pour la sélection des lignes impaires de la première partie 10 et des lignes paires de la seconde partie utilisées pendant la première moitié d'un temps de trame.

Deux périodes différentes TL1 et TL2 sont utili-

15

20

30

35

sées pour la sélection des lignes impaires et paires de la première partie 10 (et des lignes paires et impaires auxquelles elles sont appariées).

La durée d'une période TL1 séparant deux impulsions d'horloge pendant la sélection d'une ligne impaire de la première partie 10 (ou d'une ligne paire de la deuxième partie) est sensiblement égale à la durée usuelle de sélection d'une ligne. Par contre, la durée d'une période TL2 séparant deux impulsions d'horloge pendant la sélection d'une ligne paire de la première partie (ou d'une ligne impaire de la deuxième partie) est très inférieure à la durée usuelle de sélection d'une ligne. De cette manière, les lignes paires de la partie 10 et les lignes impaires de la partie 12 sont sélectionnées pendant un temps trop court pour qu'un affichage puisse être initié sur ces lignes.

On voit sur la figure 5B le chronogramme des impulsions d'horloge HL pour la sélection des lignes paires de la première partie 10 et des lignes impaires appariées de la seconde partie 12 utilisée pendant la seconde moitié d'un temps de trame.

Sur ce chronogramme, TL1 a une durée très inférieure à la durée usuelle de sélection d'une ligne alors que TL2 présente une durée sensiblement égale à la durée usuelle de sélection d'une ligne. De cette manière, la sélection des lignes ne devant pas supporter un affichage ne s'effectue que pendant un temps trop court pour qu'un affichage puisse être initié et leur sélection est sans conséquence.

La figure 6 représente schématiquement une autre variante de réalisation d'un circuit de sélection des lignes conforme à l'invention.

Ce circuit n'utilise qu'un registre 50 à 2N étages connecté à un moyen 52 amplificateur et adaptateur d'impédance lui-même connecté aux lignes des deux parties 10, 12 de l'écran.

Des signaux de données DL délivrés par un circuit de commande (non représenté) programmé à cet effet, permettent la sélection des lignes devant l'être. Les signaux DL correspondent à l'ensemble des signaux DL1 et DL2 de la figure 4. Le registre 50 contient donc deux éléments binaires non nuls.

Les impulsions d'horloge H délivrées sur une entrée du registre présentent un chronogramme asymétrique de manière analogue à ceux des figures 5A et 5B.

Les impulsions correspondant au chronogramme de la figure 5A sont appliquées au cours d'une première demi-trame et les impulsions correspondant au chronogramme de la figure 5B sont appliquées au cours de la demi-trame suivante.

La figure 7 représente schématiquement un circuit d'adressage des colonnes de l'écran conforme à l'invention. A un rythme régulier, une source 22 délivre des informations codées en binaire dans un ordre relatif aux lignes successives de l'écran. Cette source délivre par ailleurs des impulsions d'horloge TL en synchronisme avec la délivrance des informations à afficher sur une ligne de l'écran et des impulsions de trame TT. Chaque information à afficher sur un pixel de l'écran est codée en binaire par un nombre de K bits.

La sortie de la source délivrant les informations à afficher est connectée à une entrée d'une mémoire 62 de capacité au moins apte à contenir simultanément les informations à afficher sur N/2 lignes de l'écran, à une entrée d'un circuit 64 pour l'adressage des colonnes de la première partie de l'écran et à une entrée d'un circuit 66 pour l'adressage des colonnes de la seconde partie de l'écran.

Le circuit 64 comprend : un moyen d'aiguillage 68 du type multiplexeur connecté d'une part à la source 22 et d'autre part à une sortie de la mémoire 62, un registre-tampon 70 connecté à une sortie du moyen d'aiguillage 68, un registre 72 connecté à une sortie du registre-tampon 70 et un décodeur 21 connecté par une entrée au registre 72 et en sortie aux colonnes de la première partie 10 de l'écran.

Le circuit 66 comprend, connectés de manière analogue au circuit précédent, un moyen d'aiguillage 74 du type multiplexeur, un registre-tampon 76, un registre 78 et un décodeur 23 connecté aux colonnes de la seconde partie 12 de l'écran.

Les décodeurs 21 et 23 réalisent une adaptation entre les informations sous forme binaire contenues dans les registres 72 et 78 et les informations devant être appliquées aux colonnes.

Le circuit d'adressage comporte aussi, un moyen de commande 80 d'écriture et de lecture de la mémoire et délivrant sur une sortie connectée à une entrée de la mémoire 62 un signal L/E d'écriture ou de lecture.

Ce moyen 80 peut être réalisé par un compteur à deux états binaires présentant une première et une seconde entrées de données connectées aux sorties de la source 22 délivrant les impulsions d'horloge et les impulsions de trame, ces dernières effectuant une remise à zéro du compteur 80.

A partir de la remise à zéro, suite à la première impulsion d'horloge TL, le compteur délivre par exemple un signal de lecture en mémoire 62; suite à la seconde impulsion d'horloge le compteur délivre un signal d'écriture en mémoire 62. Le compteur fonctionne de cette manière pour les impulsions d'horloge successives jusqu'à la nouvelle remise à zéro lors d'une impulsion de trame.

De cette manière, au fur et à mesure de leur délivrance par la source 22, les informations devant être affichées sur les lignes de l'écran sont enregistrées une fois sur deux dans la mémoire 62. Aussi, la mémoire n'enregistre que les informations relatives aux lignes d'un seul type de parité. A titre d'exemple, on considérera dans le reste de la description que la mémoire n'enregistre que les informations à afficher sur les lignes paires de l'écran.

Par ailleurs, à chaque impulsion de lecture déli-

10

20

25

35

40

vrée par le compteur à la mémoire, celle-ci transmet les informations relatives à une ligne paire sélectionnée au moyen d'aiguillage 68 ou 74 suivant si la ligne sélectionnée est incluse dans la partie 10 ou 12 de l'écran.

D'autre part, ce compteur 80 délivre des impulsions IC1 sur une sortie à chaque fois qu'il retrouve son état initial, c'est-à-dire toutes les deux impulsions d'horloge.

Le circuit d'adressage comporte en outre un moyen 82 pour engendrer des adresses d'écriture et de lecture connecté par une sortie à une entrée de la mémoire 62.

Ce moyen 82 peut être réalisé par un compteur à N/2 états binaires présentant une entrée de comptage connectée à une sortie du compteur 80 à deux états binaires pour la réception des impulsions IC1. Il présente aussi une deuxième entrée connectée à la sortie de la source 22 délivrant les impulsions de trame qui permettent une remise à zéro du compteur 82.

Le moyen 82 fournit à la mémoire un signal AD désignant les adresses des écritures et des lectures en mémoire 62. Chaque adresse est composée par un mot de L bits avec L entier et respectant la condition :

$(\text{Log N/2})/\text{Log 2} \le L \le 1 + (\text{Log N/2})/\text{Log 2}$

A chaque impulsion IC1, le signal AD désigne une adresse particulière commune à la lecture d'une ligne d'une des parties de l'écran et à l'écriture d'une ligne de l'autre partie de l'écran. Ainsi, à titre d'exemple, pour un écran comportant les lignes paires 2, 4,...N pour la partie 10 et les lignes paires N+2, N+4,...2N pour la partie 12, les adresses de lecture et d'écriture de ces lignes correspondent respectivement à 1, 2,...N/2 codées en binaires. Chaque adresse AD étant maintenue pendant une impulsion de lecture et une impulsion d'écriture, l'information de la ligne correspondante stockée dans la mémoire à l'adresse AD est lue puis remplacée par une information correspondant à une ligne de l'autre partie de l'écran. Ces deux lignes sont des lignes du même ordre dans chaque partie, c'est-à-dire 2 et N+2 ou N+2 et 2, 4 et N+4 ou N+4 et 4 ... N et 2N ou 2N et N.

D'autre part, à chaque fois qu'il retrouve son état initial, c'est-à-dire toutes les N impulsions d'horloge, le compteur à N/2 états binaires délivre une impulsion IC2 sur une sortie.

Le circuit d'adressage comporte enfin des moyens pour la commande des aiguillages des moyens d'aiguillage 68, 74. Ces moyens sont réalisés par un compteur 84 à deux états binaires. Ce compteur 84 présente une entrée de comptage connectée à une sortie du compteur à N/2 états binaires pour la réception des impulsions IC2. Il présente aussi une deuxième entrée connectée à la sortie de la source 22 délivrant des impulsions de trame qui déclenchent sa remise à zéro.

Le compteur 84 délivre un signal HB dont la

valeur binaire détermine si les multiplexeurs 68 et 74 délivrent aux registres-tampon 70 et 76 les informations provenant directement de la source 22 et relatives aux lignes impaires ou provenant de la mémoire 62 et relatives aux lignes paires.

A chaque fois que N/2 impulsions IC1 ont été comptées par le compteur 82, c'est-à-dire lorsque N impulsions d'horloge ont été délivrées par la source 22, le compteur 84 change d'état sous l'action de l'impulsion IC2 délivrée par le compteur 82.

A titre d'exemple, pour une valeur binaire du signal HB égale à "0", c'est-à-dire pendant la première moitié du temps de trame, le multiplexeur 68 délivre sur sa sortie les informations provenant de la source 22, alors que le multiplexeur 74 délivre sur sa sortie les informations provenant de la mémoire 62.

Pour une valeur binaire du signal HB égale à "1", c'est-à-dire pendant la deuxième moitié du temps de trame, le multiplexeur 68 délivre sur sa sortie les informations provenant de la mémoire 62, alors que le multiplexeur 74 délivre sur sa sortie les informations provenant de la source 22.

La sélection par le circuit de sélection des lignes à afficher débute de manière synchrone avec la délivrance par la source 22 des informations à afficher sur une ligne impaire de l'écran. Ce synchronisme est obtenu grâce aux impulsions d'horloge TL et de trame TT qui sont transformées ou non pour former les impulsions d'horloge déclenchant le ou les registres du circuit de sélection.

Au fur et à mesure de leur délivrance par la source 22, les informations à afficher sur les lignes paires de l'écran sont enregistrées dans la mémoire 62.

A chaque sélection d'une paire de lignes, les registres 72 et 78 enregistrent les informations contenues respectivement dans les registres-tampon 70 et 76. Ces informations décodées par les décodeurs 21 et 23 sont affichées sur les lignes sélectionnées des première et seconde parties de l'écran.

Les registres-tampon 70 et 76 enregistrent alors les informations à afficher lors de la sélection suivante. Ces informations proviennent soit directement de la source 22 soit de la mémoire 62 par l'intermédiaire des multiplexeurs 68 et 74 commandés par le signal HB. Il y a donc constamment un décalage entre la délivrance des informations par la source 22 et leur affichage. Ce décalage est égal à un demi-temps de trame pour les informations à afficher sur une ligne paire alors qu'il n'égale que le temps de sélection d'une ligne pour les informations à afficher sur une ligne impaire.

A l'allumage de l'écran, la première trame permet l'initialisation des compteurs, des registres et le remplissage de la mémoire avec les informations à afficher sur la moitié des lignes paires de la trame suivante.

Les différentes connexions de la source 22 aux

éléments 62, 68, 74, de l'élément 62 aux éléments 68, 74, des éléments 68 et 74 aux éléments 70, 76 et de l'élément 82 à l'élément 62 sont en réalité réalisées par des bus.

Le procédé et le dispositif selon l'invention permettent bien de n'utiliser qu'une mémoire de capacité réduite et donc de réduire le coût des écrans à deux parties. Bien entendu, l'invention ne se limite nullement aux exemples de réalisation plus spécialement décrits et représentés ; elle en admet au contraire toutes les variantes.

## Revendications

Procédé de commande d'un écran matriciel composé d'une première partie (10) et d'une seconde partie (12) comportant chacune un nombre N pair de lignes, les lignes de chacune des parties (10, 12) étant réparties en lignes d'un premier type de parité et lignes d'un second type de parité successives, caractérisé en ce qu'il consiste à :

pour chaque trame de L'écran.

A) sélectionner, les unes après les autres, les lignes du premier type de parité successives de la première partie (10);

sélectionner, les unes après les autres, les lignes du second type de parité successives de la seconde partie (12),

chaque ligne du premier type de la première partie (10) étant sélectionnée simultanément à une ligne second type de la seconde partie (12) à laquelle elle est appariée,

B) puis, sélectionner, les unes après les autres, les lignes du second type de parité successives de la première partie (10),

sélectionner, les unes après les autres, les lignes du premier type de parité successives de la seconde partie (12),

chaque ligne du second type de la première partie (10) étant sélectionnée simultanément à une ligne du premier type de la seconde partie (12) à laquelle elle est appariée,

C) pour chaque ligne sélectionnée, afficher des informations devant l'être.

- Procédé selon la revendication 1, lesdites informations à afficher étant délivrées par une source (22) à un rythme régulier et dans un ordre relatif aux lignes successives de l'écran, caractérisé en ce que :

- D) au fur et à mesure de leur délivrance, on enregiste dans une mémoire (62) les informations à afficher sur les lignes d'un des types de parité de l'écran,

- E) parallèlement à chaque sélection d'une ligne de la première partie (10) appariée à une

ligne de la seconde partie (12), chaque sélection débutant de manière synchrone avec la délivrance par la source (22) des informations à afficher sur une ligne de l'autre type de parité de l'écran,

a) on enregistre dans un premier registre (72) à partir d'un premier registre-tampon (70) les informations à afficher sur ladite ligne sélectionnée de la première partie (10).

b) on enregistre dans un second registre (78) à partir d'un second registre-tampon (76) les informations à afficher sur ladite ligne sélectionnée de la seconde partie (12).

c) on enregistre les informations délivrées par la source (22) et à afficher sur la ligne dudit autre type de parité de la sélection suivante dans le registre-tampon qui est associé à ladite ligne,

d) on transfère à partir de la mémoire (62) les informations à afficher sur la ligne de parité définie en D) de la sélection suivante dans le registre-tampon qui est associé à ladite ligne.

Dispositif pour la mise en œuvre du procédé conforme à la revendication 1, caractérisé en œ qu'il comprend, pour adresser les colonnes de l'écran,

une source (22) apte à délivrer sur une sortie des informations à afficher,

une mémoire (62) apte à enregistrer les informations à afficher sur les lignes d'un des types de parité de l'écran, connectée à la sortie de la source,

un moyen pour commander l'écriture ou la lecture de la mémoire, connecté à ladite mémoire,

un moyen (82) pour engendrer des adresses d'écriture et de lecture connecté à ladite mémoire,

un premier moyen d'aiguillage (68) connecté d'une part à la sortie de la source et d'autre part à une sortie de ladite mémoire (62),

un moyen pour commander l'aiguillage du premier moyen d'aiguillage, connecté au premier moyen d'aiguillage,

un second moyen d'aiguillage (74) connecté d'une part à la sortie de la source et d'autre part à la sortie de ladite mémoire (62),

un moyen pour commander l'aiguillage du second moyen d'aiguillage, connecté au second moyen d'aiguillage,

un premier registre-tampon (70) connecté à une sortie du premier moyen d'aiguillage (68), un second registre-tampon (76) connecté à une

sortie du second moyen d'aiguillage (74), un premier registre (72) connecté en entrée à une

9

55

15

10

25

30

35

20

40

45

50

à l un

15

25

sortie du premier registre tampon (70) et apte à délivrer des informations à afficher sur une ligne sélectionnée de la première partie (10) de l'écran, un second registre (78) connecté en entrée à une sortie du second registre-tampon et apte à délivrer des informations à afficher sur une ligne sélectionnée de la seconde partie (12) de L'écran.

- 4. Dispositif selon la revendication 3, caractérisé en ce que la mémoire (62) est au moins apte à contenir simultanément les informations à afficher sur N/2 lignes de l'écran.

- 5. Dispositif selon la revendication 4, caractérisé en ce que le moyen (80) de commande d'écriture et de lecture de la mémoire (62) est réalisé par un compteur à deux états binaires présentant une entrée de comptage apte à recevoir un signal (TL) impulsionnel de synchronisation de la délivrance des informations à afficher sur une ligne et une deuxième entrée apte à recevoir un signal (TT) de remise à zéro, ce compteur délivrant sur une sortie une impulsion à chaque passage à son état initial et sur une autre sortie connectée à la mémoire un signal de commande L/E.

- 6. Dispositif selon la revendication 5, caractérisé en ce que le moyen (82) pour engendrer des adresses d'écriture et de lecture est réalisé par un compteur à N/2 états binaires présentant une entrée de comptage connectée à la sortie du compteur à deux états binaires délivrant des impulsions à chaque passage à son état initial et une deuxième entrée apte à recevoir un signal (TT) de remise à zéro, ce compteur délivrant sur une sortie une impulsion à chaque passage à son état initial et sur une autre sortie connectée à la mémoire un signal d'adresse AD.

- 7. Dispositif selon la revendication 6, caractérisé en ce que les premier et second moyens pour commander l'aiguillage des premier et second moyens d'aiguillage (68, 74) sont réalisés par un circuit unique (84).

- 8. Dispositif selon la revendication 7, caractérisé en ce que ledit circuit unique (84) est un compteur à deux états binaires présentant une entrée de comptage connectée à la sortie du compteur à N/2 états binaires délivrant sur une sortie une impulsion à chaque passage à son état initial et une deuxième entrée apte à recevoir un signal (TT) de remise à zéro, ce compteur délivrant sur une sortie connectée aux premier et second moyens d'aiguillage un signal de commande HB.

- 9. Dispositif selon la revendication 3, caractérisé en

ce qu'il comprend, pour sélectionner les lignes de l'écran.

au moins un registre présentant une première entrée apte à recevoir un signal d'horloge et une seconde entrée apte à recevoir un signal de donnée.

10 10. Dispositif selon la revendication 9, caractérisé en ce qu'il comprend :

un premier registre (26) présentant N étages pour la sélection des N lignes du premier type de parité de la première et de la seconde parties (10) de l'écran, et ayant une première entrée apte à recevoir un signal d'horloge et une seconde entrée apte à recevoir un premier signal de donnée (DLI),

un second registre (30) présentant N étages pour la sélection des N lignes du second type de parité de la première et de la seconde parties (12) de l'écran, et ayant une première entrée apte à recevoir le signal d'horloge et une seconde entrée apte à recevoir un second signal de donnée (DLP).

55

FIG. 1