(19)

Europäisches Patentamt

European Patent Office

Office européen des brevets

(11)

EP 0 468 973 B2

(12)

## NEUE EUROPÄISCHE PATENTSCHRIFT

(45) Veröffentlichungstag und Bekanntmachung des Hinweises auf die Entscheidung über den Einspruch:

**09.05.2001 Patentblatt 2001/19**

(51) Int Cl.<sup>7</sup>: **G09G 1/16**

(45) Hinweis auf die Patenterteilung:

**17.02.1993 Patentblatt 1993/07**

(86) Internationale Anmeldenummer:

**PCT/EP90/00466**

(21) Anmeldenummer: **90904821.7**

(87) Internationale Veröffentlichungsnummer:

**WO 90/13886 (15.11.1990 Gazette 1990/26)**

(22) Anmeldetag: **21.03.1990**

### (54) MONITORSTEUERSCHALTUNG

MONITOR CONTROL CIRCUIT

CIRCUIT DE COMMANDE DE MONITEUR

(84) Benannte Vertragsstaaten:

**AT BE CH DE DK ES FR GB IT LI LU NL SE**

(74) Vertreter: **Schoppe, Fritz, Dipl.-Ing.**

**Schoppe, Zimmermann & Stöckeler**

**Patentanwälte**

**Postfach 71 08 67**

**81458 München (DE)**

(30) Priorität: **12.05.1989 DE 3915562**

(56) Entgegenhaltungen:

**EP-A- 0 236 177 EP-A- 0 247 710**

**DE-A- 3 804 460 FR-A- 2 608 291**

**US-A- 4 796 203**

(43) Veröffentlichungstag der Anmeldung:

**05.02.1992 Patentblatt 1992/06**

- **Texas Instruments MOS memory data book**

1987, S. 4-55 bis 4-79

- **Hitachi Data Book IC Memory Products 1987/88,**

Seiten 257-301

- **IEEE Transactions on Consumer Electronics,**

vol. 34, no. 1, Feb. 88, Seiten 236-245, "TV

Standard Conversion with Picture Memories"

von A. Gebhardt et al.

(60) Teilanmeldung:

**92107715.2 / 0 500 147**

(73) Patentinhaber: **SPEA Software GmbH**

**D-82319 Starnberg (DE)**

(72) Erfinder:

- **SCHWARZ, Stefan**

D-8137 Berg (DE)

- **CARTWRIGHT, Ian**

D-8036 Stockdorf (DE)

## Beschreibung

**[0001]** Die vorliegende Erfindung befaßt sich mit einer Monitorsteuerschaltung für die Ansteuerung eines bei einer zweiten Pixelfrequenz arbeitenden Monitors aufgrund eines eine erste Pixelfrequenz aufweisenden digitalen Bildsignales.

**[0002]** Computermonitore werden bekannterweise in Abhängigkeit von den Anforderungen bezüglich der geforderten Bildschirmauflösung durch Graphikkarten unterschiedlicher Kategorien angesteuert, die sich untereinander durch die horizontale und vertikale Auflösung, also die Anzahl der Pixel, in horizontaler und vertikaler Richtung sowie durch die Pixelfrequenzen unterscheiden. Bekannte Graphikkarten-Standards sind beispielsweise MDA (320 x 200 Bildpunkte, Schwarzweiß, bei 16 MHz Pixelfrequenz), CGA (320 x 200 Bildpunkte, Farbe, bei 20 MHz Pixelfrequenz), HERCULES (740 x 400 Bildpunkte, Schwarzweiß, bei 27 MHz Pixelfrequenz), EGA (640 x 350 Bildpunkte, Farbe, bei 30 MHz Pixelfrequenz), VGA (640 x 480 Bildpunkte, Farbe, bei 32 MHz Pixelfrequenz), SUPER-EGA (800 x 600 bzw. 1024 x 768 Bildpunkte, Farbe, bei 50 MHz Pixelfrequenz, sowie neuerdings die sogenannten HR (High Resolution)-Graphiksysteme mit 1024 x 768, 1080 x 1024 sowie 1600 x 1280 Bildpunkten, Farbe, bei Pixelfrequenzen zwischen 60 MHz und 170 MHz. Für den Fachmann ist es offensichtlich, daß sich diese verschiedenen Graphik-Standards auch bezüglich der Zeilenfrequenzen, also dem Kehrwert der Horizontalsynchronisationssignalperioden, unterscheiden, die für die genannten Systeme bei 17 kHz, 22 kHz, 25 kHz, 31,5 kHz, 50 kHz sowie 64 bis 84 kHz liegen.

**[0003]** Es besteht seit längerer Zeit der Wunsch, die Ausgangssignale der verschiedenen Graphik-Standards mittels eines einzigen Monitors zu Bildschirmbildern umwandeln zu können. Zu diesem Zweck bedient man sich derzeit sogenannter "Multisync"-Monitore, die in der Lage sind, mittels umschaltbarer Schwingkreise mit verschiedenen Horizontalsynchronisationssignalfrequenzen zu arbeiten. Da die Umschaltung des "Multisync"-Monitors von einer Graphiknorm auf die nächste und somit von einer Arbeitsfrequenz auf die nächste mit einer gewissen Einschwingzeit verbunden ist, führt die Umschaltung der Bildschirmdarstellung von einer Graphiknorm auf eine nächste zu zeitlichen Unterbrechungen der Bildschirmanzeige oder anfänglichen Bildstörungen. Selbstredend steigt die Komplexität eines "Multisync"-Monitors mit zunehmender Anzahl der durch diesen bewältigbaren Graphikkarten-Standards an. Eine Anzeige zweier Teilbilder, die von zwei verschiedenen Graphikkarten kreiert werden, auf einem gemeinsamen Bildschirm ist bei den bekannten "Multisync"-Monitoren gleichfalls nicht möglich.

**[0004]** Die DE-A-38 04 460 offenbart bereits eine Monitorsteuerschaltung für Ansteuerung eines bei einer zweiten Pixelfrequenz arbeitenden Monitors aufgrund eines eine erste Pixelfrequenz aufweisenden digitalen

Bildsignales, mit einem eingangsseitigen Seriell-Parallel-Wandler in Form eines Schieberegisters, an dessen Ausgang eine Videospeichervorrichtung angeschlossen ist, in die das eingangsseitige Bildsignal nach seiner 5 Seriell-Parallel-Wandlung ablegbar ist. Da es sich bei dem Speicher lediglich um ein Schieberegister zur Seriell-Parallel-Wandlung handelt, das zum Zwecke der Seriell-Parallel-Wandlung mit dem Takt des Subsystems nach dem jeweiligen Auftreten des Blanksignales 10 des Subsystems getaktet wird, wird das eingangsseitige Bildsignal mit der Frequenz seines Subsystemtaktes in die Videospeichervorrichtung eingeschrieben. Wegen der fehlenden Synchronität des Einschreibens 15 des Bildsignales in die Videospeichervorrichtung mit dem ersten Subsystemtakt und des Auslesens aus dem Videospeicher mit dem Hauptsystemtakt können Überschneidungen des Einschreibens und des Auslesens auftreten. Diese Überschneidungen werden nach dem Stand der Technik dadurch ausgeräumt, daß einige 20 Bildelemente eines jeden Teilbildes nicht aktualisiert werden, indem dem Transferzyklus und somit dem Auslesen des Videospeichers ein Vorrang gegenüber dem Auffrischen eingeräumt wird. Die Folge dieser Art der Steuerung ist ein teilweise nicht aktueller Bildinhalt der 25 jeweiligen Teilbilder.

**[0005]** Aus der DE-A-34 25 636 ist es bekannt, bei einer Raster-Aufzeichnungseinrichtung, deren Rasterelemente in einer vorbestimmten Folge angesteuert werden müssen, und die einen Bildspeicher aufweist, zwischen einem Prozessor und der Aufzeichnungseinrichtung einen Fifo-Speicher anzugeben. Sobald der Fifo-Speicher leer ist, unterbricht ein Interrupt-Befehl das im Prozessor laufende Programm, woraufhin neue Daten 30 in den Fifo-Speicher eingeschrieben werden, wobei nach dessen Füllen der Prozessor den unterbrochenen Programmlauf wieder aufnimmt.

**[0006]** Aus der FR-A-2 608 291 ist eine Schaltung zur Anpassung einer Graphikkarte einer bestimmten Fernsehnorm an einen Monitor einer anderen Fernsehnorm 40 bekannt, bei der eine durch einen Videoprozessor erfolgende Datenverarbeitung durch einen periodisch erzeugten Auftastimpuls in Relation zu den für die Konvertierung nötigen auszulassenden oder einzufügenden Bildzeilen unterbrochen wird. Dies ermöglicht keine 45 vollständige Aktualisierung des Monitorbildes.

**[0007]** Im Hinblick auf diesen Stand der Technik liegt der vorliegenden Erfindung die Aufgabe zugrunde, eine Monitorsteuerschaltung zu schaffen, mit der ein bei einer zweiten Pixelfrequenz arbeitender Monitor mittels 50 eines eine erste Pixelfrequenz aufweisenden digitalen Bildsignales ansteuerbar ist, wobei die anzuzeigenden Bildsignale jeweils aktualisiert sein sollen.

**[0008]** Diese Aufgabe wird erfindungsgemäß durch eine Monitorsteuerschaltung für die Ansteuerung eines 55 bei einer zweiten Pixelfrequenz arbeitenden Monitors aufgrund eines eine erste Pixelfrequenz aufweisenden digitalen Bildsignales gemäß dem Oberbegriff des Patentanspruchs 1 durch die im kennzeichnenden Teil des

Patentanspruchs 1 angegebenen Merkmale gelöst

[0009] Der Erfindung liegt die Erkenntnis zugrunde, daß die Ansteuerung des mit der zweiten Pixelfrequenz arbeitenden Monitors, die mit der ersten Pixelfrequenz weder synchronisiert ist noch üblicherweise in einem festen, geraden Zahlenverhältnis steht, mittels des Bildsignals der ersten Pixelfrequenz dann möglich ist, wenn die Datenworte des digitalen Bildsignals zunächst in einer Fifo-Speichervorrichtung zwischengespeichert werden, bevor sie in eine Videospeichervorrichtung abgelegt werden, die in Synchronisation mit dem Betrieb des Monitors bei der zweiten Pixelfrequenz in einer an sich bekannten Weise auslesbar ist, um die Monitoranzeige zu erzeugen. Wie noch näher erläutert wird, bewirkt die Übertragung der Datenworte von der Fifo-Speichervorrichtung in die Videospeichervorrichtung eine Steuervorrichtung, die mit der Videospeichervorrichtung und der Fifo-Speichervorrichtung verbunden ist und diese in der Weise ansteuert, daß Datenworte aus der Fifo-Speichervorrichtung in die Videospeichervorrichtung einschreibbar ist.

[0010] Bevorzugte Weiterbildungen sind in den Unteransprüchen angegeben.

[0011] Nachfolgend wird unter Bezugnahme auf die beiliegenden Zeichnungen eine bevorzugte Ausführungsform der erfindungsgemäßen Monitorsteuerschaltung näher erläutert. Es zeigen:

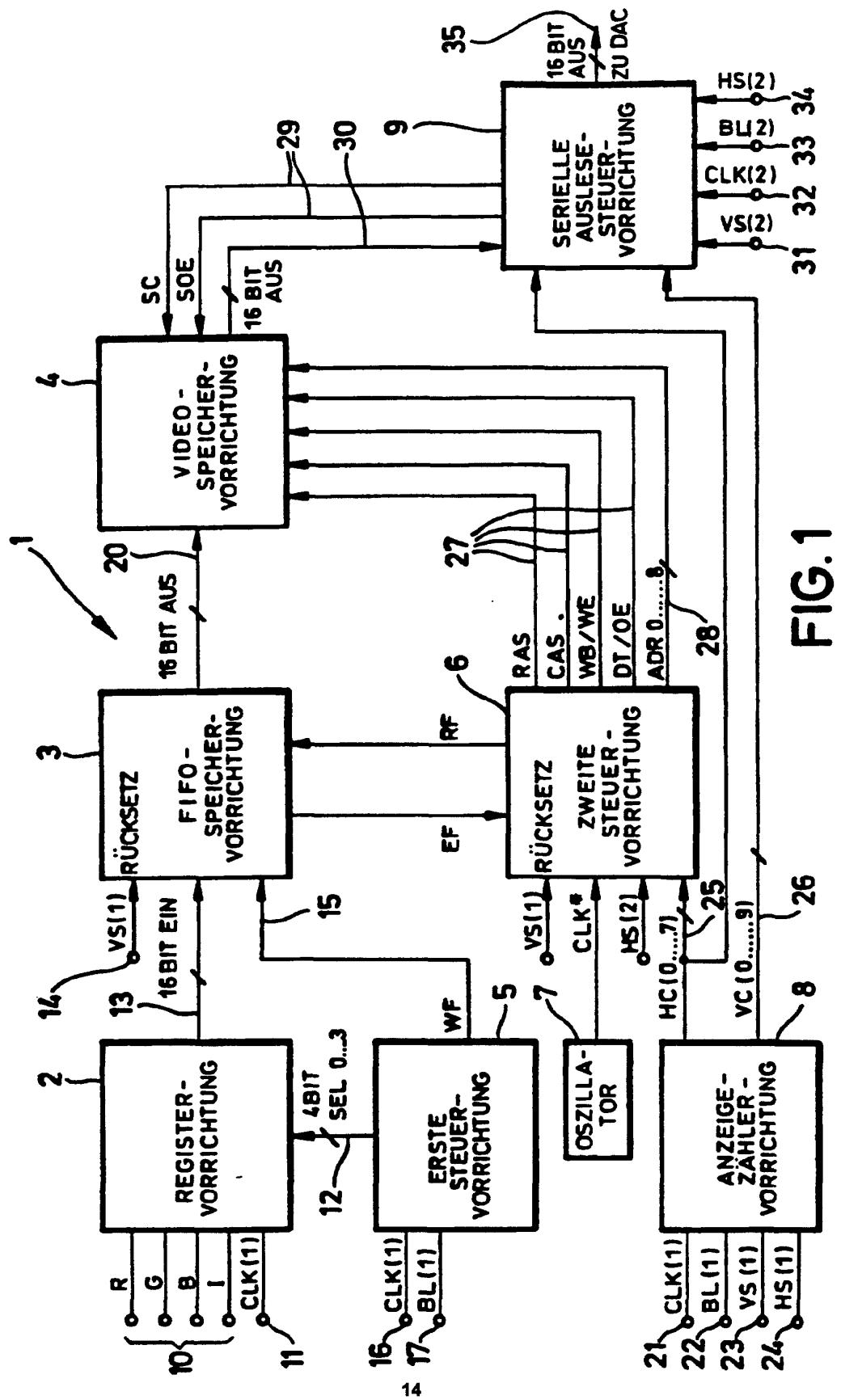

- Fig. 1 ein Blockdiagramm einer Ausführungsform der erfindungsgemäßen Monitorsteuerschaltung;

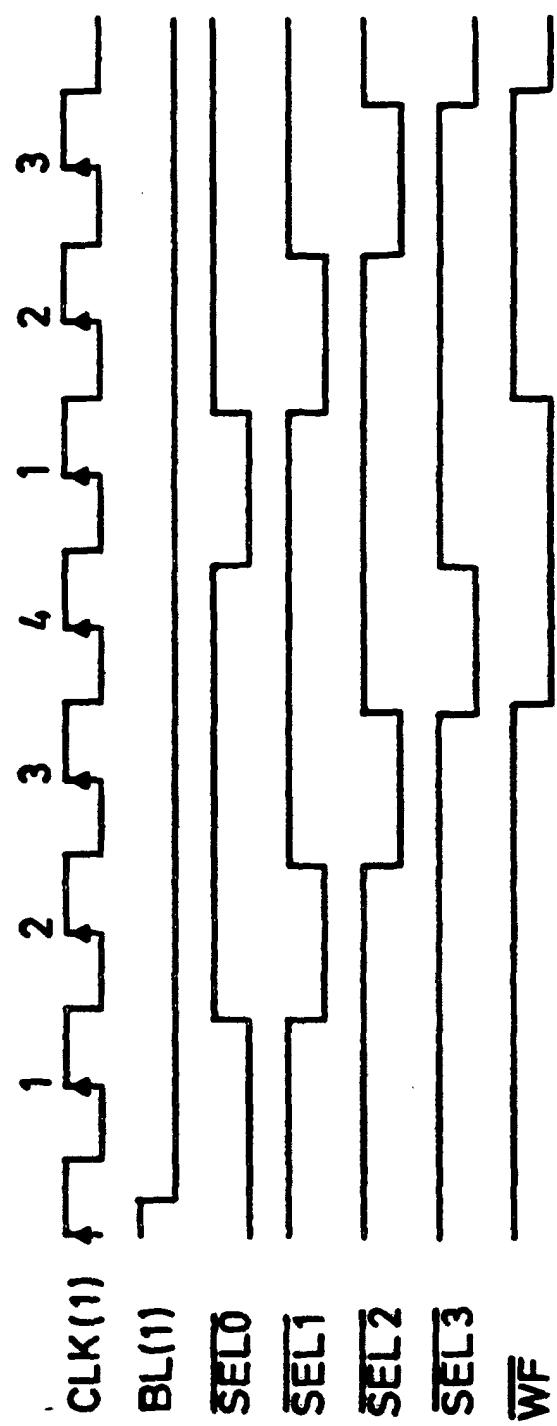

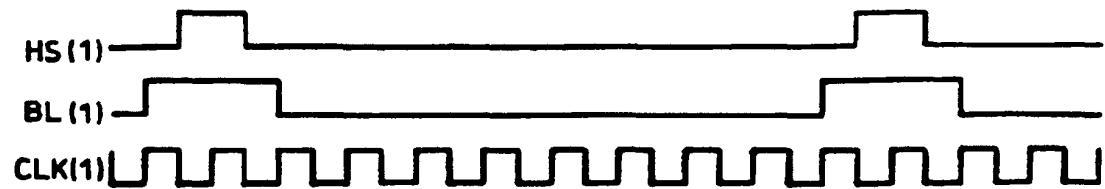

- Fig. 2 eine zeitliche Darstellung von Signalverläufen zur Erläuterung der Funktionsweise einer ersten Steuervorrichtung gemäß Fig. 1;

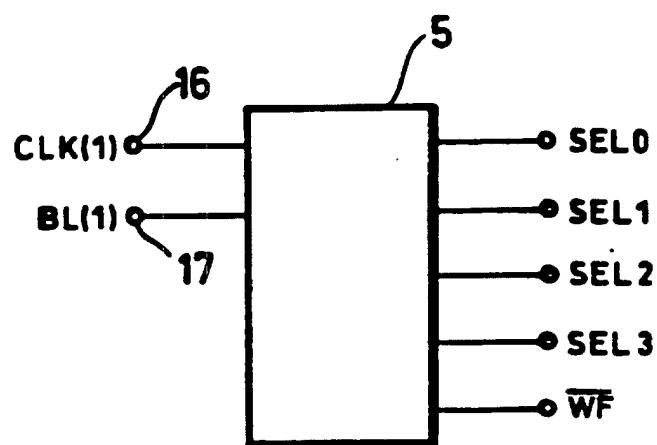

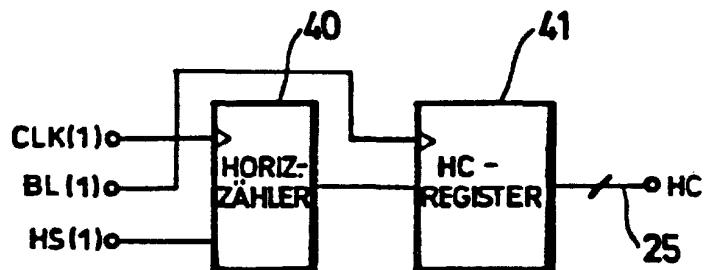

- Fig. 3 eine Blockdarstellung der in Fig. 1 gezeigten ersten Steuervorrichtung;

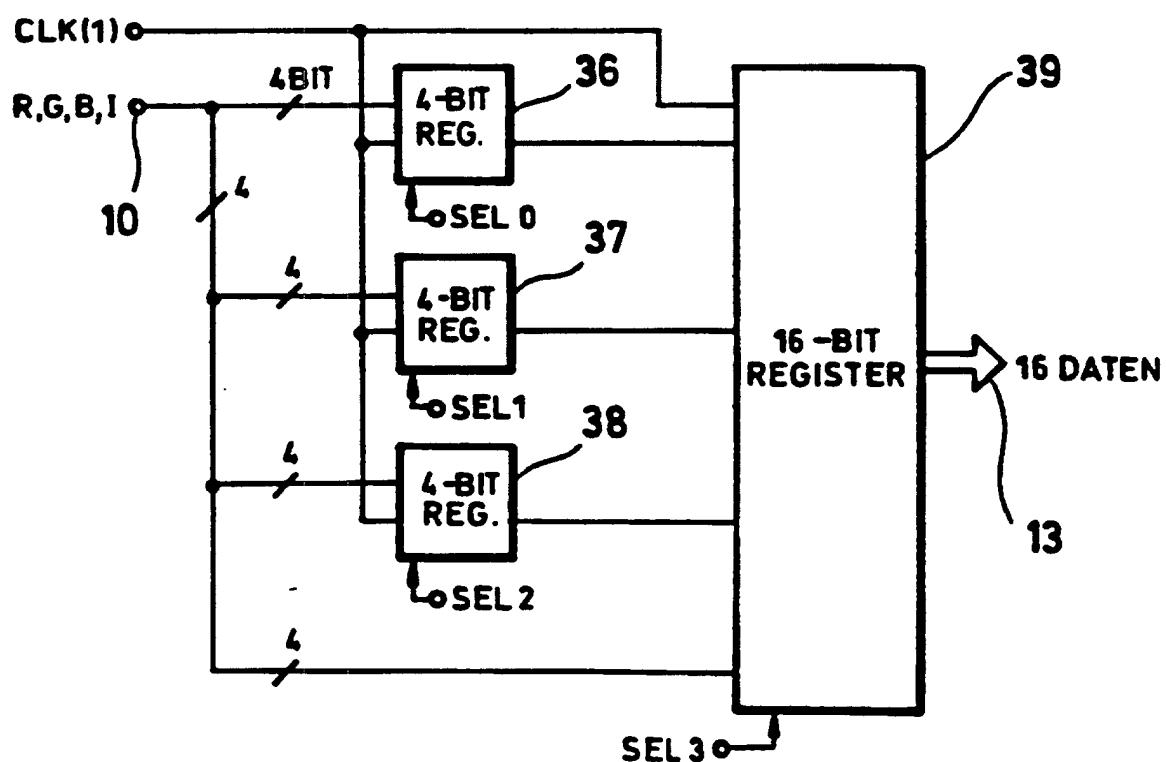

- Fig. 4 ein Blockdiagramm einer in Fig. 1 gezeigten Registervorrichtung;

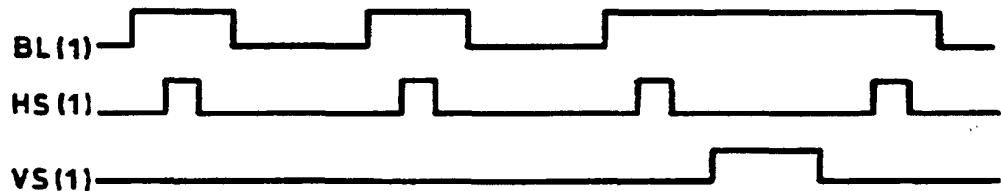

- Fig. 5 eine zeitliche Darstellung von Signalverläufen zur Erläuterung der Funktionsweise einer in Fig. 1 gezeigten Anzeigezählervorrichtung;

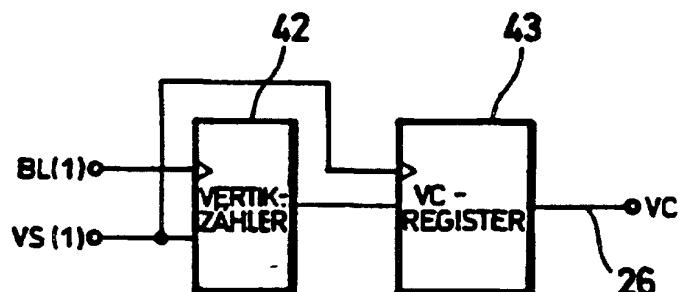

- Fig. 6 ein Blockdiagramm eines Details der Anzeigezählervorrichtung gemäß Fig. 1;

- Fig. 7 eine zeitliche Darstellung von Signalverläufen zur Erläuterung der Funktion eines weiteren Teiles der in Fig. 1 gezeigten Anzeigezählervorrichtung;

- Fig. 8 ein Blockdiagramm eines weiteren Teiles der in Fig. 1 gezeigten Anzeigezählervorrichtung;

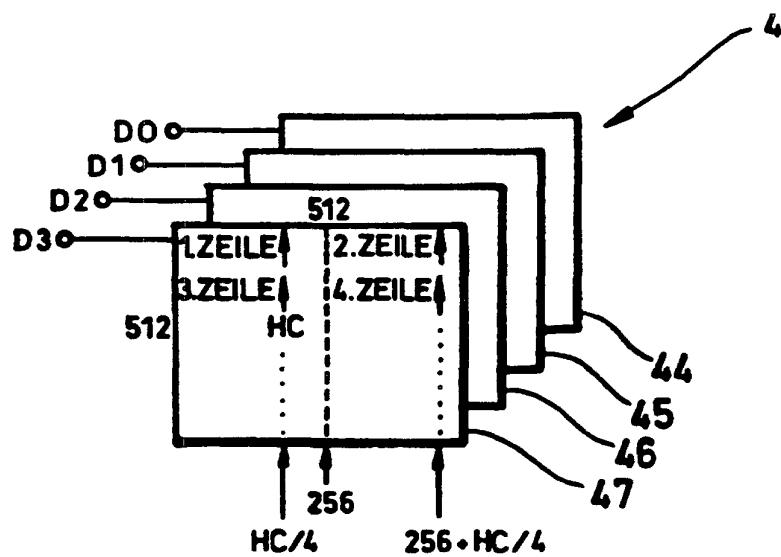

- Fig. 9 eine schematische Darstellung der Speicherorganisation einer in Fig. 1 gezeigten Videospeichervorrichtung; und

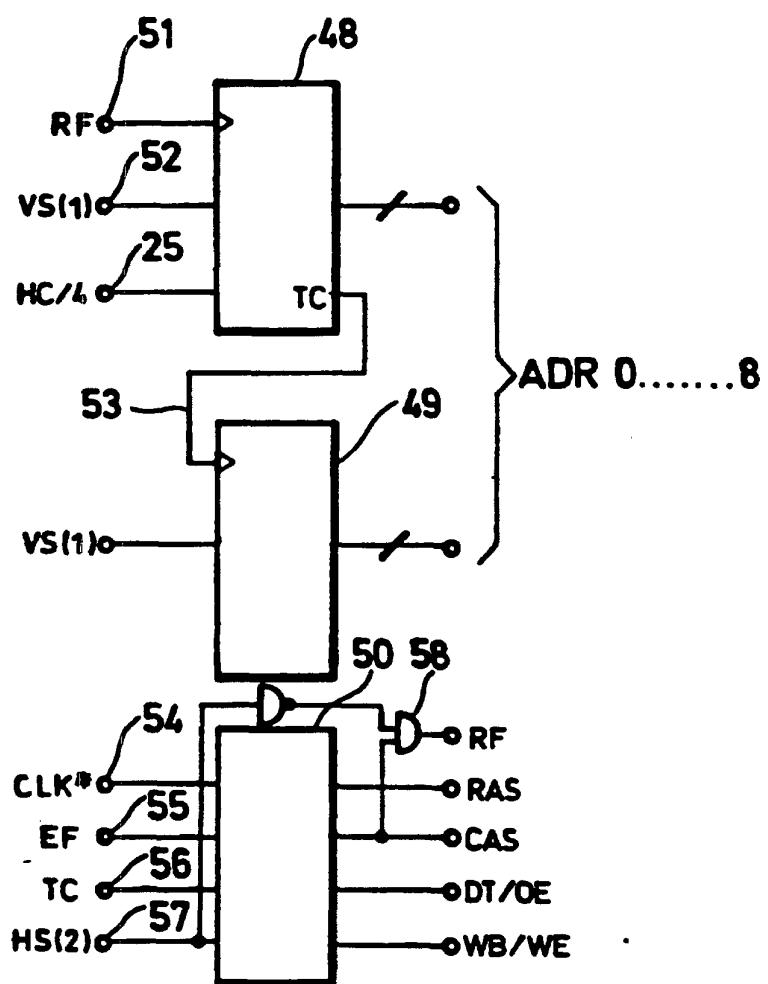

- Fig. 10 Blockdiagramme der Struktur einer in Fig. 1 gezeigten zweiten Steuervorrichtung.

[0012] Die in Fig. 1 gezeigte Ausführungsform einer Monitorsteuervorrichtung gemäß der vorliegenden Erfindung, die in ihrer Gesamtheit mit dem Bezugszeichen 1 bezeichnet ist, umfaßt eine Registervorrichtung 2, ei-

ne als Fifo-Speichervorrichtung ausgebildete erste Speichervorrichtung 3, eine Videospeichervorrichtung 4, eine erste Steuervorrichtung 5, eine zweite Steuervorrichtung 6, einen Oszillator 7, eine Anzeigezählervorrichtung 8 und eine serielle Auslesesteuervorrichtung 9.

[0013] Die Registervorrichtung 2 ist eingangsseitig mit einem Eingangsdatenbus 10 verbunden, auf dem Datenworte eines digitalen Bildsignals mit der ersten Pixelfrequenz vorliegen. Der Eingangsdatenbus 10 kann sich beispielsweise zu einer VGA-Schnittstelle erstrecken. Der Eingangsdatenbus 10 umfaßt im Beispiel je einen Anschluß für die drei Grundfarben R, G, B und einen Anschluß für ein Helligkeitsbit I. Jedes Datenwort stellt ein Pixel mit 4 bit Tiefe dar. Die Registervorrichtung 2 ist ferner eingangsseitig mit einem Takteingang 11 für ein Taktsignal mit der ersten Pixelfrequenz versehen. Die Registervorrichtung 2 empfängt von der ersten Steuervorrichtung 5 Auswahlsignale SEL0, SEL1, SEL2, SEL3 über einen Auswahladatenbus 12, der vier Bit hat. Ausgangsseitig steht die Registervorrichtung 2 über einen ersten Datenbus 13 mit Eingängen der Fifo-Speichervorrichtung 3 in Verbindung, welche ferner einen Rücksetzeingang 14 hat, dem ein Vertikalsynchronisationssignal VS(1) des ersten Bildsignals zuführbar ist. Ferner werden der Fifo-Speichervorrichtung 3 von der ersten Steuervorrichtung 5 an ihrem Schreibeingang 15 ein Schreibbefehlssignal WF zugeführt. Die erste Steuervorrichtung 5 hat einen Takteingang 16 für das erste Taktsignal CLK(1), einen Blankeingang 17 für das Blanksignal BL(1) des ersten Bildsignals.

[0014] Ausgangsseitig steht die Fifo-Speichervorrichtung 3 über einen zweiten Datenbus 20 mit der Videospeichervorrichtung 4 in Verbindung.

[0015] Die Anzeigezählervorrichtung 8 hat einen Takteingang 21 für das erste Taktsignal CLK(1), einen Blankeingang 22 für das Blanksignal BL(1) des ersten Bildsignals, einen Vertikalsynchronisationseingang 23 für das Vertikalsynchronisationssignal VS(1) und einen Horizontalsynchronisationseingang 24 für das Horizontalsynchronisationssignal HS(1).

[0016] Ausgangsseitig steht die Anzeigezählervorrichtung 8 mittels eines dritten Datenbusses 25 für einen Horizontalzählwert HC mit der zweiten Steuervorrichtung 6 sowie mit der seriellen Auslesesteuervorrichtung 9 in Verbindung. Ferner steht die Anzeigezählervorrichtung 8 über einen vierten Datenbus 26 für einen Vertikalzählwert VC mit der seriellen Auslesesteuervorrichtung 9 in Verbindung.

[0017] Ausgangsseitig steht die zweite Steuervorrichtung 6 mit Eingängen der Videospeichervorrichtung über einen Steuerbus 27 und einen Adreßbus 28 in Verbindung. Der Steuerbus 27 umfaßt je eine Leitung für ein Reihenadreßübernahmesignal RAS, ein Spaltenadreßübernahmesignal CAS, ein Schreibbefehlssignal WB/WE und ein Datenübertragungssignal DT/OE für die Übernahme einer Datenzeile aus der Videospeichervorrichtung 4.

chervorrichtung 4 in ein (nicht gezeigtes) Ausleseschieberegister derselben.

**[0018]** Die serielle Auslesesteuervorrichtung 9 steht ausgangsseitig über einen zweiten Steuerbus 29 für Steuersignale SC, SOE für das Auslesen der Videospeichervorrichtung 4 mit Steuereingängen der letztgenannten in Verbindung. Die Videospeichervorrichtung 4 steht wiederum über einen fünften Datenbus 30 mit einem Dateneingang der seriellen Auslesesteuervorrichtung 9 in Verbindung, die ihrerseits einen Vertikalsynchronisationseingang 31 für das Vertikalsynchronisationssignal VS(2) des zweiten, monitorseitigen Bildsignales, einen Takteingang 32 für ein zweites Taktsignal CLK (2) mit der zweiten Pixelfrequenz, einen Blankeingang 33 für das zweite Blanksignal BL(2) sowie einen Horizontalsynchronisationseingang 34 für das Horizontal-synchronisationssignal HS(2) des zweiten, monitorseitigen Bildsignales aufweist.

**[0019]** Ausgangsseitig steht die serielle Auslesesteuervorrichtung 9 über einen sechsten Datenbus 35 mit dem Digital-Analog-Wandler DAC des (nicht dargestellten) Monitors in Verbindung. Da die Struktur des Monitors der im Stand der Technik üblichen entspricht, bedarf es nicht deren Erläuterung.

**[0020]** Nachfolgend wird die Funktionsweise der bevorzugten Ausführungsform gemäß Fig. 1 erläutert, wobei jedoch bezüglich schaltungsmäßigen und funktionellen Details auf die nachfolgende Erläuterung zu den Fig. 2 bis 10 verwiesen wird.

**[0021]** Die Registervorrichtung 2 führt eine Seriell-Parallel-Umsetzung von jeweils vier aufeinanderfolgenden Datenworten, die mit der Pixelfrequenz am Eingangsdatenbus 10 anliegen, durch, wobei die ausgangsseitig erzeugten Datenworte die vierfache Bitzahl haben, also Datenworte einer Länge von 16 Bit sind, die parallel auf den ersten Datenbus 13 gegeben werden. Diese Umsetzung von 4-bit-Datenworten in 16-bit-Datenworte erfolgt unter der Steuerung der ersten Steuervorrichtung 5 mittels der Auswahlsignale SEL0, ... SEL3, die nach Abschluß dieser Umsetzung der Fifo-Speichervorrichtung 3 ein Schreibbefehlssignal 15 zu führt. Sobald mindestens ein Datenwort in der Fifo-Speichervorrichtung 3 abgespeichert ist, erlischt das von dieser der zweiten Steuervorrichtung 6 zugeführte Flag EF über den leeren Speicherzustand der Fifo-Speichervorrichtung, wodurch die zweite Steuervorrichtung darüber informiert wird, daß in der Fifo-Speichervorrichtung 3 in die Videospeichervorrichtung 4 umspeicherbare Datenworte vorliegen. Wie der Name sagt, ist die Fifo-Speichervorrichtung 3 derart aufgebaut, daß in diese zuerst eingelesene Datenworte bei Ansteuerung durch den Lesebefehl RF zuerst über den zweiten Datenbus 20 in die Videospeichervorrichtung 4 eingelesen werden. Wie nachfolgend noch näher erläutert wird, bewirkt die zweite Steuervorrichtung pro Schreibzyklus der Videospeichervorrichtung 4 bzw. Lesezyklus der Fifo-Speichervorrichtung 3 eine Umspeicherung einer Mehrzahl von Datenworten aus der ersten Speichervorrich-

tung 3 in die Videospeichervorrichtung 4, wobei die jeweils umgespeicherte Datenwortzahl, wie noch erläutert wird, von Fall zu Fall variieren kann.

**[0022]** Wie noch näher erläutert wird, benötigt die zweite Steuervorrichtung 6 für die richtige Abspeicherung des digitalen Bildsignals in der Videospeichervorrichtung eine Information über die Anzahl der Pixel pro Zeile des eingangsseitig anliegenden Bildsignals, die auch durch die serielle Auslesesteuervorrichtung 9 benötigt wird, welche zusätzlich die Anzahl der Zeilen des Bildes des eingangsseitigen Bildsignals für die Auslesesteuerung benötigt. Zu diesem Zwecke ermittelt die Anzeigezählervorrichtung 8 bei dem gezeigten, bevorzugten Ausführungsbeispiel durch Zählen der Taktsignale CLK(1) zwischen zwei Blanksignalen BL(1) einen Horizontalzählwert HC(0...9) sowie durch Zählen der Anzahl der Blanksignale BL(1) zwischen zwei Vertikalsynchronisationssignalen VS(1) die Anzahl der Zeilen des durch das erste Bildsignal dargestellten Bildes als Vertikalzählwert VC(0...9).

**[0023]** Die zweite Steuervorrichtung arbeitet auf einer Zeitbasis, die durch den Oszillator 7 festgelegt wird, wobei der Anfang eines Zyklus durch das Auftreten des Vertikalsynchronisationssignales VS(1) am Rücksetzeingang festgelegt wird. Das der zweiten Steuervorrichtung gleichfalls zugeführte zweite (ausgangsseitige) Blanksignal BL(2) dient allein zur Steuerung des Auffrischens der dynamischen Videospeichervorrichtung 4 und zur Steuerung der Schieberegisterübernahme, das die Übernahme einer ganzen Speicherzeile aus der Videospeichervorrichtung 4 in das Ausgangsschieberegister (nicht dargestellt) ermöglicht, und unterrichtet zu diesem Zweck die Zyklussteuerung für die Ansteuerung der Fifo-Speichervorrichtung 3 und der Videospeichervorrichtung 4. Die Ansteuerung der Videospeichervorrichtung beginnt mit der Adressierung der ersten Zeile und der ersten Spalte der Videospeichervorrichtung 4 bei Nicht-Vorliegen des Flag EF, wobei die Adressübernahme durch das Reihenadreßübernahmesignal RAS und das Spaltenadreßübernahmesignal CAS gesteuert werden, wobei während des Schreibmodus das Schreibbefehlssignal WB/WE "tief" ist. Die Übernahme der Datenworte von der Fifo-Speichervorrichtung 3 in die Videospeichervorrichtung 4 geschieht im sogenannten "page-mode", wobei die Zeilenadressierung und das Zeilenadreßübernahmesignal RAS während des Einspeicherns von Datenworten in die verschiedenen Spalten dieser Zeile unverändert bleiben, wodurch in an sich bekannter Weise die Einschreibgeschwindigkeit des Videospeichers erhöht wird. Die genaue Abfolge der einzelnen Steuersignale hängt von der Herstellerspezifikation der Videospeichervorrichtung 4 für den bei diesen Vorrichtungen vorgesehenen "page-mode"-Schreibmodus. Details der Adressierung werden unter Bezugnahme auf die Fig. 9 und 10 näher erläutert.

**[0024]** Die Steuerung des seriellen Auslesens der Videospeichervorrichtung durch die serielle Auslesesteuervorrichtung 9 erfolgt in Synchronisation mit dem mo-

nitorseitig vorliegenden zweiten Horizontalsynchronisationssignal HS(2), Vertikalsynchronisationssignal VS(2), Taktsignal CLK(2) und Blanksignal BL(2) in einer an sich bekannten Weise.

**[0025]** An dieser Stelle sei auf einen wesentlichen Aspekt der Erfindung hingewiesen, der sich aus der erfundungsgemäßen Umsetzung des Bildsignales der ersten Pixelfrequenz in ein Bildsignal der zweiten Pixelfrequenz ergibt. Es ist möglich, nicht nur das am ausgangsseitigen sechsten Datenbus 35 generierte Bildsignal dem Monitor zuzuführen, sondern auch dieses Bildsignal mit einem zweiten, synchronen Bildsignal zu kombinieren, von dem die ausgangsseitige Zeitbasis (VS(2), CLK(2), BL(2), HS(2)) erhalten wurde. Damit ist eine Kombination eines beliebigen ersten Bildsignales, der am Eingang 10, 11 der Schaltung anliegt, mit einem beliebigen zweiten, von einem anderen Graphikstandard stammenden Bildsignal in der Weise möglich, daß das erste Bildsignal auf einer Teilfläche des Monitors zur Anzeige gebracht wird und das zweite Bildsignal auf der restlichen Monitorfläche gezeigt wird.

**[0026]** Die Fig. 2 und 3 verdeutlichen die Betriebsweise der ersten Steuervorrichtung 5, die im wesentlichen als Zähler arbeitet. Durch das erste Blanksignal BL(1) wird die erste Steuervorrichtung 5 in einen Anfangszustand gesetzt, um bei Auftreten eines ersten Taktpulses CLK(1) (mit schaltungstechnisch bedingter Verzögerung) ein nulltes Auswahlsignal SEL0 rückzusetzen und ein erstes Auswahlsignal SEL1 zu setzen, wobei beim zweiten Taktpuls CLK(1) das erste Auswahlsignal rückgesetzt und das zweite Auswahlsignal SEL2 gesetzt wird, usw., wobei schließlich nach dem dritten Puls das dritte Auswahlsignal SEL3 rückgesetzt und das Fifo-Schreibsignal WF gesetzt wird, woraufhin nach dem vierten Taktpuls das dritte Auswahlsignal rückgesetzt und das Fifo-Schreibsignal nach dem darauffolgenden ersten Takt rückgesetzt wird. Diese gestaffelten Auswahlsignale SEL0 bis SEL3 werden zur Steuerung der Registervorrichtung 2 verwendet, deren detaillierter Aufbau nachfolgend unter Bezugnahme auf Fig. 4 näher erläutert wird.

**[0027]** Die Registervorrichtung 2 umfaßt drei 4-bit-Register 36, 37, 38 und ein 16-bit-Register 39, die sämtlich mit dem Takt signaleingang 11 und mit dem Eingangsdatenbus 10 in Verbindung stehen. Die Ausgänge der 4-bit-Register 36 bis 38 sind mit Eingängen des 16-bit-Registers 39 verbunden. Die Register 36 bis 39 werden in der Reihenfolge ihrer Bezugszeichen von den Auswahlsignalen SEL0 bis SEL3 angesteuert, so daß Ansteuerung des 16-bit-Registers 39 durch das vierte Auswahlsignal SEL3 vier eingangsseitige 4-bit-Datenworte in ein ausgangsseitiges 16-bit-Datenwort umgewandelt sind.

**[0028]** Nachfolgend wird unter Bezugnahme auf die Fig. 5 bis 8 die Struktur und Funktion der Anzeigezählervorrichtung 8 näher erläutert. Fig. 5 zeigt die zeitliche Relation des ersten Horizontalsynchronisationssignals HS(1), des ersten Blanksignales BL(1) und des er-

sten Takt signales CLK(1).

**[0029]** Wie in Fig. 6 gezeigt ist, umfaßt die Anzeigezählervorrichtung 8 einen Horizontalzähler 40, dessen Takteingang das erste Takt signal CLK(1) und dessen Rücksetzeingang das erste Horizontalsynchronisationssignal HS(1) zugeführt werden. Das erste Blanksignal BL(1) steuert die Übernahme des Zählerstandes des Horizontalzählers 40 in das Register 41 für den Horizontalzählwert HC, der ausgangsseitig am Bus 25 erscheint.

**[0030]** Fig. 7 zeigt (selbstverständlich mit einer gegenüber Fig. 1 gestrafften Zeitbasis) den schematisierten zeitlichen Zusammenhang zwischen dem ersten Blanksignal BL(1), dem ersten Horizontalsynchronisationssignal HS(1) und dem ersten Vertikalsynchronisationssignal VS(1).

**[0031]** Fig. 8 zeigt den die Vertikalzählung oder Zeilenzählung betreffenden Anteil der Anzeigezählervorrichtung 8, welcher einen Vertikalzähler 42 umfaßt, dessen Takteingang das erste Blanksignal BL(1) und dessen Rücksetzeingang das erste Vertikalsynchronisationssignal VS(1) zugeführt werden, und der ausgangsseitig mit einem Register 43 für den Vertikal-Zählwert VC verbunden ist, dessen Takteingang wiederum durch das erste Vertikalsynchronisationssignal angesteuert, und das ausgangsseitig mit dem vierten Datenbus 26 in Verbindung steht, auf dem der Vertikalzählwert VC ansteht.

**[0032]** Fig. 9 zeigt die Struktur der Videospeichervorrichtung 4, die in dem gezeigten Beispielsfall in vier Speicherebenen 44 bis 47 unterteilt ist. Diese Unterteilung der Videospeichervorrichtung ermöglicht eine Reduktion der Datenflußrate bei der Einspeicherung und eine vereinfachte Adressierung. Bei dem gezeigten Beispielsfall ist jede der Speicherebenen 44 bis 47 mit 512 x 512 Speicherplätzen versehen, wobei jede der Speicherebenen 44 bis 47 bei der Horizontaladresse 256 zweiteilt ist. Es ergibt sich eine Speicherorganisation von 1024 x 1024 Plätzen. Beim Ablegen der Datenworte in der Videospeichervorrichtung werden die Daten jeweils gleichzeitig den Eingängen D0 bis D3 zugeführt, wobei in der beschriebenen "page-mode"-Speicherweise zunächst die erste Zeile des Bildes in den jeweiligen ersten Speicherzeilen zwischen den Horizontaladressen 0 und einer Maximaladresse abgelegt werden, die dem Horizontalzählwert HC geteilt durch die Anzahl 4 der Speicherebenen entspricht. Nach Erreichen dieser Horizontaladresse vollfürt der (noch zu beschreibende) Horizontaladreßzähler einen Sprung zu der Horizontaladresse 256, bei der die Speicherebene unterteilt ist, um fortlaufend von diesem Horizontaladreßwert bis zu einem um den Horizontalzählwert HC geteilt durch die Anzahl der Speicherebenen erhöhten Wert zu zählen, bevor nach erfolgtem Ablegen der zweiten Zeile des ersten Bildsignales die dritte Zeile des ersten Bildsignales sodann in die zweite Zeile der Videospeichervorrichtung 44 bis 47; 4 abgelegt wird. Das Inkrementieren des Reihenadreßzählers erfolgt nach jedem zweiten Erreichen

des um die Anzahl der Speicherebenen geteilten Horizontalzählwertes HC.

[0033] Ein Blockdiagramm der zweiten Steuervorrichtung ist in Fig. 10 wiedergegeben, und umfaßt einen Spaltenadreßzähler 48, einen Reihenadreßzähler 49 und einen Steuersignalgenerator zum Erzeugen der Steuersignale für die Videospeichereinrichtung 4. Der Spaltenadreßzähler 48 wird an seinem Takteingang 51 durch das Fifolesesignal RF getaktet und wird durch das erste Vertikalsynchronisationssignal VS(1) an seinem Rücksetzeingang 52 rückgesetzt und ist ferner an den dritten Datenbus 25 zum Empfangen des Horizontalzählwertes HC angeschlossen.

[0034] Nach Rücksetzen des Spaltenadreßzählers 48 vollführt dieser die soeben unter Bezugnahme auf Fig. 9 erläuterte Horizontaladreßzählung. Im Beispieldfall ist dies eine von Null bis zu einem Viertel des Horizontalzählwertes HC ansteigende Zählung mit nachfolgendem Sprung auf die Mittenhorizontaladresse 256, um anschließend wiederum die Adresse kontinuierlich zu inkrementieren, bis diese Mittenadresse um ein Viertel des Horizontalzählwertes HC übertroffen ist. Zu diesem Zeitpunkt erscheint eine "1" am Steuerausgang TC des Spaltenadreßzählers 48, welcher mit dem Takteingang 53 des Reihenadreßzählers 49 verbunden ist, der durch diesen Signalpuls inkrementiert wird, bis er durch Auftreten des ersten Vertikalsynchronisationssignals VS(1) rückgesetzt wird.

[0035] Dem Steuersignalgenerator 50 werden das Takt signal CLK\* vom Oszillator 7 an dessen Takteingang 54, das Flag EF von der Fifo-Speichervorrichtung 3 an dessen Flageingang 55 das Steuersignal TC vom Spaltenadreßzähler 48 an dessen Steuersignaleingang 56 sowie das sekundärseitige Horizontalsynchronisationssignal HS(2) an dessen Horizontalsynchronisationseingang 57 zugeführt. Die Erzeugung des Reihenadreßübernahmesignals RAS, des Spaltenadreßübernahmesignal CAS, des Datenübernahmesignales DT/OE für die Übernahme von Daten aus der Videospeichervorrichtung in dessen Ausgangsschieberegister und des schreibsignales WB/WE für die Videospeichervorrichtung erfolgt gemäß der Spezifikation der jeweils verwendeten Videospeichervorrichtung für deren Betrieb in den "page-mode"-Schreibmodus. Das Auslesesignal RF kann durch UND-Verknüpfen des Spaltenadreßübernahmesignales CAS und des zweiten Horizontalsynchronisationssignales HS(2) mittels eines Gatters 58 erzeugt werden.

[0036] Bei dem beschriebenen Ausführungsbeispiel wird eine Registervorrichtung verwendet, um die eingesamtseitig anliegenden Datenworte mit der ersten Pixelfrequenz in Datenworte von mehrfacher Bitlänge bei einer durch die Mehrzahl geteilten ersten Pixelfrequenz zu erzeugen, wodurch die Anforderungen an die Einspeicherungsgeschwindigkeit in die Fifo-Speichervorrichtung gesenkt werden können. Die eingesamtseitige Registervorrichtung wird jedoch dann entbehrlich, wenn das erste Bildsignal eine entsprechende niedrige Da-

tenwortrate hat oder wenn eine Fifo-Speichervorrichtung mit entsprechend hoher Arbeitsgeschwindigkeit verwendet wird. In diesem Fall ist auch die erste Steuervorrichtung entbehrlich.

5 [0037] Bei der erläuterten Ausführungsform wird die Abspeicherung in die Videospeichervorrichtung jeweils ausgehend von einer Horizontaladresse 0 und einer Vertikaladresse 0, also ausgehend von der linken oberen Ecke der Videospeichervorrichtung vorgenommen.

10 [0038] Der Erfindungsgegenstand ist nicht beschränkt auf eine bestimmte Anzahl von Bits der Datenworte des verarbeiteten Bildsignales und ist ebenso auf Schwarzweiß-Bildsignale wie Farb-Bildsignale anwendbar. Wenn beispielsweise eine Farbvielfalt von 15 256 Farben gewünscht ist, was Eingangsdatenworten von 8 bit entspricht, so können zwei Schaltungen gemäß Fig. 1 parallel geschaltet werden.

[0039] Obwohl die bevorzugte Ausführungsform des Erfindungsgegenstands hardware-mäßig mittels Gate-20 Arrays implementiert ist, ist es denkbar, Zählovorrichtungen und Steuervorrichtungen sowie eine geeignete Ansteuervorrichtung für die erste Speichervorrichtung, die diese als Fifo-Speichervorrichtung arbeiten läßt, software-mäßig zu realisieren.

25 [0040] Grundsätzlich dient die erfindungsgemäße Monitorsteuerschaltung im wesentlichen zur Ansteuerung eines Monitors, dessen Pixelfrequenz verschieden ist von der des auf diesem darzustellenden digitalen Bildsignales. Jedoch soll der Begriff der "ersten Pixelfrequenz" des Bildsignales und der Begriff der "zweiten Pixelfrequenz" des Monitors so breit verstanden werden, daß hierunter auch frequenzmäßig gleiche oder ähnliche Signale mit unterschiedlicher Phase bzw. Synchronisation fallen.

30 [0041] Die Erfindung arbeitet nicht notwendigerweise mit einem Fifo-Speicher, sondern umfaßt als erste Speichervorrichtung alle solchen Speicher, aus denen zuerst abgespeicherte Daten oder Datengruppen zuerst wieder auslesbar sind, wobei es bei der Alternative der 40 Datengruppen unmaßgeblich ist, in welcher Reihenfolge die Daten innerhalb der Datengruppen ausgelesen werden.

#### 45 Patentansprüche

1. Monitorsteuerschaltung für die Ansteuerung eines Monitors, der ein Monitorbild eines Bildsignales mit einer zweiten Pixelfrequenz anzeigt, aufgrund einer ersten Pixelfrequenz aufweisenden digitalen Bildsignales,

50 bei der das Bildsignal der ersten Pixelfrequenz einem Eingang der Monitorsteuerschaltung zugeführt wird, und

55 bei der das Bildsignal der ersten Pixelfrequenz nicht mit der Monitorbildanzeige der zweiten Pi-

- xelfrequenz synchronisiert ist,

mit einer Fifo-Speichervorrichtung (3),

mit einer ersten Steuervorrichtung (5), die das

an dem Eingang der Monitorsteuerschaltung

anliegende Bildsignal mit einer von der ersten

Pixelfrequenz abhängigen Frequenz in die Fi-

fo-Speichervorrichtung (3) einschreibt,

mit einer an den Ausgang der Fifo-Speichervor-

richtung (3) angeschlossenen Videospeicher-

vorrichtung (4), und

mit einer zweiten Steuervorrichtung (6), die mit

der Videospeichervorrichtung (4) und der Fifo-

Speichervorrichtung (3) verbunden ist und die

Datenworte des digitalen Bildsignales aus der

Fifo-Speichervorrichtung (3) derart ausliest

und in die Videospeichervorrichtung (4) ein-

schreibt, daß das Auslesen der Fifo-Speicher-

vorrichtung (3) während des Auslesens von Da-

tenworten aus der Videospeichervorrichtung (4)

unterbrochen wird und daß das Auslesen der

Fifo-Speichervorrichtung (3) ferner bei Erzeu-

gen eines den leeren Zustand derselben anzei-

genden Signals (EF) unterbrochen wird,

wobei das Auslesen von Datenworten des Bild-

signales aus der Fifo-Speichervorrichtung (3)

durch die zweite Steuervorrichtung (6) auf der

Grundlage eines internen Taktes (CLK\*) der

Monitorsteuerschaltung vorgenommen wird,

so daß die von der Fifo-Speichervorrichtung (3)

in die Videospeichervorrichtung (4) umspei-

cherbare Datenwortanzahl variiert.

- 2.** Monitorsteuerschaltung nach Anspruch 1,

gekennzeichnet durch

eine eingangsseitig mit der Fifo-Speichervor-

richtung (3) verbundene Registervorrichtung (2),

mittels der die bei der ersten Pixelfrequenz empfan-

genen Datenworte des digitalen Bildsignales in Da-

tenworte mit einer Mehrzahl-fachen Bitzahl bezö-

gen auf die Bitzahl der empfangenen Datenworte

bei einer durch die Mehrzahl geteilten ersten Pixel-

frequenz umwandelbar sind.

- 3.** Monitorsteuerschaltung nach Anspruch 2,

dadurch gekennzeichnet,

daß die Registervorrichtung (2) eine gegen-

über der Mehrzahl um eins niedrigere Anzahl

von ersten Registern (36, 37, 38) zur Aufnahme

je eines der empfangenen Datenworte auf-

weist,

daß die Registervorrichtung (2) ferner ein zwei-

- tes Register (39) zur Aufnahme des Datenwör-

tes mit der Mehrzahl-fachen Bitzahl aufweist,

daß mit einem Teil seiner Eingänge an Ausgän-

ge der ersten Register (36, 37, 38) und mit ei-

nem weiteren Teil seiner Eingänge an einen

Bus (10) zur Aufnahme eines der empfangenen

Datenworte angeschlossen ist, und

daß die erste Steuervorrichtung (5) sequentiell

jedes der ersten Register (36, 37, 38) und das

zweite Register (39) mit einem Auswahlsignal

(SEL0, SEL1, SEL2, SEL3) zur Übernahme

eingangsseitig anstehender Datenworte an-

steuert.

- 4.** Monitorsteuerschaltung nach Anspruch 3,

dadurch gekennzeichnet,

daß die erste Steuervorrichtung (5) einen Takt-

eingang (16) aufweist, dem ein Taktsignal (CLK

(1)) der ersten Pixelfrequenz zuführbar ist, und

einen Halteeingang (17) aufweist, dem ein

Blanksignal (BL(1)) des ersten Bildsignales zu-

führbar ist, und

daß die erste Steuervorrichtung (5) eine der

Mehrzahl entsprechende Zahl von Auswahl-

ausgängen (12) hat und derart aufgebaut ist,

daß die Auswahlsignale (SEL0, SEL1, SEL2,

SEL3) an den Auswahlausgängen (12) jeweils

um eine erste Pixelperiode gegeneinander ver-

setzt sind.

- 5.** Monitorsteuerschaltung nach Anspruch 3 oder 4,

dadurch gekennzeichnet,

daß die erste Steuervorrichtung (5) ferner ei-

nen Schreibbefehlausgang zum Erzeugen eines

Schreibbefehles (WF) für die Fifo-Speichervorrich-

tung (3) aufweist, wobei der Schreibbefehl (WF) ge-

genüber dem Auswahlsignal (SEL3) für das zweite

Register (39) um wenigstens eine erste Pixel per-

iodē versetzt ist, und daß die Fifo-Speichervorrich-

tung (3) einen Schreibbefehleingang (15) hat und

bei Anlegen eines Schreibbefehles ein anstehen-

des Datenwort aufnimmt.

- 6.** Monitorsteuerschaltung nach einem der Ansprüche

1 bis 5,

gekennzeichnet durch

eine Anzeigezählervorrichtung (8), der das

erste Taktsignal (CLK(1)) der ersten Pixelfrequenz

und das erste Blanksignal (BL(1)) des ersten Bild-

signales zuführbar sind, wobei die Anzeigezähler-

vorrichtung (8) einen Horizontalzähler (40, 41) zum

Zählen der ersten Taktsignale (CLK(1)) zwischen

zwei ersten Blanksignalen (BL(1)) aufweist.

- 7.** Monitorsteuerschaltung nach Anspruch 6,

dadurch gekennzeichnet,

daß die Anzeigezählervorrichtung (8) ferner

- |                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5  | 13. Monitorsteuerschaltung nach Anspruch 11 oder 12 in Rückbeziehung auf Anspruch 10,<br>dadurch gekennzeichnet,<br>daß die zweite Steuervorrichtung (6) zur Ansteuerung der Videospeichervorrichtung (4) auf der Zeitbasis des durch den Oszillator (7) vorgegebenen Taktes ausgehend von einem logischen Anfangszustand bei Auftreten des ersten Vertikalsynchronisationssignales (VS(1)) pro Auslesetakt jeweils einen Lesebefehlspuls (RF) für die Fifo-Speichervorrichtung (3), ein Horizontaladreßsignal (ADR) und ein Vertikaladreßsignal (ADR) für die Adressierung der Videospeichervorrichtung (4) und Videospeichersteuersignale (RAS, CAS, WB/WE, DT/OE) erzeugt.                                     |

| 8. Monitorsteuerschaltung nach einem der Ansprüche 1 bis 7,<br>dadurch gekennzeichnet,<br>daß die Fifo-Speichervorrichtung (3) einen Rücksetzeingang (14) aufweist, dem das erste Vertikalsynchronisationssignal (VS(1)) zuführbar ist.                                                                                                                                                                                                                | 10 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 9. Monitorsteuerschaltung nach Anspruch 8,<br>dadurch gekennzeichnet,<br><br>daß die Fifo-Speichervorrichtung (3) einen Flag-Ausgang für einen leeren Zustand der Speicherbereiche der Fifo-Speichervorrichtung (3) anzeigen Flag (EF) aufweist, und daß der Flag-Ausgang mit einem FlagEingang der zweiten Steuervorrichtung (6) verbunden ist.                                                                                                       | 15 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 10. Monitorsteuerschaltung nach einem der Ansprüche 7 bis 9,<br>dadurch gekennzeichnet,<br><br>daß die zweite Steuervorrichtung (6) einen Lesebefehlausgang (RF) aufweist, der mit einem Lesesteuereingang der Fifo-Speichervorrichtung verbunden ist, und<br>daß die Fifo-Speichervorrichtung (3) derart ausgebildet ist, daß sie bei jedem Lesebefehlspuls (RF) an ihrem Lesesteuereingang ein Datenwort an die Videospeichervorrichtung (4) abgibt. | 20 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 11. Monitorsteuerschaltung nach einem der Ansprüche 1 bis 10,<br>dadurch gekennzeichnet,<br><br>daß die zweite Steuervorrichtung (6) einen Rücksetzeingang aufweist, dem das Vertikalsynchronisationssignal (VS(1)) des ersten Bildsignales zuführbar ist, und<br>daß die zweite Steuervorrichtung (6) ferner einen Takteingang aufweist, an den ein Oszillator (7) angeschlossen ist                                                                  | 40 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 12. Monitorsteuerschaltung nach einem der Ansprüche 6 bis 11,<br>dadurch gekennzeichnet,<br>daß die zweite Steuervorrichtung (6) mit der Anzeigezählovorrichtung (8) verbunden ist und von dieser zumindest den Zählewert (HC) des Horizontalzählers (40, 41) empfängt.                                                                                                                                                                                | 50 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 45 | 14. Monitorsteuerschaltung nach Anspruch 13,<br>dadurch gekennzeichnet,<br><br>daß die Videospeichervorrichtung (4) ein Ausgangsschieberegister aufweist, und<br>daß die Videospeichersteuersignale ein Spaltenadressenübernahmesignal (CAS), ein Zeilenadressenübernahmesignal (RAS), ein den Schreibzustand für das Einschreiben in die Videospeichervorrichtung (4) darstellendes Schreibsignal (WB/WE) und ein Schieberegisterübernahmesignal (DT/OE), das die Übernahme eines Datenwortes aus der Videospeichervorrichtung (4) in das Ausgangsschieberegister ermöglicht, umfassen.                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 55 | 15. Monitorsteuerschaltung nach Anspruch 14,<br>dadurch gekennzeichnet,<br>daß die zweite Steuervorrichtung (6) die genannten Steuersignale für die Videospeichervorrichtung (4) in einer solchen, von der Spezifikation der verwendeten Videospeichervorrichtung (4) abhängigen Art erzeugt, daß das Einschreiben der von der Fifo-Speichervorrichtung (3) gelieferten Datenworte in die Videospeichervorrichtung (4) in der sogenannten "page-mode"-Speicheransteuerungsart erfolgt, bei der das Zeilenadreßsignal (ADR) und das Zeilenadreßübernahmesignal (RAS) für die Videospeichervorrichtung (4) während der Einspeicherung von Daten in eine Zeile der Videospeichervorrichtung (4) unverändert bleiben. |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 50 | 16. Monitorsteuerschaltung nach einem der Ansprüche 1 bis 15,<br>dadurch gekennzeichnet,<br>daß die Videospeichervorrichtung (4) in mehrere, jeweils gleichzeitig horizontal und vertikal adressierbare und gleichzeitig beschreibbare oder auslesbare Speicherebenen (44 bis 47) unterteilt ist.                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 55 | 17. Monitorsteuerschaltung nach einem der Ansprüche                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

1 bis 16,

dadurch gekennzeichnet,

daß die Videospeichervorrichtung (4) bei wenigstens einer Horizontaladresse (256) in wenigstens einen ersten und zweiten Speicherbereich (0 bis 255, 256 bis 512) unterteilt ist, daß die zweite Steuervorrichtung (6) derart ausgebildet ist, daß sie die Horizontaladresse zunächst ansteigend von null bis zu dem Zählerwert (HC) des Horizontalzählers (40, 41) und anschließend, nach einem Sprung, fortlaufend ab der die Horizontalteilung der Videospeichervorrichtung (4, 44 bis 47) festlegenden Horizontaladresse (256) ansteigend zu bis zu der um den Zählerwert (HC) des Horizontalzählers (40, 41) erhöhten Horizontalteilungsdresse (256) zählt, und daß die Horizontaladresse, die durch die zweite Steuervorrichtung (6) erzeugt wird, durch das erste Vertikalsynchronisationsignal (VS(1)) rückgesetzt wird.

## Claims

1. A monitor control circuit for driving a monitor, which displays a monitor image of an image signal at a second pixel frequency, on the basis of a digital image signal having a first pixel frequency,

wherein the image signal having the first pixel frequency is supplied to an input of the monitor control circuit, and

wherein the image signal of the first pixel frequency is not synchronized with the monitor image display of the second pixel frequency,

the monitor control circuit comprising

a FIFO storage device (3),

a first control device (5) writing the image signal provided at the input of the monitor control circuit with a frequency dependent on the first pixel frequency into the FIFO storage device (3),

a video storage device (4) connected to the output of the FIFO storage device,

a second control device (6) connected to the video storage device (4) and the FIFO storage device (3) and reading data words of the digital image signal from the FIFO storage device (3) and writing them into the video storage device (4) in such a manner that the reading of the data words from the FIFO storage device (3) is interrupted when data words are being read from

the video storage device (4) and that the reading from the FIFO storage device (3) is interrupted when a signal (EF) indicating the empty condition of same is generated,

so that the number of data words which can be re-stored from the FIFO storage device (3) to the video storage device (4) varies.

- 10 2. A monitor control circuit according to claim 1, characterized by

a register device (2), which has its input side connected to the FIFO storage device (3) and by means of which the data words of the digital image signal received at the first pixel frequency can be converted into data words, which include a multiple number of bits with respect to the number of bits in the received data words, at a first pixel frequency divided by said multiple.

- 15 3. A monitor control circuit according to claim 2, characterized in that

20 25 the register device (2) includes a number of first registers (36, 37, 38) equal to said multiple minus one, each of said registers (36, 37, 38) storing one of the received data words,

30 35 the register device (2) additionally includes a second register (39) for storing the data word which includes the multiple number of bits, said second register (39) having part of its inputs connected to outputs of said first registers (36, 37, 38) and another part of its inputs connected to a bus (10) for storing one of the received data words, and

40 45 the first control device (5) sequentially controls each of the first registers (36, 37, 38) and the second register (39) by a selection signal (SEL0, SEL1, SEL2, SEL3) for accepting input-side data words.

4. A monitor control circuit according to claim 3, characterized in that

50 55 the first control device (5) is provided with a clock input (16), which is adapted to have supplied thereto a clock signal (CLK(1)) having the first pixel frequency, and with a holding input (17), which is adapted to have supplied thereto a blank signal (BL(1)) of the first image signal, and

the first control device (5) has a number of selection outputs (12) corresponding to said multiple and is constructed in such a way that the respective selection signals (SEL0, SEL1,

- SEL2, SEL3) at the selection outputs (12) are displaced with respect to one another by a first pixel period.

5. A monitor control circuit according to claim 3 or 4, characterized in that the first control device (5) additionally includes a write command output for producing a write command (WF) for the FIFO storage device (3), said write command (WF) being displaced by at least one first pixel period with respect to the selection signal (SEL3) for the second register (39), and that the FIFO storage device (3) has a write command input (15) and accepts a waiting data word when a write command is applied.

10. A monitor control circuit according to one of claims 1 to 5, characterized by a display counting device (8), which is adapted to have supplied thereto the first clock signal (CLK(1)) having the first pixel frequency and the first blank signal (BL(1)) of the first image signal, said display counting device (8) being provided with a horizontal counter (40, 41) for counting the first clock signals (CLK(1)) between two first blank signals (BL(1)).

15. A monitor control circuit according to claim 6, characterized in that the display counting device (8) additionally included a vertical counter (42, 43), which is adapted to have supplied thereto the first blank signals (BL(1)) and the first vertical synchronization signals (VS(1)) and by means of which the number of first blank signals (BL(1)) between two first vertical synchronization signals (VS(1)) can be ascertained.

20. A monitor control circuit according to one of claims 1 to 7, characterized in that FIFO storage device (3) has a reset input (14), which is adapted to have supplied thereto the first vertical synchronization signal (VS(1)).

25. A monitor control circuit according to claim 8, characterized in that the FIFO storage device (3) has a flag output for a flag (EF) indicating the empty condition of the storage areas of the FIFO storage device (3), and

30. the flag output is connected to a flag input of the second control device (6).

35. A monitor control circuit according to one of claims 1 to 7, characterized in that the second control device (6) has a read command output (RF) which is connected to a read

40. control input of the FIFO storage device, and the FIFO storage device (3) is constructed in such a way that in response to each read command pulse (RF) applied to its read control input it will transfer a data word to the video storage device (4).

45. A monitor control circuit according to one of claims 1 to 11, characterized in that the second control device (6) has a reset input, which is adapted to have supplied thereto the vertical synchronization signal (VS(1)) of the first image signal, and the second control device (6) is additionally provided with a clock input which has connected thereto an oscillator (7).

50. A monitor control circuit according to one of claims 6 to 11, characterized in that the second control device (6) is connected to the display counting device (8) and receives therefrom at least the count (HC) of the horizontal counter (40, 41).

55. A monitor control circuit according to claim 11 or 12 in dependence on claim 10, characterized in that for driving the video storage device (4) on the time basis of the clock predetermined by the oscillator (7), the second control device (6) will start from a logical initial condition and produce, per read cycle, one read command pulse (RF) for the FIFO storage device (3), one horizontal address signal (ADR) and one vertical address signal (ADR) for addressing the video storage device (4) and video storage control signals (RAS, CAS, WB/WE, DT/OE) in response to the appearance of the first vertical synchronization signal (VS(1)).

60. A monitor control circuit according to claim 13, characterized in that the video storage device (4) is provided with an output shift register, and the video storage control signals comprise a column address transfer signal (CAS), a line address transfer signal (RAS), a write signal (WB/WE) representative of the write condition for writing into the video storage device (4) and a shift register transfer signal (DT/OE) permitting transfer of a data word from the video storage device (4) to the output shift register.

65. A monitor control circuit according to claim 14, characterized in that the second control device (6) pro-

- duces the above-mentioned control signals for the video storage device (4) in a way, dependent on the specification of the video storage device (4) used, such that the data words supplied by the FIFO storage device (3) are written into the video storage device (4) in the so-called "page-mode" memory control fashion, in the case of which the line address signal (ADR) and the line address transfer signal (RAS) for the video storage device (4) remain unchanged when data are being stored in a line of the video storage device (4). 5

- 16.** A monitor control circuit according to one of claims 1 to 15, characterized in that the video storage device (4) is subdivided into a plurality of storage levels (44 to 47) adapted to be horizontally and vertically addressed at the same time and adapted to be written and read at the same time. 10

- 17.** A monitor control circuit according to one of claims 1 to 16, characterized in that the video storage device (4) is subdivided at least one horizontal address (256) into at least one first and one second storage area (0 to 255, 256 to 512), the second control device (6) is constructed such that it will first count the horizontal address from zero to the count (HC) of the horizontal counter (40, 41) and, subsequently, after a jump, it will continue to count from the horizontal address (256), which determines the horizontal division of the video storage device (4, 44 to 47), up to the horizontal division address (256) increased by the count (HC) of the horizontal counter (40, 41), and the horizontal address produced by the second control device (6) is reset by the first vertical synchronization signal (VS(1)). 15

- the video storage device (4) is subdivided at at least one horizontal address (256) into at least one first and one second storage area (0 to 255, 256 to 512), the second control device (6) is constructed such that it will first count the horizontal address from zero to the count (HC) of the horizontal counter (40, 41) and, subsequently, after a jump, it will continue to count from the horizontal address (256), which determines the horizontal division of the video storage device (4, 44 to 47), up to the horizontal division address (256) increased by the count (HC) of the horizontal counter (40, 41), and the horizontal address produced by the second control device (6) is reset by the first vertical synchronization signal (VS(1)). 20

- with a first control device (5) which enters into the 'fifo' memory device (3) the video signal present at the input of the monitor control command circuit with a frequency depending on the first pixel frequency, with a 'fifo' memory device (4) connected to the output of the 'fifo' memory device (3), and 25

- with a second control device (6) which is connected to the 'video' memory device (4) and to the 'fifo' memory device (3) and which reads data words from the digital video signal of the 'fifo' memory device (3) and enters them into the 'video' memory device (4) of such a kind that the reading of the 'fifo' memory device (3) is interrupted during the reading of data words from the 'video' memory device (4) and that the reading of the 'fifo' memory device (3) is, however, interrupted during the generation of a signal (EF) indicating the empty state of the latter, 30

- the reading of data words from the digital video signal of the 'fifo' memory device (3) being carried out by the second control device (6) based on an internal clock pulse (CLK\*) of the monitor control command circuit, so that the number of data words which can be stored in the 'video' memory device (4) in the 'fifo' memory device (3) varies. 35

- 2.** Monitor control circuit according to claim 1, characterized in that the digital video signal received at the second data word frequency is converted into data words having a bit number multiple based on the bit number of the data words received at the first pixel frequency divided by the plurality. 40

- 3.** Monitor control circuit according to claim 2, characterized in that the first register (2) has a number of first registers (36, 37, 38) for recording each of the data words received at the second pixel frequency, and that the second register (39) has a bit number multiple, which is connected to a part of its inputs, to the outputs of the first registers (36, 37, 38) and, via another part of its inputs, to a collector (10) for recording one of the data words received at the second pixel frequency, and that the first control device (5) sequentially controls each of the first registers (36, 37, 38) and the second register (39) with a selection signal (SEL0, SEL1, SEL2, SEL3) for resuming the data words. 45

- 4.** Monitor control circuit according to claim 3, characterized in that the first register (2) has a number of first registers (36, 37, 38) for recording each of the data words received at the second pixel frequency, and that the second register (39) has a bit number multiple, which is connected to a part of its inputs, to the outputs of the first registers (36, 37, 38) and, via another part of its inputs, to a collector (10) for recording one of the data words received at the second pixel frequency, and that the first control device (5) sequentially controls each of the first registers (36, 37, 38) and the second register (39) with a selection signal (SEL0, SEL1, SEL2, SEL3) for resuming the data words. 50

- 5.** Monitor control circuit according to claim 4, characterized in that the first register (2) has a number of first registers (36, 37, 38) for recording each of the data words received at the second pixel frequency, and that the second register (39) has a bit number multiple, which is connected to a part of its inputs, to the outputs of the first registers (36, 37, 38) and, via another part of its inputs, to a collector (10) for recording one of the data words received at the second pixel frequency, and that the first control device (5) sequentially controls each of the first registers (36, 37, 38) and the second register (39) with a selection signal (SEL0, SEL1, SEL2, SEL3) for resuming the data words. 55

## Revendications

- 1.** Circuit de commande de moniteur pour la commande d'un moniteur affichant une image de moniteur d'un signal vidéo à une seconde fréquence de pixels sur base d'un signal vidéo numérique présentant une première fréquence de pixels, 45

- dans lequel le signal vidéo à la première fréquence de pixels est amené à une entrée du circuit de commande de moniteur, et dans lequel le signal vidéo à la première fréquence de pixels n'est pas synchronisé avec l'affichage d'image de moniteur à la seconde fréquence de pixels, avec un dispositif de mémoire 'fifo' (3), 50

- dans lequel le signal vidéo à la première fréquence de pixels est amené à une entrée du circuit de commande de moniteur, et dans lequel le signal vidéo à la première fréquence de pixels n'est pas synchronisé avec l'affichage d'image de moniteur à la seconde fréquence de pixels, avec un dispositif de mémoire 'fifo' (3), 55

- présents du côté entrée.

4. Circuit de commande de moniteur suivant la revendication 3, caractérisé en ce que le premier dispositif de commande (5) présente une entrée d'horloge (16), à laquelle peut être amené un signal d'horloge (CLK) de la première fréquence de pixels, et présente une entrée de maintien (17), à laquelle peut être amenée un signal de suppression (BL(1)) du premier signal vidéo, et que le premier dispositif de commande (5) présente un nombre de sorties de sélection (12) correspondant à la pluralité et se présente de telle manière que les signaux de sélection (SEL0, SEL1, SEL2, SEL3) sont, aux sorties de sélection (13), chaque fois décalés d'une première période de pixels l'un par rapport à l'autre.

5. Circuit de commande de moniteur suivant la revendication 3 ou 4, caractérisé en ce que le premier dispositif de commande (5) présente, en outre, une sortie de commande d'écriture pour engendrer une commande d'écriture (WF) pour le dispositif de mémoire 'fifo' (3), la commande d'écriture (WF) étant décalée, par rapport au signal de sélection (SEL3) pour le second registre (39), d'au moins une première période de pixels, et que le dispositif de mémoire 'fifo' (3) présente une entrée pour commande d'écriture (15) et, lorsqu'une commande d'écriture se présente, enregistre un mot de données présent.

6. Circuit de commande de moniteur suivant l'une des revendications 1 à 5, caractérisé par un dispositif compteur d'affichage (8) auquel peuvent être amenés le premier signal d'horloge (CLK(1)) de la première fréquence de pixels et le premier signal de suppression (BL(1)) du premier signal vidéo, le dispositif compteur d'affichage (8) présentant un compteur horizontal (40, 41) pour le comptage des premiers signaux d'horloge (CLK(1) entre deux premiers signaux de suppression (BL(1)).

7. Circuit de commande de moniteur suivant la revendication 6, caractérisé en ce que le dispositif compteur d'affichage (8) présente, en outre, un compteur vertical (42, 43) auquel peuvent être amenés les premiers signaux de suppression (BL(1)) et les premiers signaux de synchronisation verticale (VS(1)) et à l'aide duquel peut être déterminé le nombre de premiers signaux de suppression (BL(1)) entre deux premiers signaux de synchronisation verticale (VS(1)).

8. Circuit de commande de moniteur suivant l'une des revendications 1 à 7, caractérisé en ce que le dispositif de mémoire 'fifo' (3) présente une entrée de temporisation à laquelle peut être amené le premier signal de synchronisation verticale (VS(1)).

9. Circuit de commande de moniteur suivant la revendication 8, caractérisé en ce que le dispositif de mémoire 'fifo' (3) présente une sortie de drapeau pour un drapeau (EF) indiquant un état libre des zones de mémoire du dispositif de mémoire 'fifo' (3), et que la sortie de drapeau est reliée à une entrée de drapeau du second dispositif de commande (6).

10. Circuit de commande de moniteur suivant l'une des revendications 7 à 9, caractérisé en ce que le second dispositif de commande (6) présente une sortie de commande de lecture (RF) qui est reliée à une entrée de commande de lecture du dispositif de mémoire 'fifo' et que le dispositif de mémoire 'fifo' (3) se présente de telle manière qu'il transmet, à chaque impulsion de commande de lecture (RF) à son entrée de commande de lecture, un mot de données au dispositif de mémoire vidéo (4).

11. Circuit de commande de moniteur suivant l'une des revendications 1 à 10, caractérisé en ce que le second dispositif de commande (6) présente une entrée de temporisation à laquelle peut être amené le signal de synchronisation verticale (VS(1)) du premier signal vidéo et que le second dispositif de commande (6) présente, en outre, une entrée d'horloge, à laquelle est raccordé un oscillateur (7).

12. Circuit de commande de moniteur suivant l'une des revendications 6 à 11, caractérisé en ce que le second dispositif de commande (6) est relié au dispositif compteur d'affichage (8) et reçoit de celui-ci au moins la valeur de comptage (HC) du compteur horizontal (40, 41).

13. Circuit de commande de moniteur suivant la revendication 11 ou 12, en rapport avec la revendication 10, caractérisé en ce que le second dispositif de commande (6) engendre, pour la commande du dispositif de mémoire vidéo (4), sur la base temporelle du temps donné par l'oscillateur (7), partant d'un état de départ logique lors de la production du premier signal de synchronisation verticale (VS(1)), par temps de lecture, chaque fois une impulsion de commande de lecture (RF) pour le dispositif de mémoire 'fifo' (3), un signal d'adresse horizontale (ADR) pour l'adressage du dispositif de mémoire vidéo (4) et des signaux de commande de mémoire vidéo (RAS, CAS, WB/WE, DT/OE).

14. Circuit de commande de moniteur suivant la revendication 13, caractérisé en ce que le dispositif de mémoire vidéo (4) présente un registre variable de sortie et que les signaux de commande de mémoire vidéo comprennent un signal de reprise d'adresse de colonne (CAS), un signal de reprise d'adresse de ligne (RAS), un signal d'écriture (WB/WE) représentant l'entrée dans le dispositif de mémoire vidéo

et un signal de reprise de registre variable (DT/OE) qui permet la reprise d'un mot de données du dispositif de mémoire vidéo (4) dans le registre variable de sortie.

5

- 15.** Circuit de commande de moniteur suivant la revendication 14, caractérisé en ce que le second dispositif de commande (6) engendre lesdits signaux de commande pour le dispositif de mémoire vidéo (4) d'une manière, en fonction de la spécification du dispositif de mémoire vidéo (4), telle que l'entrée des mots de données fournis par le dispositif de mémoire 'fifo' (3) dans le dispositif de mémoire vidéo (4) se fait suivant le type de commande de mémoire appelé "page mode" (mode par pages), dans lequel le signal d'adresse de ligne (ADR) et le signal de reprise d'adresse de ligne (RAS) pour le dispositif de mémoire vidéo (4) restent inchangés pendant la mémorisation de données sur une ligne du dispositif de mémoire vidéo (4).

10

15

20

- 16.** Circuit de commande de moniteur suivant l'une des revendications 1 à 15, caractérisé en ce que le dispositif de mémoire vidéo (4) est subdivisé en plusieurs plans de mémoire (44 à 47) pouvant, chacun, être simultanément adressés horizontalement et verticalement et pouvant être occupés en écriture ou lus simultanément.

25

- 17.** Circuit de commande de moniteur suivant l'une des revendications 1 à 16, caractérisé en ce que le dispositif de mémoire vidéo (4) est divisé, à au moins une adresse horizontale (256), en au moins une première et une seconde zone de mémoire (0 à 255, 256 à 512), que le second dispositif de commande (6) se présente de telle manière qu'il compte tout d'abord l'adresse horizontale, de manière croissante de zéro à la valeur de comptage (HC) du compteur horizontal (40, 41), et, ensuite, après un saut, en continuant à partir de l'adresse horizontale (256) établissant la division horizontale du dispositif de mémoire vidéo (4, 44 à 47), de manière croissante jusqu'à l'adresse de division horizontale (256) augmentée de la valeur de comptage (HC) du compteur horizontal (30, 41), et que l'adresse horizontale, qui est engendrée par le second dispositif de commande (6), est retardée par le premier signal de synchronisation verticale (VS(1)).

30

35

40

45

50

55

FIG. 1

FIG. 2

FIG.3

**FIG.5**

**FIG.6**

**FIG.7**

**FIG.8**

FIG.9

FIG.10