(1) Publication number:

0 476 444 A1

#### (12)

#### **EUROPEAN PATENT APPLICATION**

(21) Application number: 91115004.3

(51) Int. Cl.5: **H04L** 12/28, H04B 10/14

2 Date of filing: 05.09.91

Priority: 06.09.90 JP 238591/90

Date of publication of application:25.03.92 Bulletin 92/13

Designated Contracting States:

DE FR GB

7) Applicant: FUJITSU LIMITED 1015, Kamikodanaka Nakahara-ku Kawasaki-shi Kanagawa 211(JP)

2 Inventor: Shikata, Kiyotaka, c/o FUJITSU

LIMITED

1015, Kamikodanaka, Nakahara-ku Kawasaki-shi, Kanagawa, 211(JP) Inventor: Takao, Shinji, c/o FUJITSU KYUSHU DIG. TECHN. LTD. 2-3-7, Hakataekimae, Hakata-ku Fukuoka-shi, Fukuoka, 812(JP)

Representative: Lehn, Werner, Dipl.-Ing. et al Hoffmann, Eitle & Partner Patentanwälte Arabellastrasse 4

W-8000 München 81(DE)

#### (54) Optical transceiver.

57 An optical transceiver is coupled to a U-shaped optical bus (10) and to data terminals employing CSMA/CD. The optical transceiver includes a serialparallel converter (11) for carrying out a conversion between data to and from the data terminals and transmitting packets to be transmitted from and receiving packets to be received by the data terminals via the serial-parallel converter, an optical bus interface (12) for matching the transmitting and receiving packets to the U-shaped optical bus which is used as a transmission line, a common bus (13) which provides a data transfer path between the serialparallel converter and the data terminals during transmitting and receiving operations, a transmitting packet intermission part (14) for intermitting the transmitting packets in response to a transmission control signal, a receiving packet intermission part (15) for intermitting the receiving packets in response to a reception control signal, and a controller (16) for generating the transmission control signal and the reception control signal based on timings of the transmitting packet and the receiving packet, a relationship between the transmitting packet and a corresponding receiving packet which is looped back from the U-shaped optical bus, and a collision notification. The serial-parallel converter notifies a collision on the common bus based on an impedance of the common bus by supplying the collision notification to the controller.

25

#### BACKGROUND OF THE INVENTION

The present invention generally relates to optical transceivers, and more particularly to an optical transceiver which uses a U-shaped optical bus as its transmission line and carries out a control dependent on packet collision in a local area network (LAN) which employs carrier sense multiple access with collision detection (CSMA/CD).

The LAN which uses the U-shaped optical bus as its transmission line is virtually unaffected by external noise when compared to the conventional system which uses a metal cable as its transmission line. In addition, the restrictions on the design of the LAN system is relatively small.

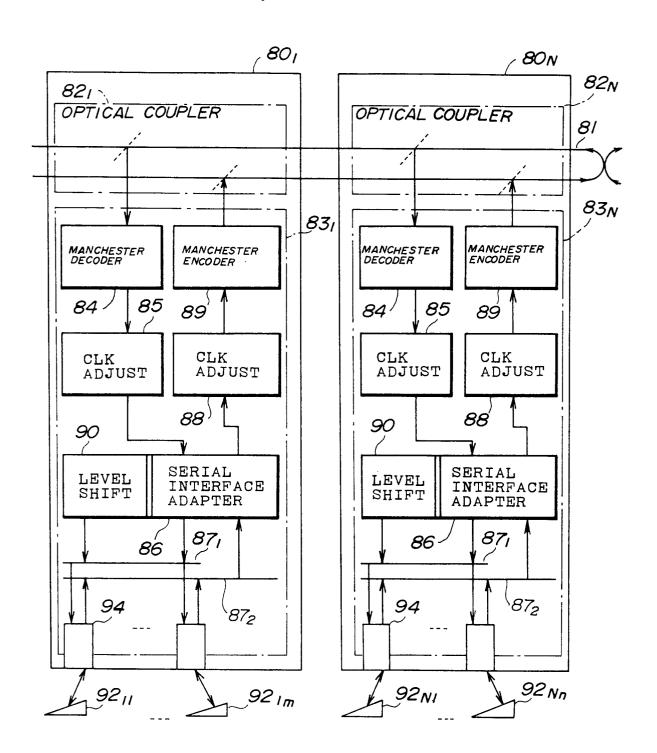

FIG.1 shows an example of a conventional LAN which uses the U-shaped optical bus as its transmission line and employs the CSMA/CD. In FIG.1, a plurality of optical transceivers  $80_1$  through  $80_N$  are arranged on a U-shaped optical bus 81. Each optical transceiver  $80_i$  is made up of a photocoupler  $82_i$  for making a photo-electric conversion in correspondence with the going and returning paths of the optical bus 81, and a coder/decoder part  $83_i$  which codes and decodes the electric signal, where i=1 to N.

In each coder/decoder part  $83_i$ , an output of the photocoupler  $82_i$  which is provided in the going path of the optical bus 81 is coupled to a receiving internal bus  $87_1$  via a Manchester decoder 84, a clock adjusting circuit 85 and one channel of a serial interface adapter 86. The Manchester decoder 84 decodes a Manchester code included in an output signal of the photocoupler  $82_i$  which is provided in the going path of the optical bus 81 into an non-return-to-zero (NRZ) signal. The clock adjusting circuit 85 absorbs the difference in the accuracies of a clock in the optical bus 81 and a clock within the coder/decoder part  $83_i$ .

In addition, in each coder/decoder part 83i, a transmitting internal bus 872 which forms a pair with the receiving internal bus 871 is coupled to a clock adjusting circuit 88 via another channel of the serial interface adapter 86. An output of the clock adjusting circuit 88 is coupled to an input of the photocoupler 82; which is provided in the returning path of the optical bus 81, via a Manchester encoder 89 which codes the NRZ signal into the Manchester code. On the other hand, the receiving internal bus 87<sub>1</sub> is coupled to a level shift circuit 90 which notifies a packet collision generated on the optical bus 81 to each data terminal by shifting the level at the receiving internal bus 871. The internal buses 87<sub>1</sub> and 87<sub>2</sub> are coupled to each data terminal 92 via an AUI cable prescribed under ISO8802-3 and a transceiver module 94.

In the conventional LAN described above, packets which are simultaneously transmitted from

a plurality of optical transceivers may collide on the optical bus 81. However, in each of the coder/decoder parts  $83_1$  through  $83_N$ , two internal buses  $87_1$  and  $87_2$  are provided in order to avoid data collision on the internal bus, and the level shift circuit 90 is provided to notify the packet collision generated on the optical bus 81 to each data terminal. For this reason, there is a problem in that the hardware scale is large in the conventional LAN.

## SUMMARY OF THE INVENTION

Accordingly, it is a general object of the present invention to provide a novel and useful optical transceiver in which the problem described above is eliminated.

Another and more specific object of the present invention is to provide an optical transceiver which is coupled to a U-shaped optical bus and to data terminals employing carrier sense multiple access with collision detection (CSMA/CD), comprising serial-parallel converting means for carrying out a conversion between data to and from the data terminals and transmitting packets to be transmitted from and receiving packets to be received by the data terminals via the serial-parallel converting means, optical bus interface means for matching the transmitting and receiving packets to the U-shaped optical bus which is used as a transmission line, a common bus which provides a data transfer path between the serial-parallel converting means and the data terminals during transmitting and receiving operations, transmitting packet intermission means, coupled between the optical interface means and the serial-parallel converting means, for intermitting the transmitting packets in response to a transmission control signal, receiving packet intermission means, coupled between the optical interface means and the serial-parallel converting means, for intermitting the receiving packets in response to a reception control signal, and control means, coupled between the optical interface means and the serial-parallel converting means, for generating the transmission control signal and the reception control signal based on timings of the transmitting packet and the receiving packet, a relationship between the transmitting packet and a corresponding receiving packet which is looped back from the U-shaped optical bus, and a collision notification, where the serial-parallel converting means includes notifying means for notifying a collision on the common bus based on an impedance of the common bus by supplying the collision notification to the control means. According to the optical transceiver of the present invention, it is unnecessary to provide a level shift circuit, and the common bus is used in common

50

during the transmitting and receiving operations. As a result, the hardware scale of the optical transceiver is effectively reduced compared to that of the conventional optical transceiver, and the optical transceiver according to the present invention is suited for production in the form of an LSI.

Other objects and further features of the present invention will be apparent from the following detailed description when read in conjunction with the accompanying drawings.

#### BRIEF DESCRIPTION OF THE DRAWINGS

FIG.1 is a system block diagram showing an example of a conventional LAN;

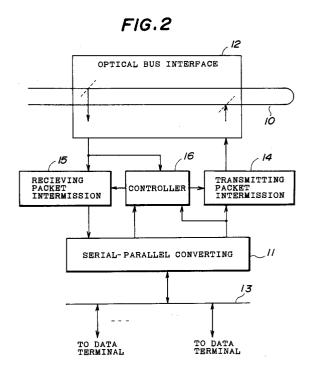

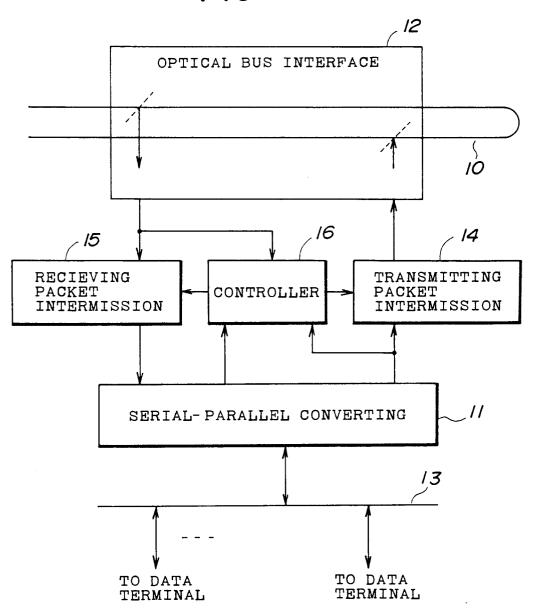

FIG.2 is a system block diagram for explaining an operating principle of an optical transceiver according to the present invention;

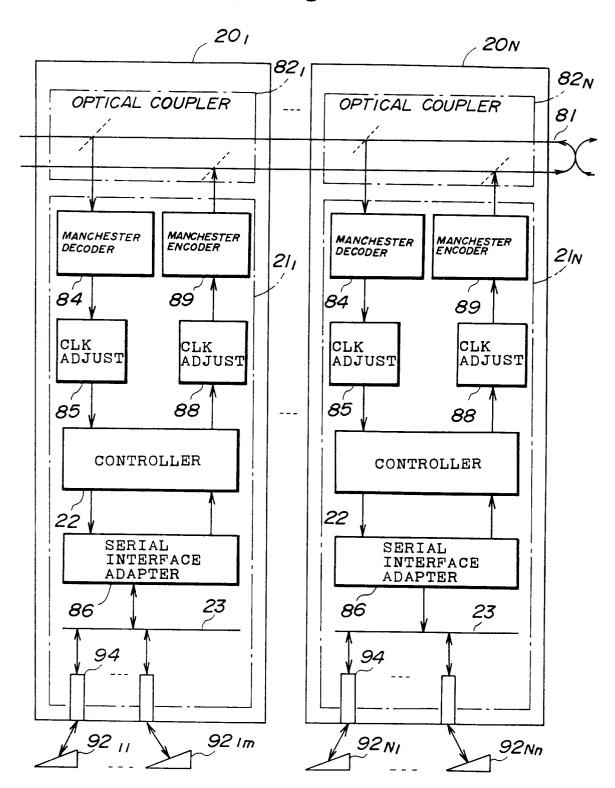

FIG.3 is a system block diagram showing an embodiment of the optical transceiver according to the present invention;

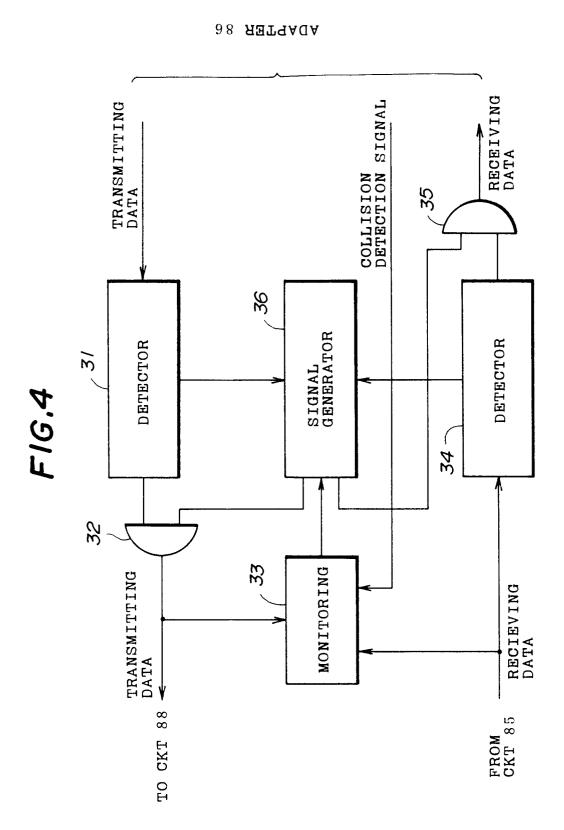

FIG.4 is a system block diagram showing an embodiment of a transmitter/receiver controller of the optical transceiver shown in FIG.3;

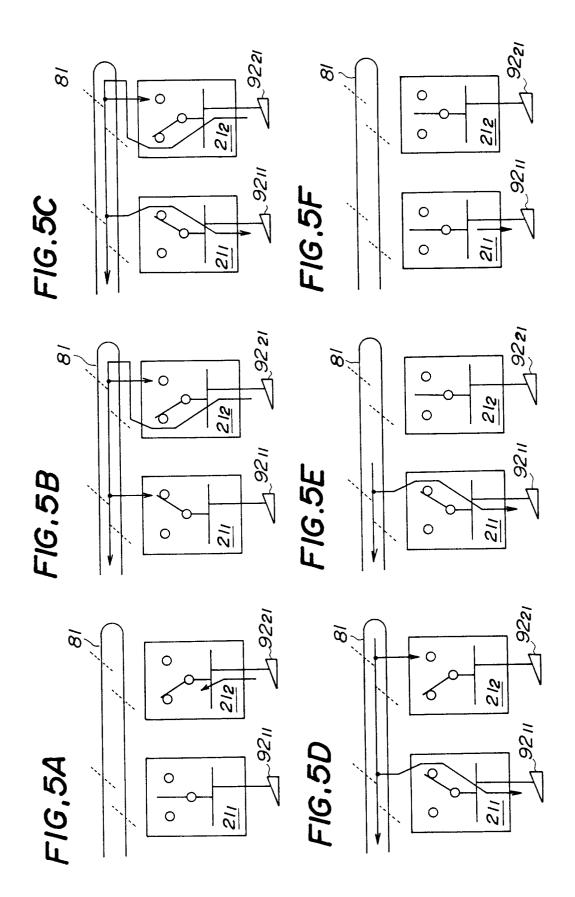

FIGS.5A through 5F are diagrams for explaining a transmitting/receiving operation of the embodiment when no collision is generated;

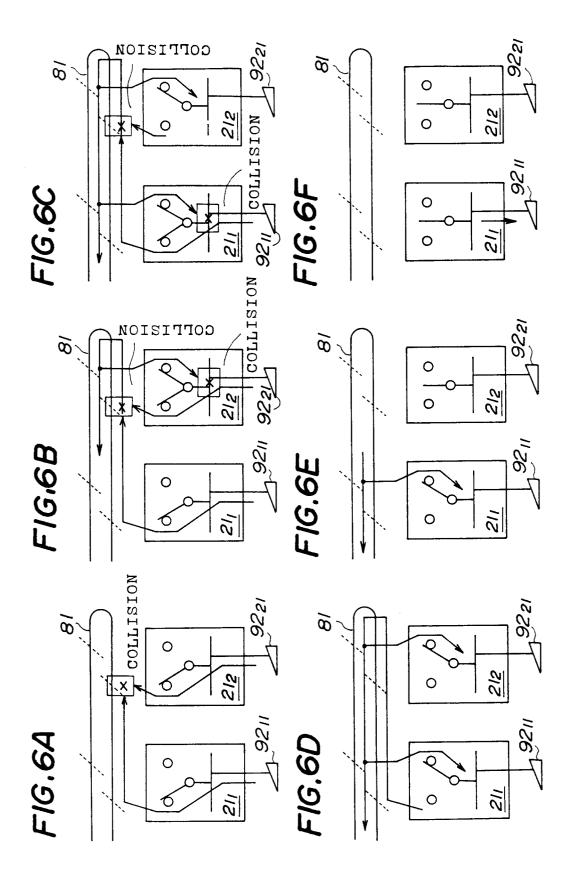

FIGS.6A through 6F are diagrams for explaining an operation of the embodiment when a collision is generated on an optical bus;

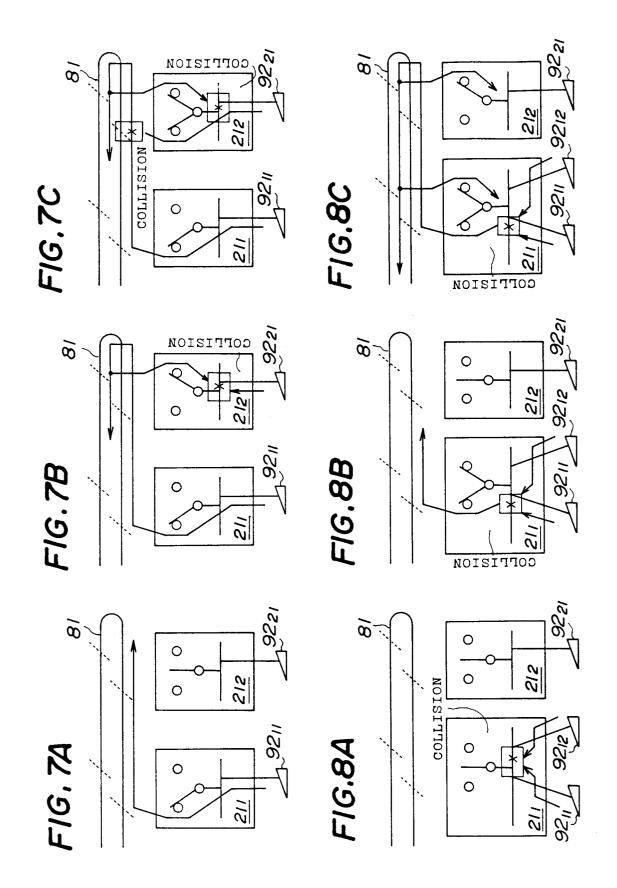

FIGS.7A through 7C are diagrams for explaining an operation of the embodiment when a collision is generated on a common bus; and

FIGS.8A through 8C are diagrams for explaining an operation of the embodiment when a collision is generated on the common bus due to simultaneous transmission from a plurality of data terminals.

### DESCRIPTION OF THE PREFERRED EMBODI-MENTS

First, a description will be given of an operating principle of an optical transceiver according to the present invention, by referring to FIG.2.

In FIG.2, a serial-parallel converter 11 converts receiving packets into data to be received by a data terminal (not shown) which employs the CSMA/CD and converts data transmitted from the data terminal into transmitting packets. An optical bus interface 12 adjusts a U-shaped optical bus 10 which is used as the transmission line to the transmitting and receiving packets. A common bus 13 functions as a data transfer line between the data terminal and the serial-parallel converter 11 when carrying out transmitting and receiving operations.

A transmitting packet intermission part 14 intermits the transmitting packets in response to a

transmission control signal. A receiving packet intermission part 15 intermits the receiving packets in response to a reception control signal. A controller 16 generates the transmission control signal and the reception control signal based on the timings of the transmitting and receiving packets, the relationship between the transmitting packet and the corresponding receiving packet which is looped back by the U-shaped optical bus 10 and a notification regarding a collision on the common bus 13. The serial-parallel converter 11 sends the notification regarding the collision on the common bus 13 based on the impedance of the common bus 13.

During the transmitting operation, the serialparallel converter 11 converts the data which is received from the data terminal via the common bus 13 into transmitting packets. The controller 16 detects the head of the transmitting packet and transmits the transmission control signal. The transmitting packet intermission part 14 supplies the transmitting packets received via the serial-parallel converter 11 to the optical bus interface 12 in response to the transmission control signal. The optical bus interface 12 matches the transmitting packets to the U-shaped optical bus 10 which is used as the transmission line, and transmits the transmitting packets to the U-shaped optical bus 10. In addition, the controller 16 maintains the transmission control signal as it is when the transmitting packet which is transmitted matches the corresponding receiving packet which is looped back and received from the U-shaped optical bus 10. Furthermore, when the controller 16 detects a tail of the transmitting packet, the controller 16 stops generating the transmission control signal so that the transmitting packet intermission part 14 returns to the original state before the start of the transmission.

On the other hand, during the receiving operation, the receiving packets received from the Ushaped optical bus 10 are supplied to the controller 16 via the optical bus interface 12. The controller 16 transmits the reception control signal when a head of the receiving packet is detected. The receiving packet intermission part 15 supplies the receiving packets to the serial-parallel converter 11 in response to the reception control signal. The serial-parallel converter 11 converts the receiving packets into a predetermined data, and the predetermined data is supplied to the data terminal via the common bus 13. Furthermore, the controller 16 stops generating the reception control signal when a tail of the receiving packet is detected so that the receiving packet intermission part 15 returns to the original state before the start of the reception.

Accordingly, during the transmitting and receiving operations in which no packet collision is gen-

55

40

15

25

30

35

40

50

55

erated, the controller 16 activates one of the transmitting packet intermission part 14 and the receiving packet intermission part 15 depending on the timing difference between the transmitting packet and the receiving packet.

The controller 16 recognizes a packet collision on the U-shaped optical bus 10 when the controller 16 detects that the transmitting packet and the corresponding receiving packet looped back from the U-shaped optical bus 10 differ during the transmitting operation. In this case, the controller 16 generates the reception control signal to activate the receiving packet intermission part 15. Since the serial-parallel converter 11 supplies the data to the common bus 13 depending on the receiving packet which is received via the receiving packet intermission part 15, a collision is generated on the common bus 13 between the data from the serialparallel converter 11 and the data from the data terminal. On the other hand, the data terminal transmits a jam signal responsive to this collision on the common bus 13, and the other optical transceivers which are located on the other side of the U-shaped optical bus 10 similarly transmit a iam signal to the U-shaped optical bus 10. The controller 16 stops generating the transmission control signal when a tail of the jam signal which is transmitted from the data terminal is detected, and stops generating the reception control signal when a tail of the jam signal which is received from the U-shaped optical bus 10 is detected. The transmitting packet intermission part 14 and the receiving packet intermission part 15 are thus respectively returned to the original states before the start of the transmission.

On the other hand, when the data terminal starts the transmitting operation after the receiving packet intermission part 15 is activated depending on the receiving packet which is received from the U-shaped optical bus 10, a collision is generated on the common bus 13 between the data from the data terminal and the data from the serial-parallel converter 11. The serial-parallel converter 11 transmits a common bus collision notification which notifies a collision on the common bus 13, depending on the impedance of the common bus 13 at the time when such a collision occurs. The controller 16 activates the transmitting packet intermission part 14 in response to the common bus collision notification, and thus, a packet collision is generated on the U-shaped optical bus 10. The data terminal transmits a jam signal depending on the collision on the common bus 13. Thereafter, the transmitting packet intermission part 14 and the receiving packet intermission part 15 are respectively returned to the original states before the start of the transmission under the control of the controller 16, according to a procedure similar to that used when a collision is generated on the common bus 13 after a packet collision is generated on the U-shaped optical bus 10.

In addition, when a plurality of data terminals arranged on the common bus 13 start the transmitting operations simultaneously, a collision is generated on the common bus 13 among the data from the data terminals. The serial-parallel converter 11 transmits a common bus collision notification depending on the impedance of the common bus 13 at the time when such a collision occurs. The controller 16 activates the transmitting packet intermission part 14 and the receiving packet intermission part 15 simultaneously in response to the common bus collision notification, and thus, a packet collision is generated on the U-shaped optical bus 10. On the other hand, each data terminal transmits a jam signal depending on the collision generated on the common bus 13. Thereafter, the parts of the optical transceiver return to the original states before the start of the transmission according to a procedure similar to that described above.

Therefore, according to the present invention, the optical transceiver uses the common bus 13 which is used in common for the transmitting and receiving operations, and there is no need to provide a level shift circuit as in the case of the conventional optical transceiver shown in FIG.1.

Next, a description will be given of an embodiment of the optical transceiver according to the present invention, by referring to FIG.3. In FIG.3, those parts which are the same as those corresponding parts in FIG.1 are designated by the same reference numerals, and a description thereof will be omitted.

In FIG.3, optical transceivers 20<sub>1</sub> through 20<sub>N</sub> are provided in place of the optical transceivers through 80<sub>N</sub> shown in FIG.1, and coder/decoder parts 21<sub>1</sub> through 21<sub>N</sub> are provided in place of the coder/decoder parts 831 through 83<sub>N</sub> shown in FIG.1. In addition, in FIG.3, each coder/decoder part 21i is characterized in that a transmitter/receiver controller 22 is arranged between the serial interface adapter 86 and the clock adjusting circuits 85 and 88, and that a common bus 23 which is used in common for the transmitting and receiving operation is provided in place of the internal buses 87<sub>1</sub> and 87<sub>2</sub> shown in FIG.1. Furthermore, each coder/decoder part 21, does not include the level shift circuit 90 shown in FIG.1.

For example, the serial interface adapter 86 may be realized using an LSI AM7992B manufactured by AMD and an LSI ULA022 manufactured by TDK. In addition, the transceiver module 94 may be realized using an LSI ULA020 manufactured by TDK.

FIG.4 shows an embodiment of the transmitter/receiver controller 22 shown in FIG.3. In

FIG.4, a transmitting data (packet) which is received from the serial interface adapter 86 is supplied to one input terminal of a transmission switch part (AND gate) 32 via a transmitting data detector 31. An output of the transmitting switch part 32 is supplied to a first input terminal of a transmission/reception monitoring part 33 and the clock adjusting circuit 88. A receiving data (packet) which is received from the clock adjusting circuit 85 is supplied to a second input terminal of the transmission/reception monitoring part 33, and to one input terminal of a receiving switch part (AND gate) 35 via a receiving data detector 34. An output of the receiving switch part 35 is supplied to the serial interface adapter 86. The transmitting data detector 31 supplies to a transmission/reception select signal generator 36 a signal which indicates head and tail of the transmitting data, while the receiving data detector 34 supplies to the transmission/reception select signal generator 36 a signal which indicates head and tail of the receiving data. The transmission/reception select signal generator 36 generates a transmission select signal and a reception select signal based on the timings of the signals which are respectively received from the transmitting data detector 31 and the receiving data detector 34. The transmission select signal is supplied to the other input terminal of the transmitting switch part 32, while the reception select signal is supplied to the other input terminal of the receiving switch part 35. A collision detection signal which is output from the serial interface adapter 86 is supplied to a third input terminal of the transmission/reception monitoring part 33. An output of the transmission/reception monitoring part 33 is supplied to the transmission select signal generator 36.

In this embodiment, the photocoupler 821, the Manchester decoder 84, the Manchester encoder 89 and the clock adjusting circuits 85 and 88 correspond to the optical interface 12 shown in FIG.2. The transmitting switch part 32 corresponds to the transmitting packet intermission part 14 shown in FIG.2, and the receiving switch part 35 corresponds to the receiving packet intermission part 15 shown in FIG.2. The transmitting data detector 31, the transmission/reception monitoring part 33, the receiving data detector 34 and the transmission/reception select signal generator 36 corresponds to the controller 16 shown in FIG.2. Further, the serial interface adapter 86 corresponds to the serial-parallel converter 11 shown in FIG.2, and the common bus 23 corresponds to the common bus 13 shown in FIG.2.

Next, a description will be given of this embodiment of the optical transceiver, by referring to FIGS.5 through 8.

FIGS.5A through 5F are diagrams for explain-

ing the transmitting and receiving operations of this embodiment when no collision is generated.

8

In the coder/decoder parts 211 and 212, the signals passing through the transmitting switch part 32 and the receiving switch part 35 are intermittently controlled by the transmission/reception select signal generator 36 of the transmitter/receiver controller 22. However, for the sake of convenience, FIGS.5A through 5F show the states of the transmitting switch part 32 and the receiving switch part 35 in a simplified manner, that is, as connection states of the common bus 23 and the Ushaped optical bus 81. Such illustrations of the states of the transmitting switch part 32 and the receiving switch part 35 are also employed in FIGS.6 through 8 which will be described later.

When a data terminal 9221 transmits a transmitting data (packet) in a state where all of the optical transceivers arranged on the U-shaped optical bus 81 are not transmitting, transmission/reception select signal generator 36 of the coder/decoder part 212 activates, that is, turns ON, the transmitting switch part 32 as shown in FIG.5A when the head of this transmitting data is detected. In addition, the transmission/reception monitoring part 33 enters the transmitting data on the U-shaped optical bus 81 via the photocoupler 822, and confirms that no packet collision is generated on the U-shaped optical bus 81 by collating the contents of the entered transmitting data with those of the transmitting data.

On the other hand, at the coder/decoder part 211, the transmission/reception select signal generator 36 activates, that is, turns ON, the receiving switch part 35 when the head of a receiving data (packet) is detected as shown in FIG.5B, and supplies the receiving data to a data terminal 9211 as shown in FIG.5C.

When the transmitting data detector 31 detects the tail (transmission complete) of the transmitting data, the transmitting switch part is deactivated, that is, turned OFF, as shown in FIGS.5D and 5E. In addition, at the coder/decoder part 211, the receiving switch part 35 is deactivated, that is, turned OFF, when the receiving data detector 34 detects the tail (reception complete) of the receiving data as shown in FIG.5F. As a result, the transmitting and receiving operation with respect to a single data (packet) is completed.

FIGS.6A through 6F are diagrams for explaining the operation of this embodiment when a collision is generated on the U-shaped optical bus 81.

The transmission/reception monitoring part 33 of each optical transceiver stores 512 bits including an address field of the transmitting data (packet) into a memory (not shown) when carrying out the transmitting operation. The transmission/reception monitoring part 33 enters the transmitting data on

50

15

25

30

35

40

50

55

the U-shaped optical bus 81 via the photocoupler 82<sub>i</sub>, and detects a data error by comparing the entered transmitting data and the transmitting data stored in the memory bit by bit. The detection of the data error corresponds to the detection of the packet collision on the U-shaped optical bus 81.

In other words, when the transmitting data from the coder/decoder parts 21<sub>1</sub> and 21<sub>2</sub> collide on the U-shaped optical bus 81 as shown in FIG.6A, the transmission/reception monitoring part 33 of each of the coder/decoder parts 21<sub>1</sub> and 21<sub>2</sub> notifies the above comparison result to the corresponding transmission/reception select signal generator 36. The transmission/reception select signal generator 36 turns ON the transmitting switch part 32 and the receiving switch part 35 simultaneously in response to this notification from the transmission/reception monitoring part 33 as shown in FIGS.6B and 6C.

At the coder/decoder parts  $21_1$  and  $21_2$ , the serial interface adapter 86 transmits a predetermined data on the common bus 23 according to such a control operation, and the data from the serial interface adapter 86 and the data from the transmitting data terminal collide on the common bus 23. The data terminals  $92_{11}$  and  $92_{21}$  respectively detect such a collision via the AUI cable and transmit a jam signal during a jam time.

At the coder/decoder parts 21<sub>1</sub> and 21<sub>2</sub>, the transmitting data detector 31 detects the stop of the jam signal transmission and turns OFF the transmitting switch part 32 as shown in FIG.6D. Furthermore, the receiving data detector 34 detects the tail of the jam signal which is received from the optical transceiver which is located on the other side of the U-shaped optical bus 81, and turns OFF the receiving switch part 35 as shown in FIGS.6E and 6E so as to return to the original state before the start of the transmission.

FIGS.7A through 7C are diagrams for explaining the operation of this embodiment when a collision is generated on the common bus 23.

The transmitting data detector 31 of the coder/decoder part 211 detects the head of the transmitting data (packet) and turns ON the transmitting switch part 32 as shown in FIG.7A when the data terminal 92<sub>11</sub> starts transmitting in a state where no optical transceiver makes a transmission. On the other hand, at the coder/decoder part 212, the receiving data detector 34 turns ON the receiving switch part 35 when the receiving data detector 34 detects the head of the receiving data (packet) which corresponds to the above transmitting data. But when the data terminal 9221 simultaneously starts transmitting, the data from the serial interface adapter 86 and the data from the data terminal 9221 collide on the common bus 23 as shown in FIG.7B.

The serial interface adapter 86 detects this

collision on the common bus 23 based on the impedance of the common bus 23, and transmits a detection signal transmission/reception monitoring part 33. The transmission/reception monitoring part 33 supplies predetermined control signal transmission/reception select signal generator 36 in response to this collision detection signal, and the transmission/reception select signal generator 36 turns ON the transmitting switch part 32 in response to this predetermined control signal as shown in FIG.7C. In addition, the data terminal 9221 detects this collision on the common bus 23 and transmits a jam data. As a result, a packet collision is generated on the U-shaped optical bus 81.

10

The coder/decoder part 21<sub>1</sub> recognizes the collision on the common bus 23 in the coder/decoder part 21<sub>2</sub> indirectly from the collision on the U-shaped optical bus 81, and returns to the original state before the start of the transmission according to the procedure described above in conjunction with FIGS.6C through 6F. Furthermore, the coder/decoder part 21<sub>2</sub> returns to the original state before the start of the transmission according to the procedure described above in conjunction with FIGS.6D through 6F.

FIGS.8A through 8C are diagrams for explaining the operation of this embodiment when a collision is generated on the common bus 23 due to simultaneous transmission from a plurality of data terminals.

When the data terminals 92<sub>11</sub> and 92<sub>12</sub> which are coupled to the coder/decoder part 211 simultaneously make transmissions, the data from the data terminals 92<sub>11</sub> and 92<sub>12</sub> collide on the common bus 23 as shown in FIG.8A. The serial interface adapter 86 detects this collision on the common bus 23 and transmits a collision detection signal to the transmission/reception monitoring part 33. The transmission/reception monitoring part 33 supplies predetermined control signal transmission/reception select signal generator 36 in response to this collision detection signal, and the transmission/reception select signal generator 36 turns ON the transmitting switch part 32 and the receiving switch part 35 in response to the predetermined control signal.

On the other hand, the data terminals 92<sub>11</sub> and 92<sub>12</sub> detect this collision on the common bus 23 and transmit jam data as shown in FIGS.8B and 8C. Each optical transceiver returns to the original state before the start of the transmission according to the procedure described above in conjunction with FIGS.6D through 6F according to the transmission end of the jam data.

Therefore, according to this embodiment, the optical transceiver does not require the level shift circuit which was conventionally required to notify

15

20

25

35

the generation of the packet collision on the Ushaped optical bus, and the two internal buses which were conventionally required can be replaced by a single common bus which is used in common for the transmitting and receiving operations.

Of course, by omitting the common bus 23, the transceiver modules 94 and the data terminals 92, and coupling the serial interface adapter 86 to a coaxial cable, the coder/decoder part 21 may be used as a repeater.

Further, the present invention is not limited to these embodiments, but various variations and modifications may be made without departing from the scope of the present invention.

Reference signs in the claims are intended for better understanding and shall not limit the scope.

#### Claims

An optical transceiver which is coupled to a Ushaped optical bus (10) and to data terminals employing carrier sense multiple access with collision detection (CSMA/CD), characterized in that there are provided:

serial-parallel converting means (11) for carrying out a conversion between data to and from the data terminals and transmitting packets to be transmitted from and receiving packets to be received by the data terminals via said serial-parallel converting means;

optical bus interface means (12) for matching the transmitting and receiving packets to the U-shaped optical bus which is used as a transmission line:

a common bus (13) which provides a data transfer path between said serial-parallel converting means and the data terminals during transmitting and receiving operations;

transmitting packet intermission means (14), coupled between said optical bus interface means and said serial-parallel converting means, for intermitting the transmitting packets in response to a transmission control signal;

receiving packet intermission means (15), coupled between said optical bus interface means and said serial-parallel converting means, for intermitting the receiving packets in response to a reception control signal; and

control means (16), coupled between said optical bus interface means and said serial-parallel converting means, for generating the transmission control signal and the reception control signal based on timings of the transmitting packet and the receiving packet, a relationship between the transmitting packet and a corresponding receiving packet which is looped back from the U-shaped optical bus, and a

collision notification,

said serial-parallel converting means including notifying means for notifying a collision on said common bus based on an impedance of said common bus by supplying the collision notification to said control means.

- 2. The optical transceiver as claimed in claim 1, characterized in that, during the transmitting operation, said serial-parallel converting means (11) converts the data which is received from the data terminal via said common bus (13) into the transmitting packets, said control means (16) detects a head of the transmitting packet and transmits the transmission control signal, and said transmitting packet intermission means (14) supplies the transmitting packets received via said serial-parallel converting means to said optical bus interface means (12) in response to the transmission control signal.

- 3. The optical transceiver as claimed in claim 2, characterized in that, during the transmitting operation, said optical bus interface means (12) matches the transmitting packets to the U-shaped optical bus (10) and transmits the transmitting packets to the U-shaped optical bus.

- 4. The optical transceiver as claimed in claim 3, characterized in that, during the transmitting operation, said control means (16) maintains the transmission control signal as it is when the transmitting packet which is transmitted matches the corresponding receiving packet which is looped back and received from the Ushaped optical bus (10).

- 5. The optical transceiver as claimed in claim 4, characterized in that, when the control means (16) detects a tail of the transmitting packet, said control means stops generating the transmission control signal so that said transmitting packet intermission means (14) returns to an original state before a start of the transmitting operation.

- 6. The optical transceiver as claimed in any of claims 1 to 5, characterized in that, during the receiving operation, the receiving packets received from the U-shaped optical bus (10) are supplied to the control means (16) via said optical bus interface means (12), said control means transmits the reception control signal when a head of the receiving packet is detected, said receiving packet intermission means (15) supplies the receiving packets to

50

15

20

25

35

40

45

50

55

said serial-parallel converting means (11) in response to the reception control signal, said serial-parallel converting means converts the receiving packets into a predetermined data, and the predetermined data is supplied to the data terminal via said common bus (13).

- 7. The optical transceiver as claimed in claim 6, characterized in that said control means (16) stops generating the reception control signal when a tail of the receiving packet is detected so that said receiving packet intermission means (15) returns to an original state before a start of the receiving operation.

- 8. The optical transceiver as claimed in any of claims 1 to 7, characterized in that said control means (16) recognizes a packet collision on the U-shaped optical bus (10) when said control means detects that the transmitting packet and the corresponding receiving packet looped back from the U-shaped optical bus differ during the transmitting operation.

- 9. The optical transceiver as claimed in claim 8, characterized in that said control means (16) generates the reception control signal to activate said receiving packet intermission means (15) when said control means recognizes the packet collision on the U-shaped optical bus (10), thereby generating a collision on said common bus (13) between the data from said serial-parallel converting means (11) and the data from the data terminal.

- 10. The optical transceiver as claimed in claim 9, characterized in that the data terminal transmits a jam signal responsive to the collision on said common bus (13) and other optical transceivers which are located on the other side of the U-shaped optical bus similarly transmit a jam signal to the U-shaped optical bus.

- 11. The optical transceiver as claimed in claim 10, characterized in that said control means (16) stops generating the transmission control signal when a tail of the jam signal which is transmitted from the data terminal is detected, and stops generating the reception control signal when a tail of the jam signal which is received from the U-shaped optical bus (10) is detected, thereby returning said transmitting packet intermission means (14) and said receiving packet intermission means (15) to original states before a start of the transmitting operation.

- 12. The optical transceiver as claimed in any of

claims 1 to 11, characterized in that said optical bus interface means (12) includes:

- a photocoupler (82) which is coupled to the U-shaped optical bus (10);

- a Manchester encoder (89), coupled to the photocoupler, for coding the transmitting packets:

- a Manchester decoder (84), coupled to the photocoupler, for decoding the receiving packets: and

clock adjusting means (85, 88), coupled between said control means (16) and the Manchester encoder and decoder, for adjusting a difference in accuracies of a clock on the Ushaped optical bus (10) and a clock within the optical transceiver.

- **13.** The optical transceiver as claimed in any of claims 1 to 12, characterized in that said control means (16) includes:

- a transmitting data detector (31), coupled to said serial-parallel converting means (11), for supplying a signal which indicates head and tail of the transmitting packets;

- a receiving data detector (34), coupled to said serial-parallel converting means, for supplying a signal which indicates head and tail of the receiving packets; and

- a transmission/reception control signal generator (36) for generating the transmission control signal and the reception control signal based on the timings of the signals which are respectively received from the transmitting data detector and the receiving data detector.

- 14. The optical transceiver as claimed in claim 13. characterized in that said control means (16) further includes a transmission/reception monitoring part (33), coupled to said optical bus interface means (12), for monitoring the transmitting and receiving packets, transmission/reception monitoring part supplying control signal said transmission/reception control signal generator (36) in response to the collision notification from said serial-parallel converting means (11).

# FIG. I PRIOR ART

FIG.2

FIG.3

## EUROPEAN SEARCH REPORT

EP 91 11 5004

| DOCUMENTS CONSIDERED TO BE RELEVANT |                                                                                                                                                                                                |                                                   |                                                               |                                                  |

|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|---------------------------------------------------------------|--------------------------------------------------|

| Category                            |                                                                                                                                                                                                | h indication, where appropriate,<br>vant passages | Relevant<br>to claim                                          | CLASSIFICATION OF THE<br>APPLICATION (Int. CI.5) |

| Υ                                   | EP-A-0 224 132 (FUJITSU<br>* Claims 1-6; figures 4-6; cc<br>10 *                                                                                                                               | )<br>Iumn 6, line 55 - column 7, line             | 1,8                                                           | H 04 L 12/28<br>H 04 B 10/14                     |

| Α                                   |                                                                                                                                                                                                |                                                   | 2-7,9-14                                                      |                                                  |

| Υ                                   | US-A-4 751 700 (ULUG)  * Claim 1; figures 1,2; column 3, lines 9-35 *                                                                                                                          |                                                   | 1,8                                                           |                                                  |

| Α                                   | US-A-4 476 467 (TERWILLIGER et al.) * Abstract; claims 1-4; figure 1 *                                                                                                                         |                                                   | 1,8                                                           |                                                  |

| Α                                   | EP-A-0 170 208 (FUJITSU<br>* Figure 12; column 9, lines<br>                                                                                                                                    | ·-·                                               | 12                                                            |                                                  |

|                                     |                                                                                                                                                                                                |                                                   |                                                               |                                                  |

|                                     |                                                                                                                                                                                                |                                                   |                                                               | TECHNICAL FIELDS<br>SEARCHED (Int. CI.5)         |

|                                     |                                                                                                                                                                                                |                                                   |                                                               | H 04 L<br>H 04 B                                 |

|                                     |                                                                                                                                                                                                |                                                   |                                                               |                                                  |

|                                     |                                                                                                                                                                                                |                                                   |                                                               |                                                  |

|                                     |                                                                                                                                                                                                |                                                   |                                                               |                                                  |

|                                     |                                                                                                                                                                                                |                                                   |                                                               |                                                  |

|                                     |                                                                                                                                                                                                |                                                   |                                                               |                                                  |

|                                     | The present search report has I                                                                                                                                                                | peen drawn up for all claims                      |                                                               |                                                  |

|                                     | Place of search                                                                                                                                                                                | Date of completion of search                      | ·                                                             | Examiner                                         |

|                                     | The Hague                                                                                                                                                                                      | 02 December 91                                    |                                                               | ALI A.                                           |

| Y :<br>A :                          | CATEGORY OF CITED DOCL<br>particularly relevant if taken alone<br>particularly relevant if combined wit<br>document of the same catagory<br>technological background<br>non-written disclosure | h another D: d<br>L: d                            | he filing date<br>locument cited in the<br>locument cited for | other reasons                                    |