(1) Veröffentlichungsnummer: 0 477 165 A2

## (2) EUROPÄISCHE PATENTANMELDUNG

(21) Anmeldenummer: 91890211.5

(51) Int. CI.<sup>5</sup>: H02H 9/02

(22) Anmeldetag: 16.09.91

(30) Priorität: 19.09.90 AT 1903/90

(43) Veröffentlichungstag der Anmeldung : 25.03.92 Patentblatt 92/13

84) Benannte Vertragsstaaten : AT DE FR GB IT

71 Anmelder: E.Z.I. ENTWICKLUNGSZENTRUM FÜR INDUSTRIEELEKTRONIK GESELLSCHAFT m.b.H. Gemeindeweg 3 A-9523 Villach Landskron (Kärnten) (AT) © Erfinder : Tüü, Miklos Szabadsag U. 40 H-9082 Nuül (HU)

Erfinder : Simcic, Christian

Finkenweg 4

A-9582 Lastschach (Kärnten) (AT)

(74) Vertreter: Beer, Manfred, Dipl.-Ing. et al Lindengasse 8 A-1070 Wien (AT)

## (54) Strombegrenzungsschaltung.

Die Regeleinrichtng (1) einer Strombegrenzungsschaltung weist in einem parallel zur Versorgungsspannungsquelle (U) liegenden Zweig (3) eine über einen Referenzspannungseingang (U<sub>ref</sub>) gesteuerte Referenzstromquelle (4) und eine dazu in Serie liegende rückgekoppelte Stromquelle (5) auf. Ein Stellglied (2) weist zumindest zwei parallel geschaltete Laststromquellen (6) auf, die in Serie zur Last (R) angeordnet sind und an denen die von der rückgekoppelten Stromquelle (5) bereitgestellte Referenzspannung (U<sub>G</sub>) liegt. Entsprchend der Anzahl (n) der ausgangsseitig parallel geschalteten Laststromquellen (6) ist der Ausgangsstrom um das (n+1)fache größer als der von der Referenzstromquelle gelieferte Referenzstrom (I<sub>ref</sub>), wobei die Reaktionszeit nur von der Schaltschnelligkeit einer der parallel geschalteten Stromquellen (5, 6) bestimmt ist.

5

10

20

25

35

40

45

50

55

Die Erfidung betrifft eine Strombegrenzungsschaltung für eine an einer Versorgungsspannungsquelle liegende Last, mit einer Regeleinrichtung, welche über ein Stellglied den Laststrom beeinflußt.

Derartige Strombegrenzungsschaltungen, bzw. auch zumindest vom Aufbau her weitgehend ähnliche Konstantstromquellen, sind bekannnt und bisher üblicherweise in Form eines Regelkreises aufgebaut. In Serie zur Last, bzw. zu dem diese wirkungsmäßig darstellenden Lastwiderstand, ist ein Meßwiderstand eingesetzt, an dem der Laststrom einen Spannungsabfall verursacht. Dieser Spannungsabfall wird einem Regelverstärker zugefürht, dessen Ausgang über ein wiederum in Serie zur Last liegendes Stellglied den Laststrom beeinflußt. Die wesentlichen Nachteile dieser bekannten Anordnung sind, daß über den Meßwiderstand der gesamte Laststrom fließt, was insbesondere bei größeren Strömen zu unerwünscht hoher Verlustleistung führt, daß weiters die Reaktionszeiten des Regelverstärkers und des Stellgliedes sich summieren, und daß schließlich der Meßwiderstand nicht in einen Schaltungsbaustein integrierbar ist.

Zumindest der erste der oben genannten Nachteile kann bei einer unter dem Namen "SENSFET" bekannt gewordenen Ausgestaltung des genannten Grundprinzips vermieden werden, bei welcher durch entsprechende Aufteilung der über den Meßwiderstand fließende Strom sehr viel kleiner (etwa um den Faktor 1000) als der Laststrom ist. Zufolge des nach wie vor vorhandenen separaten Regelverstärkers samt Stellglied bleibt jedoch das nachteilige Zeitverhalten der Gesamtanordnung.

Aufgabe der vorliegenden Erfingung ist es, eine Strombegrenzungschaltung der eingangs genannten Art so zu verbessern, daß die genannten Nachteile vermieden werden und daß insbesonders auch bei großen Strömen (typischerweise größer 5 A) kleine Reaktionszeiten (typischerweise unter 20 nSek) ermöglicht werden. Weiters soll eine gute Steuerbarkeit der Strombegrenzung ohne Regelschwingungen erzielt werden.

Dies wird gemäß der vorliegenden Erfindung dadurch erreicht, daß die Regeleinrichtung in einem parallel zur Versorgungsspannungsquelle liegenden Zweig eine über einen Referenzspannungseingang gesteuerte Referenzstromquelle und eine dazu in Serie liegende rückgekoppelte Stromquelle aufweist und daß das Stellglied zumindest zwei parall geschaltete Laststromquellen aufweist, die in Serie zur Last angeordnet sind und an denen die von der rückgekoppelten Stromquelle bereitgestellte Referenzspannung liegt. Am Stromkreiseingang befindet sich also die Referenzstromquelle, die über den Referenzspannungseingang steuerbar ist und damit die Strombegrenzung der Last steuert. Diese Referenzstromquelle versorgt die rückgekoppelte Stromquelle, wodurch die Referenzspannung eine Funktion einer festliegenden, entsprechenden inneren Eigenschaft der rückgekoppelten Stromquelle (beispielsweise der Transkonduktion des weiter unten als Ausgestaltung angesprochenen MOS-FETs) und des Eingangsstromes ist. Diese Referenzspannung wird an das Stellglied gelegt, welches zumindest zwei parallel geschaltete Laststromguellen aufweist, die in Serie zur Last angeordnet sind. Damit ist der Ausgangsstrom (n+1)mal größer als der Referenzstrom, weil ausgangsseitig beliebig viele (n) Laststromguellen parallel geschaltet sind. Es lassen sich damit Reaktionszeiten kleiner als 20 nSek erzielen, was sich aus dem Umstand ergibt, daß die Strombegrenzung in allen Stromquellen (beispielsweise Elektronenröhren oder MOS-FETs) parallel erfolgt und damit die Schnelligkeit eines derartigen Elementes die Schaltschnelligkeit des gesamten Stromkreises bestimmt.

Nach einer besonders bevorzugten Ausgestaltung der Erfindung ist vorgesehen, daß zumindest die rückgekoppelte Stromquelle und die Laststromquellen MOS-FETs aufweisen, deren GATE- und DRAIN-Anschluß jeweils miteinander verbunden sind. Auf diese Weise ergibt sich einerseits auf einfachste Art eine Integrierbarkeit der gesamten Schaltung, wobei sowohl P-Kanal als auch N-Kanal Ausführung möglich ist. Die innere Rückkopplung in den MOS-FETs ersetzt dabei quasi den früher gebräuchlichen äußeren Regelkreis, was extrem kurze Reaktionszeiten bei einfachstem Aufbau sicherstellt.

In weiterer Ausgestaltung der Erfindung kann zur Erzielung von noch kürzeren Reaktionszeiten vorgesehen werden, daß die Millerkapazität (entspricht einer Vergrößerung der Kollektor-Basis-Kapazität unter der Wirkung der Spannungsverstärkung der Schaltung) der MOS-FETs der Stromquellen durch eine einschaltbare Parallelimpedanz kompensiert ist. Damit wurden in experimentellen Schaltungsaufbauten bereits Reaktionszeiten im Bereich von 5 nSek erzielt.

Als mögliche Anwendungsbereiche der erfindungsgemäßen Strombegrenzungsschaltung sind beispielsweise Leistungsstufen, Analogtester, Meßgeräte oder Stromversorgungen zu nennen.

Der überdeckbare Strom- bzw. Spannungsbereich ist im wesentlichen nur abhängig von den verfügbaren Stromquellen (beispielsweise sogenannte "SIPMOS"-Transistoren). In allen Fällen ist ein schwingungsfreier Übergang in den Strombegrenzungsbetrieb sichergestellt.

Die Erfindung wird im folgenden noch an Wand der in der Zeichnung teilweise schematisch dargestellten Schaltungsbilder näher erläutert.

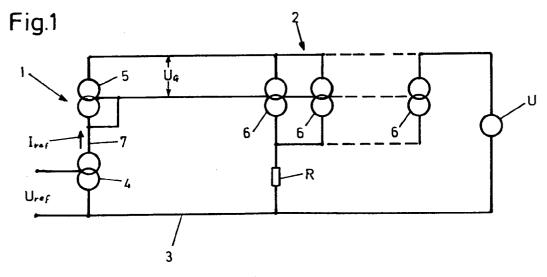

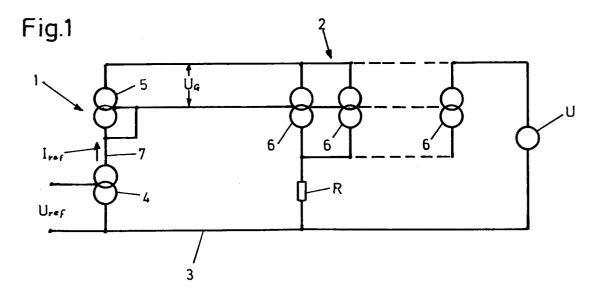

- Fig. 1 zeigt dabei ein Grundsatzschaltbild einer erfindungsgemäßen Strombegrenzungsschaltung,

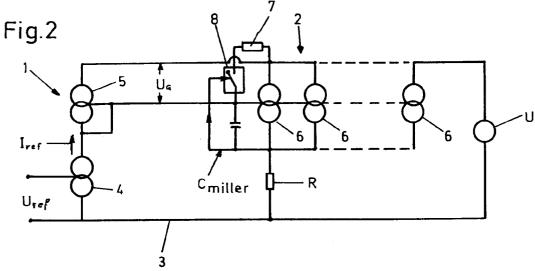

- Fig. 2 eine der Fig. 1 entsprechende Anordnung mit Kompensation der Millerkapazität und

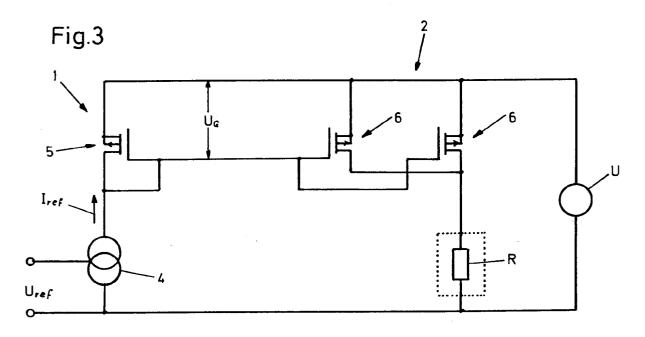

- Fig. 3 ein weiteres Beispiel der erfindungsgemäßen Strombegrenzungsschaltung mit MOS-FETs.

Gemäß Fig. 1 ist eine Strombegrenzungsschaltung für eine an einer Versorgungsspannungsquelle U lie-

gende Last (hier als Lastwiderstand R eingezeichnet) mit einer allgemein mit 1 bezeichneten Regeleinrichtung ausgestattet, welche über ein allgemein mit 2 bezeichnetes Stellglied den Laststrom beeinflußt. Die Regeleinrichtung 1 weist in einem parallel zur Versorgungsspannungsquelle U liegenden Zweig 3 eine über einen Referenzpannungseingang  $U_{ref}$  gesteuerte Referenzstromquelle 4 und eine dazu in Serie liegende rückgekoppelte Stromquelle 5 auf. Das Stellglied 2 seinerseits weist zumindest zwei parallel geschaltete Laststromquellen 6 auf, die in Serie zur Last R angeordnet sind und an denen die von der rückgekoppelten Stromquelle bereitgestellte Referenzspannung  $U_G$  liegt.

Die über den Steuereingang bzw. Referenzspannungseingang  $U_{ref}$  gesteuerte Referenzstromquelle 4 liefert über die Leitung 7 den Referenzstrom  $I_{ref}$  an die rückgekoppelte Stromquelle 5. Der an dieser entstehende Spannungsabfall ist eine Funktion einer ihrer festliegenden inneren Eigenschaften und des Eingangsstromes. Die so gewonnene Referenzspannung UG wird an die parallel liegenden Laststromquellen 6 gelegt, womit der Ausgangsstrom schließlich um das (n+1)fache - wobei n die Anzahl der Laststromquellen 6 ist - größer als der Referenzstrom  $I_{ref}$  ist.

Die Strombegrenzungssschaltung nach Fig. 2 unterscheidet sich von der nach Fig. 1 nur durch die hier schematisch eingetragene Kompensation der Millerkapazität der Laststromquellen 6 (beispielsweise MOS-FETs) durch eine über einen angedeuteten Schalter 8 einschaltbare Parallelimpetanz Z, womit die Reaktionszeit der Schaltung auf Stromschwankungen weiter verringert werden kann. Der Schalter 8 kann beispielsweise ebenfalls von einem entsprechend beschaltetem MOS-FET gebildet sein - die Parallelimpetanz Z kann im einfachsten Falle durch einen entsprechend dimensionierten Kondensator realisiert sein. Als wesentlich ist in diesem Zusammenhang anzusehen, daß über den Schalter 8 eine gewisse Verzögerung des Ansprechens der Kompensation erreicht wird, die typisch in der Gegend von 5 nSek liegen soll.

Gemäß Fig. 3 ist die Strombegrenzungsschaltung wieder ähnlich zu Fig. 1 aufgebaut, wobei hier nun aber die rückgekoppelte Stromquelle 5 und die beiden Laststromquellen 6 von MOS-FETs gebildet sind, deren GATE- und DRAIN-Anschlüsse jeweils miteinander verbunden sind. Damit läßt sich die gesamte Schaltungsanordnung sehr leicht integrieren, womit erstmals eine derartige Schaltung auf einem einzelnen Baustein vorgesehen werden kann.

Die Referenzstromquelle 4 versorgt hier den B-Kanal MOS-FET der rückgekoppelten Stromquelle 5, dessen DRAIN- und GATE-Elektroden miteinander verbunden sind, mit Referenzstrom. Der an diesem MOS-FET entstehende Spannungsabfall ist eine Funktion seiner Transkonduktion und des Eingangsstromes:  $U_{GD} = G_m \times I_{ref}$ , wobei  $U_{GD}$  die Spannung zwischen GATE und DRAIN,  $G_m$  den Koeffizienten der gesteuerten Einströmung (innere Steilheit) und  $I_{ref}$  den Referenzstrom bedeutet. Die so gewonnene Referenzspannung  $U_G$  wird an die GATE-Elektrode der weiteren MOS-FETs in den Laststromquellen 6 gelegt. Dabei ist der dort zur DRAIN-Elektrode fließende Strom gleich dem im MOS-FET 5 fließenden Referenzstrom, weil  $I_{aus} = G_m \times U_G \times (n+1)$  und weil  $U_G$  der beiden Transistoren 5, 6 gleich ist.

Damit ist der Ausgangsstrom um das (n+1)fache größer als der Referenzstrom I<sub>ref</sub>. Die Linearität der Strombegrenzung ergibt sich dabei aus der Charakteristik der MOS-FETs. Die Temperatur- und zeitunabhängige Drift ist eine Funktion der entsprechenden Technologie. Die geringere Reaktionszeit der Strombegrenzung ergibt sich aus dem Umstand, daß diese in allen Transistoren parallel erfolgt und die Schnelligkeit eines Transistors damit die Schaltschnelligkeit des gesamten Stromkreises bestimmt.

Es kann damit eine extrem schnelle Festkörperstromquelle ohne externen Meßwiderstand realisiert werden, wobei die Strombegrenzung proportional zur Steuerspannung ist und von Null bis zu einer maximalen Stromstärke (abhängig von der Anzahl der Laststromguellen) eingestellt werden kann.

## 45 Patentansprüche

10

20

25

35

40

50

55

- Strombegrenzungsschaltung, für eine an einer Versorgerspannquelle liegende Last, mit einer Regeleinrichtung, welche über ein Stellglied den Laststrom beeinflußt, dadurch gekennzeichnet, daß die Regeleinrichtung (1) in einem parallel zur Versorgungsspannquelle (U) liegenden Zweig (3) eine über einen Referenzspannungseingang (U<sub>ref</sub>) gesteuerte Referenzstromquelle (4) und eine dazu in Serie liegende rückgekoppelte Stromquelle (5) aufweist und daß das Stellglied (2) zumindest zwei parallel geschaltete Laststromquellen (6) aufweist, die in Serie zur Last (R) angeordnet sind und an denen die von der rückgekoppelten Stromquelle (5) bereitgestellte Referenzspannung (U<sub>G</sub>) liegt.

- Strombegrenzungsschaltung nach Anspruch 1, dadurch gekennzeichnet, daß zumindest die rückgekoppelte Stromquelle (5) und die Laststromquellen (6) MOS-FETs aufweisen, deren GATE- und DRAIN-Anschluß jeweils miteinander verbunden sind.

## EP 0 477 165 A2

|    | 3. | Strombegrenzungsschaltung nach Anspruch 2, dadurch gekennzeichnet, daß die Millerkapazität der MOS-FETs der Stromquellen (5, 6) durch eine einschaltbare Parallelimpetanz (Z) kompensiert ist. |

|----|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5  |    |                                                                                                                                                                                                |

| 10 |    |                                                                                                                                                                                                |

| 15 |    |                                                                                                                                                                                                |

| 20 |    |                                                                                                                                                                                                |

| 25 |    |                                                                                                                                                                                                |

| 30 |    |                                                                                                                                                                                                |

| 35 |    |                                                                                                                                                                                                |

| 40 |    |                                                                                                                                                                                                |

| 45 |    |                                                                                                                                                                                                |

| 50 |    |                                                                                                                                                                                                |

| 55 |    |                                                                                                                                                                                                |