① Veröffentlichungsnummer: 0 477 393 A1

## **EUROPÄISCHE PATENTANMELDUNG** (12)

(21) Anmeldenummer: 90118326.9

(51) Int. Cl.5: **H01L 27/02**

2 Anmeldetag: 24.09.90

43 Veröffentlichungstag der Anmeldung: 01.04.92 Patentblatt 92/14

Benannte Vertragsstaaten: AT BE CH DE DK ES FR GB GR IT LI LU NL SE 7) Anmelder: SIEMENS AKTIENGESELLSCHAFT Wittelsbacherplatz 2 W-8000 München 2(DE)

2 Erfinder: Becker, Burkhard, Dr.rer.nat. Schlüsselbergstrasse 8 W-8000 München 80(DE)

## (54) Eingangsschutzstruktur für integrierte Schaltungen.

57) Bei einer Eingangsschutzstruktur für integrierte Schaltungen mit mindestens einem Thyristor in einem Halbleitersubstrat (9) soll eine hohe Belastbarkeit gegen elektrostatische Entladungen beider Polaritäten erreicht werden. Zusätzlich zu den dem Thyristor (6, 7, 11, 13', 9) zugehörigen Diffusionsgebieten sind zwei p-Basis-Gebiete (5, 5') in dasselbe Epitaxiegebiet (13') eingebracht und mit dem Thyristoreingang (1) kurzgeschlossen.

5

10

15

20

25

40

45

50

55

Die Erfindung betrifft eine Eingangsschutzstruktur für integrierte Schaltungen nach dem Oberbegriff des Patentanspruchs 1.

Integrierte Schaltungen benötigen einen sicheren Schutz gegen elektrische Entladungen (ESD). Zu diesem Zweck werden die integrierten Schaltungen mit einer Eingangsschutzstruktur versehen. Eine solche Eingangsschutzstruktur, insbesondere für bipolare integrierte Schaltungen, ist aus der DE-OS 36 16 394 bekannt.

Um einen wirksamen Schutz gegen elektrostatische Entladungen beider Polaritäten zu erzielen, ist bereits eine Eingangsschutzstruktur vorgeschlagen, welche zwischen einen Eingang und ein Referenzpotential geschaltet ist (europäische Patentanmeldung Nr. 89115924.6). Die Schutzstruktur ist in einem Halbleitersubstrat angeordnet und enthält mindestens einen Thyristor, der aus einem Gebiet eines ersten Leitungstyps, einem Gebiet eines zweiten Leitungstyps, einer dritten Zone des ersten Leitungstyps und einer vierten Zone des zweiten Leitungstyps gebildet ist. Diese Eingangsschutzstruktur ist durch einen integrierten Widerstand gekennzeichnet, über den die dritte Zone an den Eingang und die vierte Zone gekoppelt ist. Während bei dieser Struktur negative Impulse über die Thyristor-Strecke abgeleitet werden, steht deren Sperrverhalten der Ableitung der positiven Impulse entgegen, so daß diese über die Substrat-pnp-Strecke z.B. nach Masse als Bezugspotential abgeleitet werden. Die Effektivität dieses Pfades ist der der Thyristor-Strecke allerdings unterlegen.

Der Erfindung liegt die Aufgabe zugrunde, eine Eingangsschutzstruktur der vorgeschlagenen Art so zu verbessern bzw. weiterzubilden, daß eine noch höhere ESD-Belastbarkeit bzw. ein effektiverer ESD-Schutz für integrierte Schaltungen erreicht wird.

Diese Aufgabe wird erfindungsgemäß durch eine Eingangsschutzstruktur mit den Merkmalen des Patentanspruchs 1 gelöst.

Vorteilhafte Ausgestaltungen bzw. Weiterbildungen der Erfindung sind Gegenstand zusätzlicher Ansprüche.

Die mit der Erfindung erzielten Vorteile bestehen insbesondere darin, daß vor allem eine Verbesserung der Ableitung von positiven Impulsen erreicht wird. Die Wirksamkeit der Schutzstruktur zum Ableiten positiver Impulse wird dadurch verbessert, daß zusätzlich zu den dem Thyristor zugehörigen Diffusionsgebieten zwei p-Gebiete in dasselbe Epitaxie-Gebiet eingebracht und mit dem Thyristoreingang bzw. dem diesen zugeordneten Pad kurzgeschlossen werden. Die p-Gebiete bestehen in der einfachsten Form aus zwei Basis-Diffusionsgebieten. Ein noch wirksamerer ESD-Schutz wird durch zwei Isolations-Diffusions-Gebiete erreicht. Das Einbringen von zwei p-Gebieten statt

nur eines erfolgt vor allem aus Symmetriegründen. Dieses zusätzliche p-Gebiet bildet zusammen mit der Buried-Layer eine Diode bzw. mit der Buried-Layer und dem Substrat (bzw. dem Isolationsrahmen) einen Substrat-pnp-Transistor. Gemäß einer Weiterbildung der Erfindung wird der Abstand zwischen den zusätzlichen p-Gebieten und dem Isolationsrahmen der pnp-Basisweite angepaßt. Die Funktion dieser Bauelemente besteht hauptsächlich in dem Einschleusen von freien Ladungsträgern in die bei positiven Impulsen gesperrte Zone zwischen Buried-Layer und Substrat, womit ein frühzeitiger Durchbruch des Thyristors (in Sperrrichtung) angeregt wird. Daneben erhöhen die zusätzlichen p-Gebiete die Emitter-Fläche der Substratpnp-Transistoren. Beide Effekte sorgen für eine höhere ESD-Belastbarkeit bzw. für einen effektiveren ESD-Schutz anderer Bauelemente der integrierten Schaltung, und zwar in der Größenordnung von zusätzlich mindestens 1000Volt.

Anhand von in den Figuren der Zeichnung schematisch dargestellten Ausführungsbeispielen wird die Erfindung im folgenden näher erläutert. Es zeigen

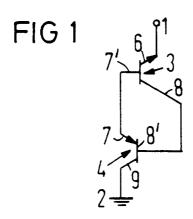

FIG 1 ein Ersatzschaltbild der für die Schutzeinrichtung verwendeten Vier-Schicht-Struktur,

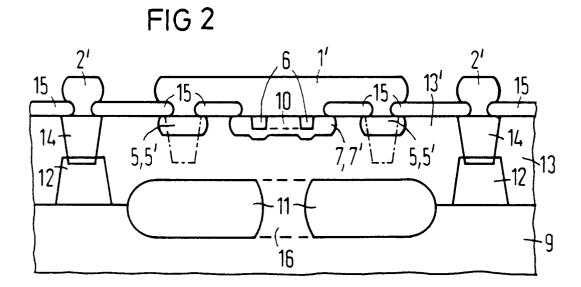

FIG 2 eine Ausführungsform der Eingangsschutzstruktur,

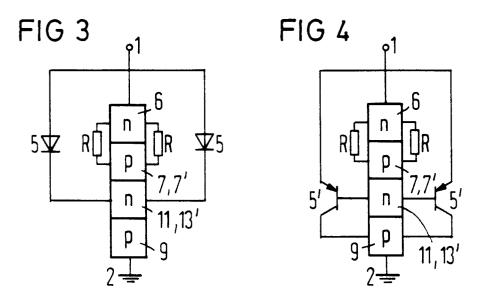

FIG 3 und 4 Ersatzschaltbilder der Eingangs-

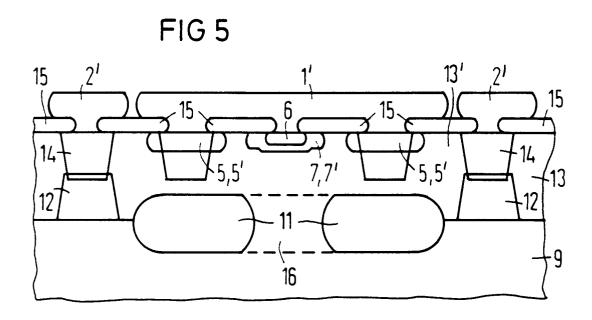

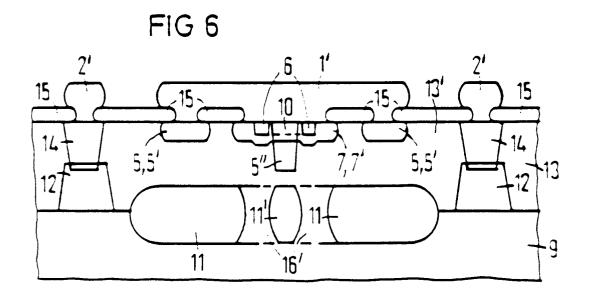

FIG 3 und 4 Ersatzschaltbilder der Eingangsschutzstruktur nach FIG 2 und FIG 5 und 6 weitere Ausführungsformen einer Eingangsschutzstruktur.

Gemäß FIG 1 liegt zwischen einem Eingangsanschluß 1 einer integrierten Schaltung, insbesondere bipolaren Schaltung, und einem Bezugspotential 2, insbesondere Masse, eine Schutzstruktur in Form einer Thyristor- bzw. Vierschicht-Struktur. Diese Struktur wird durch einen ersten Transistor 3 und einen zweiten Transistor 4 charakterisiert, die zu einem Thyristor gekoppelt sind. Bei dem ersten Transistor 3 handelt es sich vorzugsweise um einen npn-Transistor, dessen Emitter 6 mit dem Eingang 1 verbunden ist. Der zweite Transistor 4, vorzugsweise ein pnp-Transistor, ist mit seinem Kollektor 9 an das Bezugspotential 2 angeschlossen. Seine Basis 8' ist mit dem Kollektor 8 des ersten Transistors 3 und sein Emitter 7 mit der Basis 7' des ersten Transistors 3 verbunden.

Die in FIG 2 dargestellte und anhand der Ersatzschaltbilder der FIG 3 und 4 erläuterte Eingangsschutzstruktur besteht im wesentlichen aus einem Halbleitersubstrat 9 eines Leitungstyps. In dieses Halbleitersystem ist eine hochdotierte erste Zone des zweiten bzw. entgegengesetzten Leitungstyps, in diesem Beispiel also des n-Leitungstyps eindiffundiert, durch die eine vergrabene Schicht bzw. Buried-Layer-Zone 11 gebildet wird.

15

4

Diese erste Zone 11 weist vorzugsweise eine innere Aussparung 16 auf und besitzt ringförmige Gestalt. Außerdem sind in das Halbleitersubstrat 9 Zonen mit dem Leitungstyp des Substrats eindiffundiert, die Teilzonen eines an sich üblichen Isolationsrahmens 12 bilden. In weiteren Diffusionsschritten sind Zonen 14 und eine dritte Zone 7. 7' in die epitaktische Schicht 13 eingebracht, die beide den Leitungstyp des Halbleitersubstrats 9, d.h. den p-Leitungstyp haben. Dabei vervollständigen die in die Teilzonen 12 hineinreichenden Zonen 14 den die zweite und dritte Zone einschließenden Isolationsrahmen 12, 14. Die dritte Zone 7, 7' liegt innerhalb der zweiten Zone 13' und vorzugsweise über der Aussparung 16 der ersten Zone 11. Sie bildet die Basis 7' des ersten Transistors 3 (FIG 1) und gleichzeitig den Emitter 7 des zweiten Transistors 4 (FIG 1). In die dritte Zone 7, 7' wird eine vierte Zone 6 mit dem Leitungstyp der zweiten Zone, in diesem Beispiel mit dem n-Leitungstyp, eindiffundiert. Die vierte Zone 6 ist von der zweiten Zone 13' durch die dritte Zone 7, 7' isoliert und besitzt in diesem Beispiel eine Aussparung 10, die vorzugsweise über der Aussparung 16 der ersten Zone 11 angeordnet ist. Durch die spezielle Anordnung von dritter und vierter Zone sowie der auf der Oberfläche des Halbleitersystems liegenden isolierenden Schicht 15 wird ein integrierter Widerstand gebildet.

In die zweite Zone 13' des zweiten Leitungstyps, in diesem bevorzugten Ausführungsbeispiel des n-Leitungstyps, ist zu beiden Seiten der dritten Zone 7, 7' des ersten, hier p-Leitungstyps, von dieser beabstandet, eine zusätzliche Zone 5, 5' des ersten, hier also des p-Leitungstyps eindiffundiert und mit dem Eingang 1 kurzgeschlossen. Die zusätzlichen p-Gebiete 5, 5' können sowohl aus p-Basis-Diffusionsgebieten als auch aus Isolations-Diffusions-Gebieten bestehen. Im zweiten Fall ist eine höhere Schutzwirkung zu erreichen. Diese Alternative ist in den Figuren durch strichpunktierte Linien veranschaulicht.

Auf der Oberfläche des Halbleitersystems ist eine isolierende Schicht 15 aufgebracht, die zur Herstellung von Anschlußöffnungen strukturiert wird. Über einen ersten Anschluß 1' sind die vierte Zone 6, die dritte Zone 7, 7' und die zusätzlichen Zonen 5, 5' an den Eingang 1 angeschlossen. Über einen zweiten Anschluß 2' ist das Halbleitersubstrat 9 über den Isolationsrahmen 12, 14 an das Bezugspotential 2 angeschlossen.

In den Figuren 3 und 4 ist die vorstehend erläuterte Zonenfolge als Ersatzschaltbild wiedergegeben. Insgesamt stellt die Zonenfolge einen npnp-Thyristor dar, der sich, wie im Zusammenhang mit FIG 1 bereits dargelegt, aus einem ersten npn- und einem zweiten pnp-Transistor zusammensetzt. Der Thyristor besteht aus p-Substrat 9, der

zweiten, einschließlich ersten, n-leitenden Zone 11, 13', der dritten Zone 7, 7' und der vierten, n-leitenden Zone 6. Der integrierte Widerstand R wird durch die Dimensionierung der vierten Zone 6 innerhalb der dritten Zone 7, 7' einerseits und durch Überlappung des Anschlusses 1 über die dritte Zone 7, 7' sowie durch die Aussparung 10 in der vierten Zone 6 andererseits gebildet. Das zusätzliche p-Gebiet 5, 5' bildet zusammen mit der n-leitenden Zone 13' bzw. der Buried Layer 11 eine Diode 5 (FIG 3) bzw. mit dem p-Substrat 9 (bzw. dem Isolationsrahmen 12, 14) einen Substrat-pnp-Transistor 5' (FIG 4).

In FIG 5 ist eine weitere Ausführungsform der erfindungsgemäßen Eingangsschutzstruktur in einem Halbleitersystem dargestellt. Einander entsprechende Teile sind mit den gleichen Bezugszeichen wie in den anderen Figuren versehen. Auch die in den Figuren 3 und 4 gezeigten Ersatzschaltbilder gelten für dieses Ausführungsbeispiel. Lediglich der integrierte Widerstand R ist für dieses Beispiel unendlich groß, weil dritte Zone 7, 7' und vierte Zone 6 nicht mehr die spezielle Anordnung gemäß FIG 2 aufweisen und deren Emittergebiet (vierte Zone 6) und Basisgebiet (dritte Zone 7, 7') nicht mehr miteinander verbunden sind.

Im folgenden werden die Unterschiede zu der in FIG 2 dargestellten Ausführungsform erläutert. In diesem Ausführungsbeispiel ist der Abstand zwischen den zusätzlichen Zonen 5, 5' des ersten Leitungstyps, in diesem Beispiel der p-Gebiete und dem Isolationsrahmen 12, 14 der pnp-Basisweite angepaßt. Auf der Oberfläche des Halbleitersystems ist wiederum eine isolierende Schicht 15 aufgebracht, die zur Herstellung der Anschlußöffnungen entsprechend strukturiert ist. In diesem Beispiel überdeckt die isolierende Schicht 15 auch die dritte Zone 7, 7' und läßt nur die Oberfläche der vierten Zone zum Kontaktieren frei. Über einen ersten Anschluß 1' sind daher nur die vierte Zone 6 und die zusätzlichen Zonen 5, 5' an den Eingang 1 angeschlossen. Über den zweiten Anschluß 2' ist wiederum das Halbleitersubstrat 9 über den Isolationsrahmen 12, 14 mit dem Bezugspotential 2 verbunden.

Die Struktur der FIG 2 beinhaltet sowohl negative als auch positive Sperrspannungen, so daß diese zum Schutz von Eingängen mit zu verarbeitenden Signalspannungen beider Polaritäten eingesetzt werden kann.

Sind keine negativen Signalspannungen vorhanden, kann eine Schutzstruktur gemäß FIG 5 verwendet werden. Der Durchbruch liegt bei negativer Spannung im Bereich von -0,7V, wohingegen eine positive Sperrspannung in der Größenordnung von U (CEO) des lateralen pnp-Transistors erwartet wird. Der Vorteil dieser Struktur besteht vor allem in der problemloseren technologischen Realisie-

50

55

5

10

15

20

25

35

40

45

50

6

rung gegenüber der Struktur gemäß FIG 2, wo die Einstellung des integrierten Widerstandes von den Fertigungstoleranzen der jeweiligen Prozeßlinie abhängt.

Die ESD-Schutzwirkung beider Strukturen kann erhöht werden, indem man die Buried-Layer 11 mit dem Isolationsrahmen 12, 14 zusammenlaufen läßt. Hierbei wird allerdings die Durchbruchspannung für positive Signalspannungen erniedrigt und die zusätzliche Kapazität erhöht. Wird dagegen der Abstand zwischen Buried-Layer 11 und unterem Isolationsrahmen 12 beibehalten und lediglich der obere Isolationsrahmen 14 über der Buried-Layer 11 bei gleichbleibenden Abständen bezüglich der aktiven Zone, d.h. den Emitter- und Basis-Gebieten, angeordnet, kann eine Verminderung der Durchbruchspannungen bei verbesserter Schutzwirkung verhindert werden.

Das in FIG 6 dargestellte Ausführungsbeispiel zeigt, daß die Ableitwirkung des im Thyristor integrierten Substrat-pnp-Transistors 4 (FIG 1) durch das Einbringen einer p-Isolations-Diffusion 5" in die Aussparung 10 der vierten Zone 6 des n-Leitfähigkeitstyps noch erhöht werden kann. Handelt es sich hierbei um eine relativ hochohmige Isolationsdiffusion (einige hundert Ohm/Quadrat), kann auch die vollständige dritte Zone 7, 7' des p-Leitfähigkeitstyps durch diese ersetzt werden, ohne die effektive Basisweite des non-Transistors 3 wesentlich zu erhöhen. Bei Prozeßlinien mit einer Einfach-Isolation muß allerdings unterhalb der p-Isolations-Diffusions-Zone 5" ein Buried-Layer-Gebiet 11' angeordnet sein, um einen Kurzschluß zum Substrat 9 zu vermeiden. Die Aussparung des Buried-Layer-Gebietes entartet damit zu einem Ring 16' bzw. zu einem streifenförmigen Aufbau, welcher unterhalb der vierten Zone 6 angeordnet ist. Bei Prozeßlinien mit einer Doppel-Isolation kann das zusätzliche Buried-Layer-Gebiet 11' vermieden werden. Durch die Anordnung des Isolations-Diffusions-Gebiets 5" in der AusSparung der vierten Zone 6 wird zum einen eine höhere Emitter-Effektivität des Substratpnp-Transistors 4 erreicht, ohne daß die Basisweite des npn-Transistors 3 ungünstigerweise vergrößert wird. Zum anderen erfolgt durch die tiefreichende Diffusion die Ableitung der Impulse effektiv von der Oberfläche in die Tiefe. Diese Anordnung unterstützt die Substrat-pnp-Wirkung der zusätzlichen p-Gebiete 5, 5'. Ferner wird hiermit sogar eine Erhöhung der Schutzwirkung einer Eingangsschutzstruktur gemäß der europäischen Patentanmeldung Nr. 89115924.6 ohne die Verwendung der zusätzlichen p-Gebiete 5, 5' erreicht.

## Patentansprüche

Eingangsschutzstruktur für integrierte Schaltungen, die in einem Halbleitersubstrat (9) zwischen einen Eingang (1) und ein Bezugspotential (2) geschaltet ist und mindestens einen Thyristor enthält, der aus einem Gebiet eines ersten Leitungstyps, einem aus einer ersten und einer zweiten Zone (13') bestehenden Gebiet eines zweiten Leitungstyps, einer dritten Zone (7, 7') des ersten Leitungstyps und einer vierten Zone (6) des zweiten Leitungstyps gebildet ist, dadurch gekennzeichnet, daß in die zweite Zone (13') des zweiten Leitungstyps zu beiden Seiten der dritten Zone (7, 7') des ersten Leitungstyps von dieser beabstandet eine zusätzliche Zone (5, 5') des ersten Leitungstyps eingebracht ist, die mit dem Eingang (1) und der vierten Zone (6) des zweiten Leitungstyps verbunden ist.

- 2. Eingangsschutzstruktur nach Anspruch 1, dadurch gekennzeichnet, daß die zweite Zone (13') des zweiten Leitungstyps durch einen Isolationsrahmen (12, 14) bildende Diffusionszonen seitlich begrenzt ist.

- 3. Eingangsschutzstruktur nach Anspruch 1 oder 2, dadurch gekennzeichnet, daß die vierte Zone (6) des zweiten Leitungstyps, die dritte Zone (7, 7') des ersten Leitungstyps und die zusätzlichen Zonen (5, 5') des ersten Leitungstyps miteinander und mit dem Eingang (1) verbunden sind.

- 4. Eingangsschutzstruktur nach einem der Ansprüche 1 bis 3, dadurch gekennzeichnet, daß die zusätzlichen Zonen (5, 5') des ersten Leitungstyps p-Basis-Diffusionsgebiete oder p-Isolations-Diffusionsgebiete sind.

- 5. Eingangsschutzstruktur nach einem der Ansprüche 1 bis 4, dadurch gekennzeichnet, daß die erste Zone (11) des zweiten Leitungstyps als vergrabene Zone ausgebildet ist.

- Eingangsschutzstruktur nach einem der Ansprüche 1 bis 5, gekennzeichnet durch einen streifenförmigen oder zentralsymmetrischen Aufbau.

55

## EUROPÄISCHER RECHERCHENBERICHT

EP 90 11 8326

| EINSCHLÄGIGE DOKUMENTE |                                                                                                                                                            |                                                        |                                            |                                    |                                                                                                                |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--------------------------------------------|------------------------------------|----------------------------------------------------------------------------------------------------------------|

| Categorie              |                                                                                                                                                            | nts mit Angabe, soweit erforderlic<br>Bgeblichen Teile |                                            | setrifft<br>nspruch                | KLASSIFIKATION DER<br>ANMELDUNG (Int. CI.5)                                                                    |

| Α                      | GB-A-2 182 491 (SGS MIC<br>* Seite 1, Zeile 109 - Seite 2                                                                                                  |                                                        | 1,2                                        | 2,5,6                              | H 01 L 27/02                                                                                                   |

| Α                      | PATENT ABSTRACTS OF<br>(E-173)(1248) 06 Mai 1983,<br>& JP-A-58 23471 (TOKYO 5<br>1983,<br>* das ganze Dokument *                                           |                                                        |                                            | 2,5,6                              |                                                                                                                |

| Α                      | US-A-4 870 530 (ADVANC<br>* Zusammenfassung; Figure                                                                                                        | · · · · · · · · · · · · · · · · · · ·                  | 1,2                                        | 2                                  |                                                                                                                |

| A,D                    | GB-A-2 176 053 (SGS MI0<br>* Zusammenfassung; Figure<br>– -                                                                                                |                                                        | 1,2                                        | 2                                  |                                                                                                                |

|                        |                                                                                                                                                            |                                                        |                                            |                                    | RECHERCHIERTE<br>SACHGEBIETE (Int. Cl.5)                                                                       |

|                        |                                                                                                                                                            |                                                        |                                            |                                    | H 01 L                                                                                                         |

|                        |                                                                                                                                                            |                                                        |                                            |                                    |                                                                                                                |

|                        |                                                                                                                                                            |                                                        |                                            |                                    |                                                                                                                |

|                        |                                                                                                                                                            |                                                        |                                            |                                    |                                                                                                                |

|                        |                                                                                                                                                            |                                                        |                                            |                                    |                                                                                                                |

|                        |                                                                                                                                                            |                                                        |                                            |                                    |                                                                                                                |

| De                     | er vorliegende Recherchenbericht wur                                                                                                                       | de für alle Patentansprüche erste                      | lit                                        |                                    |                                                                                                                |

| Recherchenort          |                                                                                                                                                            | Abschlußdatum der Recherche                            |                                            |                                    | Prüfer                                                                                                         |

|                        | Den Haag                                                                                                                                                   | 07 Mai 91                                              |                                            |                                    | VENDANGE P.                                                                                                    |

| Y: '                   | KATEGORIE DER GENANNTEN von besonderer Bedeutung allein bevon besonderer Bedeutung in Verbi anderen Veröffentlichung derselber technologischer Hintergrund | etrachtet<br>ndung mit einer                           | nach dem<br>D: in der Anm<br>L: aus andere | Anmelded<br>eldung an<br>en Gründe | ent, das jedoch erst am oder<br>atum veröffentlicht worden ist<br>geführtes Dokument<br>n angeführtes Dokument |

| P: 1                   | nichtschriftliche Offenbarung<br>Zwischenliteratur<br>der Erfindung zugrunde liegende Th                                                                   | eorien oder Grundsätze                                 | &: Mitglied de<br>übereinstii              |                                    | n Patentfamilie,<br>Dokument                                                                                   |