11) Publication number:

0 482 678 A2

# (12)

# **EUROPEAN PATENT APPLICATION**

(21) Application number: 91121918.6

(51) Int. Cl.5: G09G 1/16

2 Date of filing: 23.07.85

This application was filed on 20 - 12 - 1991 as a divisional application to the application mentioned under INID code 60.

Priority: 23.07.84 US 633367

23.07.84 US 633383

23.07.84 US 633384

23.07.84 US 633385

23.07.84 US 633386

23.07.84 US 633387

23.07.84 US 633388

23.07.84 US 633389

- (43) Date of publication of application: 29.04.92 Bulletin 92/18

- Publication number of the earlier application in accordance with Art.76 EPC: 0 182 454

- 84 Designated Contracting States: **DE FR GB**

- (71) Applicant: TEXAS INSTRUMENTS **INCORPORATED** 13500 North Central Expressway Dallas Texas 75265(US)

- (72) Inventor: Bond, Jeffrey C. 3207 Rifle Gap Lane Sugar Land, TX 77478(US) Inventor: Guttag, Karl M.

11602 Ensbrook

Houston, TX 77099(US)

Inventor: Thaden, Robert C.

6425 S. Gessner No. 1220

Houston, TX 77036(US)

Inventor: Pinkham, Raymond

2023 Retriever Lane

Missouri City, TX 77489(US)

Inventor: Novak, Mark 4225-D Airport Road

Colorado Springs, CO 80910(US)

Inventor: Watts, Mark W. 24307 Kennedy Ranch Dr. Hockley, TX 77447(US) Inventor: Vanaken, Jerry

13563 Fernhill

Sugar Land, TX 77478(US)

Inventor: Moravec, John V.

212 Hinricher Dr.

Willow Springs, IL. 60480(US) Inventor: Albachten, Rudy J. III

87 Lyons Drive

Centerville, OH 45459(US)

(74) Representative: Blanco White, Henry Nicholas

et al

**ABEL & IMRAY Northumberland House**

303-306 High Holborn London WC1V 7LH(GB)

(54) Video system controller with a row address override circuit.

(57) The present invention is a video system which includes a data processor (1), such as a mircoprocessor, for processing data, a video memory (5) for storing data from the data processor corresponding to an image to be displayed, a display (11), such as a raster scan cathode ray tube, for displaying the image data stored in the video memory means, and a video system controller (3) connected to the video memory (5) For controlling the transfer of data from the video memory (5) to the display (11) and between the data processor (1) and the video memory (5). The video memory (5) is preferrably a multiport dynamic randon access memory including an addressable memory array. The video system controller (3) performs a number of functions including refresh of the dynamic random access memory, multiplexing of the various access requests of the video memory and control of the blanking interval of the display. This is accomplished by having a first portion which operates synchronously with the video memory (5) and a second portion which operates synchronously with the data

processor (1). The transfer operations in the video system controller are preferrably controlled through the use of a programmable state machine which manipulate inputs in a logic array.

# BACKGROUND OF THE INVENTION

This invention relates to electronic computer systems and the like, and more particularly relates to improved methods and apparatus for achieving a video display having high resolution.

It is conventional to present the output from a computer as an image on the screen of a cathode ray tube or the like. The screen is actually composed of a collection of dots or "pixels", and the image is therefore produced by selecting and illuminating those pixels necessary to form the desired image. If the image sought to be presented is merely a simplistic pattern of numbers or other symbols, this may be achieved with a relatively limited number of pixels. However, if a more complex image (with a greater resolution) is desired, then a screen must be chosen which has a substantially greater number of pixels.

It should be understood that each pixel used to form the image is illuminated by a separate output data signal from the processing section of the computer, and that an increase in resolution requires a screen having a greater number of pixels. More particularly, since each video data signal must also be stored before being transferred to the video screen, an increase in image resolution also requires that the data storage section have a corresponding increase in the number of memory cells for receiving and holding all of these data signals.

If a different screen having an increased number of pixels is employed for the purpose of enhancing the resolution of the image displayed on the screen, this will not by itself cause a disproportionate increase in the overall cost of the system. However, the size or capacity of the memory component or circuit is a significant factor in the cost of the system, and an increase in the resolution of the image being presented effectively decreases the time interval available to effect a complete transfer of all of the data signals between the storage and the video section.

There have been many attempts and proposals for overcoming or mitigating these disadvantages. In particular, a larger storage unit may be selected to accommodate the increased number of input signals, but as hereinbefore explained, such a unit is inherently expensive, and its use in a home computer system will disproportionately increase the costs of such computer systems. The technology is available to provide specially designed memory units capable of fast access for higher data velocity, but such units are even more expensive than slower access memory units.

Alternatively, an increase in data storage capacity may be achieved by simply adding additional memory units. However, this not only increases the overall cost of the system, since each memory unit is a separate storage component this tends to increase the length of the time required to transfer video data to the pixels.

It has been proposed to mitigate part of the problem which arises when the data storage is composed of a plurality of separate random-access memory units or "chips", by interconnecting them in parallel with a shift register, whereby all of the units may be unloaded and their contents transferred to the shift register at the same time. The data in the shift register is then sequentially clocked to the pixels at the proper video data rate. Although this technique has been extremely beneficial in reducing the data transfer cycle to that corresponding to a single memory chip, it does not attack the problem of increased cost. Moreover, since the storage circuit is composed of memory units of standard design, there will inherently be more cells in the storage unit than there are pixels on the video screen, and whenever the storage is unloaded into the video section, it is necessary to unload more cells than are actually required to produce the image.

The control circuits for the prior art systems required three different controllers, one for handling system memory, one for handling of text information and one for handling of graphic information. These systems often resulted in bottlenecks at the video memory.

The text subsystem is only required if the performance of the bit-mapped controller subsystem is sufficient to handle text in a reasonable period of time. Today in a number of products, the text and graphics are combined into one subsystem. These systems, however, have the drawback that they must have physically separate data buses between the least part of the system memory and the display memory. In one example -- part of the main system memory is in a shared memory space with the display data, there is a separate isolated data bus that connects to a high speed ROM that is used to contain important (for performance) routines.

Due to the fact that most display devices must be constantly refreshed with display data, there is a need for a relatively constant "background" task that continually transfers the contents of the display memory to the display device. This "background" with normal RAMs can monopolize the data bus into and out of the RAMs for as much as 85% (percent). With the multiport video RAM type device (such as Texas Instrument Inc's TMS4161 for example), the amount of data bus requirement needed for the display refresh task can be dropped down to less than 3%. This creates the aformentioned bottleneck when other types of RAMs are used.

In systems using conventional memories for holding the display data it is imperative that the significant portion of the processor's main system memory not be on the same physical data bus as the display data bus, or else the system performance would be substantially reduced. For example if the processor were connected on a bus where 80% of the bus cycles were allocated to display refresh, the overall system performance could be degraded by as much as 5 times (due to only getting 20% or 1/5th of the accesses).

The solutions to date, using conventional memories for the display data, have been to isolate at least a significant portion (if not all) the CPU's main system memory data bus from the display memory data bus. This isolation lets the processor run significantly faster on the isolated system memory bus that it can out of the display memory bus. In some cases, such as systems using a NEC7220 manufactured by Nippon Electric Corporation, the isolation of the display memory is such that the processor has only very limited access to the display memories.

#### SUMMARY OF THE INVENTION

15

30

35

40

45

50

55

The present invention is a video system which includes a mircoprocessor for processing data, a video memory for storing data from the microprocessor corresponding to an image to be displayed, a display, such as a raster scan cathode ray tube, for displaying the image data stored in the video memory means, and a video system controller connected to the video memory for controlling the transfer of data from the video memory to the display and between the microprocessor and the video memory.

The video memory is preferrably a multiport dynamic random access memory including an X Y addressable memory array organized in a plurality of color planes. The video system controller performs automatic refresh of this dynamic random access memory.

The video system controller includes a row address latch, a column address latch and X Y address logic. The video system controller multiplexes the various access requests of the video memory with a priority circuit. This is accomplished with a first portion which operates synchronously with the video memory and a second portion which operates synchronously with the microprocessor. This permits the processor to run at a rate independent of the pixel rate of the video display. The transfer operations in the video system controller are preferrably controlled through the use of a programmable state machine which manipulates inputs in a logic array.

The video system controller supports the multiple plane memory array. Data may be written into a plurality of memory planes simultaneously via a row address override circuit. A number of output logic circuits equal to the number of memory planes produce write enable signals independently permitting data to be loaded into selected memory planes. The video memory controller also controls an external shift register employed as a buffer between the video memory and the display.

The video memory and CRT controller or video system controller (VSC) controls two essential features.

- 1. Normal Dynamic Ram control -- This may include all or part of the following DRAM refresh address generation, RAS and CAS strobes, write enable generation, row and column address multiplexing, and other features found in standard dynamic ram controllers. A CPU or other Host processor is given direct or indirect access to the Dynamic RAM.

- 2. The special control generation necessary to effect the transfer of the to and/or from the memory array and the shift register inside the special VRAMs.

Further significant features that may be included are:

- 2A. The control hardware necessary to cause the transfer to or from the memory array and the shift register inside the memory array to happen automatically. This hardware may be in the form of programmable or fixed counters that once initialized will cause the transfers to be made automatically in a relationship that is couple/related to the vertical and horizonal scanning of a display device such as a CRT.

- 3. Including a timing function (either programmable or fixed timing) that produces control signal outputs necessary for the control of a display device like (but not limited to) a CRT.

- 4. Since there may be multiple operations needing to access the bus such as the host processor access, dram refresh, and shift register transfers, it is generally preferred that arbitration logic that controls which of conflicting requests gets the bus, and then sees that the appropriate address is applied to the addresses of the memories is applied is included. This may involve including internal or external address multiplexing.

- 4A. In the case where host processor conflict with dram refresh or other accesses it may be desirable to indicate that the cycle of the host needs to be extended by the means of a "not-ready" like signal.

- 5. Signals from a host processor may directly/asynchronously effect the address, ras, cas dram timing or the timing could be controlled synchronously to the controller after the request signals from the host have been synchronized. Or there could be a mixture of synchronous and asynchronous control where normally the host directly controls the dram control signal except in cases where there is an access conflict where the controller detects this conflict and substitutes its own control signals and indicates a longer request cycle.

- 6. In addition to controlling special VRAM, the video controller may also control standard dynamic rams. These and other features/advantages may be apparent from a reading of the specification in conjunction with the figures in which:

BRIEF DESCRIPTION OF THE FIGURES

```

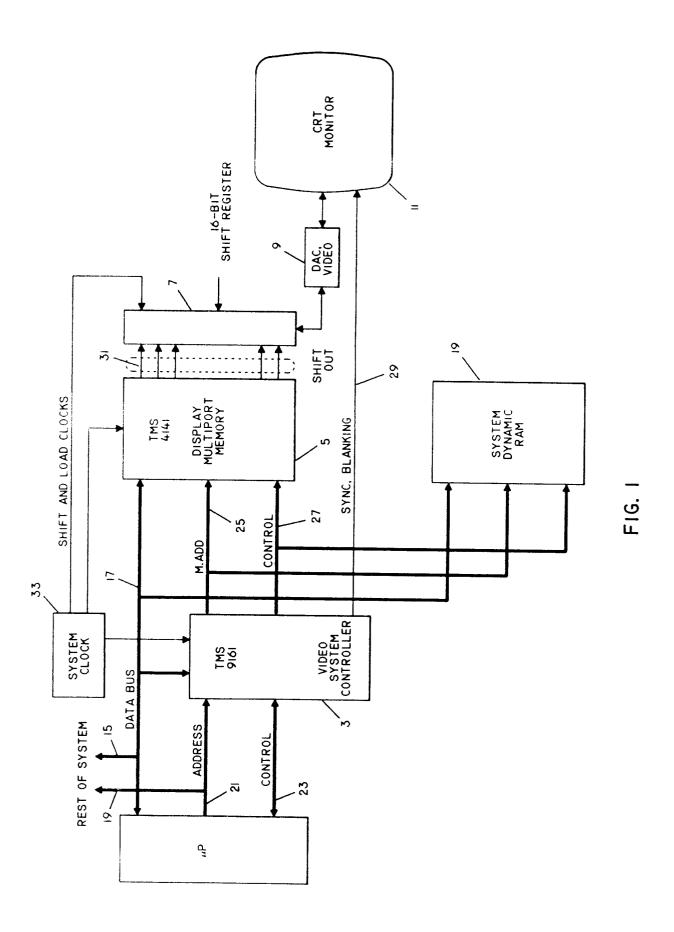

Figure 1 is a block diagram incorporating a video controller according to the inventions;

```

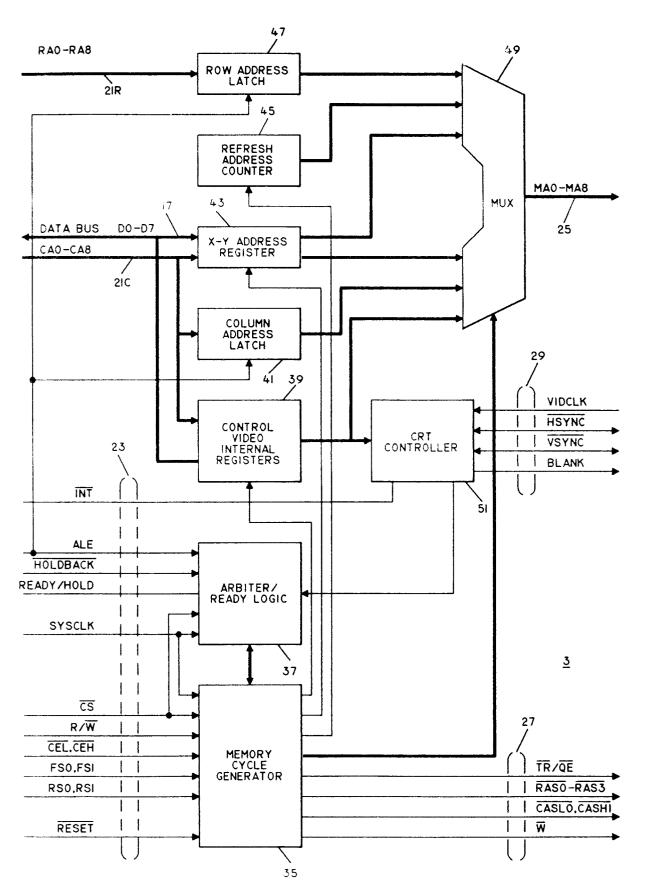

Figure 2 is a functional block diagram of the video controller of Figure 1,

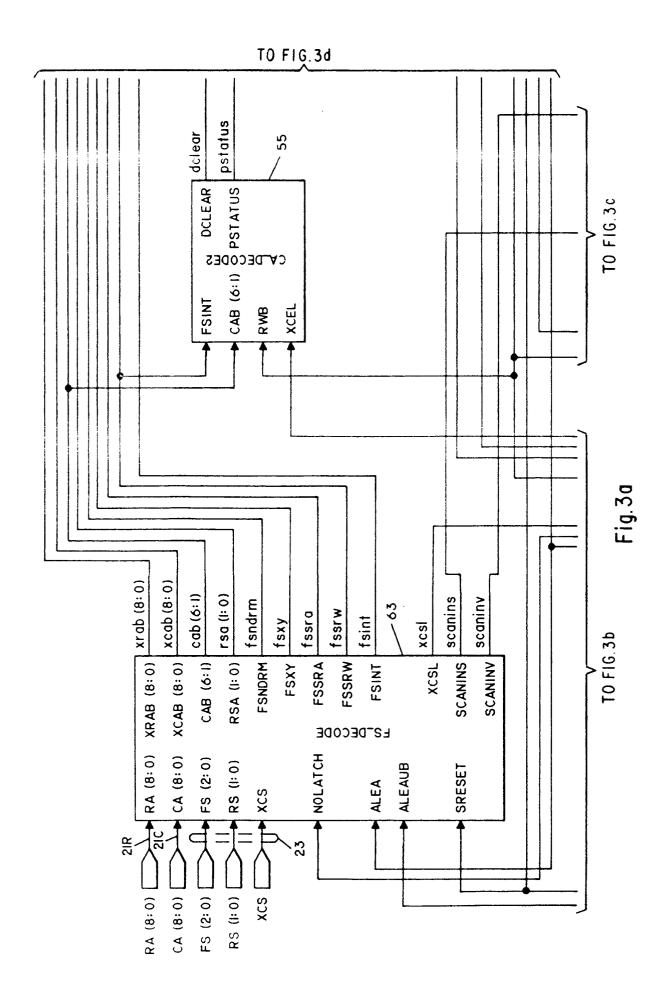

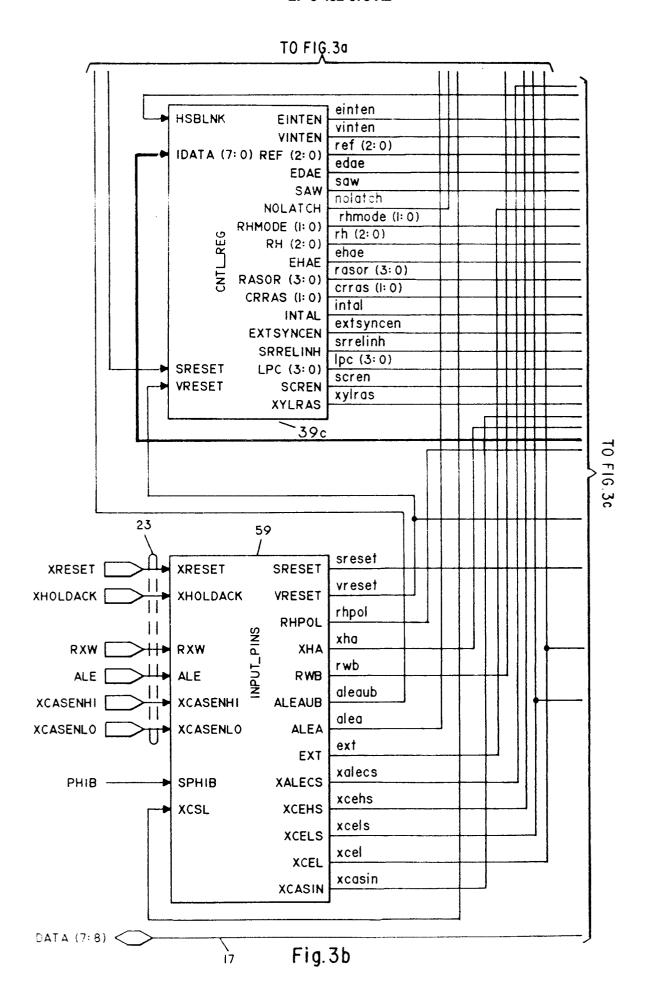

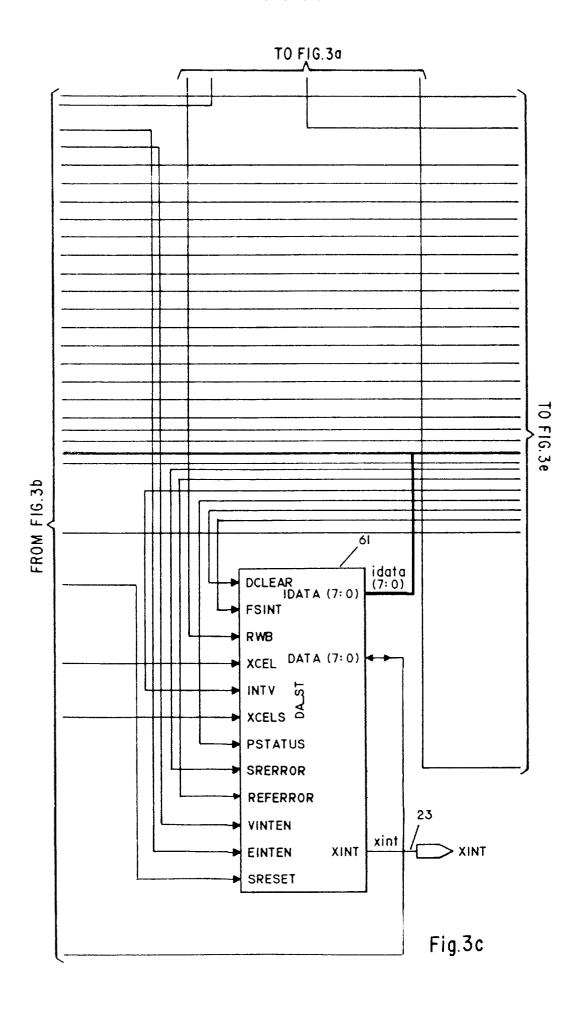

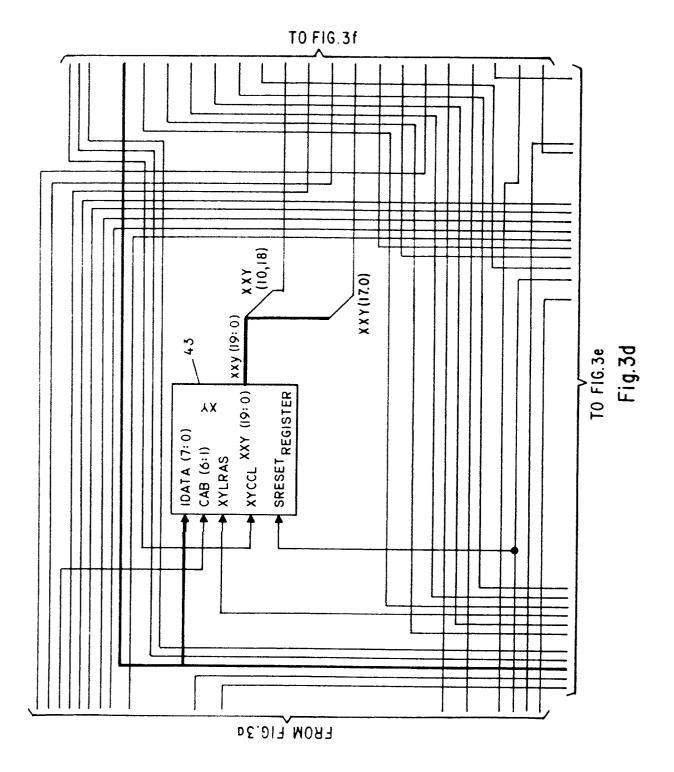

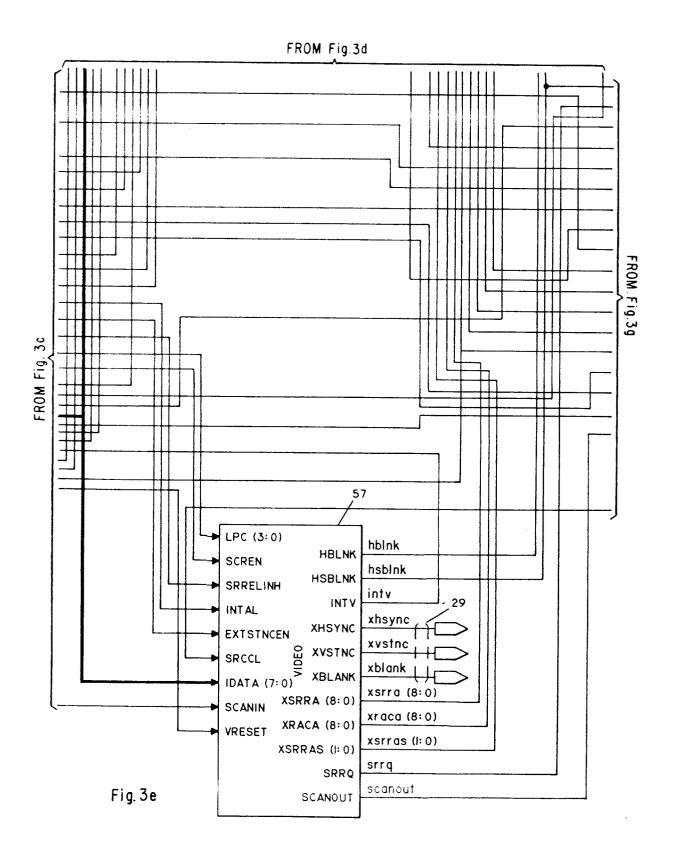

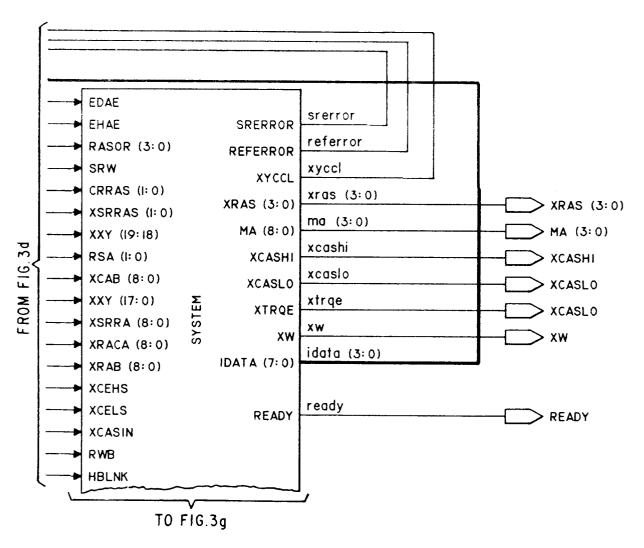

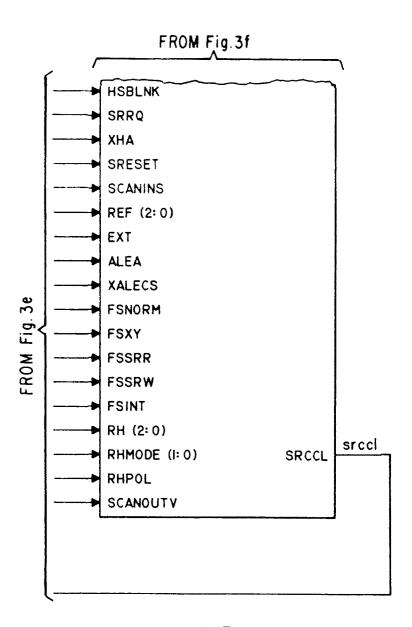

75 Figure 3 is a wiring diagram of circuit blocks used to implement the functions of Figure 2;

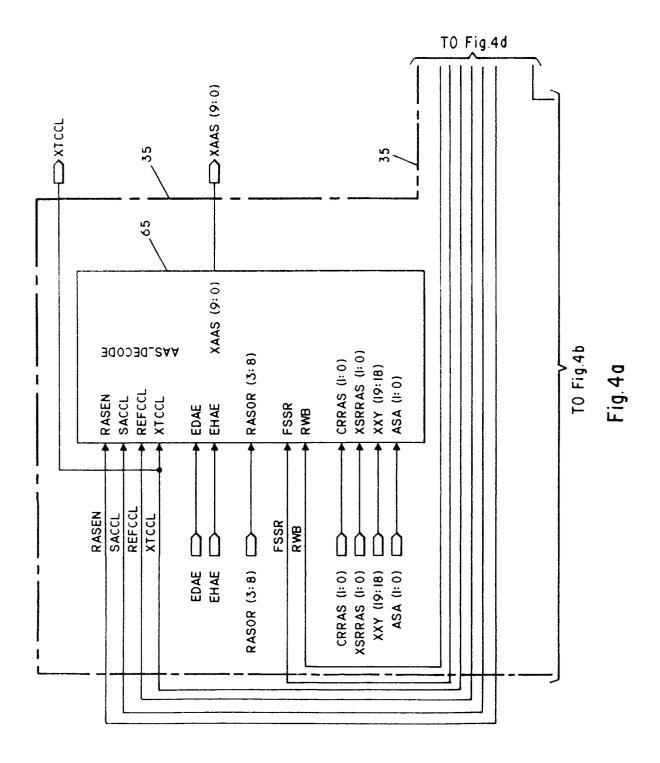

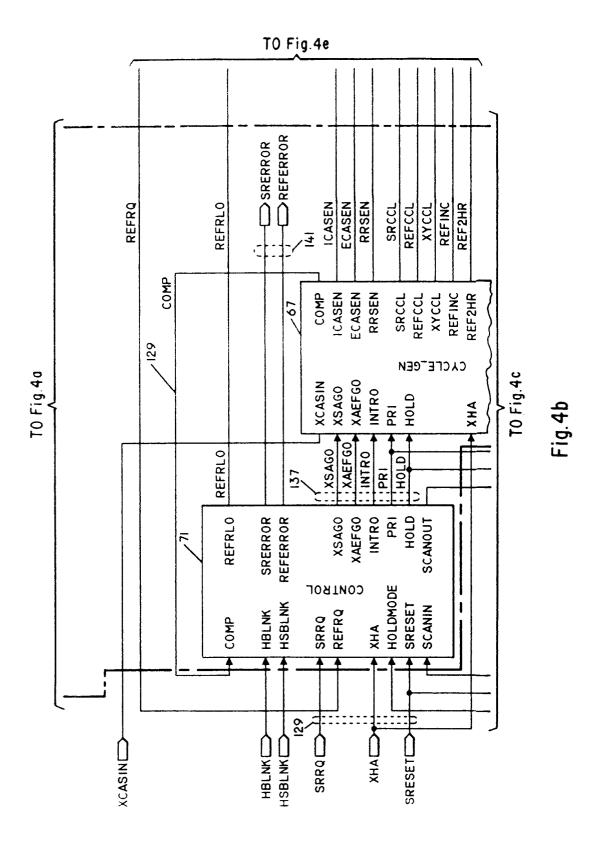

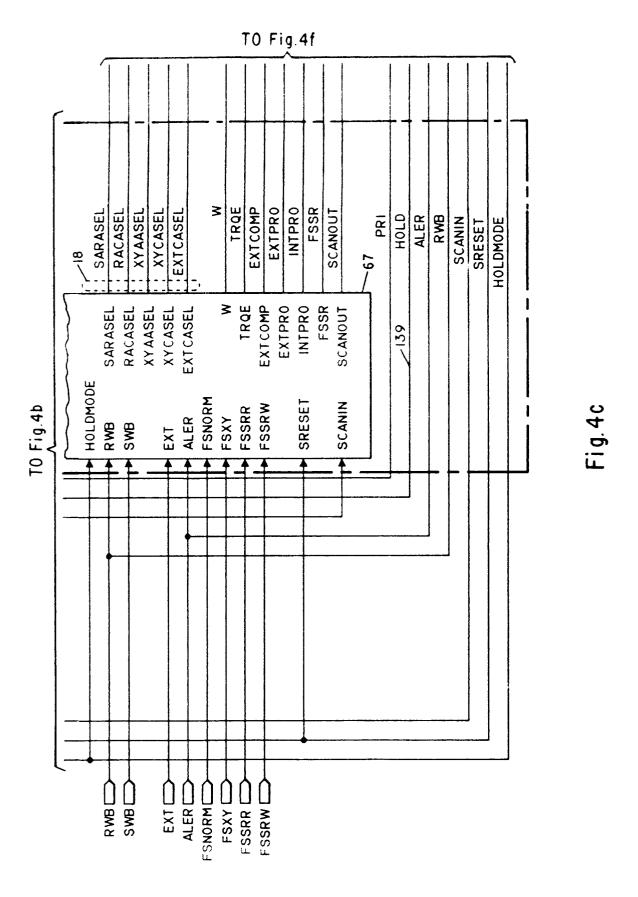

Figure 4 is a block diagram of the system block of Figure 3;

Figure 5 is a block diagram of the video block of Figure 3;

Figure 6 is a block diagram of the DA-ST block of Figure 3;

Figure 7 is a block diagram of the CRT block of Figure 3;

20 Figure 8 is a schematic diagram of the control block of Figure 4;

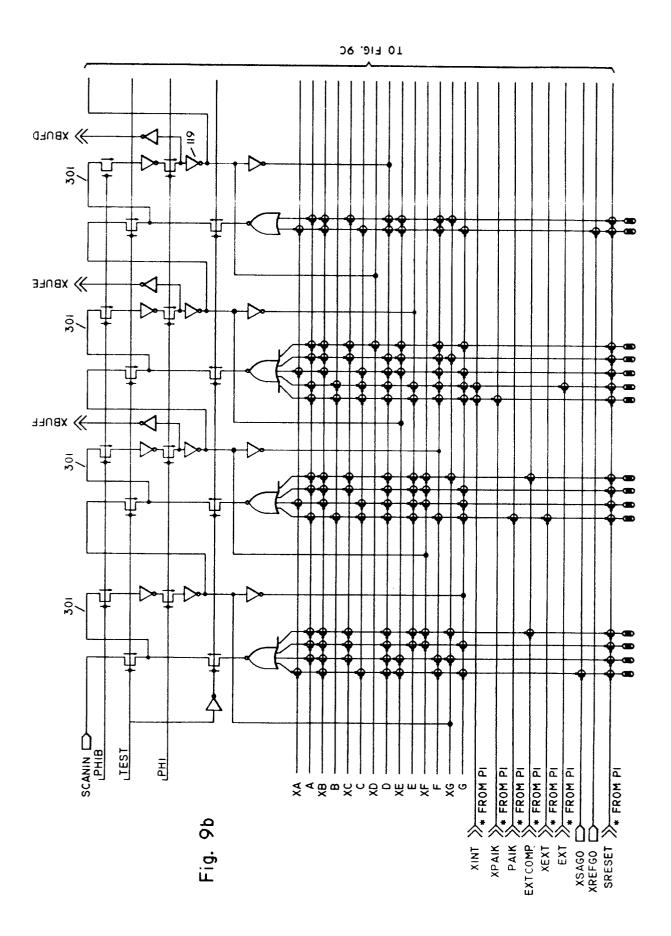

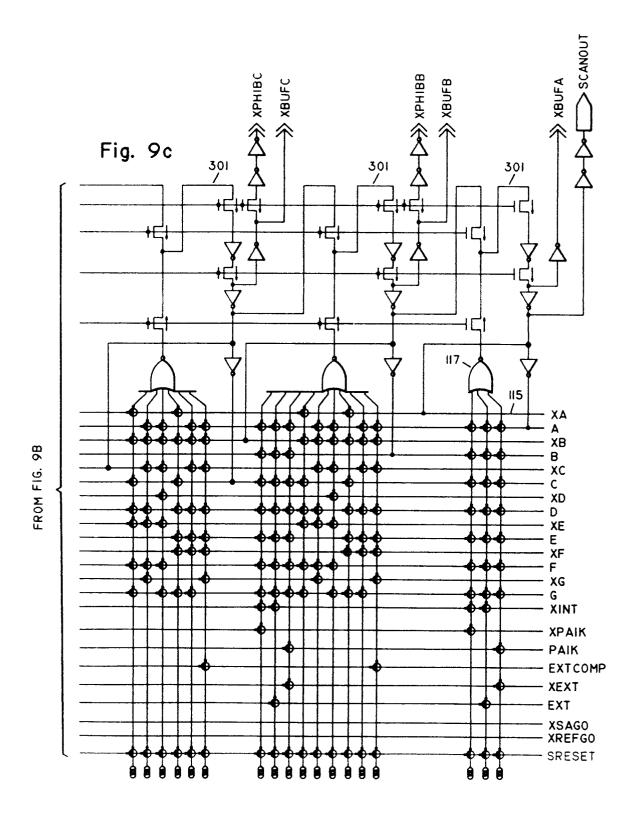

Figure 9 is a schematic diagram of the cycle generator of Figure 4;

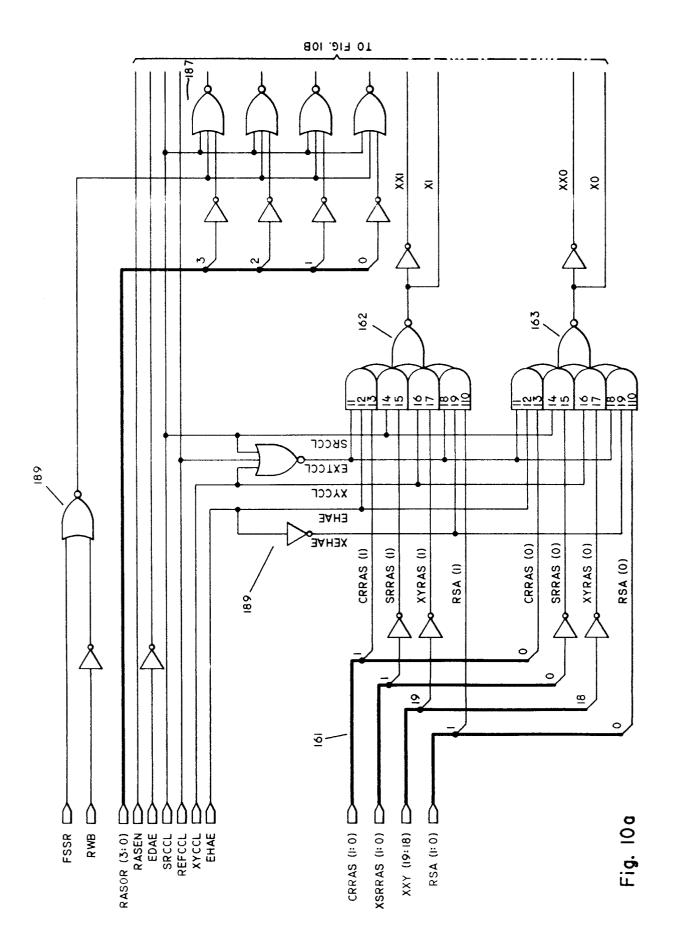

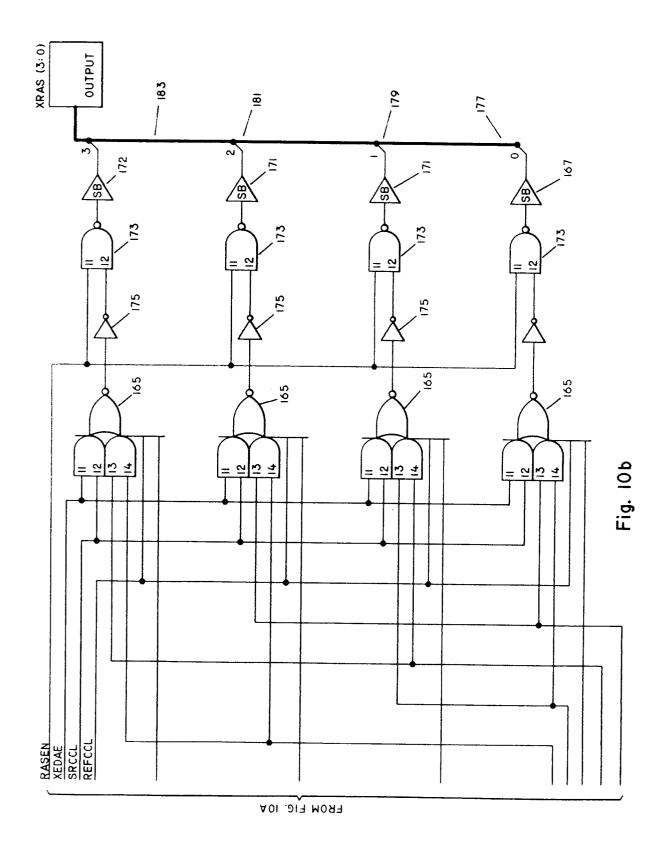

Figure 10 is a schematic diagram of RAS decode block of Figure 4;

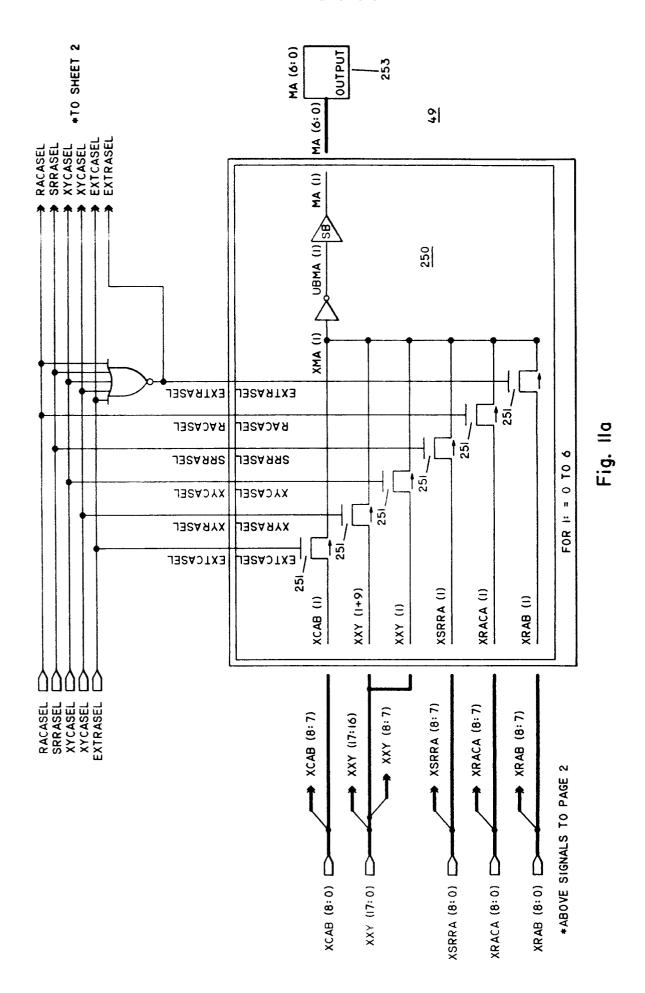

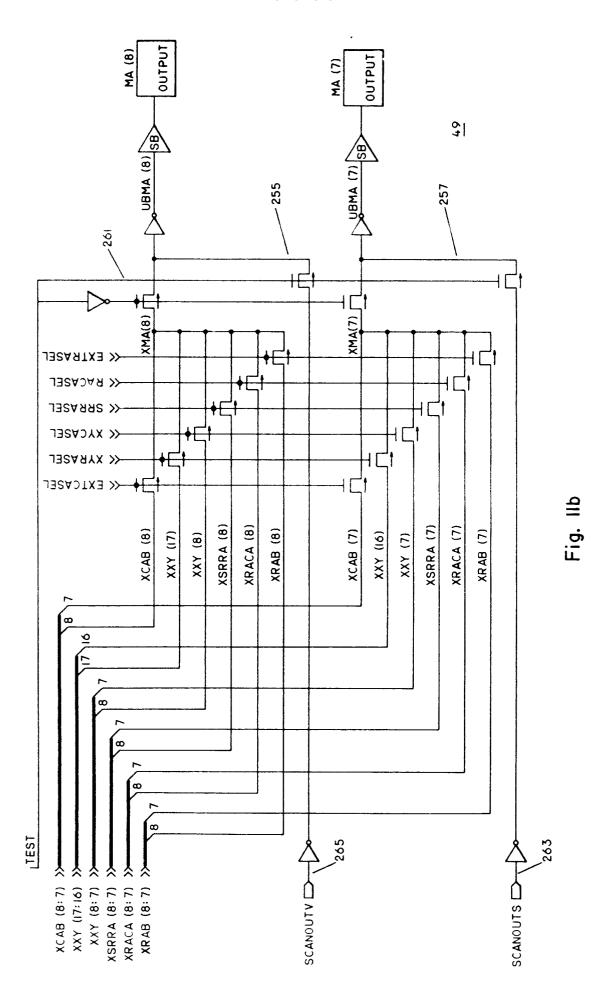

Figure 11 is a schematic diagram of Figure 7;

Figure 12 is a schematic diagram of mem pins block of Figure 4;

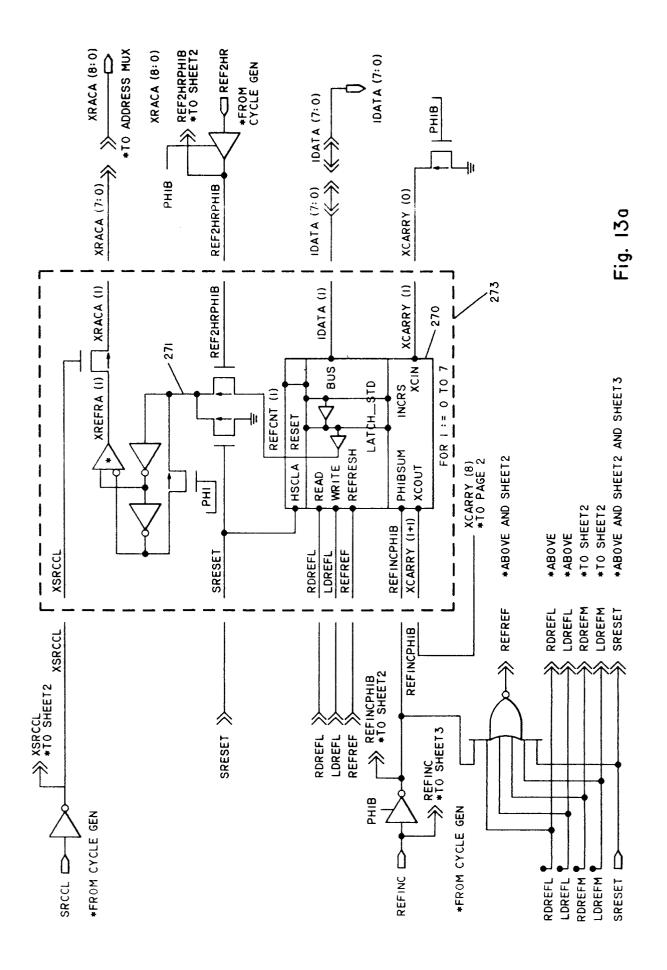

Figure 13 is a schematic diagram of the refresh block of Figure 4;

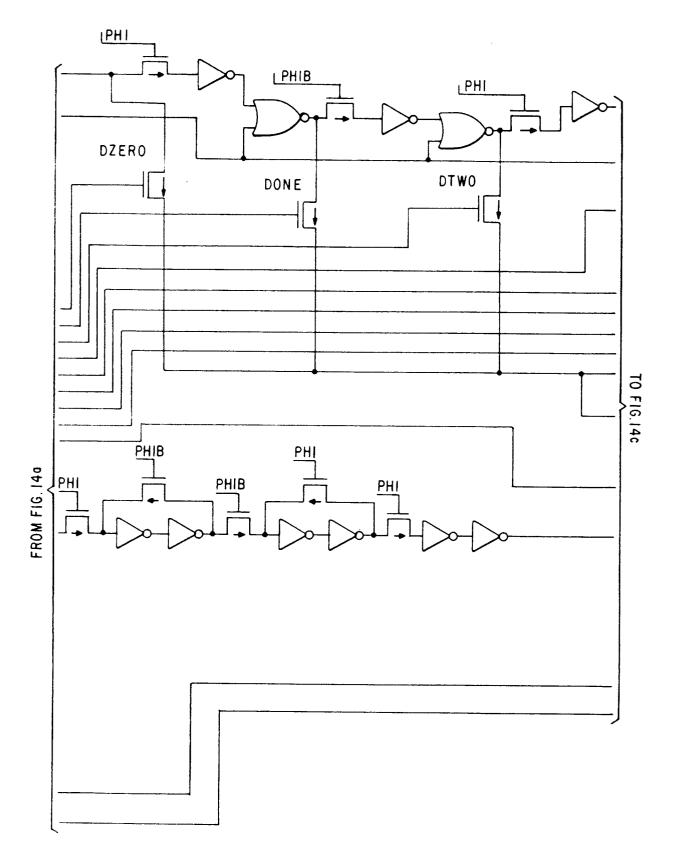

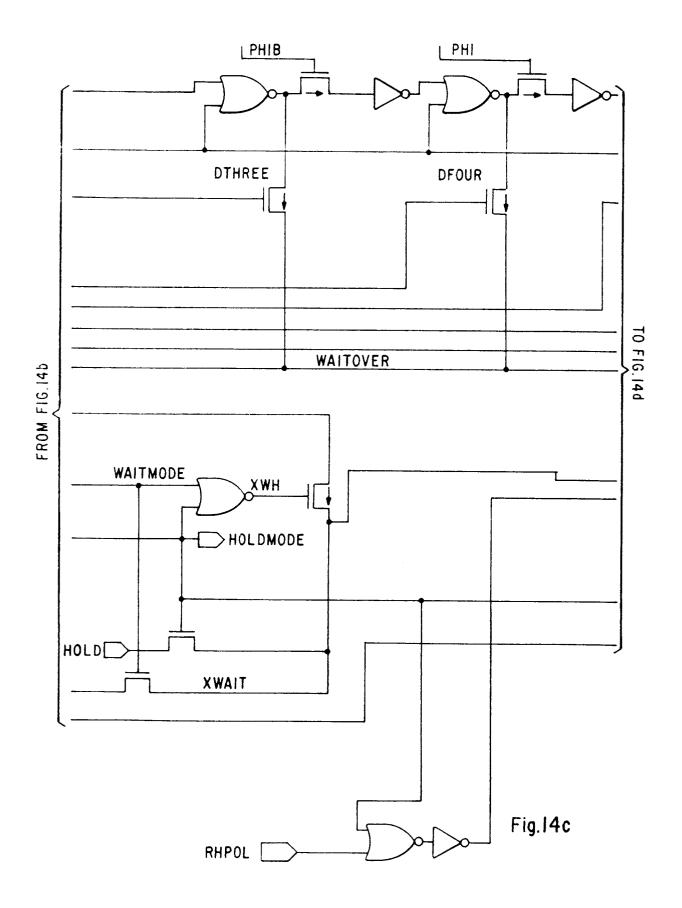

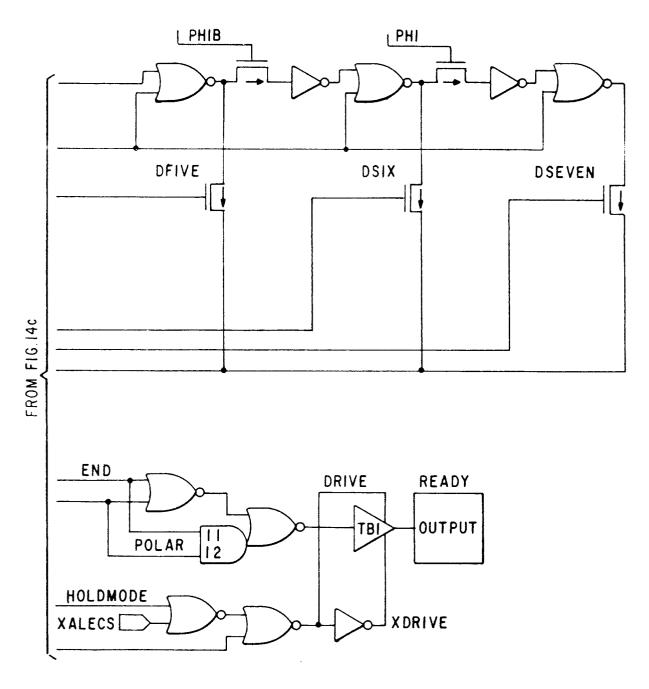

Figure 14 is a schematic diagram of ready hold block of Figure 4;

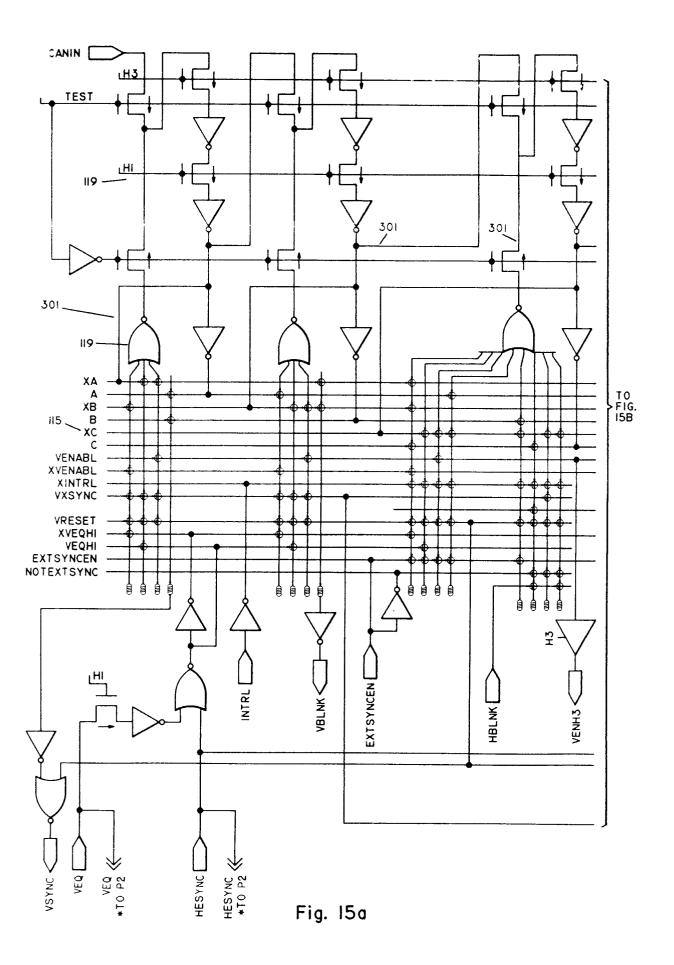

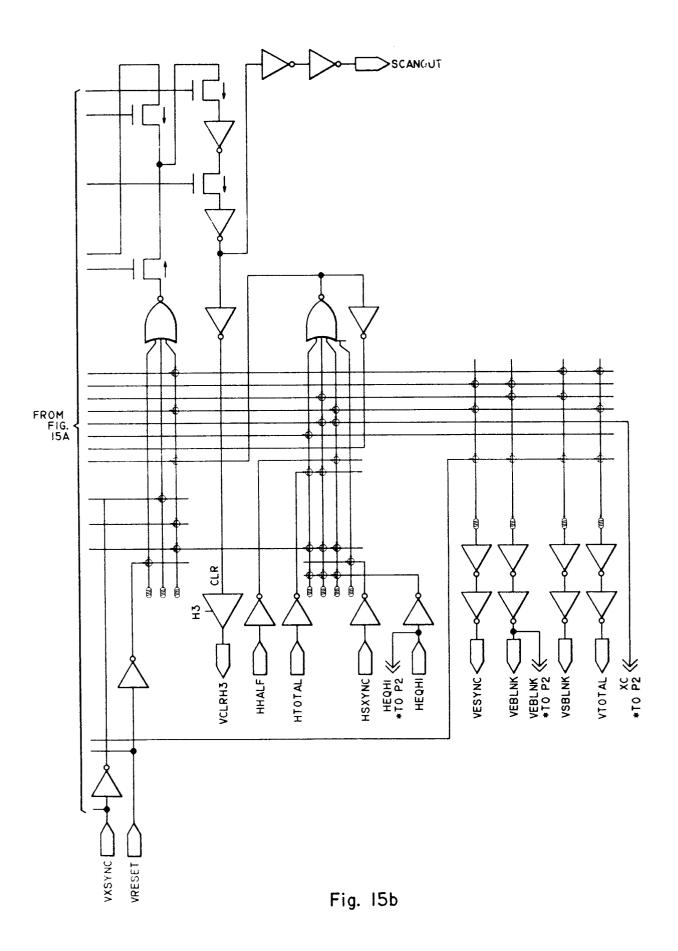

Figure 15 is a schematic diagram of the video block of Figure 7;

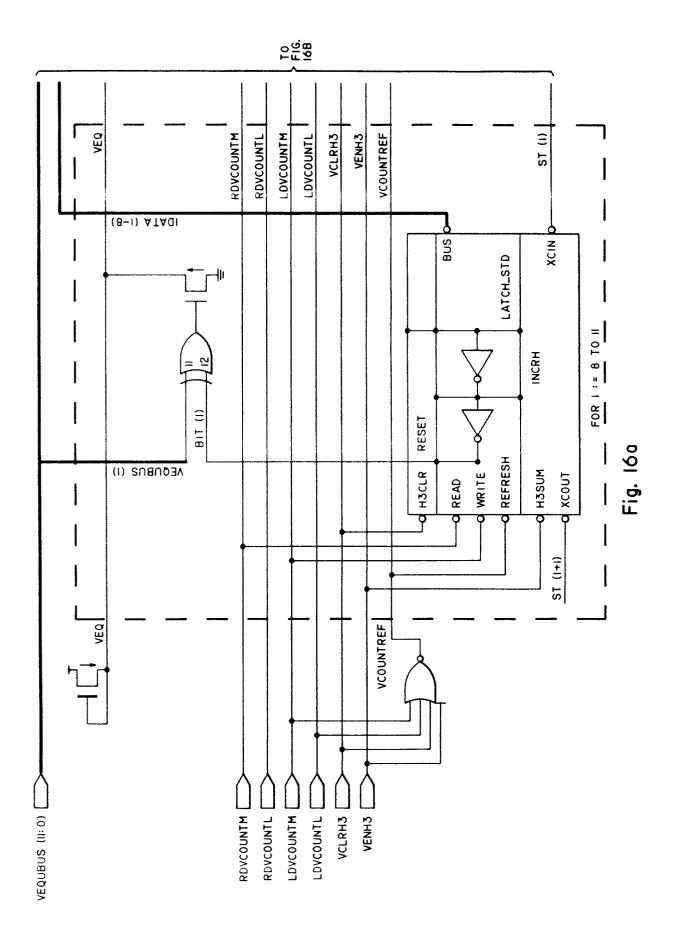

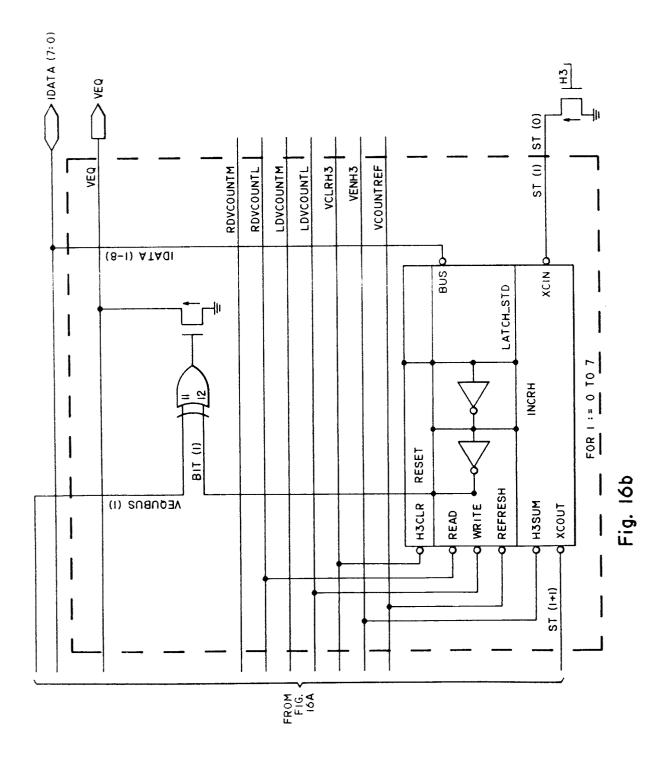

Figure 16 is a schematic diagram of the vertical counter of Figure 7;

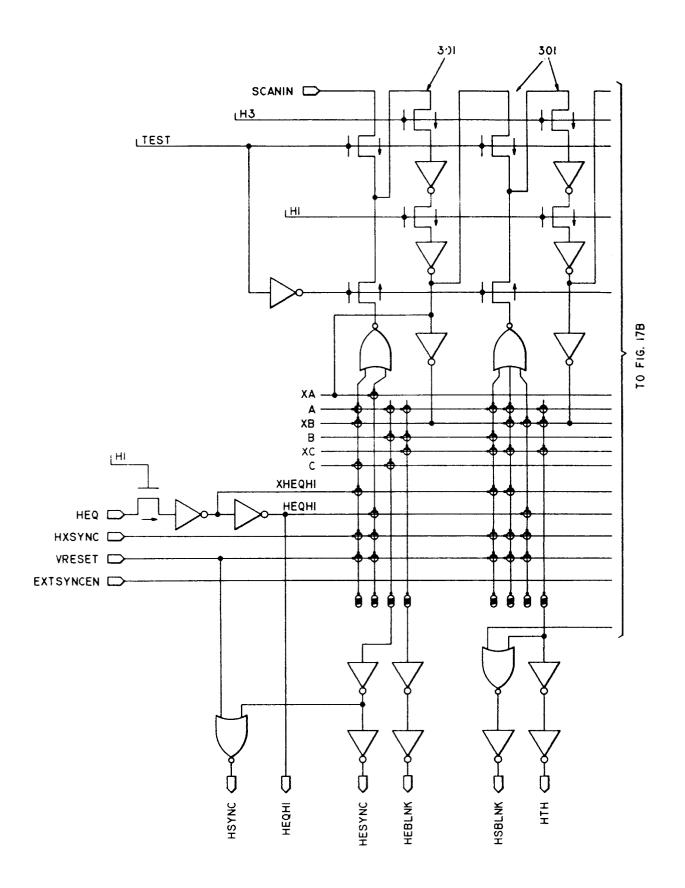

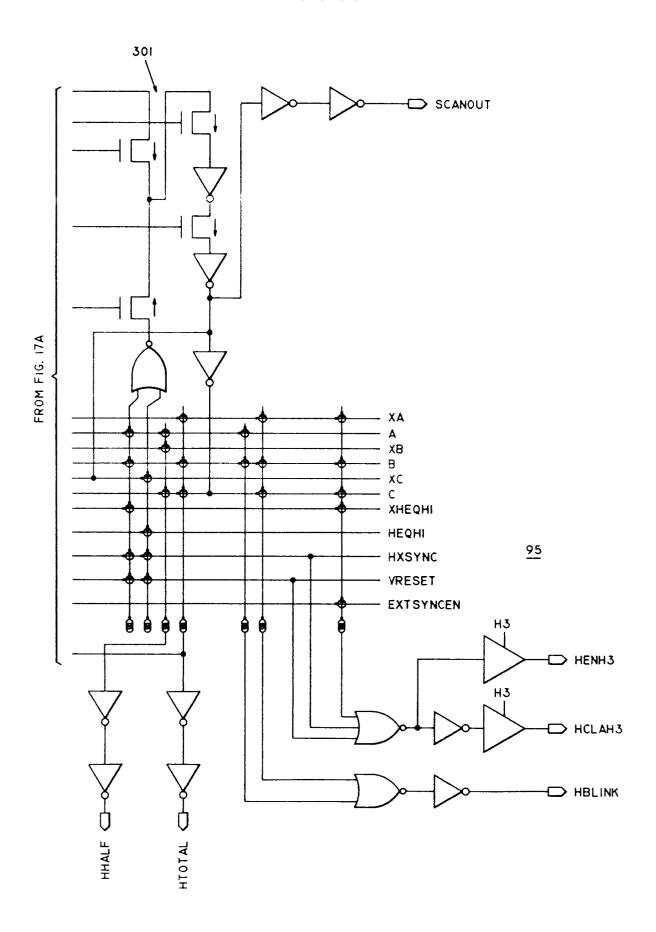

Figure 17 is a schematic diagram of the horizontal counter of Figure 7;

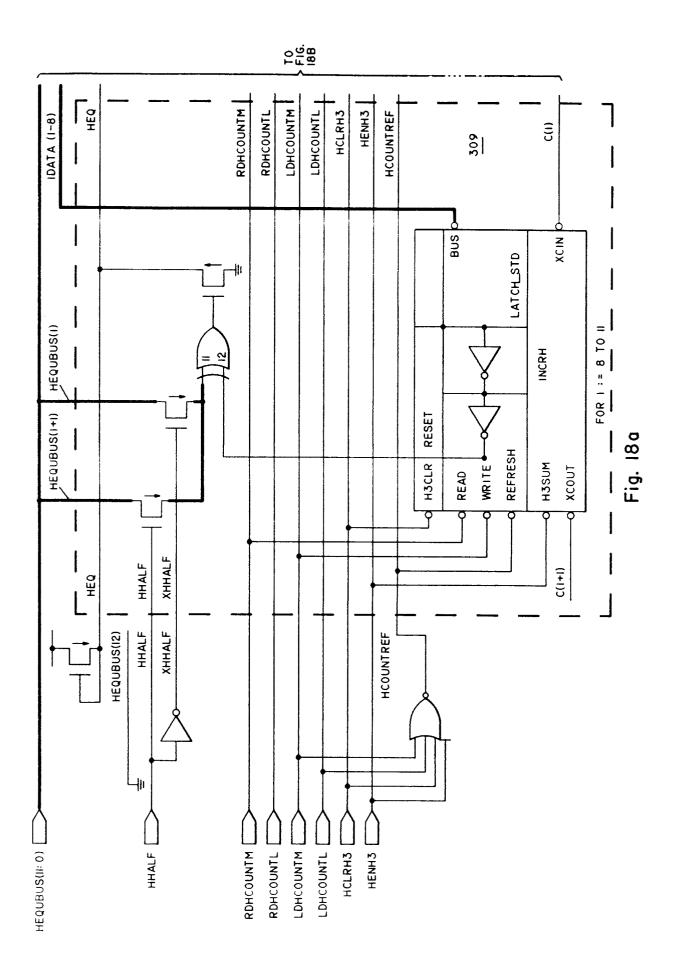

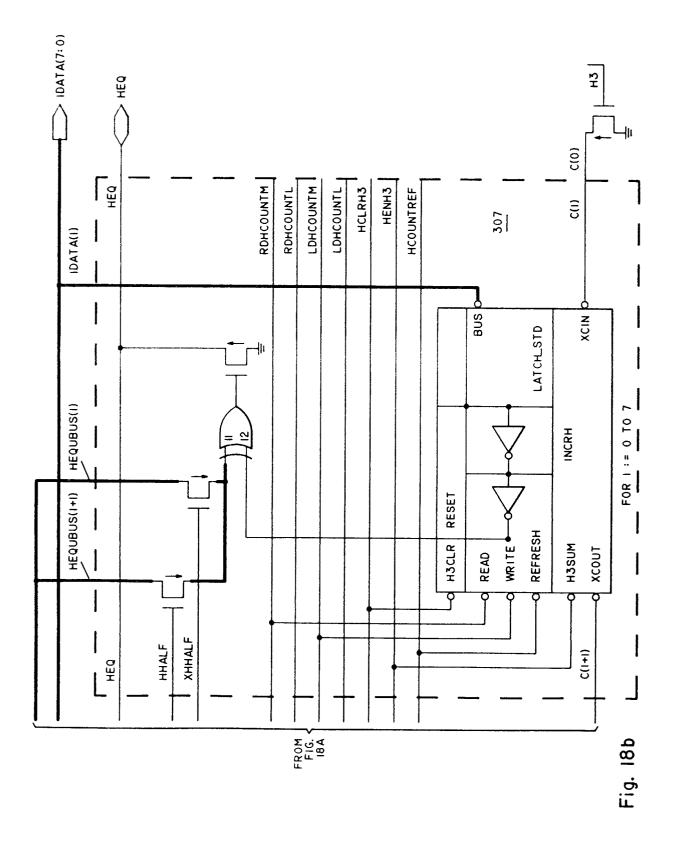

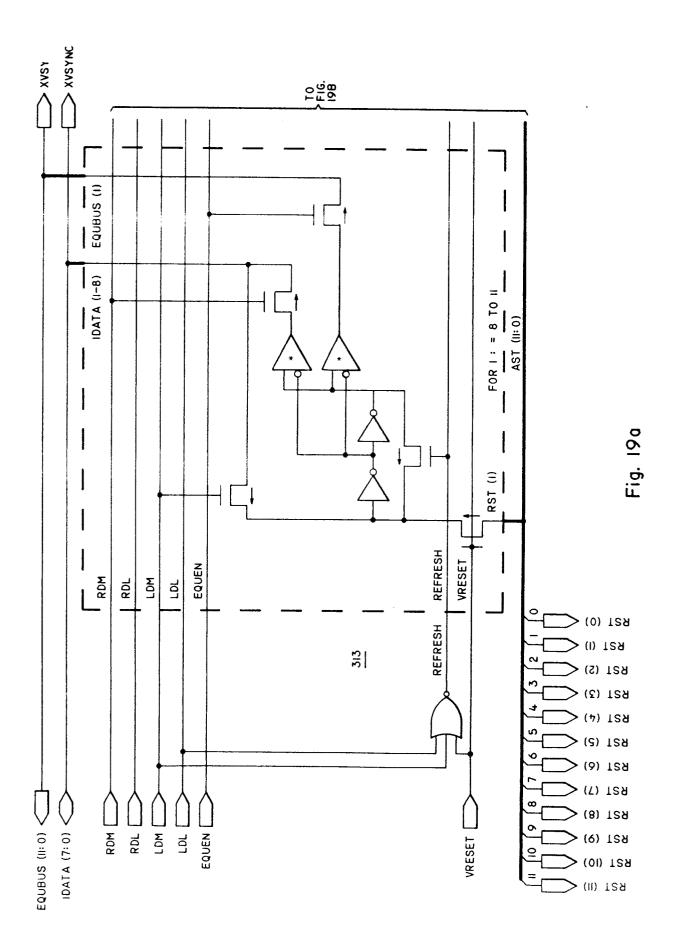

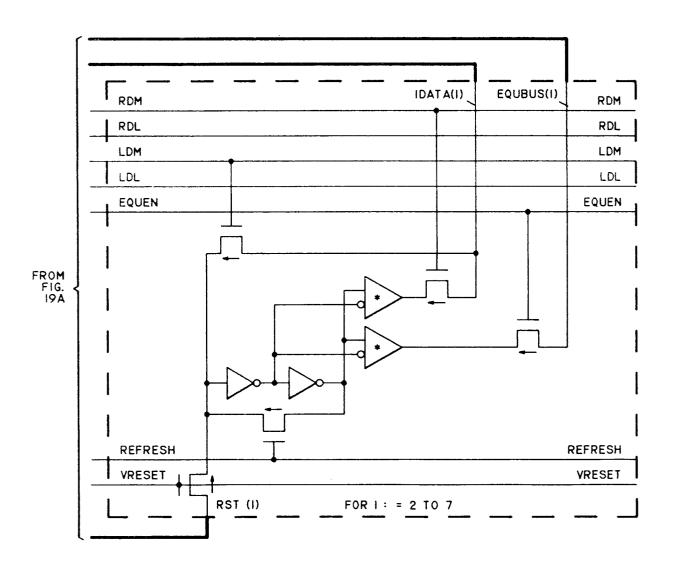

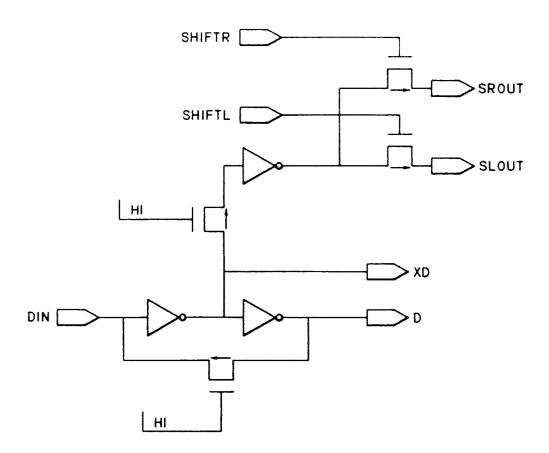

Figure 18 is a schematic diagram of the horizontal counter of Figure 7; Figure 19 is a schematic diagram of the basic register

used in Figures 16, 17 and 18;

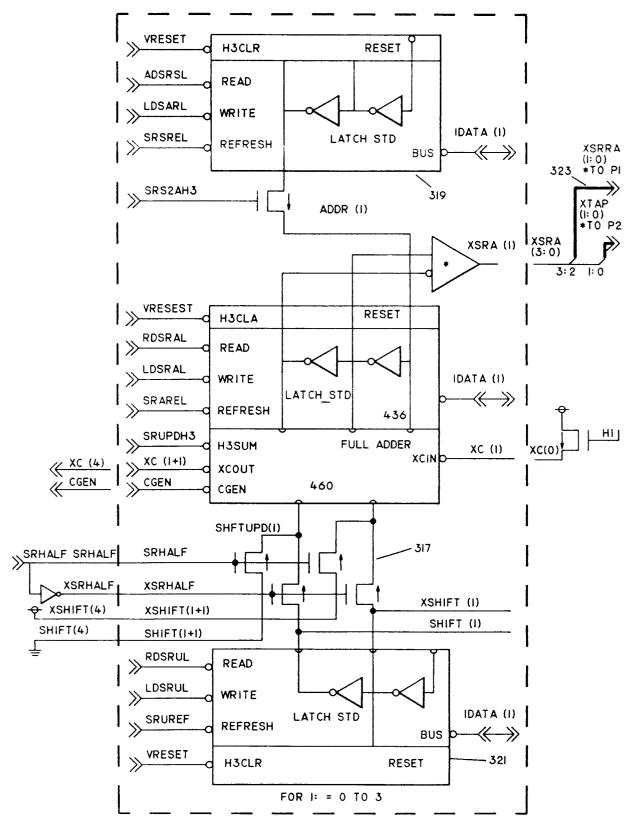

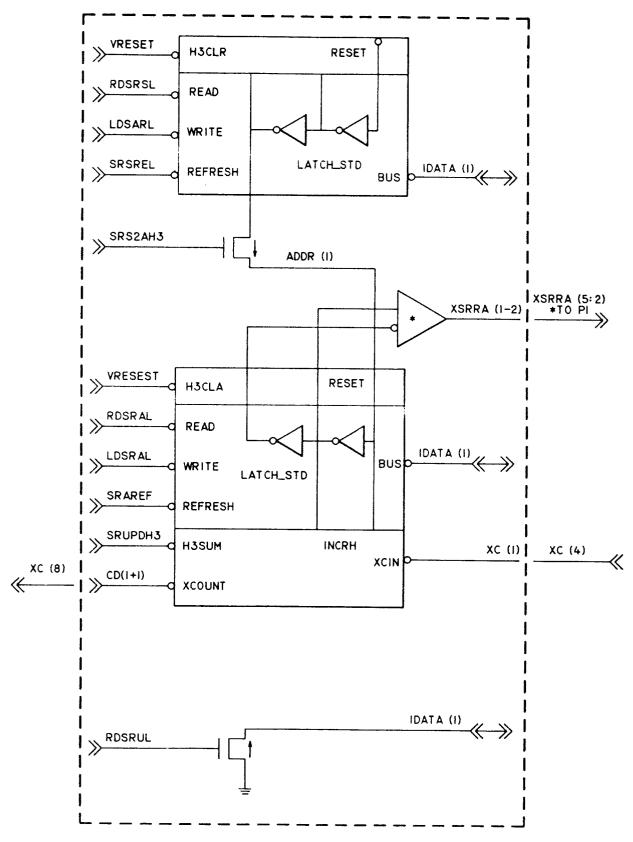

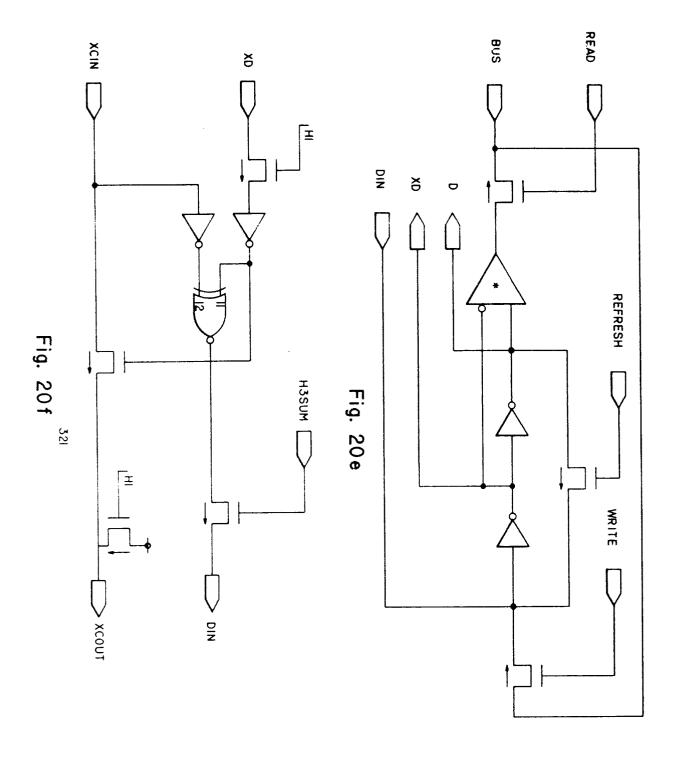

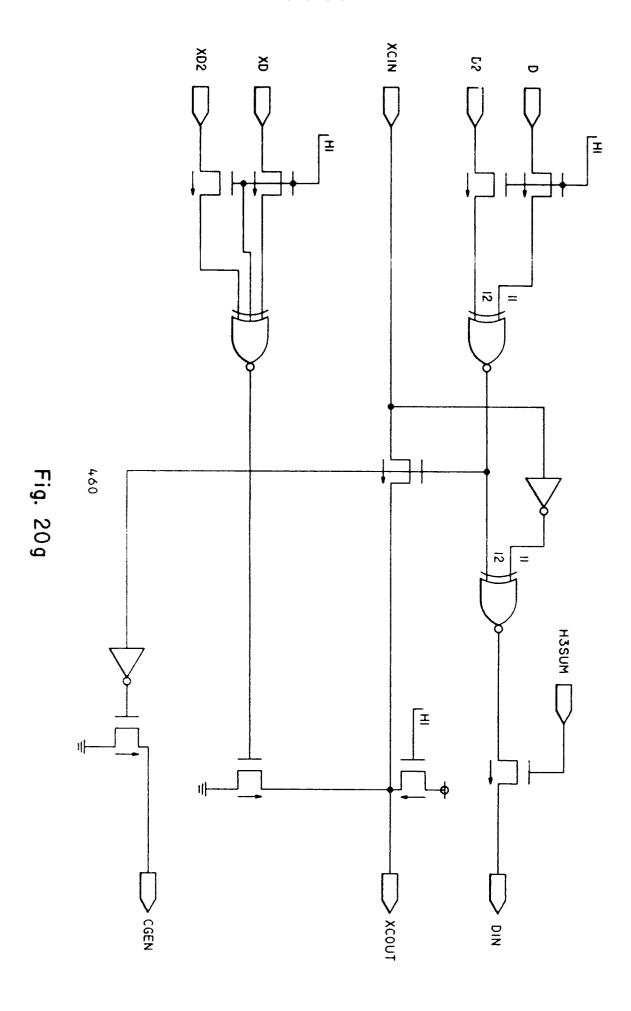

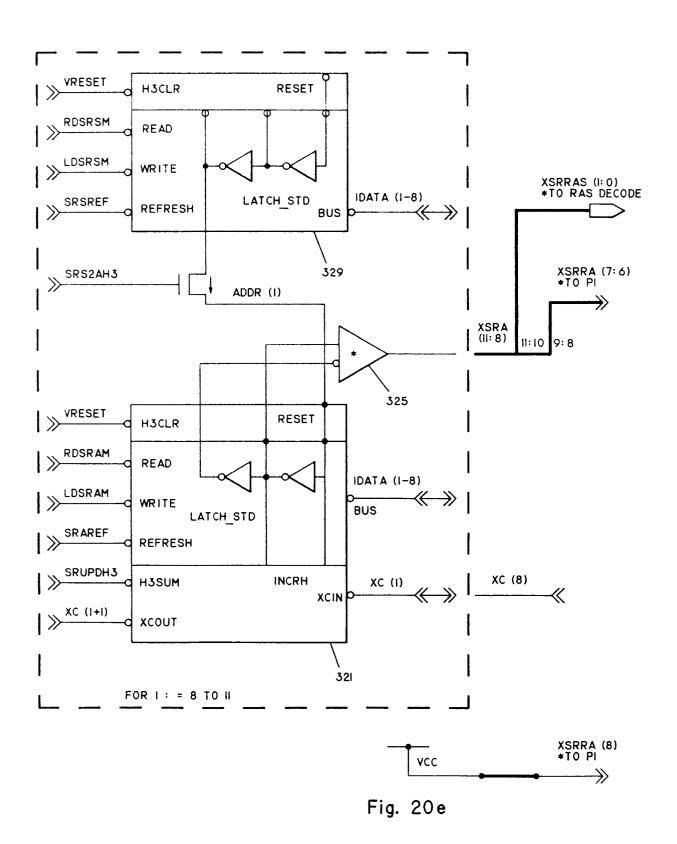

Figure 20 is a schematic diagram of the SRDAT block of Figure 7;

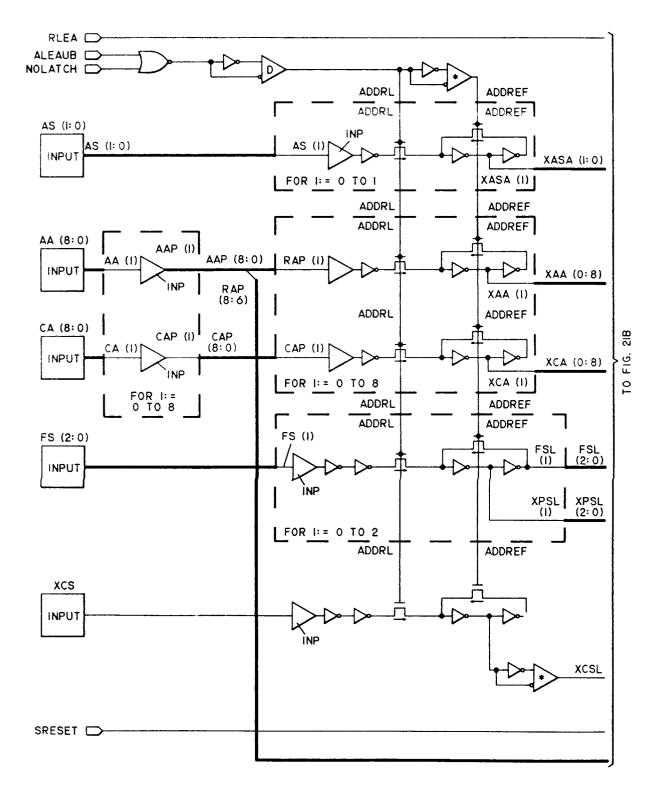

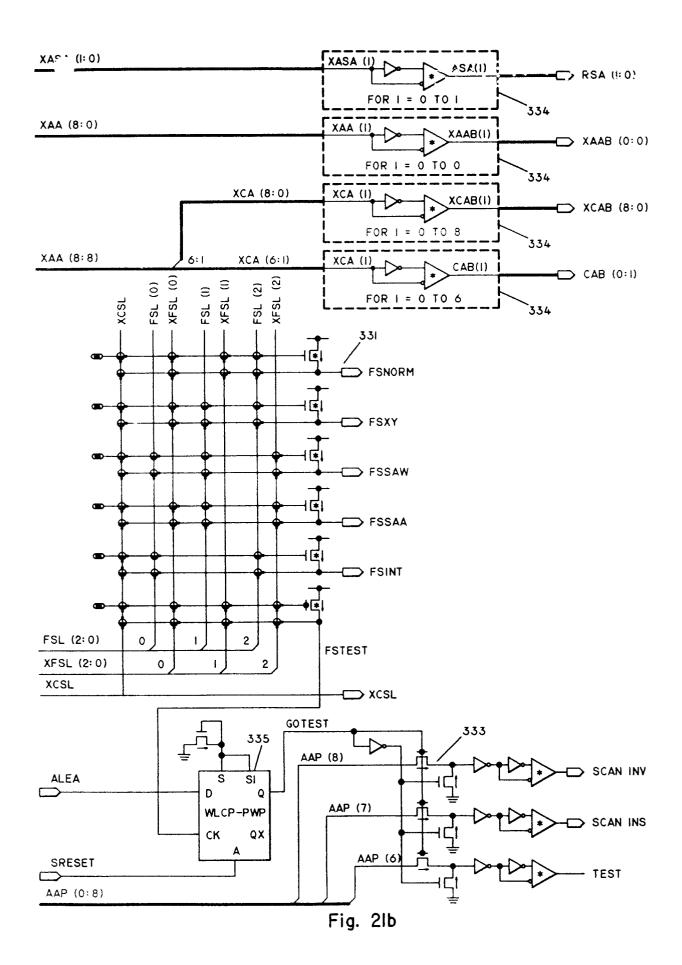

Figure 21 is a schematic diagram of the FS decode block of Figure 3;

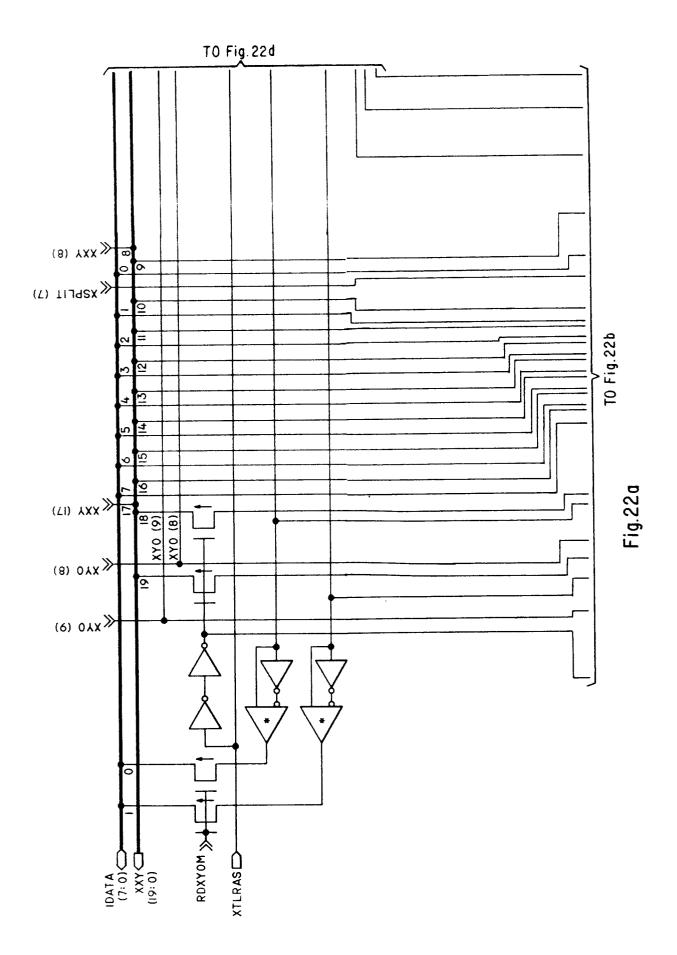

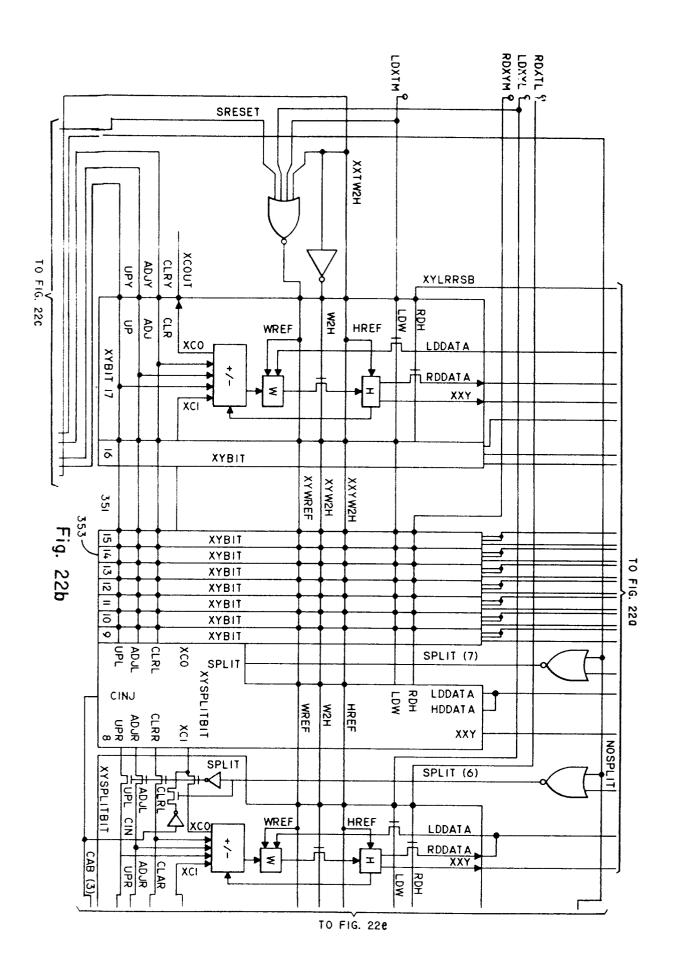

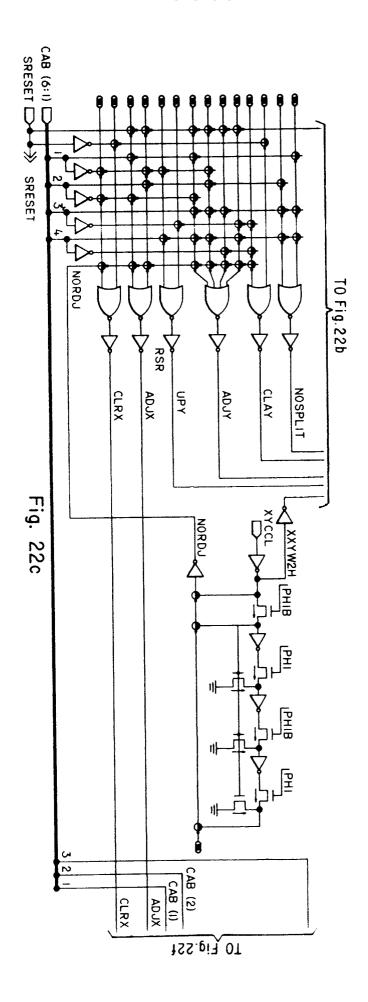

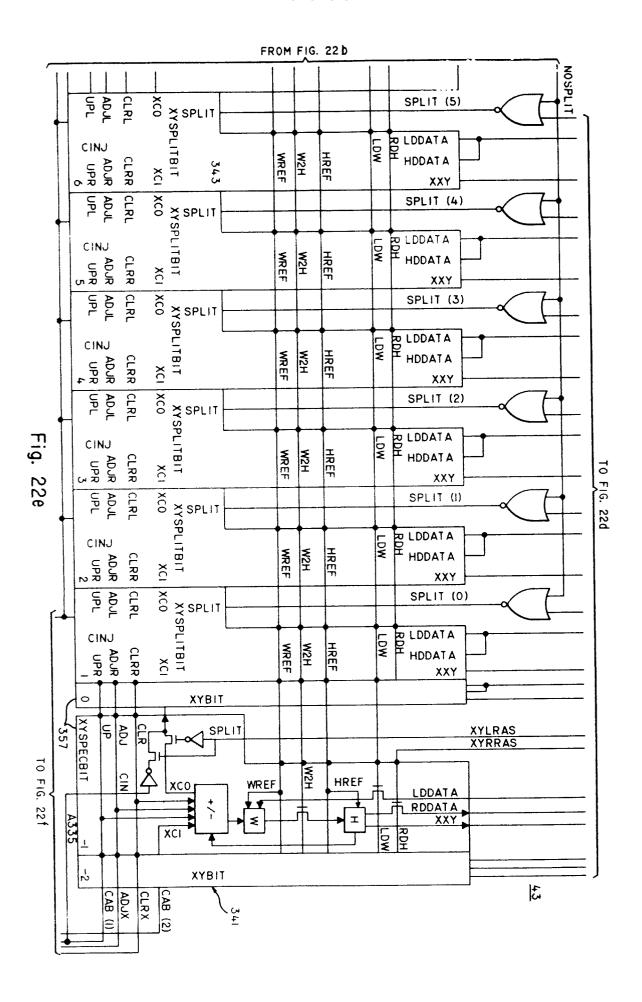

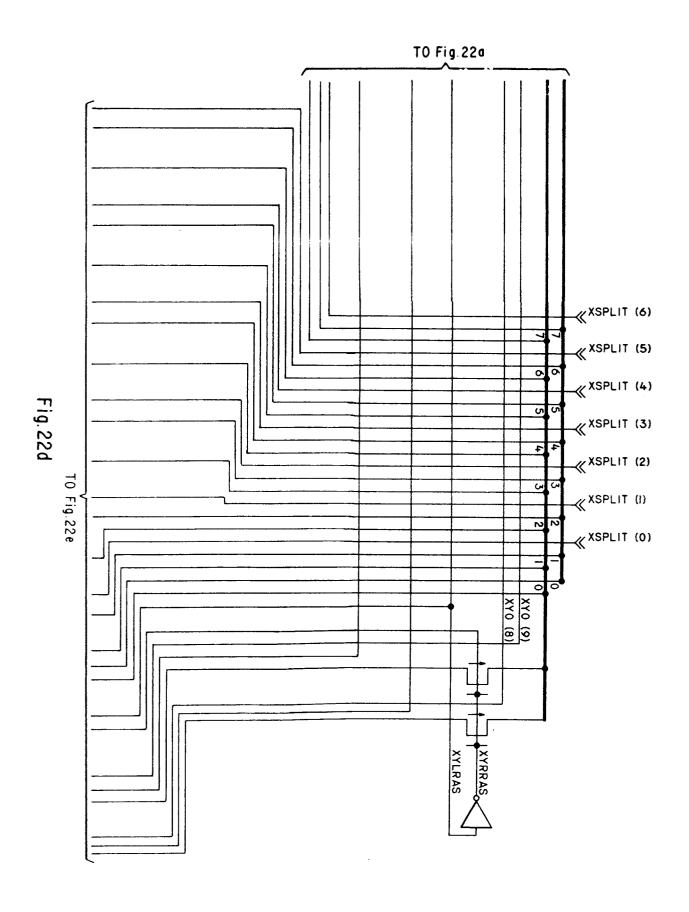

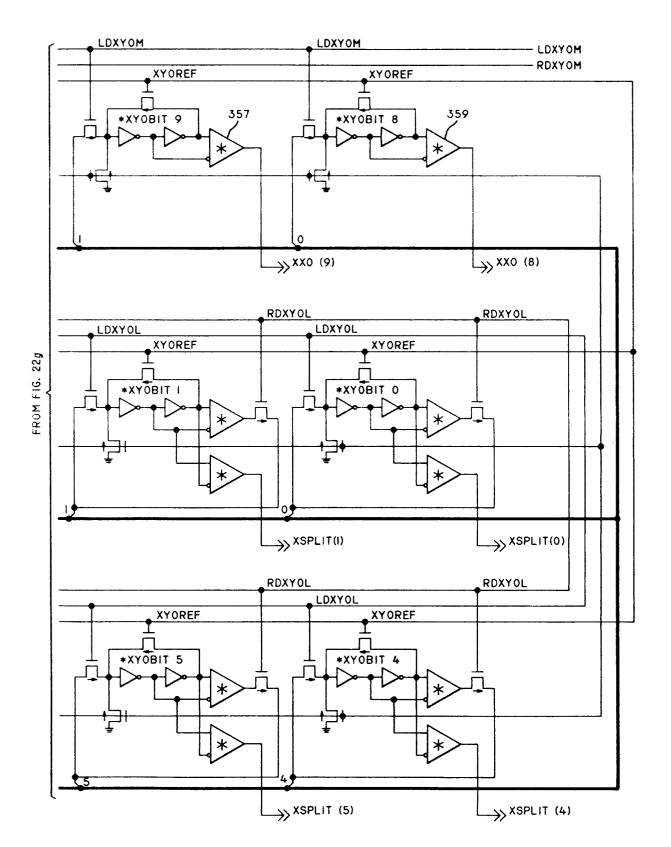

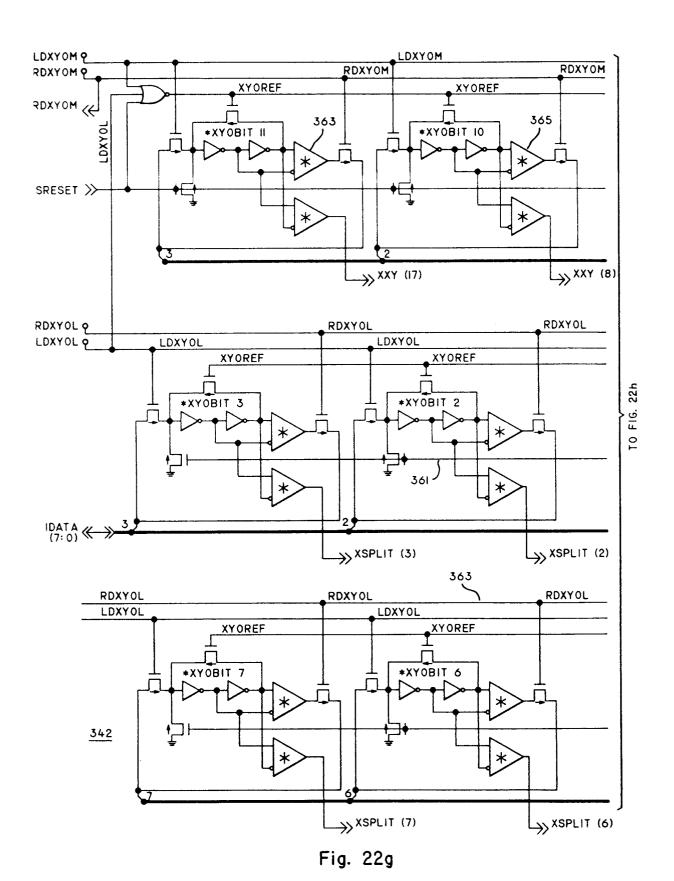

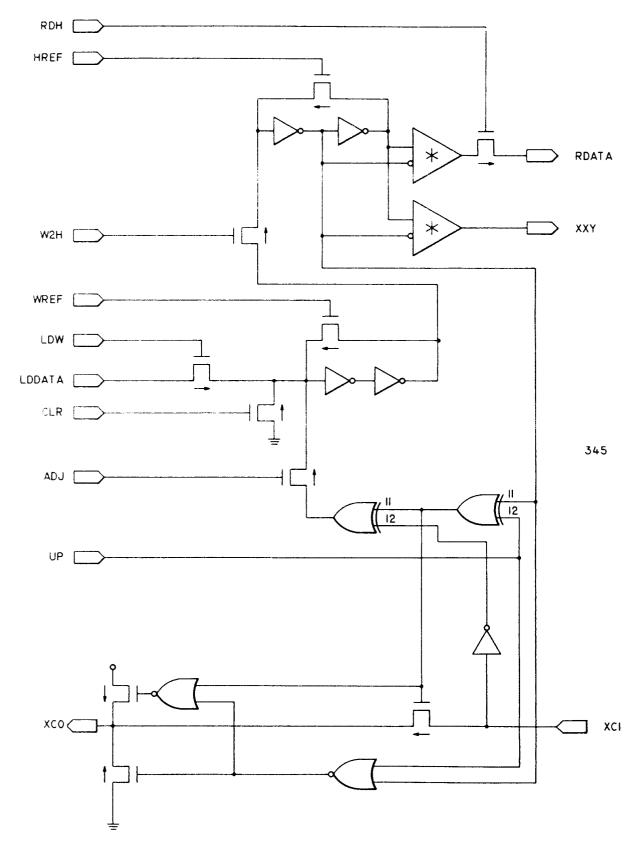

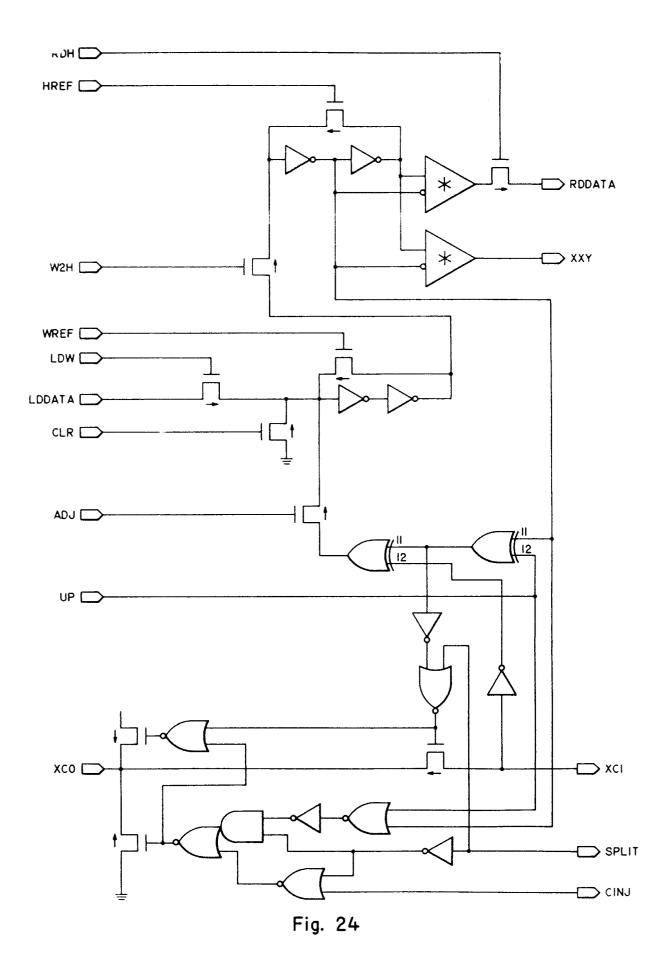

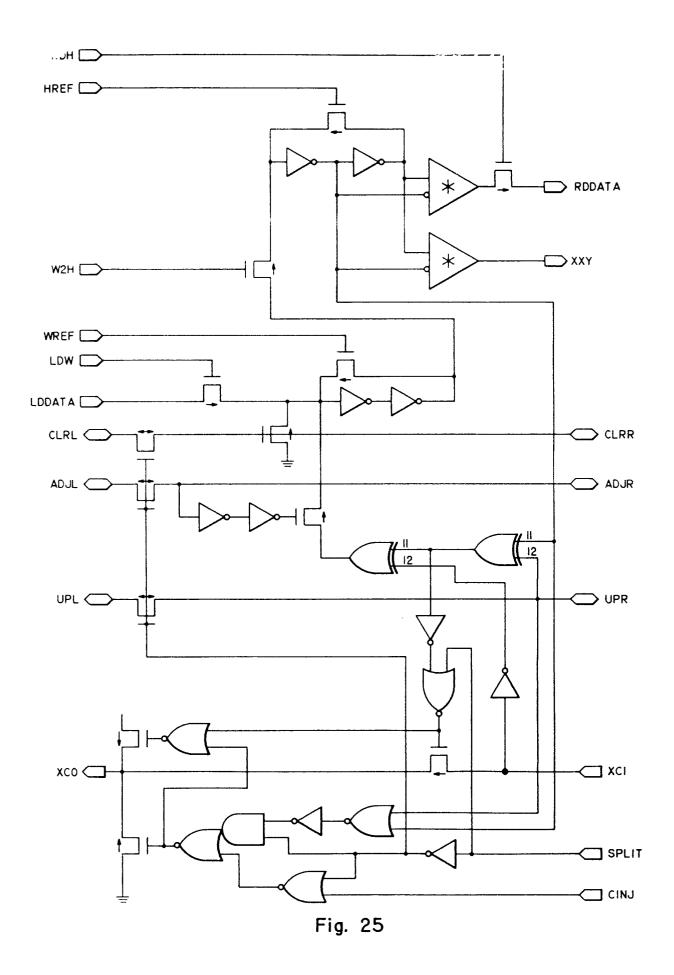

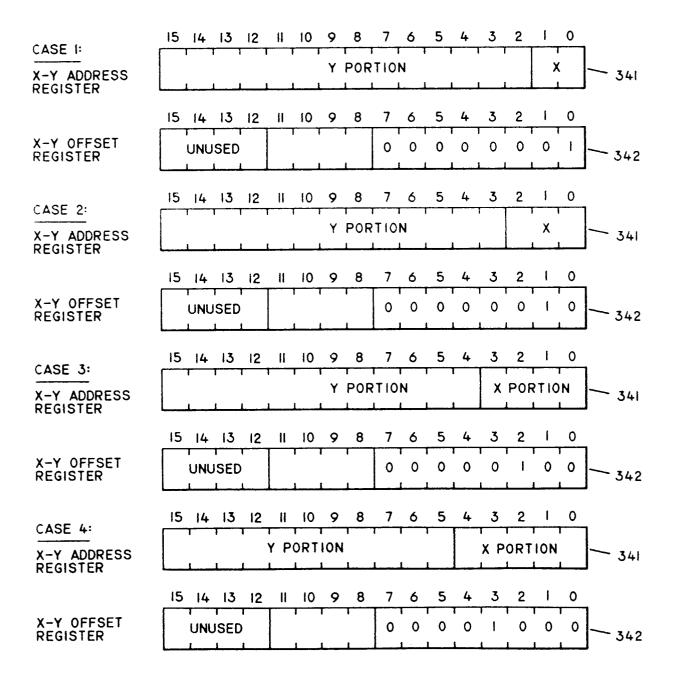

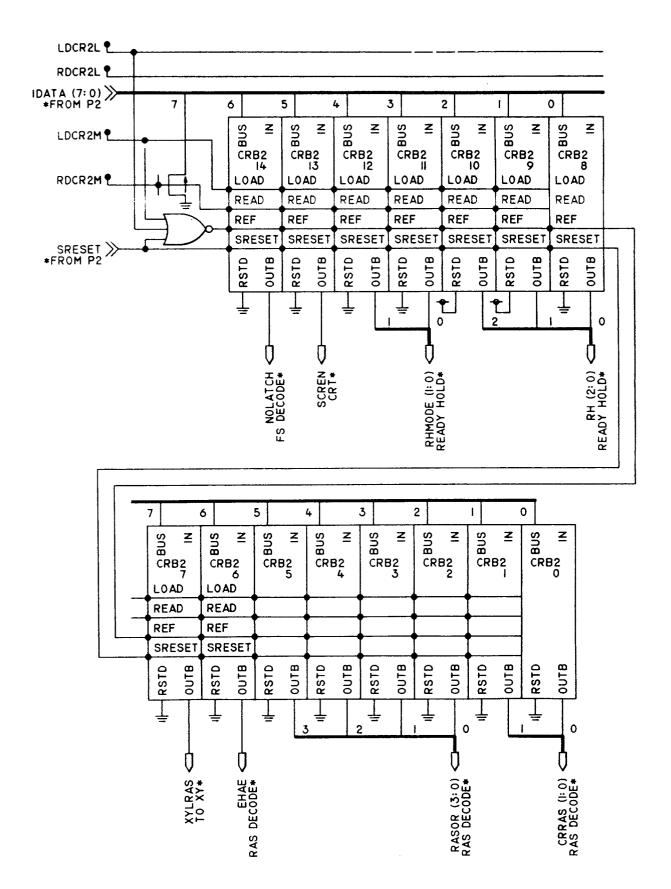

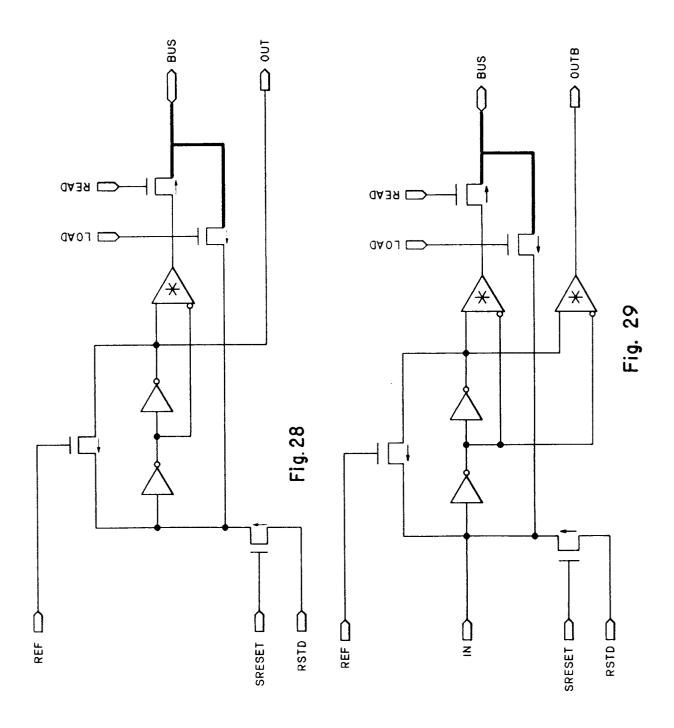

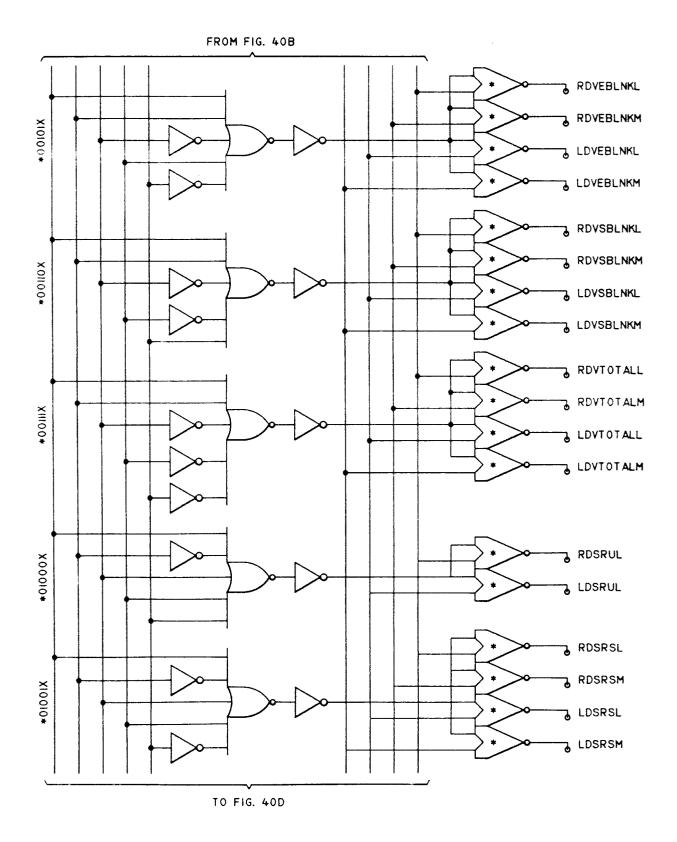

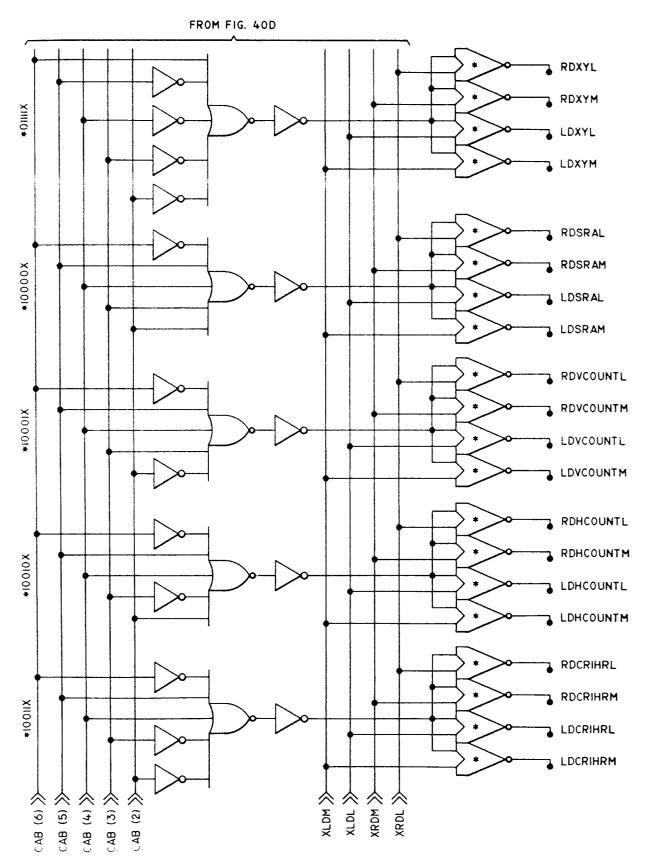

Figures 22 through 26 are schematic diagrams of the XY register block of Figure 3;

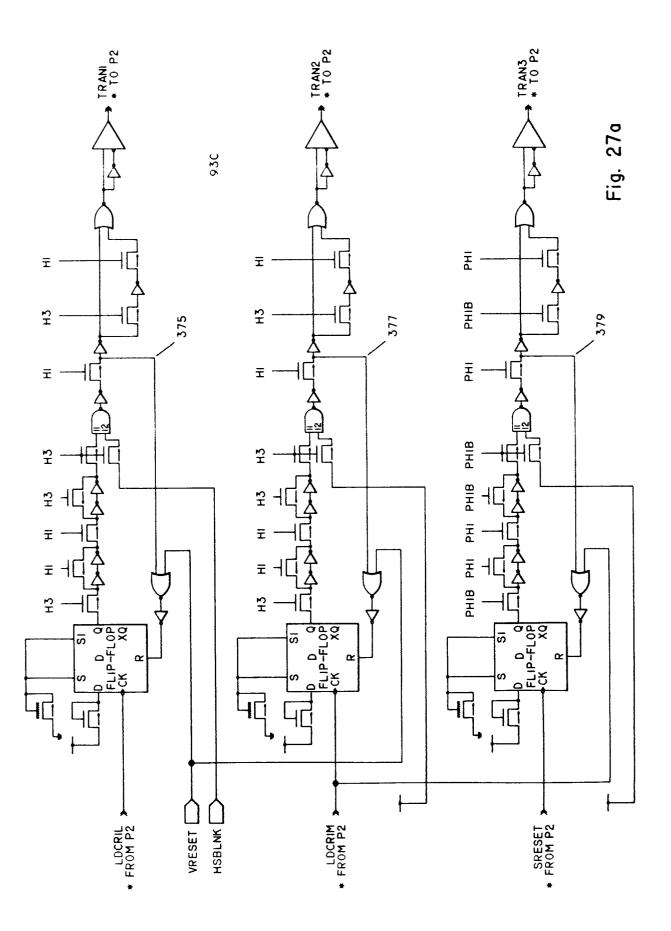

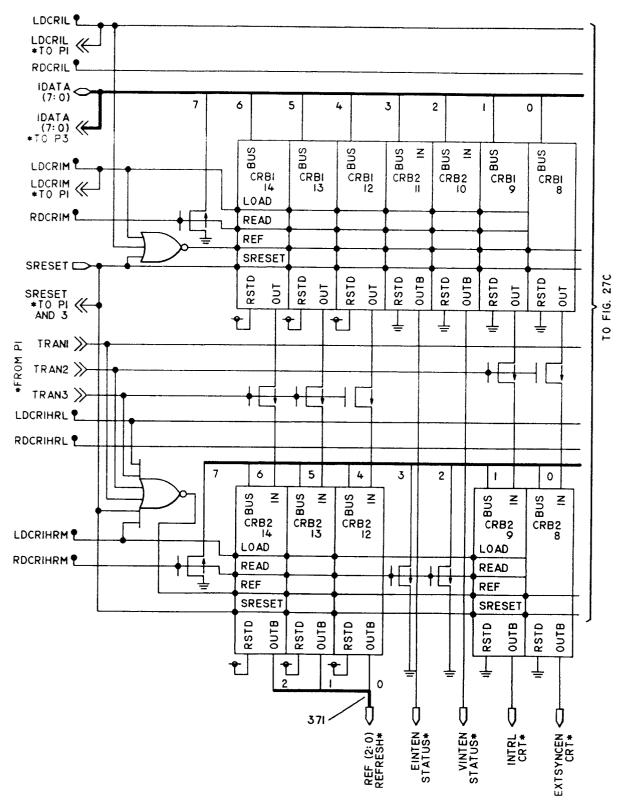

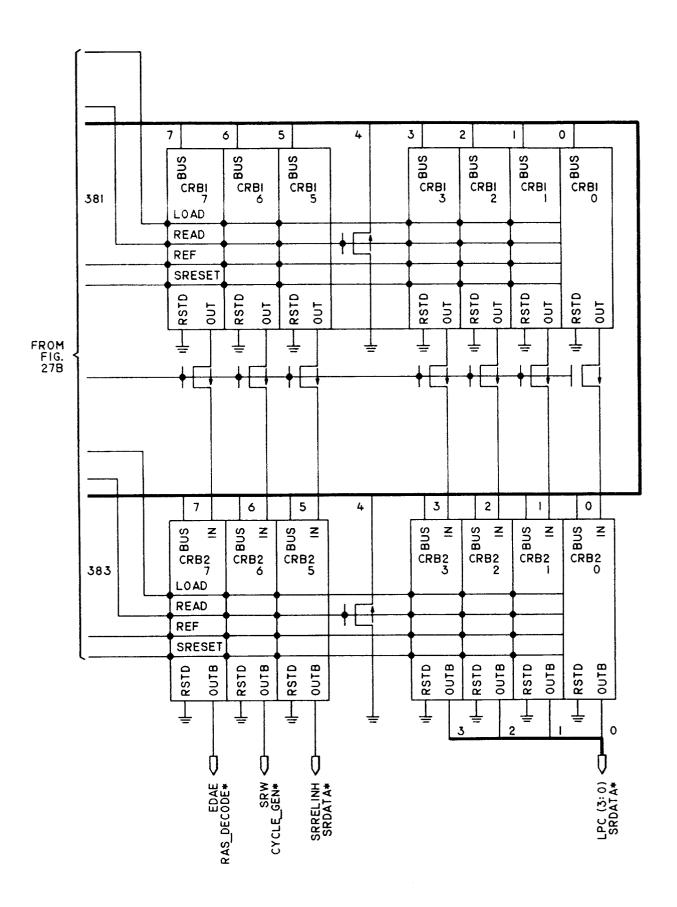

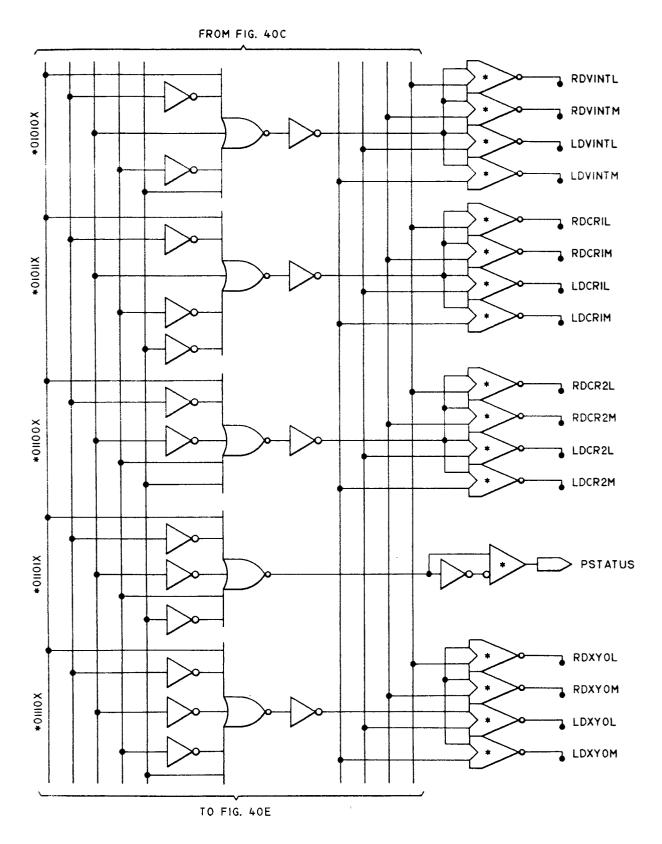

Figures 27 through 29 are schematic diagrams of the cont reg block of Figure 3;

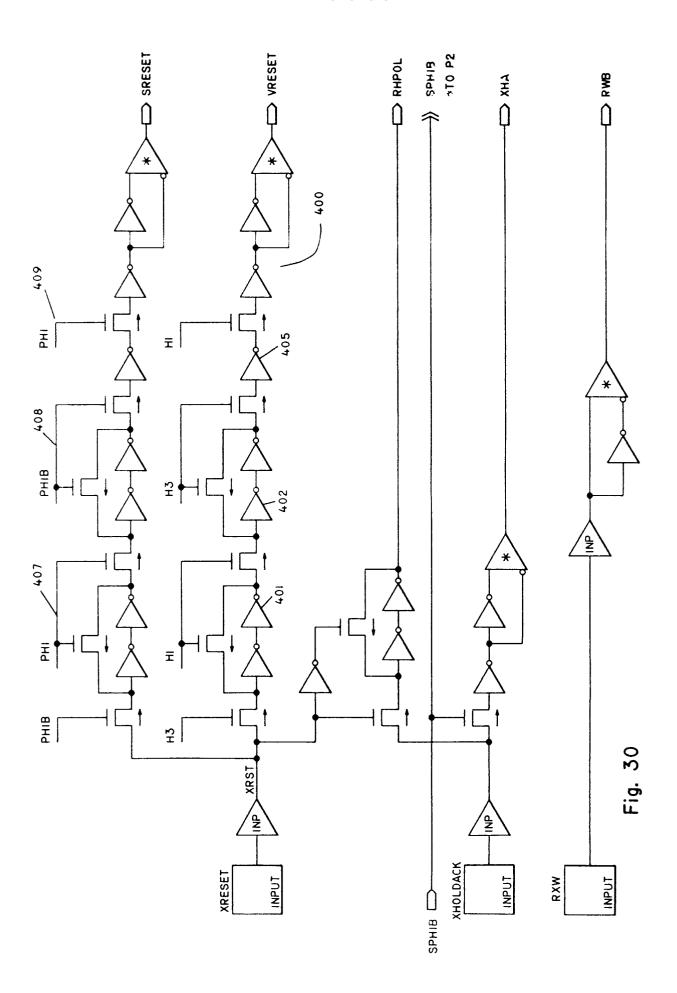

Figure 30 is a schematic diagram of the input pins block of Figure 3;

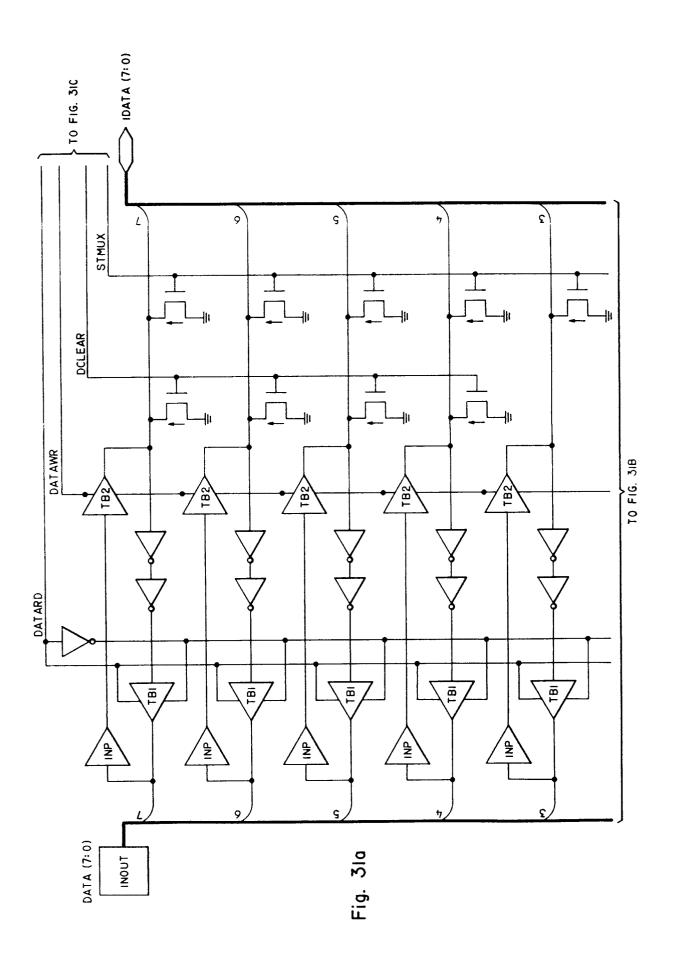

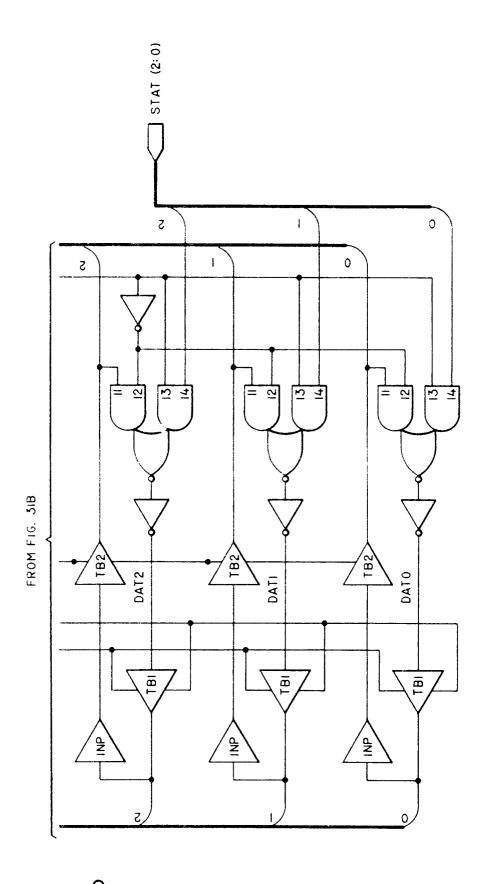

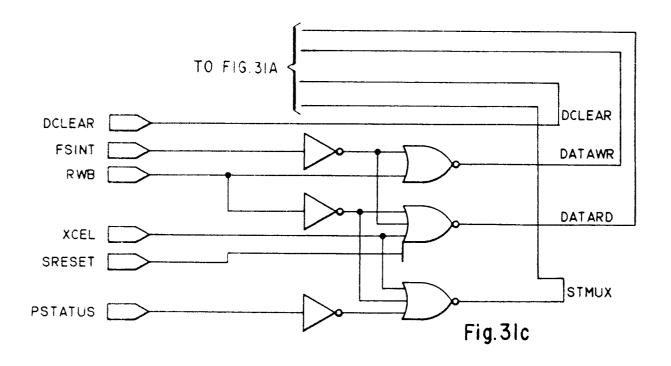

Figure 31 is a schematic diagram of the data pins block of Figure 3;

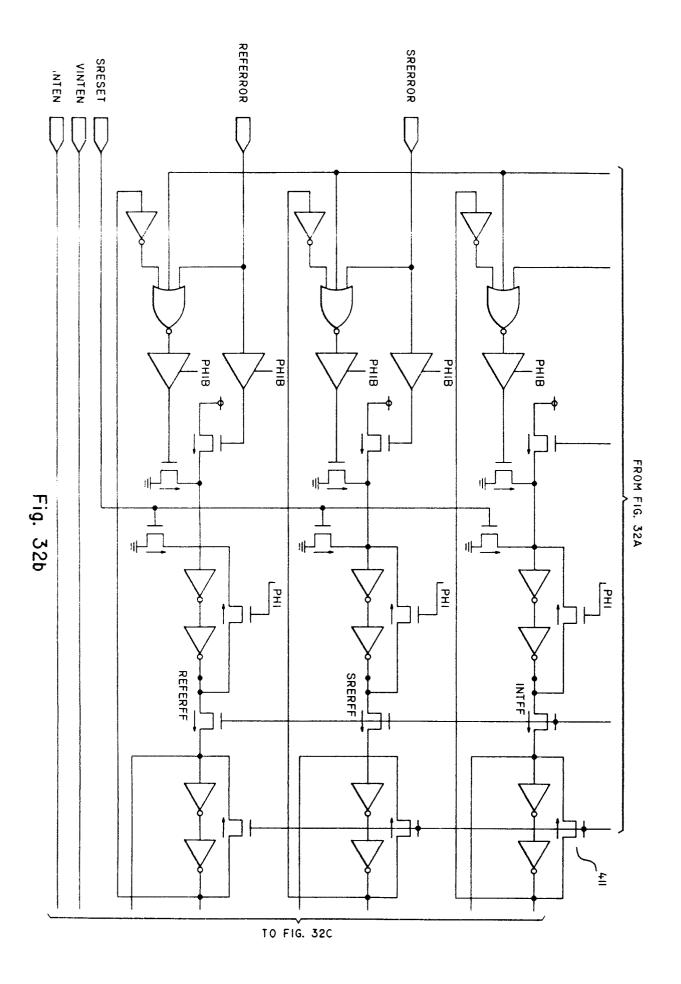

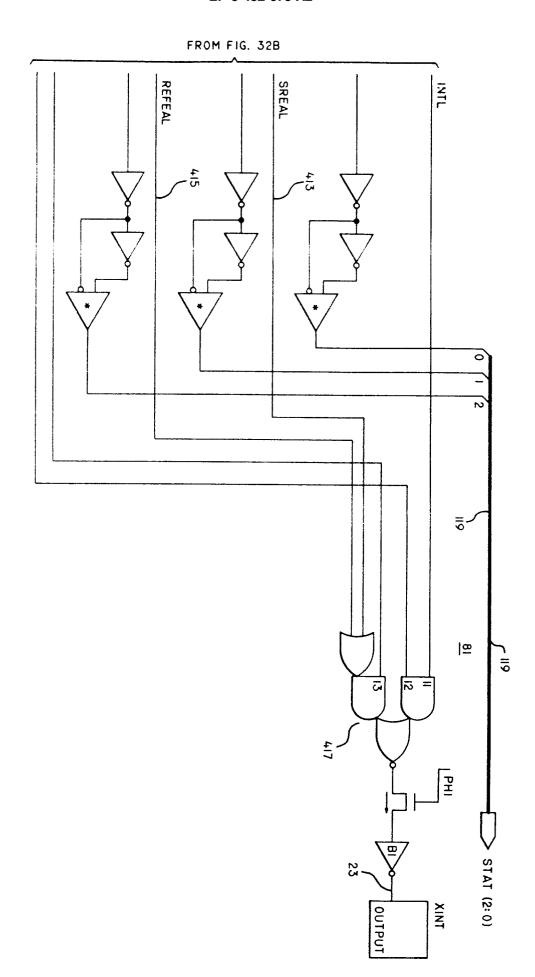

Figure 32 is a schematic diagram of the data state block of Figure 3;

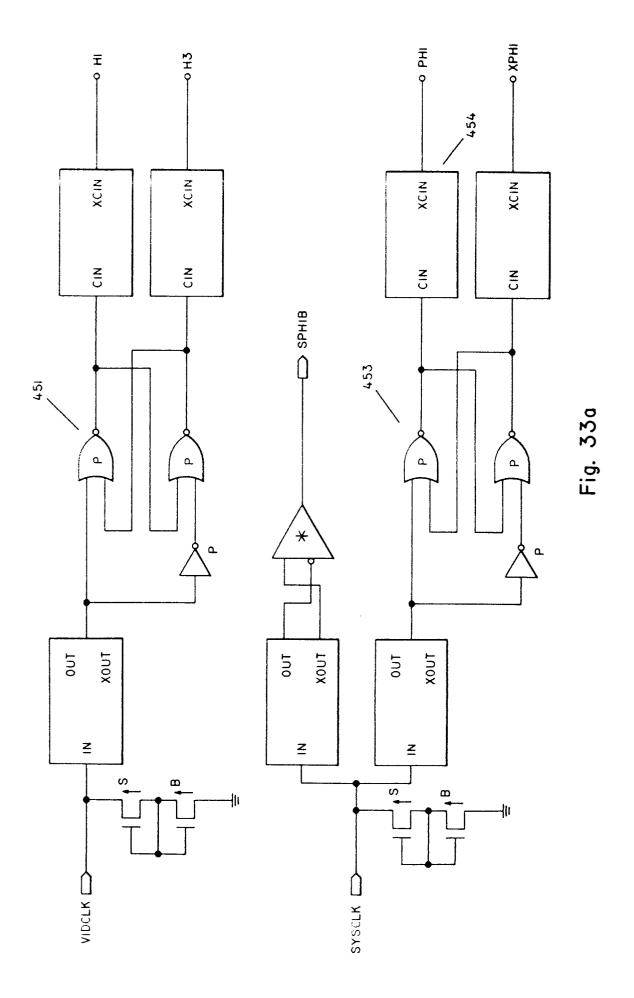

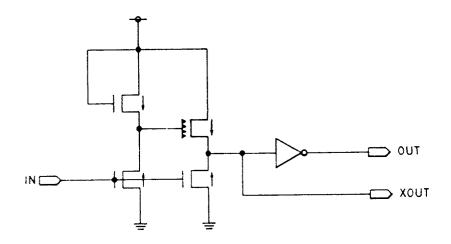

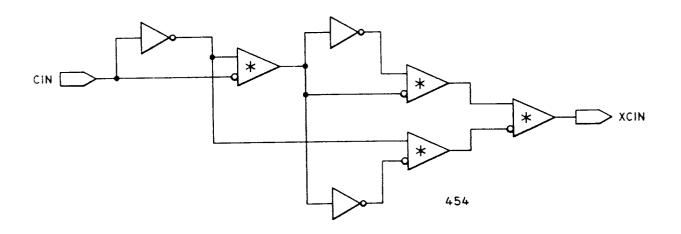

40 Figure 33 is a schematic diagram of the dual clocks used in the video system controller;

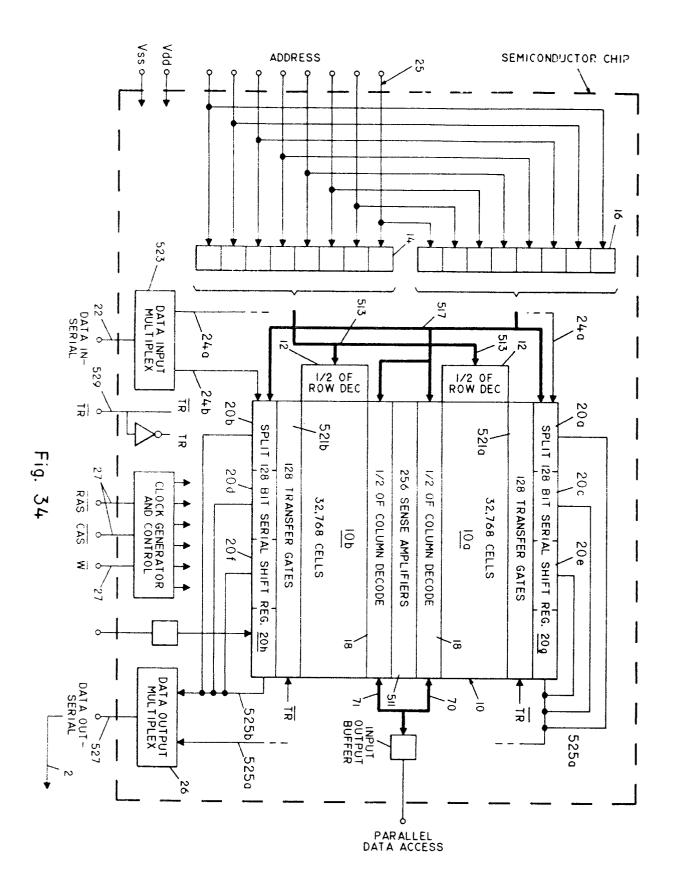

Figure 34 is a schematic diagram of one embodiment of the display memory;

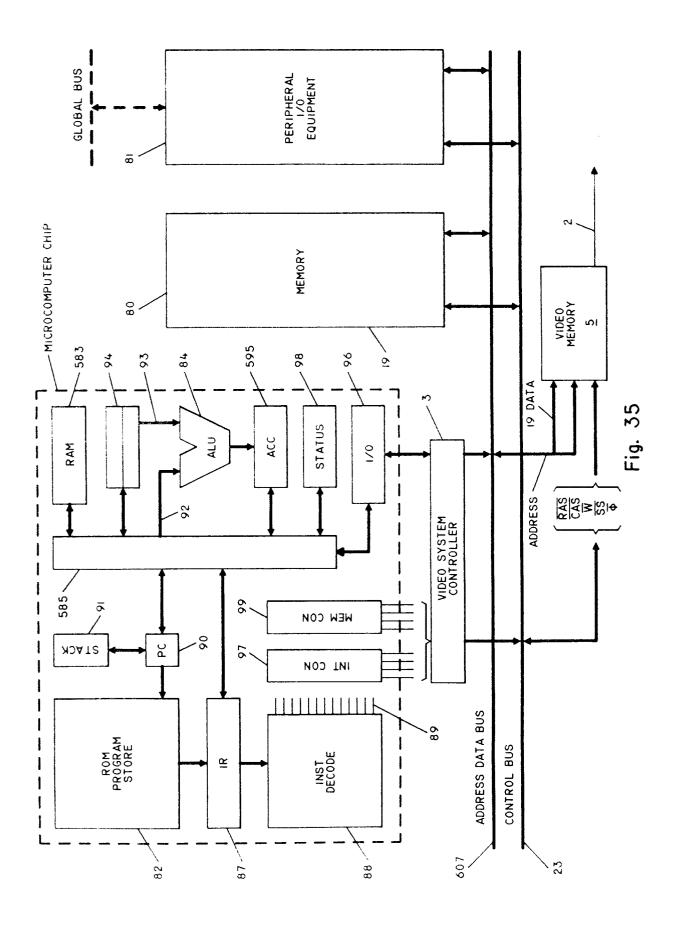

Figure 35 is a block diagram of a microprocessor of Figure 1;

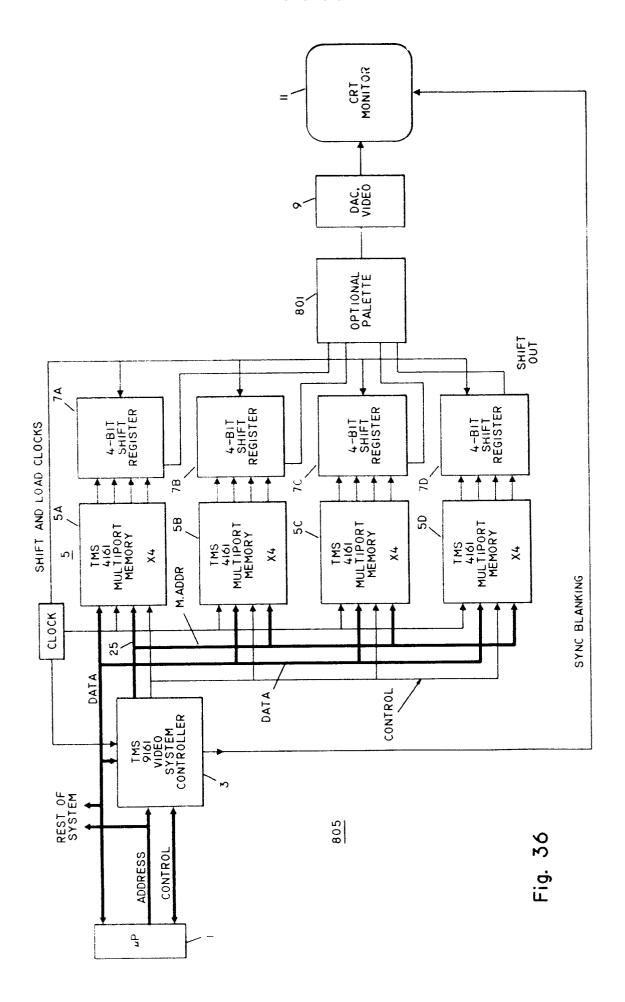

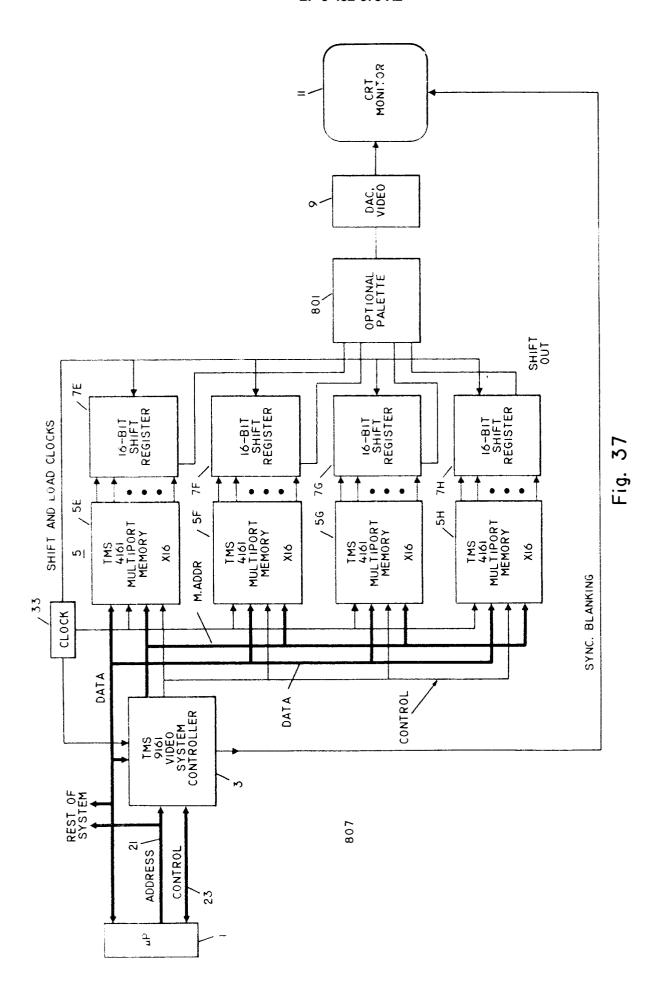

Figures 36 and 37 are alternative embodiments of a video system; and

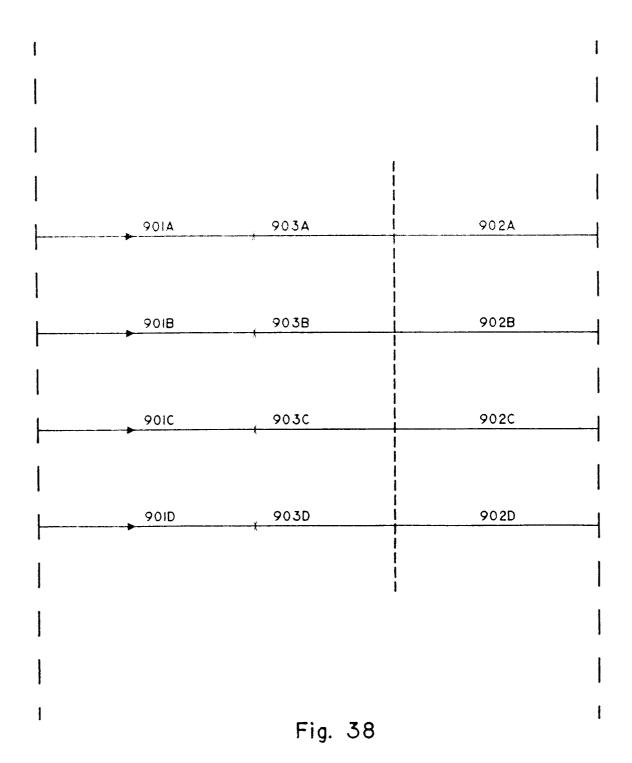

Figure 38 is a diagram of the data transfer cycle.

45

5

10

25

### DETAILED DESCRIPTION OF SPECIFIC EMBODIMENT

In Figure 1, to which reference should now be made, there is a block diagram of an embodiment of the video system controller according to the invention. The blocks that are shown in Figure 1 include a microprocessor 1, a video system controller 3, a display memory 5 such as that disclosed in U.S. Application 567,040 assigned to assignee of the present invention and incorporated herein by reference. The Output of the display memory 5 is connected to a shift register 7 which shifts data to an optional digital to analog converter 9 for application to an appropriate monitor or television display 11 or other output or input device via bidirectional data bus 9A. Additionally, a system dynamic RAM 19 is provided for the storage of data and/or instructions for processing by a microprocessor 1. The microprocessor 1 contains data inputs from terminal 15 and applies the data to a bi-directional bus 17 which connects the microprocessor 1 to the video system controller 3, the display memory 5 and the system dynamic RAM 19. Additionally, the microprocessor provides address information to the video system controller 3 and to a

second terminal 19 which in conjunction with terminal 15 are connected to a port device such as a keyboard, as well as other peripheral devices which may be utilized by the system. The microprocessor 1 provides address information to the video system controller 3 via an address bus 21. The handling of the interface between the microprocessor 1 and video system controller 3 is provided by the bi-directional bus 23 over which the control signals are transferred between the microprocessor 1 and the video system controller 3. The output of the video system controller 3 is applied in the form of address information and control signals to the display memory 5 and system dynamic RAM 19 via address bus 25. The control of the transfer of data to and from the display memory 5 and the system dynamic RAM 19 is provided from the video system controller 3 via the control bus 27. Additionally, a sync and blanking signal is provided to the CRT monitor 11 via sync line 29. The microprocessor 1 executes the program instructions that are provided to it either by the data bus 17 or stored within its own internal memories. In response to these program instructions, control signals and data in the form of commands are passed to the video system controller 3. The video system controller 3 performs four basic functions. These functions are (1) it allows the microprocessor 1 virtually uncontested access to the system dynamic RAM 19 and the display memory 5; (2) automatically generates the refresh cycles needed to maintain the data stored within the system dynamic RAM 19 and the display memory 5; (3) performs the display update cycles needed to periodically load new video data into the display memory 5 and in particular into the shift registers contained within the display memory 5; (4) generates the video sync signals and blank signals necessary to control the video

The display memory 5 includes a bit map RAM unit or chip having sufficient cells to accomodate any screen display intended for the CRT monitor 11 and further includes a serial shift register that has a plurality of taps at locations corresponding to different preselected columns of cells in the display memory 5. Additionally, provisions are included for selecting taps to unload only a portion of the shift register containing the bits of interest, whereby unused portions of the shift may be effectively excluded and the time for transferring of data of interest to the CRT monitor 11 is reduced. The optional high speed shift register 7 is interfaced to the internal shift register ports of the display memories 5 via conductors 31, and shifts the data to an optional digital to analog video signal converter 9 or other output devices and input devices. The CRT monitor 11 displays the information that is provided to it from the microprocessor 1 via the data bus 17 under the control of the video system controller 3 which handles the transfer of data from the display memory 5 to the CRT monitor via the optional shift

register 7 and the digital to analog converter 9. Timing for the system is provided by the system clock 33 which provides the shift and

load clocks to the system, and in particular to the video system controller 3, the display memory 5 and the shift register 7.

35

Figure 2 to which reference should now be made, is a functional block diagram of the video system controller 3 of Figure 1 in which a multiplexer 49 accepts addresses from the microprocessor 1 via address bus 21 as well as from a refresh address counter 45 which is used to refresh the memory cells of the display memory 5, from an X-Y address register 43 and the shift register address from the control and video internal register 39. The addresses are converted to a 9 bit row in column address required for the display memory 5 and/or the system DRAM 19. The address that is provided by the microprocessor 1 is divided into two groups, RA0-RA8 are the row address bits which are applied to a row address latch 47 via data bus 21R and the CA0-CA8 address bits which are the column address bits which apply to the column address latch 41 via data bus 21C. Of course the mnemonic CA stands for the column address bits. An arbitor-ready logic 37 determines the source of the addresses that is applied by a multiplexer 49 and data bus 25 to the display memory 5 as well as providing a ready/hold signal to the microprocessor 1 as a portion of the control signals carried via data bus 23. The control signals used to control the multiplexer 49 and the subsequent multiplexing of the row column addresses as they are outputted on the data bus 25 in the form of MA0-MA8, which stands for memory address is generated by a memory cycle controller 35. The row and column address inputs from the microprocessor 1 are stored in a row address latch 47 and a column address latch 41 respectively by the falling edge of the control signal "ALE" prior to being multiplexed to the display memory 5.

Both the X-Y registers 43 and the control and video register 39 are programmable registers which are directly accessible by the microprocessor 1.

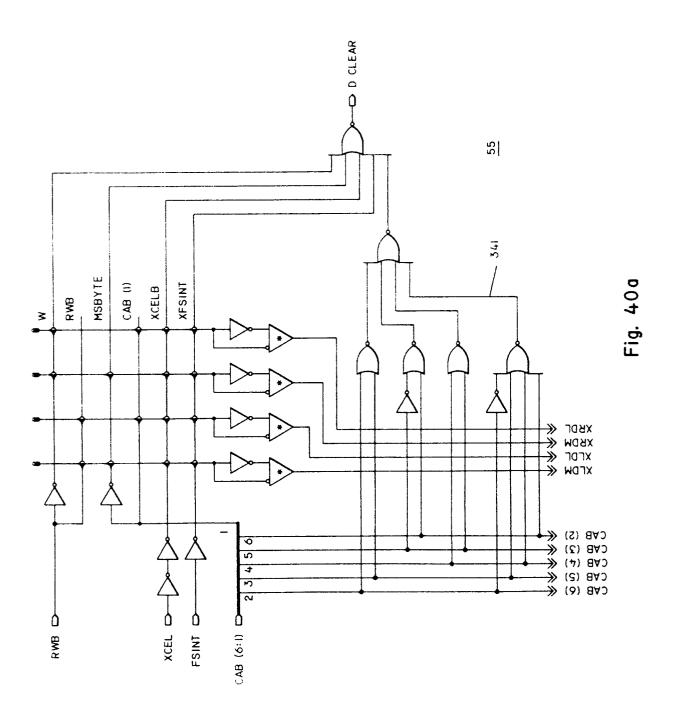

Data bus 17 in the embodiment of Figure 2 is only 8 bits wide, each register of the X-Y address register 43 and the control and video register 39 is 16 bits wide. Consequently, the microprocessor 1 accesses the high and low bits of the registers in separate cycles. The bit value inputted on column address bit line that is a part of address bus 21C determines whether the high or low byte of the register is addressed. An access of an internal register is enabled by setting the appropriate function code select which is designated

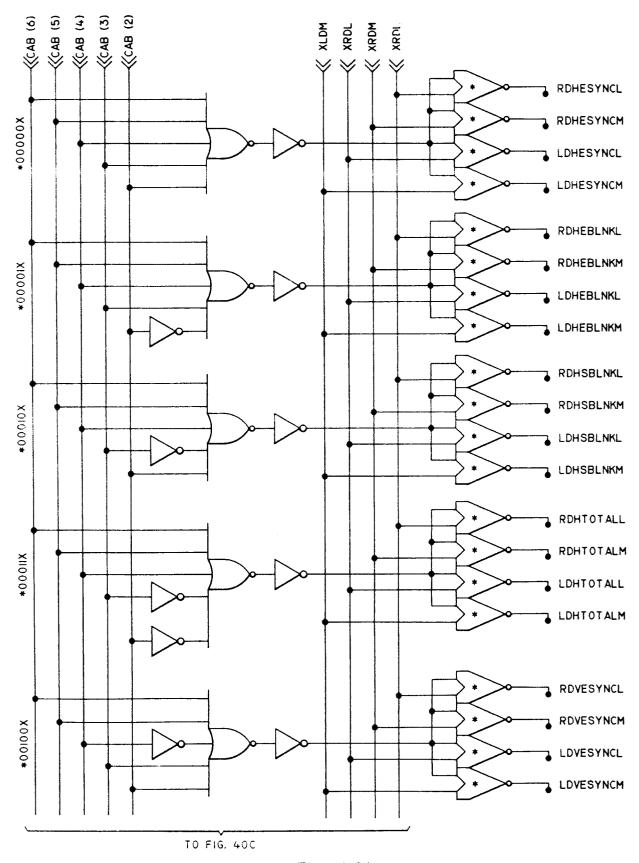

by the function select lines FS0 - FS2 at the start of the cycle. Selection of one of the registers, which in the embodiment of Figure 2 total up to 18, is determined by the 5 bit code input on data lines CA6 through CA2 which are a portion of address bus 21C during the access by the microprocessor 1. The value input on CA1 selects the high or low bytes of the register. The state of the read and write line, R/W- input which must be valid prior to and during the time the column address enable low byte, CEL, which is a control line that is present on data bus 23 goes low, which determines whether the register access is a read or a write. The control and video registers include video timing registers, display update registers, and control registers. The video timing registers are programmed to generate the horizontal and vertical sync and blanking signals needed to control the CRT monitor 11 of Figure 1. The values loaded into these registers are customized to fit the particular display resolution and timing requirements of the CRT monitor 11. Both interlaced and non-interlaced scan modes are available. The video system controller can be programmed to lock up to externally generated sync signal, an application in which the graphic image generated within the display memory 5 is to be superimposed upon an external video signal.

The display update registers are required because the video system controller 3 generates the display update cycles necessary to periodically refresh the video display. The display update registers maintain the row and tap point address output to the display memory 5 during each display update cycle. The display update cycle is a special type of display memory 5 access which transfers 256 bits of data between the memory cell array and the shift register within each display memory 5 in the memory system. In graphics application, the display update cycle takes place during horizontal blanking to load the shift register with a new load of data from the memory cell array.

During the subsequent active horizontal scans, the contents of the shift registers within the display memory 5 are clocked from the serial out pads and displayed on the CRT monitor 11. The video system controller 3 can be programmed to transfer data in the opposite direction, i.e., from the shift register to the memory cell array, all of which are contained within the display memory 5. This mode of operation is convenient for capturing video images that are generated externally and then clocked into the shift register through the serial input during the preceding active horizontal scan.

The display control registers contain a starting display address corresponding to the location within the display memory 5 that is displayed at the upper left of the screen. The amount by which the display address is incremented between display update cycles is also programmable. These programmable features include (1) specifying the number of scan lines between successive display update cycles; (2) specifying the direction (read or write) of data transfer; (3) specifying the horizontal sync, Hsync, and vertical sync, Vsync, lines to be either inputs or outputs; and the selection of either interlaced or non-interlaced video. These features are controlled by means of the values loaded into the control registers and the video timing registers. In the embodiment represented by the block diagram of Figure 2, there are two control registers which control the specification of a number of programmable features, including the various modes of operation supported by the video system controller 3 that have already been mentioned. Each active register can be both read or written too by the microprocessor 1. Also included in this block of registers are the status register which can be read but not written to.

A status register contain three active bits. One of these bits indicates when a particular horizontal scan on the screen has been displayed. The other two status bits indicate error conditions. One bit indicates when a pending request for a DRAM refresh cycle has been locked out for too long, and the other bit indicates when a pending request for a display update cycle has been blocked for too long. When enabled, these status conditions cause interrupt requests to be sent to the microprocessor 1.

The X-Y address register 43 maintains the X-Y addresses that represent the concatination of the X and Y coordinates of a location on the graphics screen that is being displayed by the display monitor 5. The video system controller 3 can be configured to provide an internal 20 bit X-Y address in place of the address provided by the microprocessor 1. This feature is useful in extending the address reach of certain processors. Even when the microprocessor 1 has sufficient address reach to directly access any pixel on the screen, the hardware updating of the X-Y address between accesses is likely to be more efficient than the same functions performed in the microprocessor 1's software. The X-Y portion of the address can be independently incremented, decremented, or cleared, under control of the inputs CA4-CA1 supplied by the microprocessor 1 during each X-Y address register 43 access. The incrementing takes place following completion of the access in preparation for the transfer of the next X-Y address to the X-Y address register 43. The video system controller's X-Y addressing feature permits internal algorithms such as line drawings or custom character drawing routines to access a series of adjacent pixels on the screen at hardware assisted speeds.

An arbitor 37 is responsible for generating requests for memory and register access cycles. When more than one request is outstanding, the arbitor is responsible for deciding which request is to be generated next based upon the relative priorities of the completed requests. Since the display update and the DRAM refresh cycles are generated internally by the video system controller 5 typically utilize fewer than 2% of the available memory cycles, the arbitor is likely to grant a request from the microprocessor 1 for a memory register access immediately. However, when a display memory 5 refresh request has been outstanding for sometime, its priority is increased to insure that the refresh cycle occurs before memory data is lost. The arbitor holds the microprocessor 1 in check by means of the RDY/HOLD- signal.

A memory cycle generator 35 is responsible for performing the memory cycles assigned to it by the arbiter/ready logic 37. The memory cycle generator controls the multiplexer 49 and generates the timing for control signals and addresses during a memory cycle. The memory cycle generator 35 can perform microprocessor-direct memory access, X-Y addressing, display update, refresh of the display memory 5 and the system dynamic random access memory (DRAM) 19, shift register read and shift register write cycle.

The video system control can perform refresh cycles to the display memory 5 and system DRAM 19 at regular intervals. The refresh address counter 45 generates a 9 bit row address output during a refresh cycle. Contained within the refresh address counter 45 determines the number of refresh cycles per horizontal scan line. Timing for this transfer is illustratesd in Figure 38.

15

A refresh address register within the refresh address counter 45 is inaccessible to the microprocessor 1, maintains the current row address and is incremented following each memory refresh cycle. The enabling of refresh cycles and the frequency of refresh cycles are determined by three control register bits within the control register 39C.

The CRT controller 57 also contains a 4 bit scan line counter which is used to count the number of active horizontal scan lines output to the CRT monitor 11 between successive display update cycles. Any number of scan lines from 1 to 16 can be specified. For example, in a system in which each display update cycle transfers enough data to do the video shift register within the display memory 5 for two complete scan lines, a display update cycle is required only at the beginning of every other scan line.

Figure 38 depicts four successive scan lines on the CRT monitor 11 and will be used to reference the locations at which various video system controller 3 activities ocur. Llne segments 901A through 901D represent the active portion of each horizontal scan line. Intervals 902A through 902D represent the blanked portion of each horizontal scan line. The microprocessor 1 may request a memory access at any time and the video system controller 3 will grant the access and perform the memory cycle based on arbitration logic within the VSC. Two types of cycles are produced by the VSC at particular times during the raster. During the interval labeled 902A, 902B, 902C, 902D, the video system controller 3 performs a display update cycle also known as a shift register reload cycle. This causes a shift register transfer to take place within the video memories 5, which is data to be displayed on the next scan line. The beginning of intervals 901A-D represents the end of the horizontal blanking interval. At this point the video system controller begins performing refresh cycles to all memories of the system. Up until point 903A-D on each scan line, microprocessor 1 requested memory access cycles are granted with priority over internally requested refresh cycles. Half way through the active scan line, denoted by 903A-D, refresh cycles are given priority over microprocessor requested cycles. Display update cycles arse always given priority over microprocessor requested cycles.

Figure 3 to which reference should now be made is a wiring diagram of circuit blocks used to implement the functional blocks of Figure 2 on a single metal oxide silicon chip with field effort transistors.

System 53 contains the memory cycle generator 35, registers 39A which are a portion of the control and video internal registers 39 of Figure 2, the multiplexer 49, the refresh counter 45, and the arbiter/ready logic 37. Video block 57 completes the functions of the CRT controller 51 as well as the video internal registers 39C. The X-Y logic block 43 corresponds to the X-Y registers 43 of Figure 2. The FS decode logic 63 contains not only the row and column address latches 41 and 47, but also the function select decode logic which decodes the function select input signals FS (2-0). The CA-decode logic 55 which is a portion fo the control and video internal registers 39 of Figure 2, contains the decode circuits associatesd with the column address latch 41. The remainder of the control registers are contained within the control reg block 39C of Figure 3 and input pins 59 and data status 61 contain input logic for receipt of data from the microprocessor 1 of Figure 2 and to provide the status to the microprocessor 1 of Figure 1 as well as providing the control signals necessary to implement the bidirectional transfer of data between the microprocessor 1 and the display memory 5 and system DRAM 19.

Table 1 provides a definition for the pneumonics used in Figure 3 to describe the different signals that are illustrated on the figure.

# TABLE 1 I/O CONNECTIONS FOR THE VIDEO SYSTEM CONTROLLER 3

SIGNAL

5

55

| 10 | NAME    | DIRECTION | DESCRIPTION                                            |

|----|---------|-----------|--------------------------------------------------------|

|    | RA8-RA0 | In Row    | Address 8 to 0 (9 input lines)                         |

|    |         | Thes      | e 9 address inputs are multiplexed to memory address   |

| 15 |         | line      | s MA8-MAO during row address time when a               |

|    |         | micr      | oprocessor 1 initiated memory access cycle is          |

| 20 |         | exec      | uted. While ALE is high and the display memory 5 is    |

|    |         | avai      | lable for a microprocessor 1 initiated cycle, the      |

|    |         | MA8-      | MAO outputs follow the RA8-RAO inputs, which are       |

| 25 |         | lato      | hed by the high-to=low transition of ALE. RAO is the   |

|    |         | LSB,      | least significant bit.                                 |

|    |         |           |                                                        |

| 30 | CA8-CA0 | In Colu   | mn Address 8 to 0 (9 input lines)                      |

|    |         | Thes      | e 9 address inputs are multiplexed to memory address   |

|    |         | line      | es MA8-MAO during column address time when a           |

| 35 |         | micr      | oprocessor 1 initiated memory access cycle is          |

|    |         | peri      | formed. When the microprocessor 1 accesses one of the  |

| 40 |         | 18 r      | registers internal to the Video System Controller 3, a |

|    |         | regi      | ster is selected by the code input on CA6-CA2, and the |

|    |         | uppe      | er or lower byte of the register is selected by the    |

| 45 |         |           |                                                        |

|    |         |           |                                                        |

|    |         |           |                                                        |

| 50 |         |           |                                                        |

value input on CA1. During an X-Y address cycle, the value input on CA4-CA1 determines the manner in which the X-Y address stored within the X-Y register is incremented or decremented following completion of the cycle. These inputs are latched by the falling edge of ALE. CAO is the LSB.

RS1, RSO In RAS Select 1 and 0

During microprocessor 1 direct cycles and shift-register-transfer cycles, these two lines determine which of the four row address strobes, RAS3- to RAS0-, is driven active-low. RS1-RSO are latched by the falling edge of ALE. If extended-row address select mode is enable, these inputs are ignored.

CEH- In Column Address Enable High Byte

This signal enables the activation of CASHI- during an initiated memory cycle by the microprocessor 1.

CELIn Column Address Enable Low Byte

This signal enables the activation of CALSO- during a microprocessor 1 initiated memory access cycle. CEL- is also used to strobe data into the internal registers during register write cycles and to enable register data onto D7-D0 during register read cycles.

ALE In Address Latch Enable

The high-to-low transition of ALE latches the CS-, RASO-RAS8, CASO-CAS8, RS1-RSO, and FS2-FSO inputs, and is interpreted by the Video Display Controller 5 as a command from the host processor to initiate the cycle specified by the values latched at these inputs. ALE is required to be synchronous to SYSCLK, and must meet setup and hold times specified with regard to each low-to-high SYSCLK transition.

20 R/W- In Read, Not Write

During a memory cycle initiated by the microprocessor 1, R/W- indicates the direction of the data transfer (high for read, low for write), and determines the state of the W- signal output from the Video System Controller 3 to the memory. By appropriately controlling the state of the R/W- input, the microprocessor 1 initiated memory cycle can be a read, write, early write, or read-modify-write cycle. Similarly, during an access of an internal register by the microprocessor, R/W-indicates whether the data is transferred to or from the register. At the beginning of the register access cycle, R/W- is required to be valid prior to the high-to-low transition on the CEL- input.

INT- Out Interrupt Request

The interrupt request output is driven active-low to indicate that an interrupt condition previously enabled by the microprocessor 1 has occurred. INT- will remain active until the microprocessor 1 initiates a read of the Status Register. The Video System Controller 3 can be programmed to generate an interrupt at the start of a particular scan line in each vertical field, and also when a refresh or display-update error has occurred.

D7-D0 I/O Data Bus Lines 7 to 0

The microprocessor 1 accesses the registers internal to the Video System Controller 3 through this 8-bit bidirectional data bus. DO is the LSB. Each of the 18 16-bit registers within the VSC that are accessible one byte at a time via D7-D0. The microprocessor 1 must be accessed one byte at a time via D7-D0. The microprocessor 1 accessed the memory through a separate data path external to the Video System Controller 3, whose width is determined by the width of the microprocessor 1's data bus.

# RDY/HOLD- Out Ready or Hold

The operation and timing of the RDY/HOLD- output are configured by means of several control bits contained in Control Register 39, and also by the state of the HOLDACK- input at the end of reset. With the Video System Controller 3 configured in ready or wait mode, the RDY/HOLD- line remains in high impedance until the microprocessor 1 requests a memory cycle. In hold/hold acknowledge mode, the RDY/HOLD- line is always driven.

# HOLDACK- In Hold Acknowledge

When the Video System Controller 3 is configured in hold/hold acknowledge mode, the HOLDACK- input is driven active-low by the microprocessor 1 to acknowledge a hold requests from the Video System Controller 3. While in this mode, the Video System Controller 3 can perform an internally-requested cycle (display update or refresh) only upon receipt of a hold acknowledgment from the microprocessor 1. A second use of the HOLDACK- line is to configure active level of the VSC's RDY/HOLD-line at system power-up. The level input on the HOLDACK- line just prior to the end of reset determines whether the RDY/HOLD- output is initially configured as active-high or active-low. If HOLDACK- is high at the end of reset, then while the VSC remains configured in ready or wait mode, the RDY/HOLD- output is active-low, meaning a low

level means "ready" and a high level means "not ready". The meaning of the high and low levels of RDY/HOLD- are reversed if HOLDACK- is low at the end of reset. When the VSC is configured in hold/hold acknowledge mode, however, the meaning of the levels output on the RDY/HOLD- line are fixed independent of the level on HOLDACK- at the end of reset.

CS-

In Chip Select

This input operates as a master chip select. Before any microprocessor 1-initiated access involving the Video System Controller 3 can begin, CS- must be active-low. This includes both accesses of Video System Controller 3 internal registers and accesses of the memory system controlled by the Video System Controller 3.

FS2-FS0 In Function Selects 2 to 0

The three-bit function-select code input on FS2-FS0 indicates the type of cycle requested by the microprocessor 1. All cycles initiated by the microprocessor 1 begin on the high-to-low transition of ALE.

SYSCLK In System Clock

SYSCLK is the system input clock, which is used to generate the timing of signals output to the memory, and the timing of the INT- and RDY/HOLD- signals output to the microprocessor 1. Additionally, all microprocessor 1 interface signals input to the Video System Controller 3 must be synchronous to SYSCLK.

RESET- In Reset

The RESET- input is driven active-low to place the Video System Controller 3 in a known initial state. RESET- is low, the internal registers are forced to their default values, and all display memory 5 control outputs are forced to their inactive levels. RESET- should be driven low when power is first applied, and remain low After RESET- is brought for at least 1 msec. inactive-high, the microprocessor 1 accesses neither the Video System Controller 3 nor the memory it controls for another 1 msec. This time is required to allow the Video System Controller 3 to perform at least 8 RAS-only refresh cycles, thus bringing the display memory 5 it's current initial state. After the required time has elapsed, the registers internal to the Video System Controller 3 should be loaded with the values appropriate to the application.

50

5

10

15

20

25

30

35

40

45

MA8-MA0 Out Memory Address 8 to 0

The 9 memory address outputs are multiplexed address lines designed to interface directly to display memory 5, as well as to conventional DRAMs. The Video System Controller 3 multiplexes 9 bits of row address and 9 bits of column address over these lines. When the display memory 5 is 256K DRAMs that require 9 bits of row and column address interface to all 9 memory address outputs, while 64K DRAMs requiring only 9 bits of row and column address are connected to MA7-MAO. MAO is the LSB.

RAS3- TO RASO Out Row Address Strobe 3 to 0

These active-low outputs are designed to directly drive the RAS- inputs on both conventional memory 13 and the display memory 5. During a microprocessor 1 direct read or write cycle, or a microprocessor shift register transfser cycle, the default mode of operation is that the four row-address-strobe outputs, RAS3- to RAS0-, are controlled by the RS1 and RS0 inputs. The two-bit code input on RS1-RS0 determines which of the four RAS outputs is driven active-low during the cycle. Alternately, the Video System Controller 3 can be configured to use two control register bits in place of the RS1-RS0 to determine which of the four RAS outputs is active during a microprocessor 1-direct cycle. During a DRAM-refresh cycle all four RAS- outputs are always driven active-low.

During a display-update cycle, the default mode of operation is that all four RAS- outputs are driven active-low. Alternately, the Video System Controller 3 can be configured to drive only one of the four RAS outputs low during a display-update cycle.

10

5

CASHI- Out Column Address Strobe, High Byte

15

20

This active-low output is designed to directly drive the CAS- inputs on both conventional memory 13 and the display memory 5. During memory cycles initiated by the microprocessor 1, CASHI- becomes active only after the CEH- input is driven active-low. In 16-bit systems, CASHI- is typically used to enable a read or write to the high byte (8 MSBs) of the memory data bus. CASHI- is driven active-low during the internally-requested display-update cycles, and remains inactive-high during

25

30

35 CASLO-

Out Column Address Strobe, Low Byte

DRAM-refresh cycles.

The operation of CASLO- is similar to the operation of CASHI-, as described above, except that CASLO- is enabled by an active=low level on CEL- rather than CEH-. In 16-bit systems, CALSO- typically is used to enable the low byte (8 LSBs) of the memory data bus. CASLO- is driven active-low during internally-requested display-update cycles, and remains inactive-high during DRAM-refresh cycles.

50

40

45

W- Out Write Control

This signal is intended to drive the W- inputs on both conventional DRAMs and TMS4161 multiport DRAMs. W- is driven active-low during write cycles requested by the host processor. During internally-initiated display-update cycles, W- is driven active-low if a write is indicated by control bit B6 in Control Register 39C.

TR-/QE- Out Shift Register Transfer and Output Enable

The TR-/QE- output can directly drive the TR-/QE- inputs on the display memory 5. The signals used to enable shift-register cycles, and those used to enable the display memory 5 output buffers during read cycles are multiplexed over this single pin.

BLANK- Out Video Blanking

The BLANK- output is used to control the blanking input on a CRT monitor 11. BLANK- is driven active-low during both horizontal blanking and vertical blanking intervals. This output is TTL-compatible. The entire screen is blanked immediately following reset, and the active portions of the screen are unblanked only after control bit B13 in Control Register 39C is set.

HSYNC- I/O Horizontal Sync

Except when external sync mode is enabled, HSYNC-operates as an output, generating the horizontal sync pulses used to control a CRT monitor 11. HSYNC- is driven active-low during horizontal sync intervals, the timing of which is determined by the values programmed into the Video System Controller 3's horizontal timing registers. In external sync mode, HSYNC- is an input rather than an output, and a high-to-low transition on HSYNC- forces the Horizontal Counter Register to zero. This bidirectional pin is TTL-compatible.

VSYNC- I/O Vertical Sync

Except when external sync mode is enabled, VSYNCoperates as output, generating the vertical sync pulses

used to control a CRT monitor. VSYNC- is driven

active-low during vertical sync internals, the timing of

which is determined by the values programmed into the

Video System Controller 3's vertical timing registers.

In external sync mode, VSYNC- is an input rather than an

output, and a high-to-low transition on VSYNC- forces the

Vertical Counter Register to zero. This bidirectional

pin is TTL-compatible.

# VIDCLK In Video Clock

5

10

15

20

The video input clock drives the portion of the logic within the Video System Controller 3 chip that is responsible for generating the timing for the sync and blanking signals. VIDCLK also logic internal responsible for generating requests for display-update and DRAM-refresh cycles. Typically, VIDCLK is harmonically related to the dot (or pixel) clock used to stream video data from the external shift registers in the memory system to the CRT monitor. input is TTL-compatible.

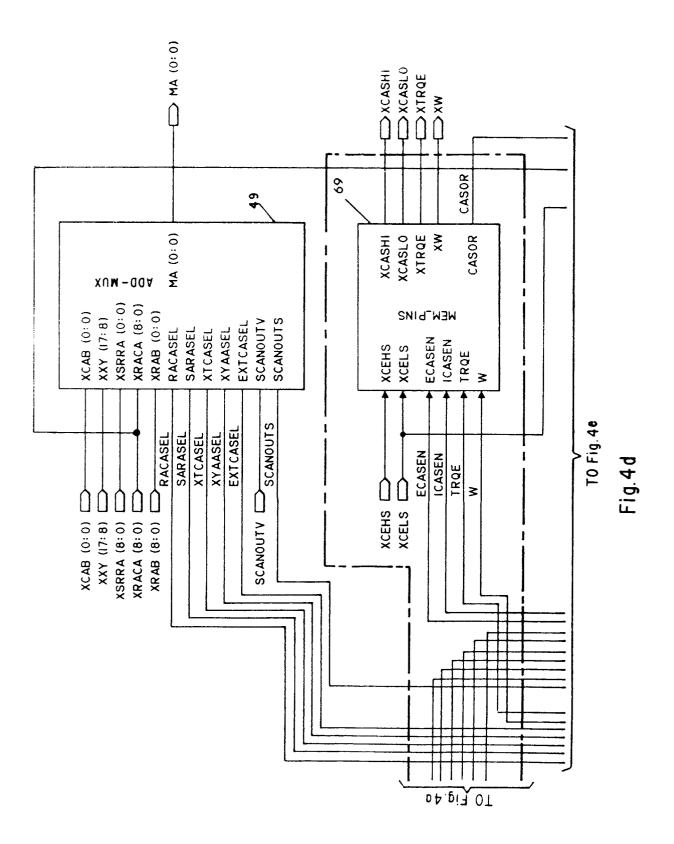

In Figure 4 the system 53 includes the logic to implement memory cycle generator 35. This is divided into several logic components which include the row address select RAS, decode logic 65 which decodes a row address select operation; memory pins 69 which control the loading of data through the memory that is provided by a memory cycle generator 67; memory cycle 67 generates the memory cycle transfers to handle the transfer of data between the microprocessor 1 and the display memory 5 or the system DRAM 19; and control 71 generates the internal control signals that are used by the video system controller 3. Additionally, the arbiter ready logic 37 is contained in the system block diagram as is the refresh address counter 45 which is a portion of the system block diagram 53.

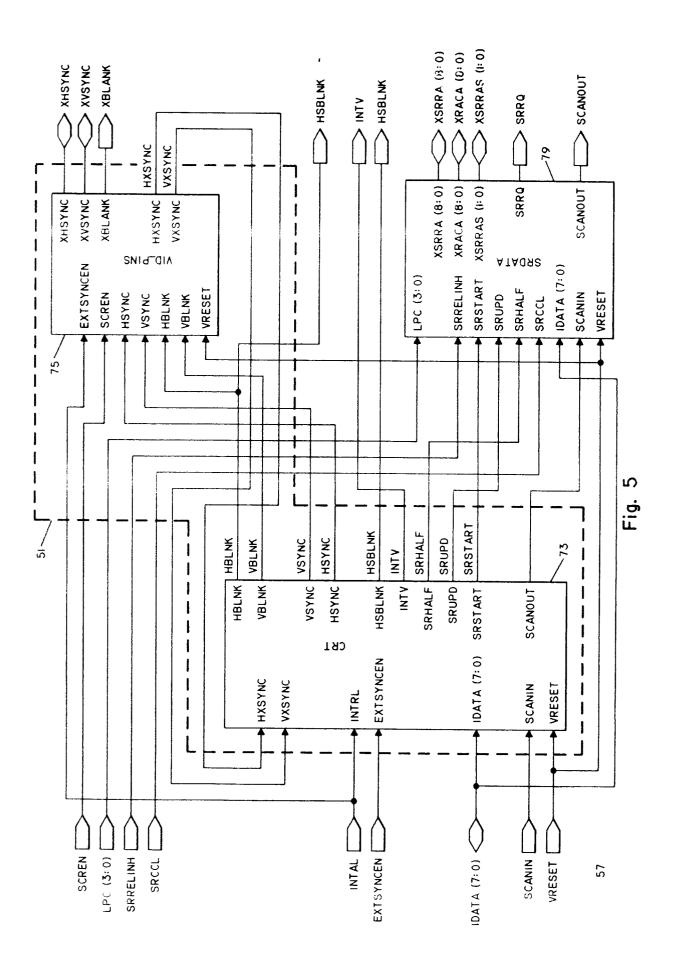

Figure 5 is a connecting diagram of the video block 57 of Figure 3 and includes the CRT controller 51 which contains the CRT logic 73 which generates the CRT signal such as blank and sync, both horizontal and vertical and applies these signals to the video pins 75 which converts this signals to signals which are voltage and current levels acceptable by the CRT monitor 11. As was previously discussed, the display memory 5, in the preferred embodiment, has built in shift registers in which the microprocessor 1 may write to directly. The control of data transfer to the shift register is provided by the SR logic 79 which is a portion of the video block 57.

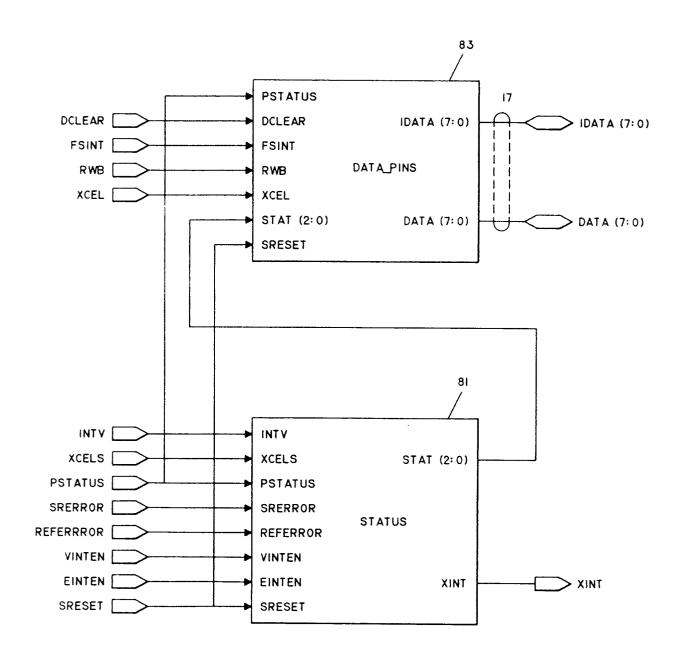

Figure 6 is a connection diagram of the DA-ST block 61 of Figure 3. It includes data pins for receiving the data and converting it to logic levels acceptable by the video system controller 3. Additionally, as part of the interface to the microprocessor 1, the display memory 5, and the system memory 19 status is provided by a status block 81 of Figure 6.

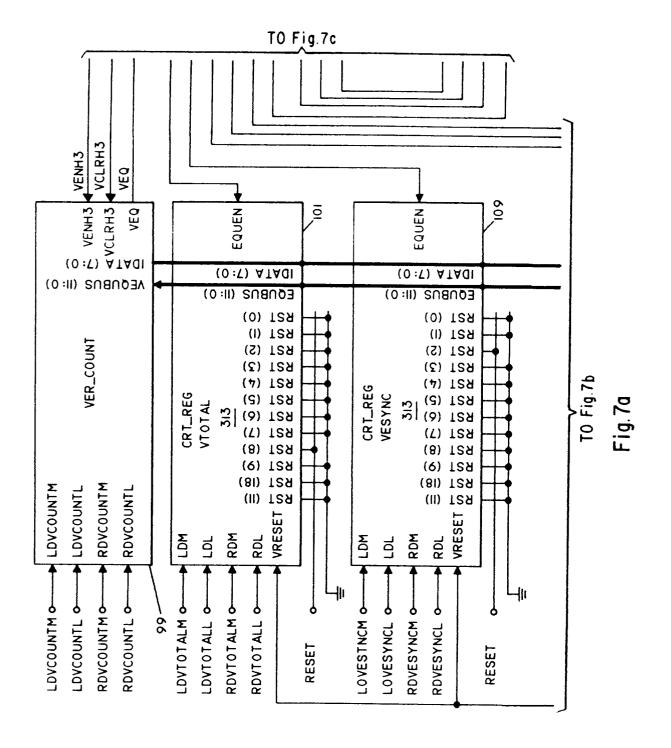

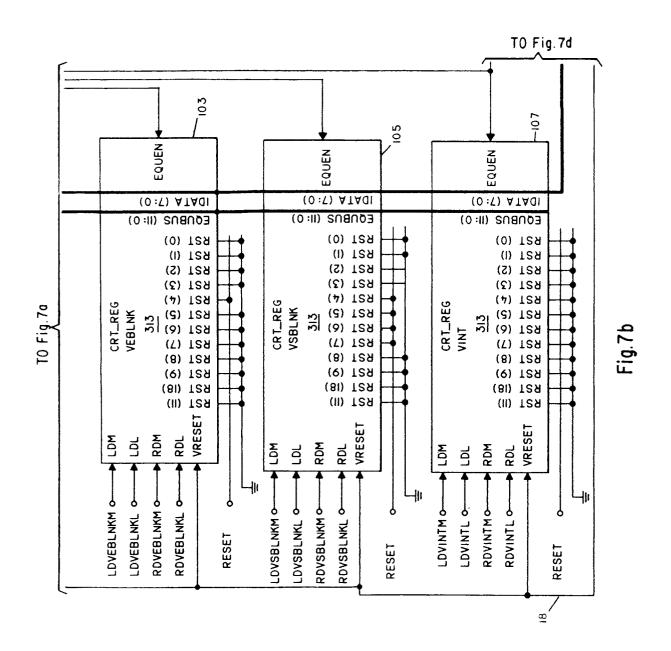

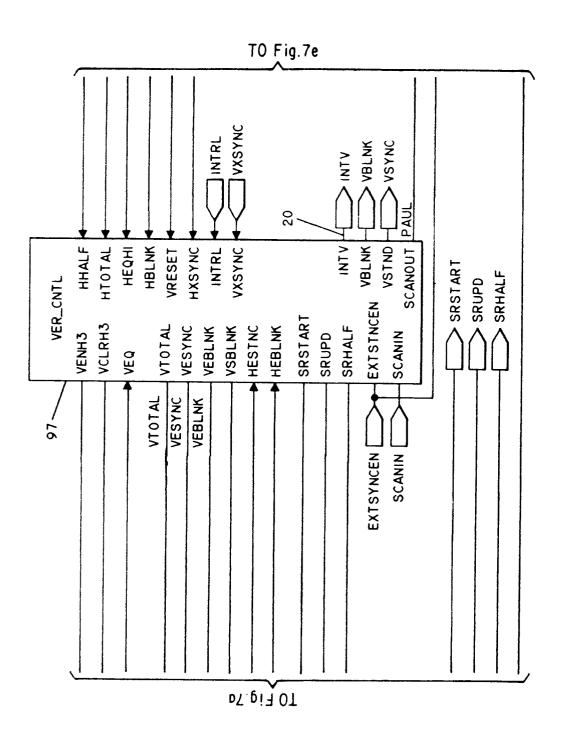

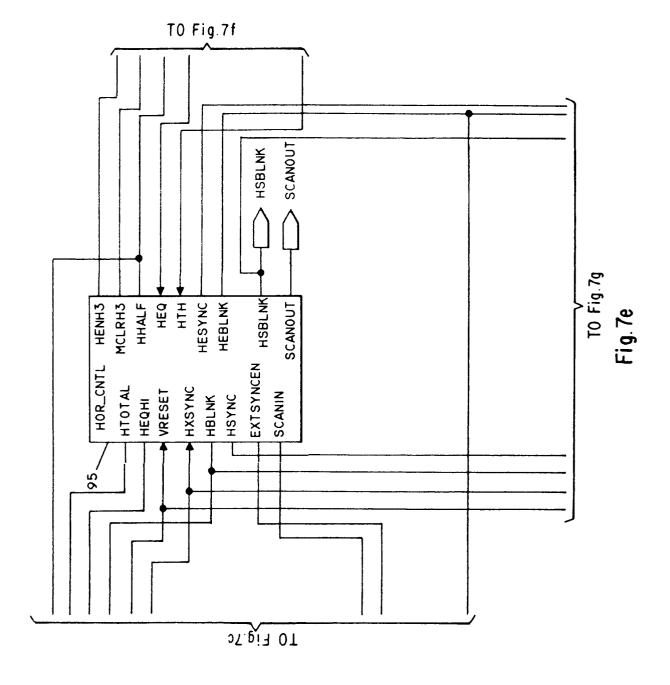

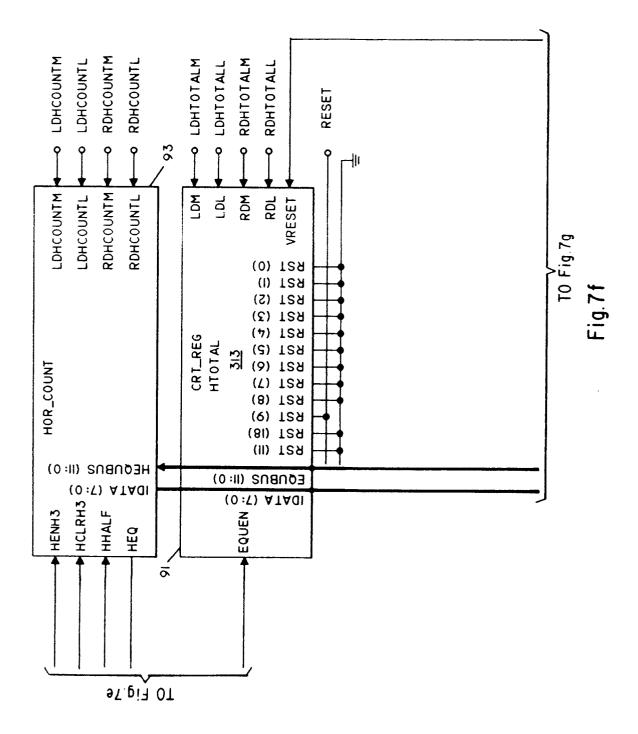

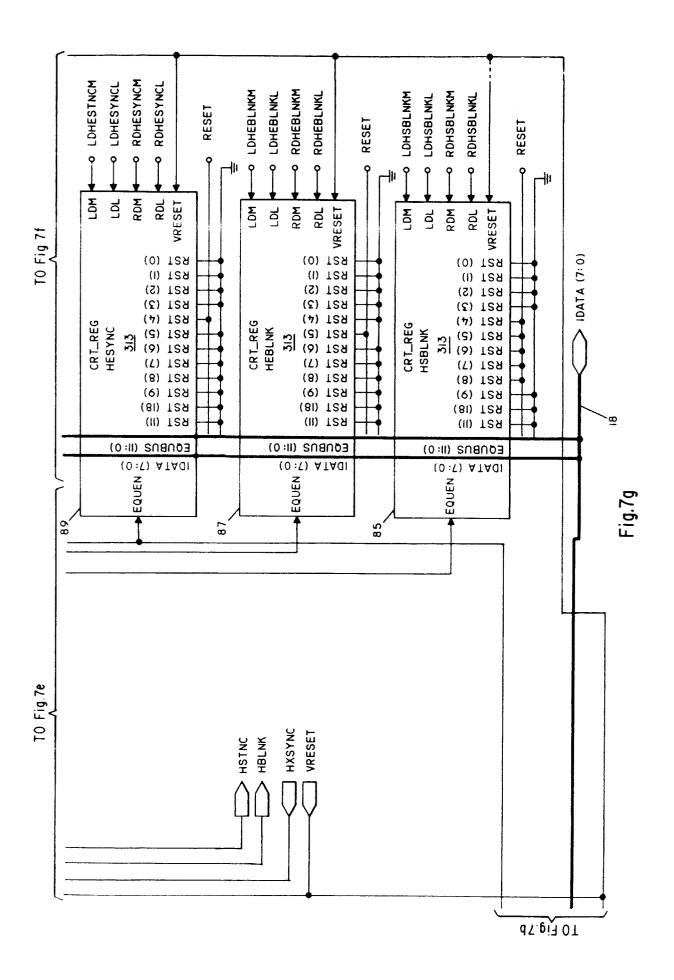

Figure 7, to which reference should now be made, is shown a connection diagram of the CRT block 73 of Figure 5. The CRT block includes the vertical control logic 97, the horizontal control logic 95, a horizontal counter 93 and a vertical counter 99. Additionally, there are 9 programmable registers which can be both written to and read from by the microprocessor 1 through an 8 bit data pad 18 that is provided by the DA-ST block 61 to the video block 57. Each register in the embodiment shown in Figure 7 is 12 bits wide. The microprocessor 1 accesses the programmable registers within the CRT block 73 as well as other areas of the video system controller 3 by means by special read and write cycles. A register access cycle is selected by setting the functions select inputs FS2-FS0 to one of two 3 bit codes, either 000 or 010. Being there are 18 programmable registers in the video system controller 3 and only 9 in the CRT block 73 the information described here is applicable to all 18 programmable registers. One of 18 registers is selected by a 5 bit register address input in the column address input CA6-CA2. Binary codes 00000 thru 10001 are valid register addresses. Codes 10010 through 11111 are reserved. The high or low byte of the register is selected by the value input on CA1. If CA1 is zero, the low byte is selected; otherwise, the high byte is selected. In Figure 7, the logic represented by the CRT block 73 generates the horizontal sync, vertical sync, and blanking outputs needed to control CRT monitor 11. These signals are outputed on the HSYNC-VSYNC-BLANK linear. The video system controller may be programmed to provide sync and blanking signals appropriate to the particular CRT monitor 11 and screen resolution selected for the desired

application. In addition, the video system controller 3 can be programmed to interrupt the microprocessor 1 at the end of any horizontal scan line by driving an interrupt, INT- to its active low level by the control of the INTV signal that is present on line 23. These signals are programmed by the parameters loaded into the nine registers of the CRT block 73 by the microprocessor 1. These registers include the horizontal end sync register 89, HESYNC; the horizontal end blank 87, HEBLNK; horizontal start blank 85, HSBLNK; horizontal total 91, HTOTAL; vertical end sync 109, VESYNC; vertical end blank 103, VEBLNK; vertical start blank 105, VSBLNK; vertical total 101, VTOTAL; and vertical interrupt 107, VINT. The two additional registers, the horizontal counter 93 and the vertical counter 95, are used in generating the video timing signals.

The horizontal counter 93 is a counter whose contents are compared with the horizontal end sync register 89, the horizontal end blank register 85, the horizontal start blank register 85 and the horizontal total register 91 to determine the limits of the horizontal sync and blanking intervals. Similarly, the vertical counter 99 is a counter whose contents are compared with the vertical end sync register 109, the vertical end blank register 103, the vertical start blank register 105, and the vertical total register 101 to determine the limits of the vertical sync and blank in intervals. The contents of the vertical interrupt register 107 are compared with the vertical counter 99 to determine when a particular scan line is being outputed to the CRT monitor 11. The microprocessor 1 can be interrupted when this condition is detected.

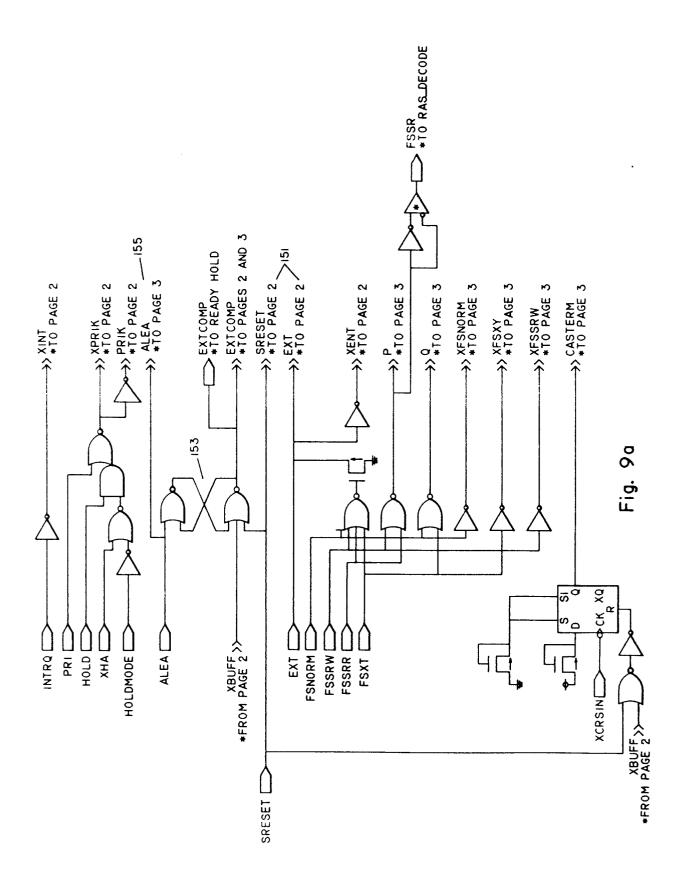

In performing a role as a controller for the display memory 5, and system DRAM 19, the display update controller, and CRT monitor 11 timing controller, video system controller 3 must perform several types of access cycles. Some of these types of cycles are initiated by the microprocessor 1, while others are initiated automatically by the video system controller. The memory cycle generator 35 performs most of the access cycles. And in particular, the cycle generator 67 which is shown in Figures 8 and performs the following cycles:

Direct cycles which are initiated by the microprocessor 1;

55

X-Y register 43 indirect cycle which is also initiated by the microprocessor 1;

display memory 5 and system DRAM 19 refresh cycles are initiated automatically by the video system controller 3;

display update cycle initiated automatically by the video system controller;

and shift register transfer cycles which includes the shift register write and shift register read for transferring data to and from the shift register within the display memory 5.

The control circuit 71 handles the request for all internal cycles including the CRT monitor display update cycles, and the memory 5 and 19 refresh cycles. The horizontal blank signal tells the control logic 71 the location of the raster on the CRT for request of a display update or refresh. This request is transferred to the cycle generator 67 for implementing the display update cycle or the refresh update cycle.

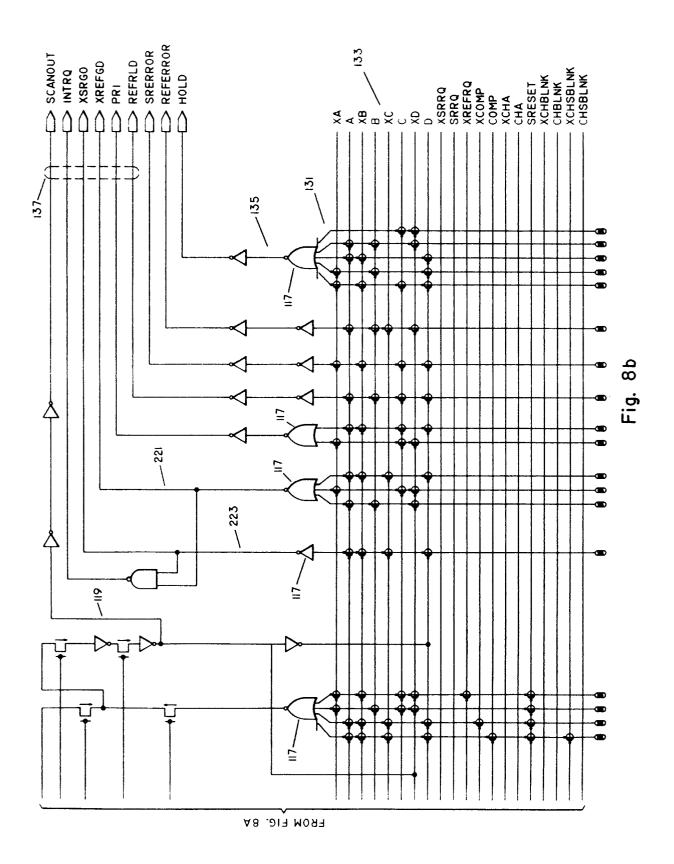

Figure 8 is a schematic diagram of the control block 71 and includes two synchronizer circuits 111 and 113. Synchronizer circuit 111 synchronizes the horizontal blanking signal with the internal clock that is used to control the logic within the system block 53. The CRT monitor 11 uses a separate clock system than the system 53 and consequently the horizontal blank signal and the horizontal stop blank signal that are applied to the system 53 from the video block 57 use a different clock which needs to be sychronized with the internal clock that is used to operate the control 71. Additionally the control 71 includes a Mealy-model state machine that is comprised of a plurality of programmable logic arrays 115 and an OR-gate 117 and a latch circuit 119. Each output of each stage in the embodiment of Figure 9 there are four stages 121, 123, 125 and 127 is applied to the column lines A, B, C, and D the compliments thereof are applied to XA, XB, XC and XD column lines. Additional controls are provided to the programmable logic arrays 115 in the row lines at data lines 129. Additionally, the Mealy state machine includes a PLA 133 and the decode logic 135 at point 131. The output of the control circuit is applied to the cycle generator 67 via data bus 137 to the ready hold logic via data line 139 and to the data status block 61 via data bus 141. A unique feature of the control logic is the state machine is laid out on "N" channel metal oxide silicon field efect transistor logic circuits utilizing a standard cell that is multiple repeated and programmed by placement of a transistor 143 which determines the operation of the state machine that is used to implement the control block 71.

Logic gates 117 are configured with a plurality of input leads 217. These leads may be tied to a large number of outputs from the programmable logic array 115 that is illustrated at 219 or connected to a minimal number of inputs to the NOR gate 117 as illustrated at 221 or just a single line with all the inputs of the NOR gate tied together as is illustrated at location 223 to provide for the implementation of a standard cell NOR gate.

The arbiter and ready hold logic 37 is based upon its operation by the cycle generator 67 in which logic circuits 151 of Figure 8 determine the priority of the operation whether it's internal or external to the video system controller 3. EXT and compliment, XEXT signals which are based on the ALE signal represent a

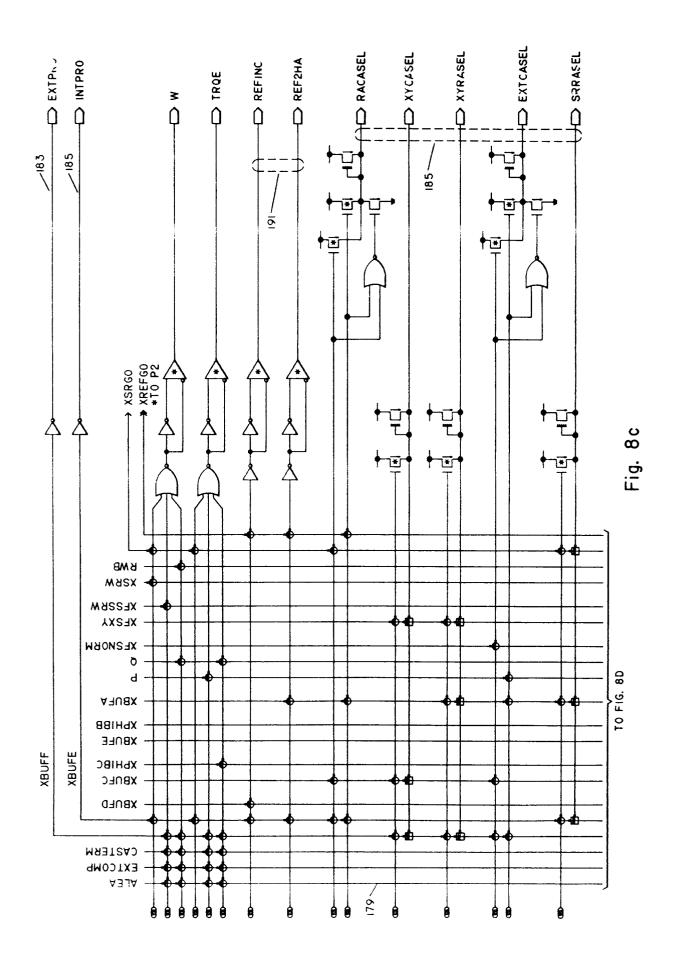

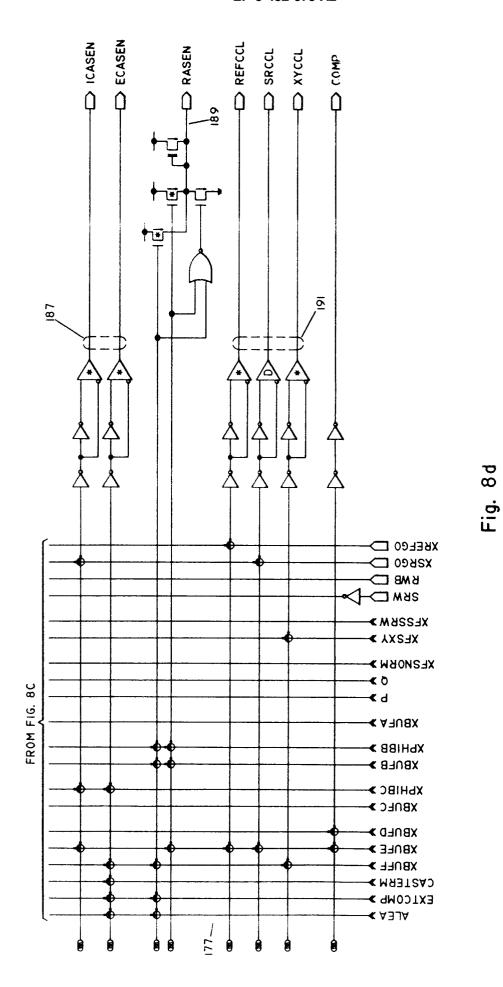

request from the microprocessor 1 for a memory access cycle. ALE is latched on to the cycle generator by the latch 153. Additionally, circuit 155 provides buffering for the internal cycle request XINT. The cycle generator 67 includes a Moore-model state machine composed of a first stage 161, a second stage 165, a third stage 167, a fourth stage 169, a fifth stage 171, a sixth stage 173, and a seventh stage 175. Each stage includes a PLA 115, an OR gate 117, an a latch circuit 119 with the output of each stage applied to the row lines A through G and the compliment applied to the XA through XG lines. The outputs are further decoded by logic 177 that includes a PLA 179 and decode logic 181. The logic 177 provides an indication at data bus 183 for an external cycle and 185 an internal cycle is in progress. The W conductor indicates a write operation where the TRQE provides the enable to the shift register and the output enable Of memories 5 and 19. REFINC provides the increment refresh to the refresh logic 45 and REF2HR provides for transfer from the refresh counter to the refresh hold register contained within the refresh logic of the refresh block 45 of Figure 4. Data lines or outputs 185 are the controls for the address selects of the multiplexer 49 and provide for SRRASEL which is a select of the display update row address. The RACASEL is the row address, column address select lines used for display update and refresh cycles. XYRASEL is the XY row address select lines, the XYCASEL is the XY column address select and the EXTCASEL is the external column address select lines. If none of these are active, then the row address (RA) 21d is sellected. Lines 187 provide for the internal column address enable, ICASEN, and the external column address enable, ECASEN. Row address enable RASEN is provided on the data line 189. Data lines 191 select the source to the RAS decode logic 65 which includes the XY cycle, XYCCL, the shift register cycle SRCCL, and the refresh cycle REFCCL. Additionally, line 193 is the completion line indicating that an internal cycle operation is complete and the XYGO signal is the adjust enable to the XY register 43 and is present on data line 195.

In Figure 10 to which reference should now be made, there is shown a block diagram of the row address select decode circuit that is represented by the block 65 entitled "RAS decode". The row address select override circuit provides a mode of operation that allows writing data to memory N times faster than without mode. N being the number of memory planes within the system, for example the display memory 5 of Figure 2 in one embodiment is configured too have four memory planes. For the video system controller 3, four row address select planes are supported in the embodiment of Figure 10. One embodiment is to designate each of the four planes that are illustrated on figure 10 at areas 177, 179, 181, and 183. Writing to one plane generates an image in one primary color. Writing the same data to two planes generates a mixed color. Using load address select override feature allows writing to both planes at the same time. To do this, the RAS override bits in the control register contained within the block 39C of Figure 3 are loaded with the binary value of the color. When writing to one plane of memoryusing this feature, the other planes are also selected. The row address select override feature also applies to shift register transfers. These shift registers, of course, are located within the display memory 5. This feature allows for clearing the screen of the CRT monitor 11 four times faster because all four row address select planes may be transferred in a single cycle. Prior to this invention, data was written to one bank of memories or plane in a single memory cycle. To draw an object requires writing to each code or plane individually.

The row address override logic is controlled by four bits which are programmed and stored in the control register 39C by the microprocessor 1 that select which row address select output bit will be forced active during the memory access cycle. These four bits are RASOR(3-0). These four bits are gated with function decode and the R/W-signals to prevent memory read conflicts. The row address override feature is enabled only for the following types of memory cycles; microprocessor 1 random access write cycle, microprocessor 1 requested shift register to memory transfer, and microprocessor 1 requested memory to shift register transfer. The four gated bits are then OR'd with the row select zero and the row select one bits to form the select for the row address select output. On Figure 10 the row address select enable is bit is brought to the row select decode logic from the cycle generator 67 and is represented by RASEN. This bit enables the four bits from the control registers which were previously enumerated by the OR logic 164 onto the XRAS(3-0) outputs. Additionally, NOR gates 162 and 163 decode the function that is being implemented being it is the row address select from the function select decode circuit that is represented by RSA, the XXY from the X-Y register 43 which indicates where the data is being written into memory, a shift register, SSRRAS from the video block 57 and the extended control register row address select bits provided from the control register 39C and represented by signal CRRAS. These signals are multiplexed by logic 161 and with NR gate 162 and 163 in conjunction with the appropriate cycle that is being implemented being its shift register cycle represented by the signal SRCCL, a refresh cycle represented by the signal REFCCL, and an XY cycle represented by the signal XYCCL. These signals are of course from the cycle generator 67 of Figure 4 and were combined by logic gates 185, in addition to the signal EHAE which is brought over from

the control register block 39C. The decode block 63 provides the function select shift register signal represented by the mnemonic FSSR and the RWB signal in which the four row select output bits are gated by the logic gates 187. The function select and the read/W- signals are combined by the NOR gate 189.

Figures 11A and 11B are schematic diagrams of the multiplexer 49, which outputs the memory address to memories 5 and 19. As was discussed in conjunction with Figure 2, the multiplexer 49 selects either the output from the row address latch 47, the refresh address counter 45, the XY address register 43 or the column address latch 61. These inputs are brought into the multiplexer 49 as signals XCAB, which is the input from the column address latch 41 and XRAB, which is the input from the row address latch 47, both of which are a part of the FS decode block 63 of Figure 3, the XXY signal which is the input from the XY register 43 of Figure 3, the XSRRA which is the shift register row address that is a part of the video block 57, and the XRACA which is the output of the refresh block 45 and the video block 57. The multiplexer in the embodiment shown includes 7 stages 250 in which the aforementioned signals are selected via pass transistors 251 and applied to the output terminals 253. The cycle generator 67 provides the select for each of the functions. EXTCASEL provides the column select, XYRASEL provides the XY row select function, XYCASEL is the column select of the XY register 43, SRRASEL is the shift register row address output select enable, and RACASEL is the refresh row address and shift register column address select enable. The OR combination of all of these functions provides a signal that is denoted EXTRASEL which connects the RA address bus 21d to the output of the multiplexer 49 at the output terminal 25. The output terminal is an 9 bit terminal and the remaining two bits are illustrated in Figure 11 D by circuits 255 and 257. Additionally, test logic is provided for testing of the VSC 3 at area 261 and is enabled by the scan outs signal that is brought into the multiplexer 49 at point 263 from the cycle generator 67 and the scan out video scanout signal which is the output of the video block 57 that is applied to the multiplexer at 265. These two signals are the circuit of a scan path that serially connects all otherwise in accessible storage nodes within the VSC 3, and is used during test of the device.

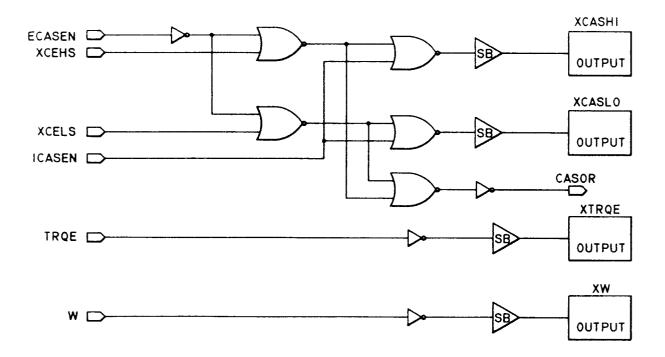

The memory pins 69 as shown in Figure 12 provide the control signals for writing into the display memory 5, the output of which are the write command, XW, the TRQE command and the two column address strobes XCASHI and XCASLO. The column address enable high and low signals that are provided from the input pins 59 are gates by ICASEN and ECASEN, both of which are generated by cycle generator 67, onto outputs XCASHI and XCASLO.

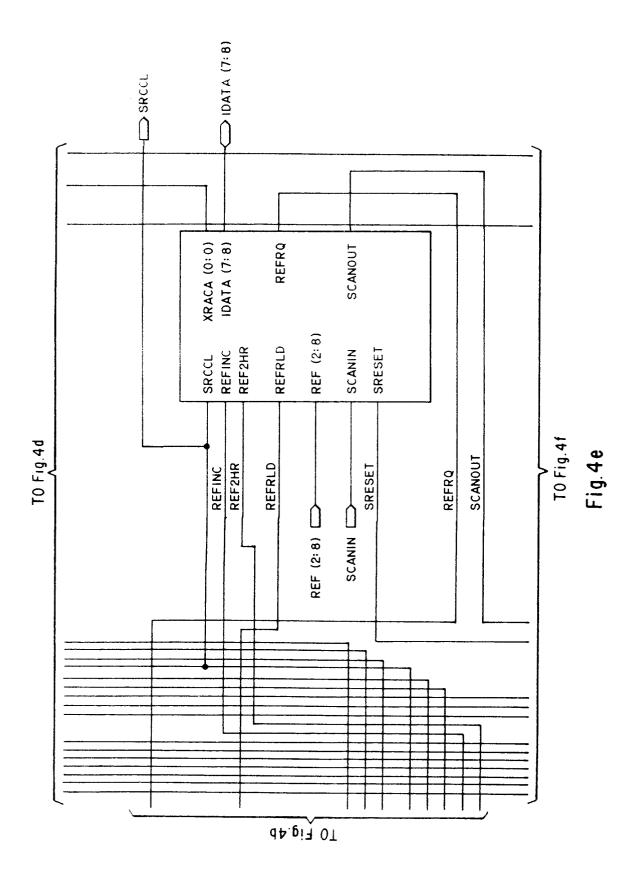

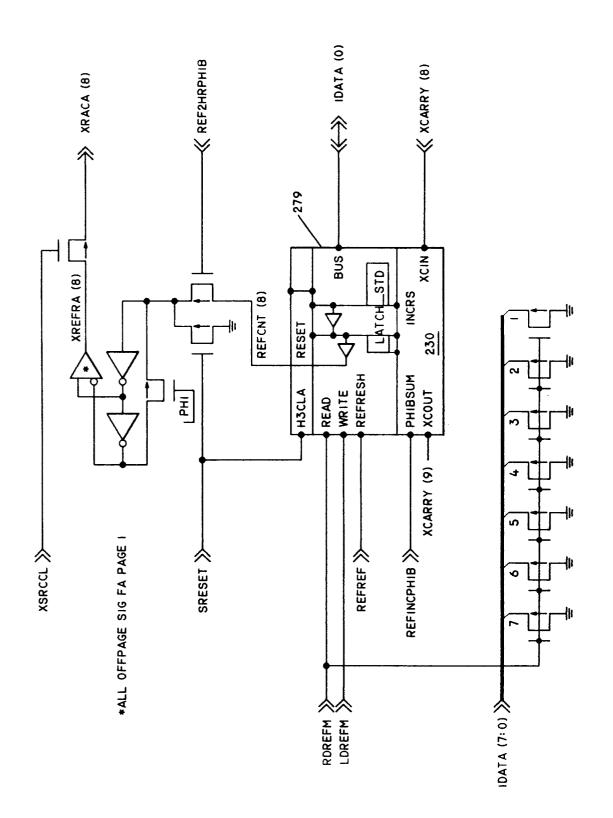

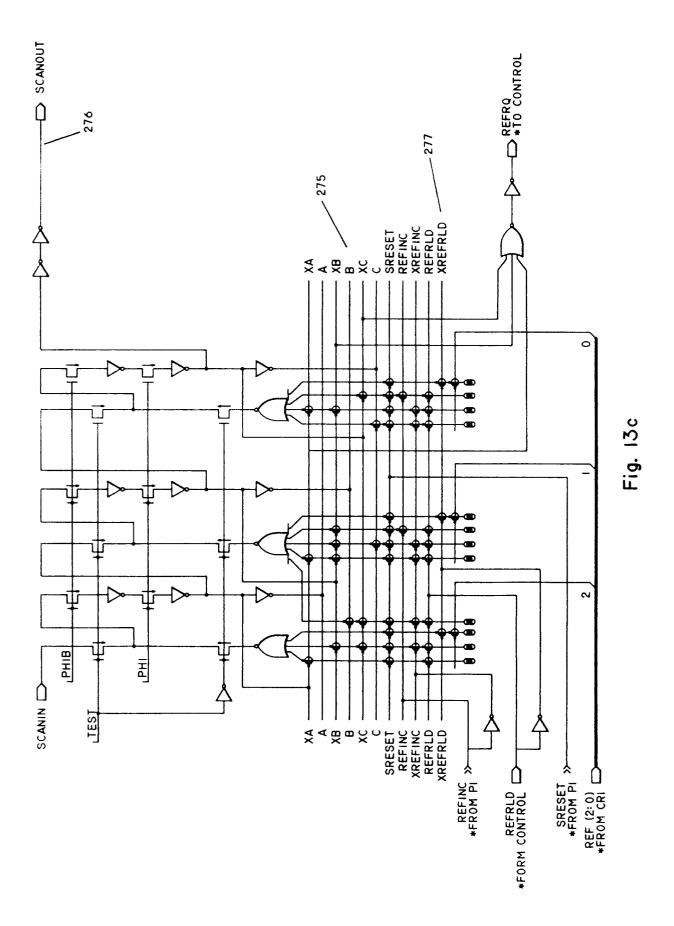

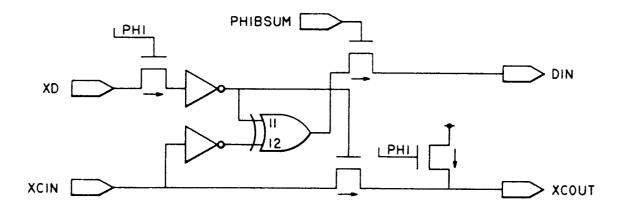

The video system controller 3 is configured to perform refresh cycles for the display memory 5 at regular intervals. The refresh counters (Figure 13) contained within the refresh address counter 45 generate 9 bit row addresses output during the refresh cycles. A refresh burst counter not accessible to the microprocessor 1, determines the number of refresh cycles per horizontal scan line. A refresh address register, also inaccessible to the microprocessor 1, maintains the current row address and is incremented following each refresh cycle. The enabling of the refresh cycles and the frequencies of the refresh cycles are determined by three control register bits within the video system controller 3. Eight of the nine bit row addresses are provided by the circuit 273 of Figure 13A which includes a refresh counter block 270 and a holding register 271. Upon command from the cycle generator via the SRCCL signal, the counter 270 is enabled to the multiplexer 49 via the bus XRACA which connects the refresh address counter 45 to the multiplexer. Figure 13B provides the remaining counter state 279 associated with counter 270. A Mealymodel state machine illustrated in Figure 13C at 275, which, as mentioned earlier, is not accessible to the host computer, determines the number of refresh cycles per horizontal scan line that are performed. Its output REFRQ is issued to control logic 71 indicating that additional refresh cycles need to be performed during the current scan line. The refresh address register 270 maintains the current row address and is incremented following each refresh cycle for the display memory 5 and system memory 19. The cycle generator 67 performs the arbitration for determining the priorities of the memory cycles that are to be

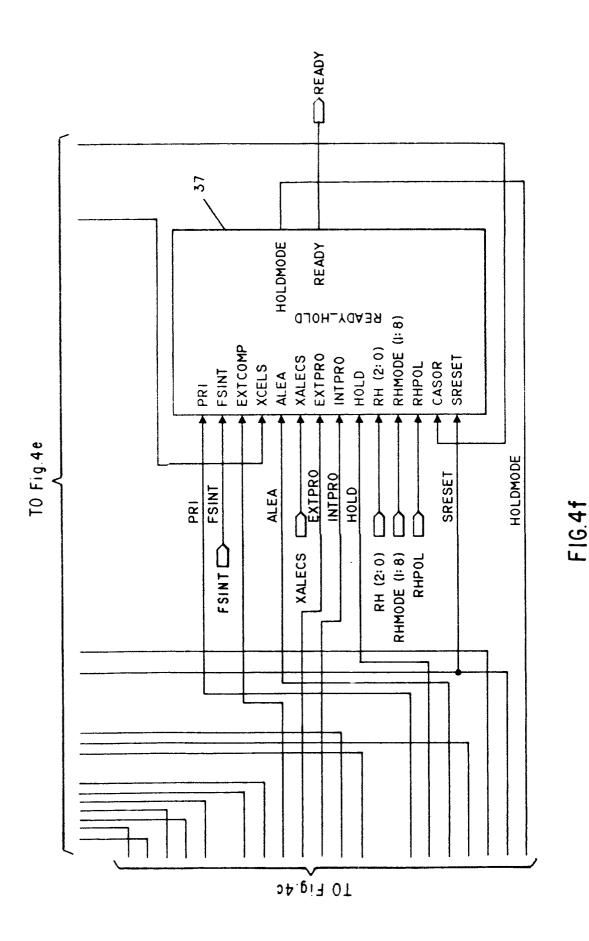

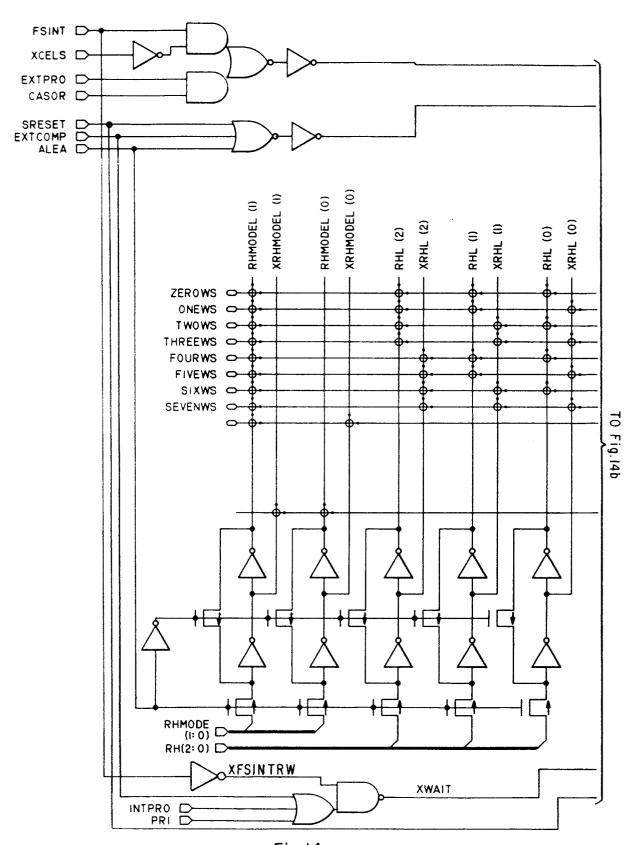

Ready hold logic 37 (Figure 14) provides the ready/hold signal which informs the microprocessor of the current status of the cycle generator 67. Several modes of operation are available, programmed by control register bits RHMODE (1-0) and RH(2-0). These modes are ready, wait and hold modes. In ready mode, the microprocessor 1 programs a particular number of wait states that are desired during a microprocessor initiated cycle by loading RH(2-0). When the cycle requested by the microprocessor 1 begins, circuits 293 provide a timing sequence, which when complete, informs the host that the cycle is complete by activating ready/hold output. If an internal cycle is in progress, or a previously requestesd microprocessor requested cycle is still underway when the microprocessor 1 requests another cycle, then the previous cycle must complete. Wait mode does not include programmable wait states, but simply informs the microprocessor that his cycle has started by activiating the ready/hold output. When ready hold logic is programmed to be in the hold mode, the VSC 3 must issue a request for the microprocessor 1 to "hold" because it is time for

the VSC 3 to perform a refresh cycle or a shift register reload cycle. The microprocessor acknowledges the request for hold by providing a logic xero level on the xholdback input. When programmed to be in either the ready or wait mode, the ready/hold output active logic level is programmable by the state of the xholdback input during reset. This completes the discussion of the system block Figure 3 and the circuits thereto as is illustrated in Figure 4 through 14.

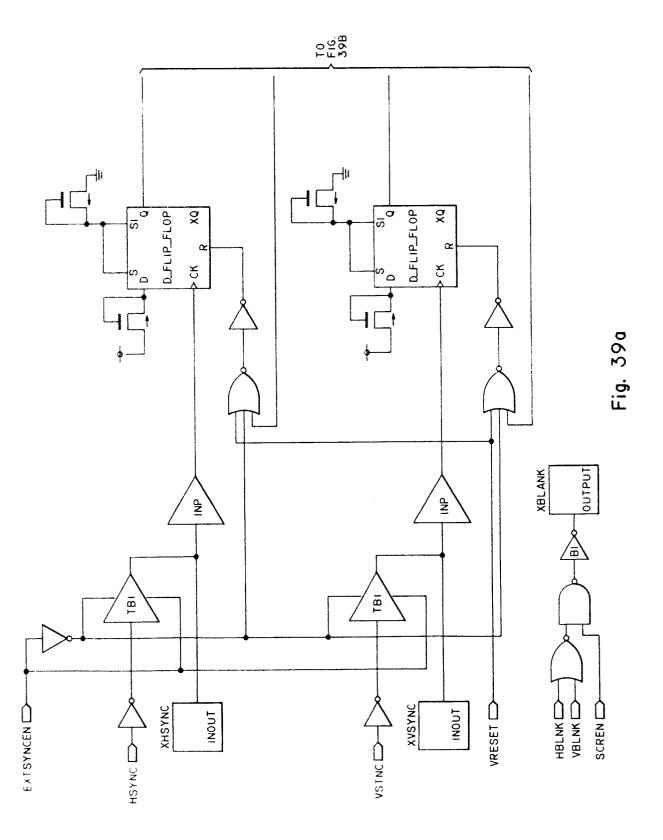

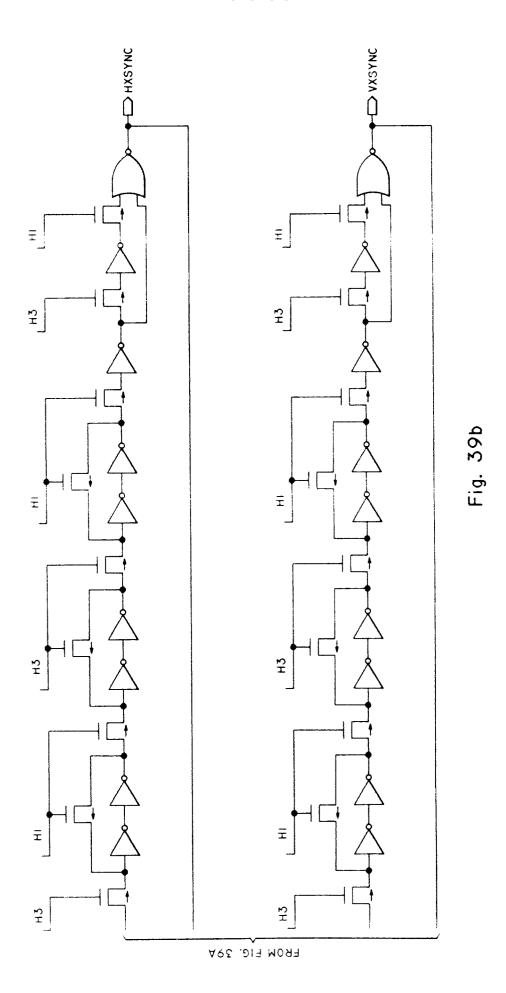

The video block 57 (Figure 15) is used to generate the horizontal sync HSYNC-, vertical sync VSYNC-, and blanksignals used to drive the CRT monitor 11 in a bit map graphic system. These signals are synchronous to the video input clock, VIDCLK. The signals output at the HSYNC-, the VSYNC- and the VLANK- pins are programmed through 8 microprocessor 1 accessible video timing registers. The vertical-control logic 97 as illustrated includes a plurality of state machine cells 301 that are a PLA 115, a logic gate 117 and a latch 119. The state machine standard cells 301 are connected in a counter figure configuration as is illustrated in Figure 15 and provide a sequence of gating signals that select which vertical counter. When the counter reaches the value in the selected timing register, the vertical control state machine cycles to the next timing register. The vertical counter register 99 counts the horizontal lines in the video displays and serves as the timing base for determining the limits of the vertical sync and blanking intervals. The contents of the vertical counters are compared with the values in the vertical timing registers to mark off the vertical sync and blanking intervals. The count is incremented by one at the beginning of each horizontal sync interval with one exception.

The exception is during the vertical front porch and sycn intervals of an old field in an interlaced frame, the increment of the vertical counter occurs at midpoint where the count and the horizontal counter 95 is equal to one-half the value in the horizontal total register 91. The vertical counter 97 is reset to zero upon reaching the value in the vertical total register 101 on the next following edge of the Vid lk after a high to low transition on an active reset-signal forces the vertical counter to zero. This interval may be read by the microprocessor 1 during the intervals between increments, but may not be written to. Multiple read cycles are normally used for accessing the vertical counter 97. Two consecutives reads returning the same data information indicates that the microprocessor 1 access is in an interval between increments.

Figure 16 is a schematic diagram of the vertical counter 99 and provides two counter stages 303 and 305. The first counter stage 305 provides for 8 bits of data and is repeated 8 times and the second stage 303 provides for 4 bits of data so that there is a maximum number of 12 bits stored in the vertical counter.

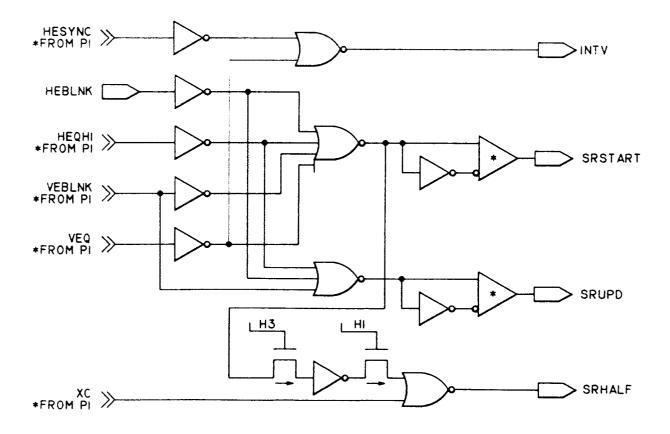

Figure 17 is a schematic diagram of the horizontal control circuit 95 in which the control signals are generated for controlling the horizontal registers 85, 87, 89, 91 and 93.

Figure 18 is a schematic diagram of the horizontal counter 93. The horizontal counter is a 12 bit counter that is divided into two stages 307 and 309, with 307 providing the first 8 bits 0-7 and 309 providing the remaining 4 bits 8-11. The horizontal counter 93 is incremented on VIDCLK falling edge, and serves as a timing base for determining the limits of the horizontal sync and blanking intervals. The value of the horizontal counter is compared to the value of the four other horizontal timing registers in order to generate the signal output HYSYNC- and BLANK-. When the horizontal counter 93 reaches the value in the horizontal total registers 91, it is reset to zero by the circuit 311. When the video system controller is configured in the external sync mode, HYSNC- is an input and the horizontal counter is forced to zero as a delay from the fallen edge of HYNC-. The vertical counter is reset in a similar way to activating the YSYNC-input. External sync mode allows the YSC 3 to "sync-up" to an external video source. This permits displaying multiple video sources on the same monitor simultaneously. External sync mode is enabled by writing to the EXTSYNCEN bit in control register 39C. Figure 38 shows the latch and synchronizing circuits which process the incoming sync pulses. An active reset- signal forces the horizontal counter 93 to zero. And this counter is not accessible to the microprocessor 1.

The remaining registers of Figure 7 are illustrated in Figure 19 which is a schematic diagram of the basic register block 313.

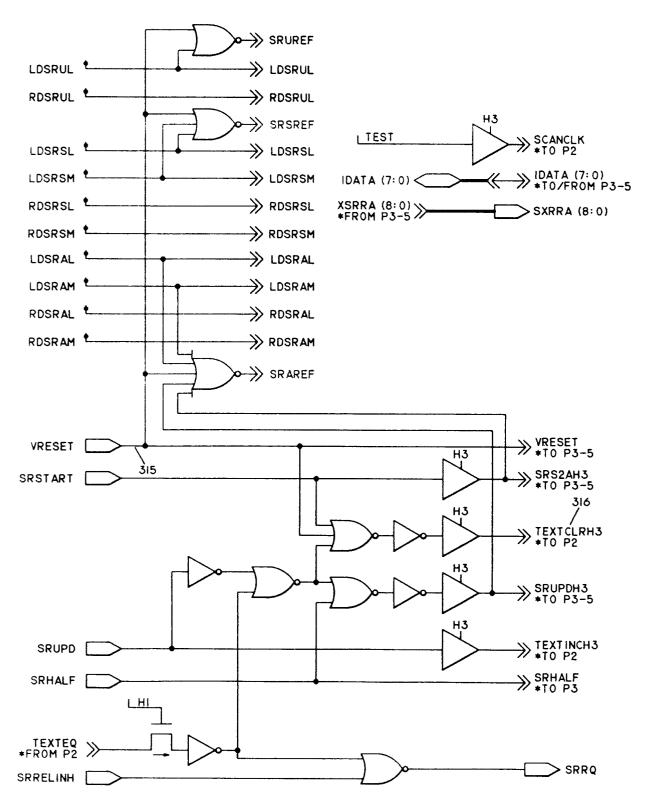

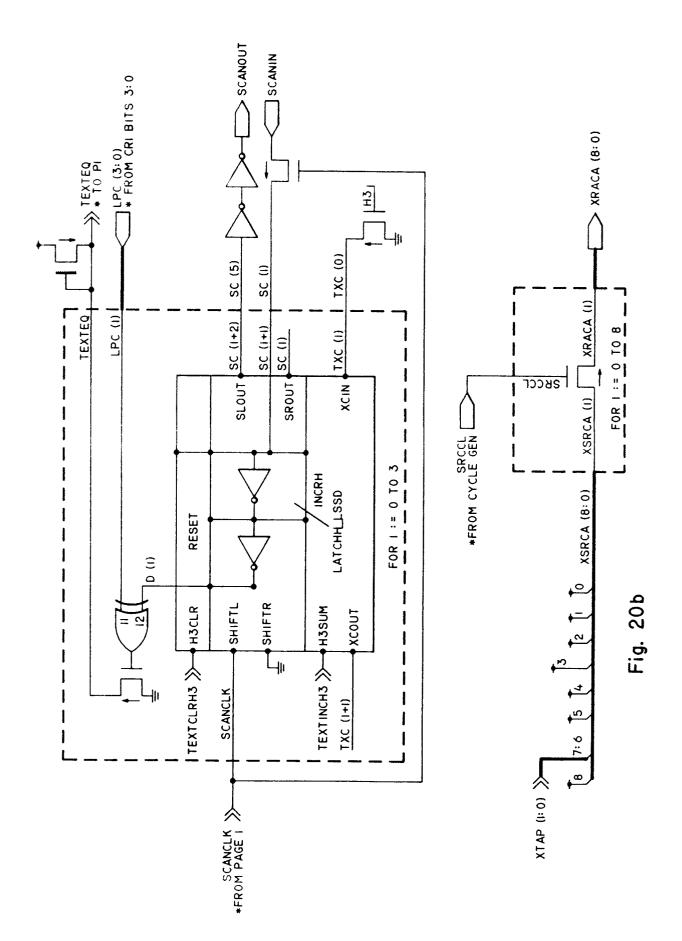

Another function of the video block 57 includes the SR data block. SR stands for shift registers which are contained within the display memory 5. A shift register read or write cycle is an access initiated by the microprocessor 1. Shift register cycles are specifically geared toward transferring data between the display memory 5 cell arrays and shift registers withing the display memory 5. Display update cycles are initiated automatically within the video system controller 3. Shift register cycles may also be initiated under explicit microprocessor 1 control. Figure 20 is a schematic diagram of the SR data control circuit that is contained within the video block 57. The direction of the transfer of data is determined by the state of control bit SRW in control register 1. A shift register transfer cycle can be initiated either by the VSC3 (display update) or by the microprocessor, whereby the type of cycle desired is determined by the function select code input on lines FS0-FS2. The function select code of a binary value of zero indicates a register access cycle, binary No. 1 an XY indirect cycle, binary 2 a register access cycle, binary 3 a microprocessor direct cycle, binary

4 a shift register cycle shift register to memory, binary 5 shift register cycle memory to shift register 6 and 7 are unused or for special functions such as test mode. A shift register write cycle transfers the contents of the shift register within the display memory 5 to the specific specified row within the on-chip memory cell array and a shift register read cycle transfers the contents of a specified row within the memory cell array to the shift register.

Figure 20A shows the generation of the control logic for the shift register address which provides the memory address to display memory 5 during VSC 3 requested display update cycles. Figure 20B is a 4 bit control that counts up to the value specified by control bits PLC(3-0) of control register 381. The state of this count determines the period of shift register reload (display update) cycles and can vary from once every horizontal scan line to once every 16 scan lines. Figure 20C 20D and 20E show the logic of the 12 bit shift register address counter. The least significant 4 bits which are shown in Figure 206 include a full adder which allows the shift register address to be incremented. In normal operation, by 1, 2, 4, or 8. The least significant 2 bits of this address specify the tap point that is selected on the external display memory 5. The next 8 significant bits are routed to the memory address output pins and represent the row address bits. The final 2 most significant bits of this counter represent the row address select control bits. These bits are decoded to one of 4 active row address selects (RAS (3-0)) during a shift register update cycle when the VSC 3 is in the extended host address enable mode programmed by setting the EHAE bit within control register 381. If this bit is inactive, then all RAS outputs are active during a shift register update cycle.

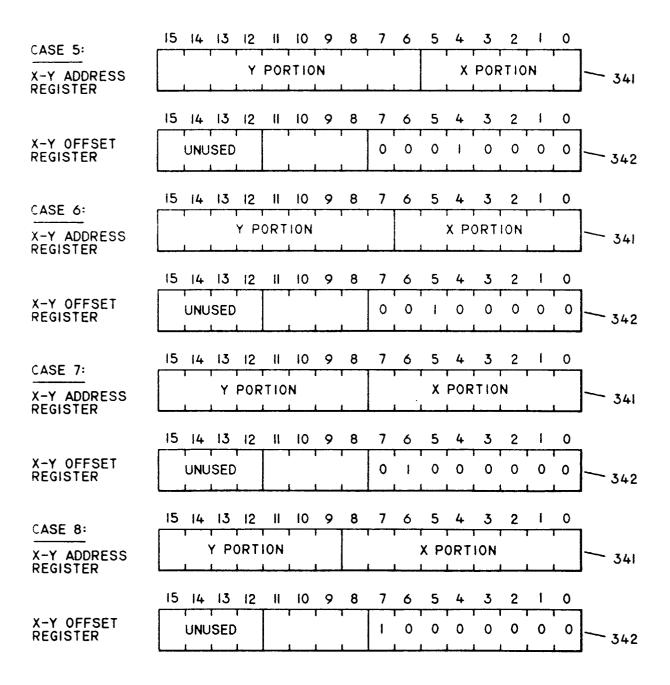

As was discussed earlier, the FS decode circuit decodes the functions that are to be implemented by the video system controller based upon the binary value of the three function select decode signals that are applied thereto. The schematic diagram of the FS decode block 63 is provided in Figure 21. The FS decode logic 63 is illustrated in Figure 21 and receives from the microprocessor 1 control signals FSO-2, row select signal RSO-1, plus column address on data bus 21C and row address on data bus 21R, as well as the CS signal which is brought into the FS decode circuit 63. Additionally a reset signal is provided from the input pins block 59 as is the ALE signal and the no latch signal, which comes from the control registers. It provides the row address, the column address, and the complements thereto, as well as decoding the function select inputs. The different functions are decoded by the PLA 331 and correspond to the previously denoted functions. In order for any function select decode to be active, the chip select input (XCS) must be active. Additionally, circuit 333 and 335 provides for the scan and test mode generation. Line drivers 334 are used to drive the row address signals and the column address signals.