① Veröffentlichungsnummer: 0 500 147 A2

## **EUROPÄISCHE PATENTANMELDUNG**

(21) Anmeldenummer: **92107715.2**

(51) Int. Cl.5: G09G 1/16

2 Anmeldetag: 21.03.90

(12)

Diese Anmeldung is am 07 - 05 - 1992 als Teilanmeldung zu der unter INID-Kode 60 erwähnten Anmeldung eingereicht worden.

Priorität: 12.05.89 DE 3915562

(43) Veröffentlichungstag der Anmeldung: 26.08.92 Patentblatt 92/35

© Veröffentlichungsnummer der früheren Anmeldung nach Art. 76 EPÜ: 0 468 973

Benannte Vertragsstaaten:

AT BE CH DE DK ES FR GB IT LI LU NL SE

Anmelder: SPEA SOFTWARE AG Moosstrasse 18b W-8130 Starnberg(DE)

② Erfinder: Schwarz, Stefan Seehang 2 W-8137 Berg(DE) Erfinder: Cartwright, Ian Föhrenstrasse 4 W-8036 Stockdorf(DE)

Vertreter: Schoppe, Fritz, Dipl.-Ing. Seitnerstrasse 42 W-8023 Pullach bei München(DE)

## (S4) Verfahren zur Ansteuerung eines Monitors und Monitorsteuerschaltung.

© Eine Monitorsteuerschaltung dient zur Ansteuerung eines Monitors, dessen Anzeige durch Auslesen eines digitalen Bildsignales mit einer zweiten Pixelfrequenz aus einer Videospeichervorrichtung erzeugbar ist, aufgrund eines eine erste Pixelfrequenz aufweisenden digitalen Bildsignales.

Zur lückenfreien Umwandlung des ersten Bildsignales in das zweite Bildsignal oder zur Kombination von Bildsignalen unterschiedlicher Graphikstandards wird das digitale Bildsignal der ersten Pixelfrequenz mit einer von der ersten Pixelfrequenz abhängigen Frequenz in eine Fifo-Speichervorrichtung (3) eingelesen, und es wird ein Auslesen von in die Videospeichervorrichtung (4) einzuspeichernden Datenworten des digitalen Bildsignales aus der Fifo-Speichervorrichtung (3) nur während solcher Zeitabschnitte vorgenommen, während der kein Auslesen von Daten aus der Videospeichervorrichtung (4) stattfindet, wodurch die aus der Fifo-Speichervorrichtung (3) zur Einspeicherung in die Videospeichervorrichtung (4) auslesbare Datenwortzahl variieren kann.

15

Die vorliegende Erfindung befaßt sich mit einem Verfahren zur Ansteuerung eines bei einer zweiten Pixelfrequenz arbeitenden Monitors, dessen Anzeige durch Auslesen eines digitalen Bildsignales mit einer zweiten Pixelfrequenz aus einer Videospeichervorrichtung erzeugbar ist, aufgrund eines eine erste Pixelfrequenz aufweisenden digitalen Bildsignales, nach dem Oberbegriff des Anspruchs 1. Ferner befaßt sich die vorliegende Erfindung mit einer Monitorsteuerschaltung, die dazu dient, einen bei einer zweiten Pixelfrequenz arbeitenden Monitor anzusteuern, dessen Anzeige durch Auslesen eines digitalen Bildsignales mit der zweiten Pixelfrequenz aus einer Videospeichervorrichtung erzeugbar ist, aufgrund eines eine erste Pixelfrequenz aufweisenden digitalen Bildsignales, nach dem Oberbegriff des Patentanspruchs 5.

Computermonitore werden bekannterweise in Abhängigkeit von den Anforderungen bezüglich der geforderten Bildschirmauflösung durch Graphikkarten unterschiedlicher Kategorien angesteuert, die sich untereinander durch die horizontale und vertikale Auflösung, also die Anzahl der Pixel, in horizontaler und vertikaler Richtung sowie durch die Pixelfrequenzen unterscheiden. Graphikkarten-Standards sind beispielsweise MDA (320 x 200 Bildpunkte, Schwarzweiß, bei 16 MHz Pixelfrequenz), CGA (320 x 200 Bildpunkte, Farbe, bei 20 MHz Pixelfrequenz), HERCULES (740 x 400 Bildpunkte, Schwarzweiß, bei 27 MHz Pixelfrequenz), EGA (640 x 350 Bildpunkte, Farbe, bei 30 MHz Pixelfrequenz), VGA (640 x 480 Bildpunkte, Farbe, bei 32 MHz Pixelfrequenz), SUPER-EGA (800 x 600 bzw. 1024 x 768 Bildpunkte, Farbe, bei 50 MHz Pixelfrequenz, sowie neuerdings die sogenannten HR (High Resolution)-Graphiksysteme mit 1024 x 768, 1080 x 1024 sowie 1600 x 1280 Bildpunkten, Farbe, bei Pixelfrequenzen zwischen 60 MHz und 170 MHz. Für den Fachmann ist es offensichtlich, daß sich diese verschiedenen Graphik-Standards auch bezüglich der Zeilenfrequenzen, also dem Kehrwert der Horizontalsynchronisationssignalperioden, unterscheiden, die für die genannten Systeme bei 17 kHz, 22 kHz, 25 kHz, 31,5 kHz, 50 kHz sowie 64 bis 84 kHz liegen.

Es besteht seit längerer Zeit der Wunsch, die Ausgangssignale der verschiedenen Graphik-Standards mittels eines einzigen Monitores zu Bildschirmbildern umwandeln zu können. Zu diesem Zweck bedient man sich derzeit sogenannter "Multisync"-Monitore, die in der Lage sind, mittels umschaltbarer Schwingkreise mit verschiedenen Horizontalsynchronisationssignalfrequenzen zu arbeiten. Da die Umschaltung des "Multisync"-Monitores von einer Graphiknorm auf die nächste und somit von einer Arbeitsfrequenz auf die nächste mit einer gewissen Einschwingzeit verbunden ist, führt die Umschaltung der Bildschirmdarstellung von ei-

ner Graphiknorm auf eine nächste zu zeitlichen Unterbrechungen der Bildschirmanzeige oder anfänglichen Bildstörungen. Selbstredend steigt die Komplexität eines "Multisync"-Monitores mit zunehmender Anzahl der durch diesen bewältigbaren Graphikkarten-Standards an. Eine Anzeige zweier Teilbilder, die von zwei verschiedenen Graphikkarten kreiert werden, auf einem gemeinsamen Bildschirm ist bei den bekannten "Multisync"-Monitoren gleichfalls nicht möglich.

Die DE-A1-38 04 460 offenbart bereits eine Monitorsteuerschaltung für Ansteuerung eines bei einer zweiten Pixelfrequenz arbeitenden Monitores aufgrund eines eine erste Pixelfrequenz aufweisenden digitalen Bildsignales, mit einem eingangsseitigen Seriell-Parallel-Wandler in Form eines Schieberegisters, an dessen Ausgang eine Videospeichervorrichtung angeschlossen ist, in die das eingangsseitige Bildsignal nach seiner Seriell-Parallel-Wandlung ablegbar ist. Da es sich bei dem Speicher lediglich um ein Schieberegister zur Seriell-Parallel-Wandlung handelt, das zum Zwecke der Seriell-Parallel-Wandlung mit dem Takt des Subsystems nach dem jeweiligen Auftreten des Blanksianales des Subsystemes getaktet wird, wird das eingangsseitige Bildsignal mit der Frequenz seines Subsystemtaktes in die Videospeichervorrichtung eingeschrieben. Wegen der fehlenden Synchronität des Einschreibens des Bildsignales in die Videospeichervorrichung mit dem ersten Subsystemtakt und des Auslesens aus dem Videospeicher mit dem Hauptsystemtakt können Überschneidungen des Einschreibens und des Auslesens auftreten. Diese Überschneidungen werden nach dem Stand der Technik dadurch ausgeräumt, daß einige Bildelemente eines ieden Teilbildes nicht aktualisiert werden, indem dem Transferzyklus und somit dem Auslesen des Videospeichers ein Vorrang gegenüber dem Auffrischen eingeräumt wird. Die Folge dieser Art der Steuerung ist ein teilweise nicht aktueller Bildinhalt der jeweiligen Teilbilder.

Aus der DE-A1-34 25 636 ist es bekannt, bei einer Raster-Aufzeichnungseinrichtung, deren Rasterelemente in einer vorbestimmten Folge angesteuert werden müssen, und die einen Bildspeicher aufweist, zwischen einem Prozessor und der Aufzeichnungseinrichtung einen Fifo-Speicher anzuordnen. Sobald der Fifo-Speicher leer ist, unterbricht ein Interrupt-Befehl das im Prozessor laufende Programm, woraufhin neue Daten in den Fifo-Speicher eingeschrieben werden, wobei nach dessen Füllen der Prozessor den unterbrochenen Programmlauf wieder aufnimmt.

Aus dem Fachbuch Jan Hendrik Jansen, Anwendungen digitaler Bauelemente, Franzis-Verlag, ISBN 3-7723-7931-1, 1985, ist es bekannt, daß Fifo-Speicher Register sind, die in der digitalen Elektronik zum Speichern von Zwischenergebnis-

55

20

25

40

sen dienen und die zur Koppelung von nach unterschiedlichen Zeitschemata arbeitenden Medien eingesetzt werden können. Mit Monitorsteuerschaltungen befaßt sich diese Fachveröffentlichung nicht.

Aus der FR-A-2 608 291 ist eine Schaltung zur Anpassung einer Graphikkarte einer bestimmten Fernsehnorm an einen Monitor einer anderen Fernsehnorm bekannt, bei der eine durch einen Videoprozessor erfolgende Datenverarbeitung durch einen periodisch erzeugten Auftastimpuls in Relation zu den für die Konvertierung nötigen auszulassenden oder einzufügenden Bildzeilen unterbrochen wird. Dies ermöglicht keine vollständige Aktualisierung des Monitorbildes.

In Hinblick auf diesen Stand der Technik liegt der vorliegenden Erfindung die Aufgabe zugrunde, ein Verfahren zur Ansteuerung eines Monitors und eine Monitorsteuerschaltung der eingangs genannten Art zu schaffen, durch die ein bei einer zweiten Pixelfrequenz arbeitender Monitor mittels eines eine erste Pixelfrequenz aufweisenden digitalen Bildsignales ansteuerbar ist, wobei die anzuzeigenden Bildsignale jeweils aktualisiert sein sollen.

Diese Aufgabe wird durch ein Verfahren gemäß Patentanspruch 1 und durch eine Monitorsteuerschaltung gemäß Patentanspruch 5 gelöst.

Der Erfindung liegt die Erkenntnis zugrunde, daß die Ansteuerung des mit der zweiten Pixelfrequenz arbeitenden Monitores, die mit der ersten Pixelfrequenz weder synchronisiert ist noch üblicherweise in einem festen, geraden Zahlenverhältnis steht, mittels des Bildsignales der ersten Pixelfrequenz dann möglich ist, wenn die Datenworte des digitalen Bildsignales zunächst in einer Fifo-Speichervorrichtung zwischengespeichert werden, bevor sie in eine Videospeichervorrichtung abgelegt werden, die in Synchronisation mit dem Betrieb des Monitores bei der zweiten Pixelfrequenz in einer an sich bekannten Weise auslesbar ist, um die Monitoranzeige zu erzeugen. Wie noch näher erläutert wird, bewirkt die Übertragung der Datenworte von der Fifo-Speichervorrichtung in die Videospeichervorrichtung eine Steuervorrichtung, die mit der Videospeichervorrichtung und der Fifo-Speichervorrichtung verbunden ist und diese in der Weise ansteuert, daß Datenworte aus der Fifo-Speichervorrichtung in die Videospeichervorrichtung einschreibbar ist.

Bevorzugte Weiterbildungen sind in den Unteransprüchen angegeben.

Nachfolgend wird unter Bezugnahme auf die beiliegenden Zeichnungen eine bevorzugte Ausführungsform der erfindungsgemäßen Monitorsteuerschaltung näher erläutert. Es zeigen:

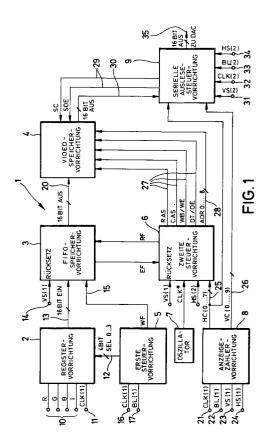

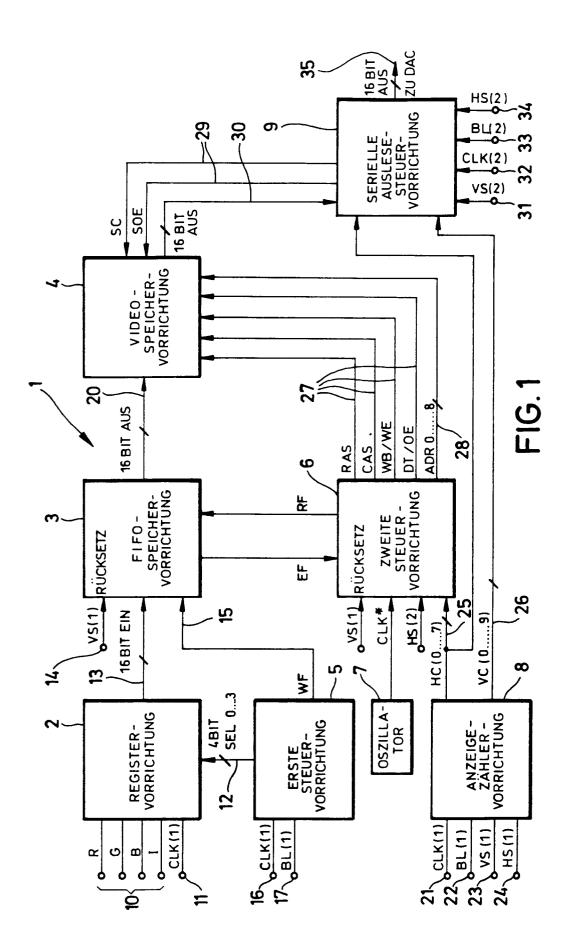

- Fig. 1 ein Blockdiagramm einer Ausführungsform der erfindungsgemäßen Monitorsteuerschaltung;

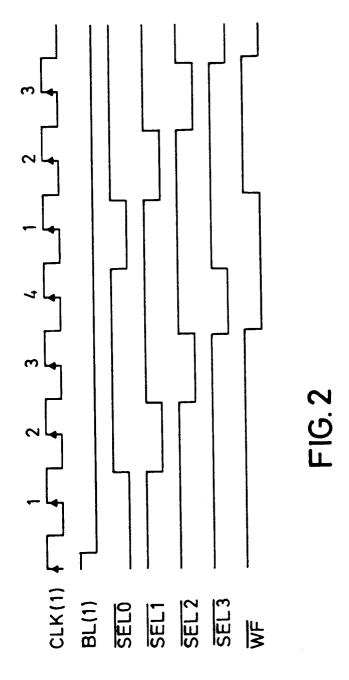

- Fig. 2 eine zeitliche Darstellung von Signal-

- verläufen zur Erläuterung der Funktionsweise einer ersten Steuervorrichtung gemäß Fig. 1;

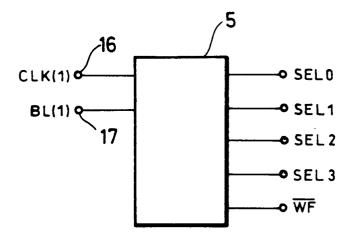

- Fig. 3 eine Blockdarstellung der in Fig. 1 gezeigten ersten Steuervorrichtung;

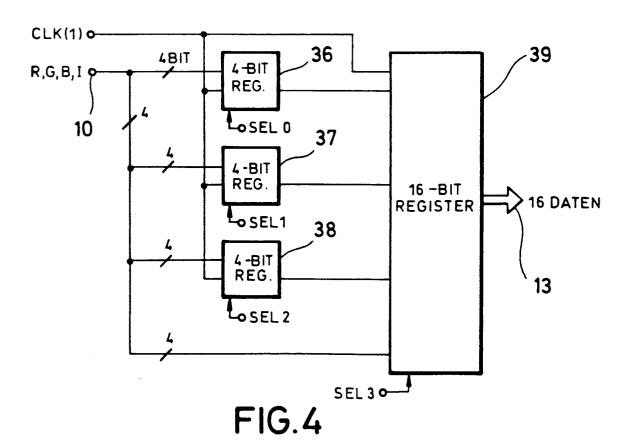

- Fig. 4 ein Blockdiagramm einer in Fig. 1 gezeigten Registervorrichtung;

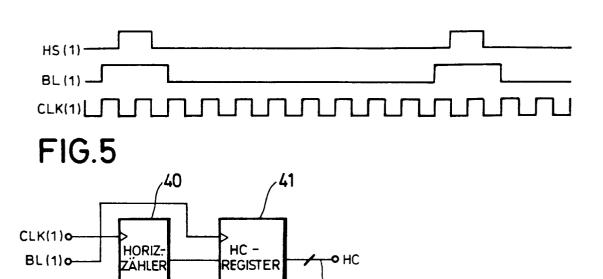

- Fig. 5 eine zeitliche Darstellung von Signalverläufen zur Erläuterung der Funktionsweise einer in Fig. 1 gezeigten Anzeigezählervorrichtung;

- Fig. 6 ein Blockdiagramm eines Details der Anzeigezählervorrichtung gemäß Fig. 1:

- Fig. 7 eine zeitliche Darstellung von Signalverläufen zur Erläuterung der Funktion eines weiteren Teiles der in Fig. 1 gezeigten Anzeigezählervorrichtung;

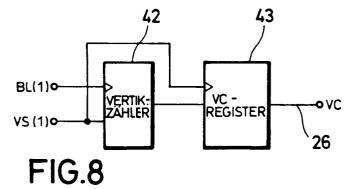

- Fig. 8 ein Blockdiagramm eines weiteren Teiles der in Fig. 1 gezeigten Anzeigezählervorrichtung;

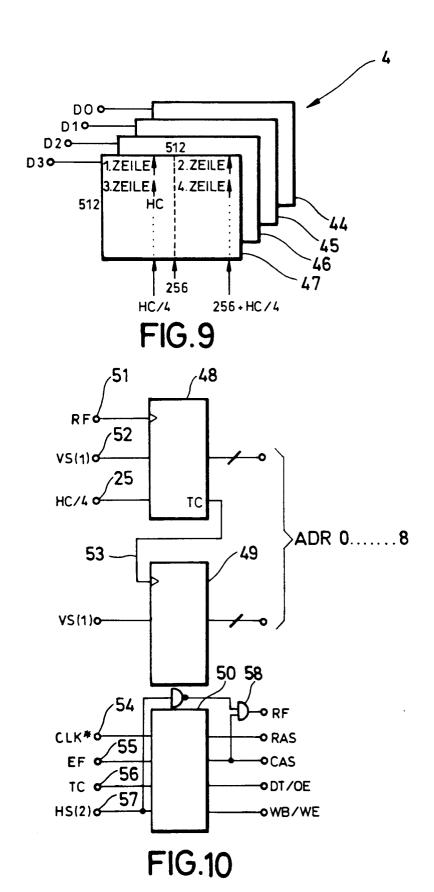

- Fig. 9 eine schematische Darstellung der Speicherorganisation einer in Fig. 1 gezeigten Videospeichervorrichtung; und

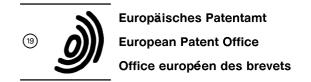

- Fig. 10 Bockdiagramme der Struktur einer in Fig. 1 gezeigten zweiten Steuervorrichtung.

Die in Fig. 1 gezeigte Ausführungsform einer Monitorsteuervorrichtung gemäß der vorliegenden Erfindung, die in ihrer Gesamtheit mit dem Bezugszeichen 1 bezeichnet ist, umfaßt eine Registervorrichtung 2, eine als Fifo-Speichervorrichtung ausgebildete erste Speichervorrichtung 3, eine Videospeichervorrichtung 4, eine erste Steuervorrichtung 5, eine zweite Steuervorrichtung 6, einen Oszillator 7, eine Anzeigezählervorrichtung 8 und eine serielle Auslesesteuervorrichtung 9.

Die Registervorrichtung 2 ist eingangsseitig mit einem Eingangsdatenbus 10 verbunden, auf dem Datenworte eines digitalen Bildsignales mit der ersten Pixelfrequenz vorliegen. Der Eingangsdatenbus 10 kann sich beispielsweise zu einer VGA-Schnittstelle erstrecken. Der Eingangsdatenbus 10 umfaßt im Beispielsfall je einen Anschluß für die drei Grundfarben R, G, B und einen Anschluß für ein Helligkeitsbit I. Jedes Datenwort stellt ein Pixel mit 4 bit Tiefe dar. Die Registervorrichtung 2 ist ferner eingangsseitig mit einem Taktsignaleingang 11 für ein Taktsignal mit der ersten Pixelfrequenz versehen. Die Registervorrichtung 2 empfängt von der ersten Steuervorrichtung 5 Auswahlsignale SEL0, SEL1, SEL2, SEL3 über einen Auswahldatenbus 12, der vier Bit hat. Ausgangsseitig steht die Registervorrichtung 2 über einen ersten Datenbus 13 mit Eingängen der Fifo-Speichervorrichtung 3 in Verbindung, welche ferner einen Rücksetzein-

15

25

gang 14 hat, dem ein Vertikalsynchronisationssignal VS(1) des ersten Bildsignales zuführbar ist. Ferner werden der Fifo-Speichervorrichtung 3 von der ersten Steuervorrichtung 5 an ihrem Schreibeingang 15 ein Schreibbefehlssignal WF zugeführt. Die erste Steuervorrichtung 5 hat einen Takteingang 16 für das erste Taktsignal CLK(1), einen Blankeingang 17 für das Blanksignal BL(1) des ersten Bildsignales.

5

Ausgangsseitig steht die Fifo-Speichervorrichtung 3 über einen zweiten Datenbus 20 mit der Videospeichervorrichtung 4 in Verbindung.

Die Anzeigezählervorrichtung 8 hat einen Takteingang 21 für das erste Taktsignal CLK(1), einen Blankeingang 22 für das Blanksignal BL(1) des ersten Bildsignales, einen Vertikalsynchronisationseingang 23 für das Vertikalsynchronisationssignal VS(1) und einen Horizontalsynchronisationseingang 24 für das Horizontalsynchronisationssignal HS(1).

Ausgangsseitig steht die Anzeigezählervorrichtung 8 mittels eines dritten Datenbusses 25 für einen Horizontalzählwert HC mit der zweiten Steuervorrichtung 6 sowie mit der seriellen Auslesesteuervorrichtung 9 in Verbindung. Ferner steht die Anzeigezählervorrichtung 8 über einen vierten Datenbus 26 für einen Vertikalzählwert VC mit der seriellen Auslesesteuervorrichtung in Verbindung.

Ausgangsseitig steht die zweite Steuervorrichtung 6 mit Eingängen der Videospeichervorrichtung über einen Steuerbus 27 und einen Adreßbus 28 in Verbindung. Der Steuerbus 27 umfaßt je eine Leitung für ein Reihenadreßübernahmesignal RAS, ein Spaltenadreßübernahmesignal CAS, ein Schreibbefehlssignal WB/WE und ein Datenübertragungssignal DT/OE für die Übernahme einer Datenzeile aus der Videospeichervorrichtung 4 in ein (nicht gezeigtes) Ausleseschieberegister derselben.

Die serielle Auslesesteuervorrichtung 9 steht ausgangsseitig über einen zweiten Steuerbus 29 für Steuersignale SC, SOE für das Auslesen der Videospeichervorrichtung 4 mit Steuereingängen der letztgenannten in Verbindung. Die Videospeichervorrichtung 4 steht wiederum über einen fünften Datenbus 30 mit einem Dateneingang der seriellen Auslesesteuervorrichtung 9 in Verbindung, die ihrerseits einen Vertikalsynchronisationseingang 31 für das Vertikalsynchronisationssignal VS(2) des zweiten, monitorseitigen Bildsignales, einen Takteingang 32 für ein zweites Taktsignal CLK(2) mit der zweiten Pixelfrequenz, einen Blankeingang 33 für das zweite Blanksignal BL(2) sowie einen Horizontalsynchronisationseingang 34 für das Horizontalsynchronisationssignal HS(2) des zweiten, monitorseitigen Bildsignales aufweist.

Ausgangsseitig steht die serielle Auslesesteuervorrichtung 9 über einen sechsten Datenbus 35 mit dem Digital-Analog-Wandler DAC des (nicht dargestellten) Monitors in Verbindung. Da die Struktur des Monitors der im Stand der Technik üblichen entspricht, bedarf es nicht deren Erläuterung.

Nachfolgend wird die Funktionsweise der bevorzugten Ausführungsform gemäß Fig. 1 erläutert, wobei jedoch bezüglich schaltungsmäßigen und funktionellen Details auf die nachfolgende Erläuterung zu den Fig. 2 bis 10 verwiesen wird.

Die Registervorrichtung 2 führt eine Seriell-Parallel-Umsetzung von jeweils vier aufeinanderfolgenden Datenworten, die mit der Pixelfrequenz am Eingangsdatenbus 10 anliegen, durch, wobei die ausgangsseitig erzeugten Datenworte die vierfache Bitzahl haben, also Datenworte einer Länge von 16 Bit sind, die parallel auf den ersten Datenbus 13 gegeben werden. Diese Umsetzung von 4-bit-Datenworten in 16-bit-Datenworte erfolgt unter der Steuerung der ersten Steuervorrichtung 5 mittels der Auswahlsignale SEL0, ... SEL3, die nach Abschluß dieser Umsetzung der Fifo-Speichervorrichtung 3 ein Schreibbefehlssignal 15 zuführt. Sobald mindestens ein Datenwort in der Fifo-Speichervorrichtung 3 abgespeichert ist, erlischt das von dieser der zweiten Steuervorrichtung 6 zugeführte Flag EF über den leeren Speicherzustand der Fifo-Speichervorrichtung, wodurch die zweite Steuervorrichtung darüber informiert wird, daß in der Fifo-Speichervorrichtung 3 in die Videospeichervorrichtung 4 umspeicherbare Datenworte vorliegen. Wie der Name sagt, ist die Fifo-Speichervorrichtung 3 derart aufgebaut, daß in diese zuerst eingelesene Datenworte bei Ansteuerung durch den Lesebefehl RF zuerst über den zweiten Datenbus 20 in die Videospeichervorrichtung 4 eingelesen werden. Wie nachfolgend noch näher erläutert wird, bewirkt die zweite Steuervorrichtung pro Schreibzyklus der Videospeichervorrichtung 4 bzw. Lesezyklus der Fifo-Speichervorrichtung 3 eine Umspeicherung einer Mehrzahl von Datenworten aus der ersten Speichervorrichtung 3 in die Videospeichervorrichtung 4, wobei die jeweils umgespeicherte Datenwortzahl, wie noch erläutert wird, von Fall zu Fall variieren

Wie noch näher erläutert wird, benötigt die zweite Steuervorrichtung 6 für die richtige Abspeicherung des digitalen Bildsignales in der Videospeichervorrichtung eine Information über die Anzahl der Pixel pro Zeile des eingangsseitig anliegenden Bildsignales, die auch durch die serielle Auslesesteuervorrichtung 9 benötigt wird, welche zusätzlich die Anzahl der Zeilen des Bildes des eingangsseitigen Bildsignales für die Auslesesteuerung benötigt. Zu diesem Zwecke ermittelt die Anzeigezählervorrichtung 8 bei dem gezeigten, bevorzugten Ausführungsbeispiel durch Zählen der Taktsignale CLK(1) zwischen zwei Blanksignalen BL(1) einen Horizontalzählwert HG(0...9) sowie durch Zählen der Anzahl der Blanksignale BL(1) zwischen

zwei Vertikalsynchronisationssignalen VS(1) die Anzahl der Zeilen des durch das erste Bildsignal dargestellten Bildes als Vertikalzählwert VC(0...9).

7

Die zweite Steuervorrichtung arbeitet auf einer Zeitbasis, die durch den Oszillator 7 festgelegt wird, wobei der Anfang eines Zyklus durch das Auftreten des Vertikalsynchronisationssignales VS-(1) am Rücksetzeingang festgelegt wird. Das der zweiten Steuervorrichtung gleichfalls Zugeführte zweite (ausgangsseitige) Blanksignal BL(2) dient allein zur Steuerung des Auffrischens der dynamischen Videospeichervorrichtung 4 und zur Steuerung der Schieberegisterübernahme, das die Übernahme einer ganzen Speicherzeile aus der Videospeichervorrichtung 4 in das Ausgangsschieberegister (nicht dargestellt) ermöglicht, und unterbricht zu diesem Zweck die Zyklussteuerung für die Ansteuerung der Fifo-Speichervorrichtung 3 und der Videospeichervorrichtung 4. Die Ansteuerung der Videospeichervorrichtung beginnt mit der Adressierung der ersten Zeile und der ersten Spalte der Videospeichervorrichtung 4 bei Nicht-Vorliegen des Flag EF, wobei die Adressenübernahme durch das Reihenadreßübernahmesignal RAS und das Spaltenadreßübernahmesignal CAS gesteuert werden, wobei während des Schreibmodus das Schreibbefehlssignal WB/WE "tief" ist. Die Übernahme der Datenworte von der Fifo-Speichervorrichtung 3 in die Videospeichervorrichtung 4 geschieht im sogenannten "page-mode", wobei die Zeilenadressierung und das Zeilenadreßübernahmesignal RAS während des Einspeicherns von Datenworten in die verschiedenen Spalten dieser Zeile unverändert bleiben, wodurch in an sich bekannter Weise die Einschreibgeschwindigkeit des Videospeichers erhöht wird. Die genaue Abfolge der einzelnen Steuersignale hängt von der Herstellerspezifikation der Videospeichervorrichtung 4 für den bei diesen Vorrichtungen vorgesehenen "page-mode"-Schreibmodus. Details der Adressierung werden unter Bezugnahme auf die Fig. 9 und 10 näher erläutert.

Die Steuerung des seriellen Auslesens der Videospeichervorrichtung durch die serielle Auslesesteuervorrichtung 9 erfolgt in Synchronisation mit dem monitorseitig vorliegenden zweiten Horizontalsynchronisationssignal HS(2), Verikalsynchronisationssignal VS(2), Taktsignal CLK(2) und Blanksignal BL(2) in einer an sich bekannten Weise.

An dieser Stelle sei auf einen wesentlichen Aspekt der Erfindung hingewiesen, der sich aus der erfindungsgemäßen Umsetzung des Bildsignales der ersten Pixelfrequenz in ein Bildsignal der zweiten Pixelfrequenz ergibt. Es ist möglich, nicht nur das am ausgangsseitigen sechsten Datenbus 35 generierte Bildsignal dem Monitor zuzuführen, sondern auch dieses Bildsignal mit einem zweiten, synchronen Bildsignal zu kombinieren, von dem die ausgangsseitige Zeitbasis (VS(2), CLK(2), BL-

(2), HS(2)) erhalten wurde. Damit ist eine Kombination eines beliebigen ersten Bildsignales, der am Eingang 10, 11 der Schaltung anliegt, mit einem beliebigen zweiten, von einem anderen Graphikstandard stammenden Bildsignal in der Weise möglich, daß das erste Bildsignal auf einer Teilfläche des Monitors zur Anzeige gebracht wird und das zweite Bildsignal auf der restlichen Monitorfläche gezeigt wird.

Die Fig. 2 und 3 verdeutlichen die Betriebsweise der ersten Steuervorrichtung 5, die im wesentlichen als Zähler arbeitet. Durch das erste Blanksignal BL(1) wird die erste Steuervorrichtung 5 in einen Anfangszustand gesetzt, um bei Auftreten eines ersten Taktpulses CLK(1) (mit schaltungstechnisch bedingter Verzögerung) ein nulltes Auswahlsignal SEL0 rückzusetzen und ein erstes Auswahlsignal SEL1 zu setzen, wobei beim zweiten Taktpuls CLK(1) das erste Auswahlsignal rückgesetzt und das zweite Auswahlsignal SEL2 gesetzt wird, usw., wobei schließlich nach dem dritten Puls das dritte Auswahlsignal SEL3 rückgesetzt und das Fifo-Schreibsignal WF gesetzt wird, woraufhin nach dem vierten Taktpuls das dritte Auswahlsignal rückgesetzt und das Fifo-Schreibsignal nach dem darauffolgenden ersten Takt rückgesetzt wird. Diese gestaffelten Auswahlsignale SEL0 bis SEL3 werden zur Steuerung der Registervorrichtung 2 verwendet, deren detaillierter Aufbau nachfolgend unter Bezugnahme auf Fig. 4 näher erläutert wird.

Die Registervorrichtung 2 umfaßt drei 4-bit-Register 36, 37, 38 und ein 16-bit-Register 39, die sämtlich mit dem Taktsignaleingang 11 und mit dem Eingangsdatenbus 10 in Verbindung stehen. Die Ausgänge der 4-bit-Register 36 bis 38 sind mit Eingängen des 16-bit-Registers 39 verbunden. Die Register 36 bis 39 werden in der Reihenfolge ihrer Bezugszeichen von den Auswahlsignalen SEL0 bis SEL3 angesteuert, so daß Ansteuerung des 16-bit-Registers 39 durch das vierte Auswahlsignal SEL3 vier eingangsseitige 4-bit-Datenworte in ein ausgangsseitiges 16-bit-Datenwort umgewandelt sind.

Nachfolgend wird unter Bezugnahme auf die Fig. 5 bis 8 die Struktur und Funktion der Anzeigezählervorrichtung 8 näher erläutert. Fig. 5 zeigt die zeitliche Relation des ersten Horizontalsynchronisationssignales HS(1), des ersten Blanksignales BL(1) und des ersten Taktsignales CLK(1).

Wie in Fig. 6 gezeigt ist, umfaßt die Anzeigezählervorrichtung 8 einen Horizontalzähler 40, dessen Takteingang das erste Taktsignal CLK(1) und dessen Rücksetzeingang das erste Horizontalsynchronisationssignal HS(1) zugeführt werden. Das erste Blanksignal BL(1) steuert die Übernahme des Zählerstandes des Horizontalzählers 40 in das Register 41 für den Horizontalzählwert HC, der ausgangsseitig am Bus 25 erscheint.

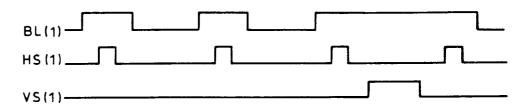

Fig. 7 zeigt (selbstverständlich mit einer ge-

50

15

25

10

genüber Fig. 1 gestrafften Zeitbasis) den schematisierten zeitlichen Zusammenhang zwischen dem ersten Blanksignal BL(1), dem ersten Horizontalsynchronisationssignal HS(1) und dem ersten Vertikalsynchronisationssignal VS(1).

Fig. 8 zeigt den die Vertikalzählung oder Zeilenzählung betreffenden Anteil der Anzeigezählervorrichtung 8, welcher einen Vertikalzähler 42 umfaßt, dessen Takteingang das erste Blanksignal BL-(1) und dessen Rücksetzeingang das erste Vertikalsynchronisationssignal VS(1) zugeführt werden, und der ausgangsseitig mit einem Register 43 für den Vertikal-Zählwert VC verbunden ist, dessen Takteingang wiederum durch das erste Vertikalsynchronisationssignal angesteuert, und das ausgangsseitig mit dem vierten Datenbus 26 in Verbindung steht, auf dem der Vertikalzählwert VC ansteht.

Fig. 9 zeigt die Struktur der Videospeichervorrichtung 4, die in dem gezeigten Beispielsfall in vier Speicherebenen 44 bis 47 unterteilt ist. Diese Unterteilung der Videospeichervorrichtung ermöglicht eine Reduktion der Datenflußrate bei der Einspeicherung und eine vereinfachte Adressierung. Bei dem gezeigten Beispielsfall ist jede der Speicherebenen 44 bis 47 mit 512 x 512 Speicherplätzen versehen, wobei jede der Speicherebenen 44 bis 47 bei der Horizontaladresse 256 gezweiteilt ist. Es ergibt sich eine Speicherorganisation von 1024 x 1024 Plätzen. Beim Ablegen der Datenworte in der Videospeichervorrichtung werden die Daten jeweils gleichzeitig den Eingängen D0 bis D3 zugeführt, wobei in der beschriebenen "page-mode"-Speicherweise zunächst die erste Zeile des Bildes in den jeweiligen ersten Speicherzeilen zwischen den Horizontaladressen 0 und einer Maximaladresse abgelegt werden, die dem Horizontalzählwert HC geteilt durch die Anzahl 4 der Speicherebenen entspricht. Nach Erreichen dieser Horizontaladresse vollführt der (noch zu beschreibende) Horizontaladreßzähler einen Sprung zu der Horizontaladresse 256, bei der die Speicherebene unterteilt ist, um fortfahrend von diesem Horizontaladreßwert bis zu einem um den Horizontalzählwert HC geteilt durch die Anzahl der Speicherebenen erhöhten Wert zu zählen, bevor nach erfolgtem Ablegen der zweiten Zeile des ersten Bildsignales die dritte Zeile des ersten Bildsignales sodann in die zweite Zeile der Videospeichervorrichtung 44 bis 47; 4 abgelegt wird. Das Inkrementieren des Reihenadreßzählers erfolgt nach jedem zweiten Erreichen des um die Anzahl der Speicherebenen geteilten Horizontalzählwertes HC.

Ein Blockdiagramm der zweiten Steuervorrichtung ist in Fig. 10 wiedergegeben, und umfaßt einen Spaltenadreßzähler 48, einen Reihenadreßzähler 49 und einen Steuersignalgenerator zum Erzeugen der Steuersignale für die Videospeichereinrichtung 4. Der Spaltenadreßzähler 48 wird an

seinem Takteingang 51 durch das Fifolesesignal RF getaktet und wird durch das erste Vertikalsynchronisationssignal VS(1) an seinem Rücksetzeingang 52 rückgesetzt und ist ferner an den dritten Datenbus 25 zum Empfangen des Horizontalzählwertes HC angeschlossen.

Nach Rücksetzen des Spaltenadreßzählers 48 vollführt dieser die soeben unter Bezugnahme auf Fig. 9 erläuterte Horizontaladreßzählung. Im Beispielsfall ist dies eine von Null bis zu einem Viertel des Horizontalzählwertes HC ansteigende Zählung mit nachfolgendem Sprung auf die Mittenhorizontaladresse 256, um anschließend wiederum die Adresse kontinuierlich zu inkrementieren, bis diese Mittenadresse um ein Viertel des Horizontalzählwertes HC übertroffen ist. Zu diesem Zeitpunkt erscheint eine "1" am Steuerausgang TC des Spaltenadreßzählers 48, welcher mit dem Takteingang 53 des Reihenadreßzählers 49 verbunden ist, der durch diesen Signalpuls inkrementiert wird, bis er durch Auftreten des ersten Vertikalsynchronisationssignales VS(1) rückgesetzt wird.

Dem Steuersignalgenerator 50 werden das Taktsignal CLK\* vom Oszillator 7 an dessen Takteingang 54, das Flag EF von der Fifo-Speichervorrichtung 3 an dessen Flageingang 55 das Steuersignal TC vom Spaltenadreßzähler 48 an dessen Steuersignaleingang 56 sowie das sekundärseitige Horizontalsynchronisationssignal HS(2) an dessen Horizontalsynchronisationseingang 57 zugeführt. Die Erzeugung des Reihenadreßübernahmesignals RAS, des Spaltenadreßübernahmesignal CAS, des Datenübernahmesignales DT/OE für die Übernahme von Daten aus der Videospeichervorrichtung in dessen Ausgangsschieberegister und des Schreibsignales WB/WE für die Videospeichervorrichtung erfolgt gemäß der Spezifikation der jeweils verwendeten Videospeichervorrichtung für deren Betrieb in den "page-mode"-Schreibmodus. Das Auslesesignal RF kann durch UND-Verknüpfen des Spaltenadreßübernahmesignales CAS und des zweiten Horizontalsynchronisationssignales HS(2) mittels eines Gatters 58 erzeugt werden.

Bei dem beschriebenen Ausführungsbeispiel wird eine Registervorrichtung verwendet, um die eingangsseitig anliegenden Datenworte mit der ersten Pixelfrequenz in Datenworte von mehrfacher Bitlänge bei einer durch die Mehrzahl geteilten ersten Pixelfrequenz zu erzeugen, wodurch die Anforderungen an die Einspeicherungsgeschwindigkeit in die Fifo-Speichervorrichtung gesenkt werden können. Die eingangsseitige Registervorrichtung wird jedoch dann entbehrlich, wenn das erste Bildsignal eine entsprechende niedrige Datenwortrate hat oder wenn eine Fifo-Speichervorrichtung mit entsprechend hoher Arbeitsgeschwindigkeit verwendet wird. In diesem Fall ist auch die erste Steuervorrichtung entbehrlich.

50

35

40

45

50

55

Bei der erläuterten Ausführungsform wird die Abspeicherung in die Videospeichervorrichtung jeweils ausgehend von einer Horizontaladresse 0 und einer Vertikaladresse 0, also ausgehend von der linken oberen Ecke der Videospeichervorrichtung vorgenommen.

Der Erfindungsgegenstand ist nicht beschränkt auf eine bestimmte Anzahl von Bits der Datenworte des verarbeiteten Bildsignales und ist ebenso auf Schwarzweiß-Bildsignale wie Farb-Bildsignale anwendbar. Wenn beispielsweise eine Farbvielfalt von 256 Farben gewünscht ist, was Eingangsdatenworten von 8 bit entspricht, so können zwei Schaltungen gemäß Fig. 1 parallel geschaltet werden.

Obwohl die bevorzugte Ausführungsform des Erfindungsgegenstande hardware-mäßig mittels Gate-Arrays implementiert ist, ist es denkbar, Zählervorrichtungen und Steuervorrichtungen sowie eine geeignete Ansteuervorrichtung für die erste Speichervorrichtung, die diese als Fifo-Speichervorrichtung arbeiten läßt, software-mäßig zu realisieren.

Grundsätzlich dient die erfindungsgemäße Monitorsteuerschaltung im wesentlichen zur Ansteuerung eines Monitors, dessen Pixelfrequenz verschieden ist von der des auf diesem darzustellenden digitalen Bildsignales. Jedoch soll der Begriff der "ersten Pixelfrequenz" des Bildsignales und der Begriff der "zweiten Pixelfrequenz" des Monitors so breit verstanden werden, daß hierunter auch frequenzmäßig gleiche oder ähnliche Signale mit unterschiedlicher Phase bzw. Synchronisation fallen.

## Patentansprüche

Verfahren zur Ansteuerung eines bei einer zweiten Pixelfrequenz arbeitenden Monitors, dessen Anzeige durch Auslesen eines digitalen Bildsignales mit der zweiten Pixelfrequenz aus einer Videospeichervorrichtung (4) erzeugbar ist, aufgrund eines eine erste Pixelfrequenz aufweisenden digitalen Bildsignales,

gekennzeichnet durch folgende Verfahrensschritte:

- Einlesen des digitalen Bildsignales mit einer von der ersten Pixelfrequenz abhängigen Frequenz in eine Fifo-Speichervorrichtung (3);

- Auslesen von in die Videospeichervorrichtung (4) einzuspeichernden Datenworten des digitalen Bildsignales aus der Fifo-Speichervorrichtung (3) nur während solcher Zeitabschnitte, während der kein Auslesen von Daten aus der Videospeichervorrichtung (4) stattfindet, wodurch die aus der Fifo-Speichervorrichtung (3)

zur Einspeicherung in die Videospeichervorrichtung (4) auslesbare Datenwortzahl variieren kann.

- 2. Verfahren nach Anspruch 1, gekennzeichnet durch folgenden Verahrensschritt:

- Kombinieren des aus der Videospeichervorrichtung (4) ausgelesenen Bildsignales mit einem weiteren Bildsignal, durch das die zweite Pixelfrequenz festgelegt ist, zur gemeinsamen Anzeige von zwei Bildern, deren ursprüngliche Bildsignale unterschiedliche Pixelfrequenzen haben, auf dem Monitor.

- Verfahren nach Anspruch 2, dadurch gekennzeichnet.

- daß das Bildsignal der ersten Pixelfrequenz und das weitere Bildsignal Bildsignale von unterschiedlichen Graphikstandards sind.

- **4.** Verfahren nach einem der Ansprüche 1 bis 3, dadurch gekennzeichnet,

- daß die aus der Fifo-Speichervorrichtung (3) ausgelesenen Datenworte auf einen Datenbus (20), der für die Datenverbindung mit der Videospeichervorrichtung (4) dient, ausgegeben werden.

- 5. Monitorsteuerschaltung für die Ansteuerung eines bei einer zweiten Pixelfrequenz arbeitenden Monitors, dessen Anzeige durch Auslesen eines digitalen Bildsignales mit der zweiten Pixelfrequenz aus einer Videospeichervorrichtung (4) erzeugbar ist, aufgrund eines eine erste Pixelfrequenz aufweisenden digitalen Bildsignales,

mit einer ersten Speichervorrichtung (3), in die das digitale Bildsignal mittels einer ersten Steuervorrichtung (5) mit einer von der ersten Pixelfrequenz abhängigen Frequenz einlesbar ist.

dadurch gekennzeichnet,

- daß die erste Speichervorrichtung eine Fifo-Speichervorrichtung (3) ist, und

- daß eine zweite Steuervorrichtung (6) zum Steuern des Auslesens von in die Videospeichervorrichtung (4) einzuschreibenden Datenworten des digitalen Bildsignales aus der Fifo-Speichervorrichtung (3) vorgesehen ist, die das Auslesen von Datenworten aus der Fifo-Speichervorrichtung (3) nur während solcher Zeitabschnitte vornimmt, während der kein

10

15

20

25

30

35

40

45

50

55

Auslesen von Daten aus der Videospeichervorrichtung (4) stattfindet, wodurch die aus der Fifo-Speichervorrichtung (3) zur Einspeicherung in die Videospeichervorrichtung (4) auslesbare Datenwortzahl variieren kann.

**6.** Monitorsteuerschaltung nach Anspruch 5, gekennzeichnet durch

eine eingangsseitig mit der Fifo-Speichervorrichtung (3) verbundene Registervorrichtung (2), mittels der die bei der ersten Pixelfrequenz empfangenen Datenworte des digitalen Bildsignales in Datenworte mit einer Mehrzahl-fachen Bitzahl bezogen auf die Bitzahl der empfangenen Datenworte bei einer durch die Mehrzahl geteilten ersten Pixelfrequenz umwandelbar sind.

Monitorsteuerschaltung nach Anspruch 6, dadurch gekennzeichnet,

daß die Registervorrichtung (2) eine gegenüber der Mehrzahl um eins niedrigere Anzahl von ersten Registern (36, 37, 38) zur Aufnahme je eines der empfangenen Datenworte aufweist,

daß die Registervorrichtung (2) ferner ein zweites Register (39) zur Aufnahme des Datenwortes mit der Mehrzahl-fachen Bitzahl aufweist, daß mit einem Teil seiner Eingänge an Ausgänge der ersten Register (36, 37, 38) und mit einem weiteren Teil seiner Eingänge an einen Bus (10) zur Aufnahme eines der empfangenen Datenworte angeschlossen ist, und

daß die erste Steuervorrichtung (5) sequentiell jedes der ersten Register (36, 37, 38) und das zweite Register (39) mit einem Auswahlsignal (SEL0, SEL1, SEL2, SEL3) zur Übernahme eingangsseitig anstehender Datenworte ansteuert.

Monitorsteuerschaltung nach Anspruch 7, dadurch gekennzeichnet,

daß die erste Steuervorrichtung (5) einen Takteingang (16) aufweist, dem ein Taktsignal (CLK(1)) der ersten Pixelfrequenz zuführbar ist, und einen Halteeingang (17) aufweist, dem ein Blanksignal (BL(1)) des ersten Bildsignales zuführbar ist, und

daß die erste Steuervorrichtung (5) eine der Mehrzahl entsprechende Zahl von Auswahlausgängen (12) hat und derart aufgebaut ist, daß die Auswahlsignale (SEL0, SEL1, SEL2, SEL3) an den Auswahlausgängen (12) jeweils um

eine erste Pixelperiode gegeneinander versetzt sind

**9.** Monitorsteuerschaltung nach Anspruch 7 oder 8, dadurch gekennzeichnet,

daß die erste Steuervorrichtung (5) ferner einen Schreibbefehlausgang zum Erzeugen eines Schreibbefehles (WF) für die Fifo-Speichervorrichtung (3) aufweist, wobei der Schreibbefehl (WF) gegenüber dem Auswahlsignal (SEL3) für das zweite Register (39) um wenigstens eine erste Pixelperiode versetzt ist, und daß die Fifo-Speichervorrichtung (3) einen Schreibbefehleingang (15) hat und bei Anliegen eines Schreibbefehles ein anstehendes Datenwort aufnimmt.

**10.** Monitorsteuerschaltung nach einem der Ansprüche 5 bis 9, gekennzeichnet durch

eine Anzeigezählervorrichtung (8), der das erste Taktsignal (CLK(1)) der ersten Pixelfrequenz und das erste Blanksignal (BL(1)) des ersten Bildsignales zuführbar sind, wobei die Anzeigezählervorrichtung (8) einen Horizontalzähler (40, 41) zum Zählen der ersten Taktsignale (CLK(1)) zwischen zwei ersten Blanksignalen (BL(1)) aufweist.

**11.** Monitorsteuerschaltung nach Anspruch 10, dadurch gekennzeichnet,

daß die Anzeigezählervorrichtung (8) ferner einen Vertikalzähler (42, 43) aufweist, dem die ersten Blanksignale (BL(1)) und die ersten Vertikalsynchronisationssignale (VS(1)) zuführbar sind und mittels dessen die Anzahl von ersten Blanksignalen (BL(1)) zwischen zwei ersten Vertikalsynchronisationssignalen (VS(1)) ermittelbar ist.

**12.** Monitorsteuerschaltung nach einem der Ansprüche 5 bis 11, dadurch gekennzeichnet,

daß die Fifo-Speichervorrichtung (3) einen Rücksetzeingang (14) aufweist, dem das erste Vertikalsynchronisationssignal (VS(1)) zuführbar ist.

**13.** Monitorsteuerschaltung nach Anspruch 12, dadurch gekennzeichnet,

daß die Fifo-Speichervorrichtung (3) einen Flag-Ausgang für ein einen leeren Zustand der Speicherbereiche der Fifo-Speichervorrichtung (3) anzeigendes Flag (EF) aufweist, und

10

15

20

25

30

35

40

daß der Flag-Ausgang mit einem Flag-Eingang der zweiten Steuervorrichtung (6) verbunden ist.

**14.** Monitorsteuerschaltung nach einem der Ansprüche 11 bis 13, dadurch gekennzeichnet,

daß die zweite Steuervorrichtung (6) einen Lesebefehlsausgang (RF) aufweist, der mit einem Lesesteuereingang der Fifo-Speichervorrichtung verbunden ist, und

daß die Fifo-Speichervorrichtung (3) derart ausgebildet ist, daß sie bei jedem Lesebefehlspuls (RF) an ihrem Lesesteuereingang ein Datenwort, das zur Einspeicherung in die Videospeichervorrichtung (4) bestimmt ist, abgibt.

**15.** Monitorsteuerschaltung nach einem der Ansprüche 5 bis 14, dadurch gekennzeichnet,

daß die zweite Steuervorrichtung (6) einen Rücksetzeingang aufweist, dem das Vertikalsynchronisationssignal (VS(1)) des ersten Bildsignales zuführbar ist, und

daß die zweite Steuervorrichtung (6) ferner einen Takteingang aufweist, an den ein Oszillator (7) angeschlossen ist.

**16.** Monitorsteuerschaltung nach einem der Ansprüche 10 bis 15, dadurch gekennzeichnet,

daß die zweite Steuervorrichtung (6) mit der Anzeigezählervorrichtung (8) verbunden ist und von dieser zumindest den Zählwert (HC) des Horizontalzählers (40, 41) empfängt.

Monitorsteuerschaltung nach Anspruch 15 oder

in Rückbeziehung auf Anspruch 14, dadurch gekennzeichnet,

daß die zweite Steuervorrichtung (6) zur Ansteuerung der Videospeichervorrichtung (4) auf der Zeitbasis des durch den Oszillator (7) vorgebenen Taktes ausgehend von einem logischen Anfangszustand bei Auftreten des ersten Vertikalsynchronisationssignales (VS(1)) pro Auslesetakt jeweils einen Lesebefehlspuls (RF) für die Fifo-Speichervorrichtung (3), ein Horizontaladreßsignal (ADR) und ein Vertikaladreßsignal (ADR) für die Adressierung der Videospeichervorrichtung (4) und Videospeichersteuersignale (RAS, CAS, WB/WE, DT/OE) erzeugt.

**18.** Monitorsteuerschaltung nach Anspruch 17, dadurch gekennzeichnet,

daß die Videospeichersteuersignale ein Spaltenadressenübernahmesignal (CAS), ein Zeilenadressenübernahmesignal (RAS), ein den Schreibzustand für das Einschreiben in die Videospeichervorrichtung (4) darstellendes Schreibsignal (WB/WE) und ein Schieberegisterübernahmesignal (DT/OE), das die Übernahme eines Datenwortes aus der Videospeichervorrichtung (4) in ein Ausgangsschieberegister derselben ermöglicht, umfassen.

**19.** Monitorsteuerschaltung nach Anspruch 18, dadurch gekennzeichnet,

daß die zweite Steuervorrichtung (6) die genannten Steuersignale für die Videospeichervorrichtung (4) in einer solchen, von der Spezifikation der verwendeten Videospeichervorrichtung (4) abhängigen Art erzeugt, daß das Einschreiben der von der Fifo-Speichervorrichtung (3) gelieferten Datenworte auf einen Datenbus (20) zum Ausschluß der Videospeichervorrichtung (4) in der sogenannten "page-mode"-Speicheransteuerungsart erfolgt, bei der das Zeilenadreßsignal (ADR) und das Zeilenadreß-übernahmesignal (RAS) für die Videospeichervorrichtung (4) während der Einspeicherung von Daten in eine Zeile der Videospeichervorrichtung (4) unverändert bleiben.

55

FIG.3

FIG.6

HS (1)0-

FIG.7