(11) Numéro de publication : 0 506 530 A1

12

## **DEMANDE DE BREVET EUROPEEN**

(21) Numéro de dépôt : 92400755.2

61 Int. Cl.<sup>5</sup>: **G09G 3/36**

(22) Date de dépôt : 20.03.92

(30) Priorité: 29.03.91 FR 9103855

(43) Date de publication de la demande : 30.09.92 Bulletin 92/40

84) Etats contractants désignés : **DE GB NL**

71 Demandeur : THOMSON-LCD 51, Esplanade du Géneral de Gaulle F-92800 Puteaux (FR) (72) Inventeur: Hepp, Bernard THOMSON-CSF, SCPI, Cédex 67 F-92045 Paris la Défense (FR) Inventeur: Maier, Michael THOMSON-CSF, SCPI, Cédex 67 F-92045 Paris la Défense (FR)

(4) Mandataire: Grynwald, Albert et al THOMSON-CSF SCPI F-92045 PARIS LA DEFENSE CEDEX 67 (FR)

- (54) Ecran matriciel à définition améliorée et procédé d'adressage d'un tel écran.

- 57) La présente invention concerne un écran matriciel à définition améliorée, associé à au moins un circuit de commande.

Cet écran comporte à chaque intersection des lignes  $(L_1, L_2, L_3)$  et des colonnes  $(C_1, C_2, C_3)$  de la matrice de conducteurs, deux transistors  $(T_1, T_2)$  de commutation de telle sorte que chaque couple ligne-colonne commande deux cellules électro-optiques diagonalement opposées. D'autre part les colonnes paires sont reliées à un premier circuit de commande alimenté par une première tension et les colonnes impaires à un second circuit de commande alimenté par une tension inverse.

Application aux écrans à cristaux liquides.

5

10

20

25

30

35

40

45

50

La présente invention concerne un écran matriciel à définition améliorée, plus particulièrement un écran matriciel du type à commande active dans lequel chaque point-image est défini, à l'intersection de deux réseaux de conducteurs orthogonaux appelés lignes et colonnes, par un élément électro-optique connecté aux réseaux de conducteurs par un élément de commutation. Elle concerne plus particulièrement les écrans dans lesquels l'élément optique est un cristal liquide qui est connecté aux réseaux de conducteurs par l'intermédiaire d'un transistor de commutation.

Les écrans matriciels à cristaux liquides de ce type doivent, pour fonctionner correctement, être rafraîchis le plus fréquemment possible (au moins toutes les 20 ms) et la polarité de chacune des différentes cellules électro-optiques de la matrice doit aussi être alternée fréquemment, en général à chaque trame.

Différentes techniques d'adressage peuvent être utilisées dans ce cas.

Ainsi une technique connue consiste à adresser les lignes successivement les unes après les autres en alternant la polarité du ou des circuits de commande toutes les trames. Chaque ligne est donc rafraîchie en fonction de la durée trame en général toutes les 20 ms. Toutefois, ce procédé complique l'adressage des lignes et ne peut être mis en oeuvre qu'avec des écrans dans lesquels on utilise une mémoire d'image afin de pouvoir adresser progressivement toutes les lignes de l'écran. Une autre technique connue consiste à adresser les lignes deux à deux avec décalage d'une trame à l'autre. Par exemple, on adresse tout d'abord les lignes 1 et 2, 3 et 4, ... pendant une trame paire, puis les lignes 2 et 3, 4 et 5, ... pendant une trame impaire. Cet adressage est réalisé en alternant la polarité des circuits de commande toutes les deux trames. Ainsi chaque ligne est rafraîchie à chaque trame, à savoir toutes les 20 ms, mais ce procédé complique lui aussi l'adressage des lignes.

De plus, dans les cas décrits ci-dessus on obtient en sortie des circuits de commande une tension égale à deux fois la tension nécessaire pour commuter le cristal liquide, soit en général une excursion de 10 à 14 volts.

La présente invention a donc pour but de remédier à ces inconvénients en proposant une nouvelle structure d'écran matriciel à définition améliorée qui permet d'éviter l'utilisation d'une mémoire de trame et de limiter l'excursion de tension en sortie à une valeur plus faible à savoir, en général 5 volts. La présente invention a aussi pour but de proposer un procédé d'adressage de cet écran matriciel qui soit de mise en oeuvre simple.

En conséquence, la présente invention a pour objet un écran matriciel à définition améliorée associé à au moins un circuit de commande, caractérisé en ce qu'il comporte, à chaque intersection des lignes et des colonnes de la matrice de conducteurs, deux tran-

sistors de commutation de telle sorte que chaque couple ligne-colonne commande deux cellules électro-optiques diagonalement opposées et en ce que les colonnes paires  $(C_{2m})$  sont reliées à un premier circuit de commande alimenté par une première tension  $(V^+)$  et les colonnes impaires  $(C_{2m+1})$  à un second circuit de commande alimenté par une tension inverse  $(V^-)$ .

La présente invention a aussi pour objet un procédé d'adressage d'un écran matriciel tel que défini ci-dessus caractérisé en ce que les lignes impaires  $(L_{2n+1})$  sont adressées pendant une trame et les lignes paires  $(L_{2n})$  pendant la trame suivante.

D'autres caractéristiques et avantages de la présente invention apparaîtront à la lecture de la description d'un mode de réalisation pris à titre d'exemple non limitatif, cette description étant faite avec référence au dessin ci-annexé dans lequel :

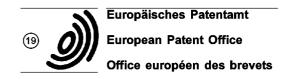

la figure 1 est une vue simplifiée et partielle d'un écran matriciel conforme à la présente invention et

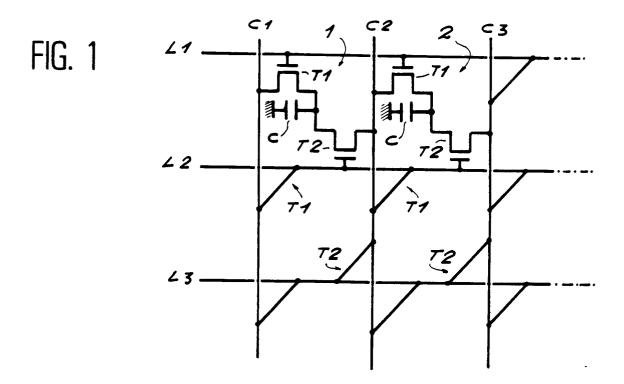

les figures 2a et 2b sont des vues schématiques simplifiées d'un écran matriciel illustrant le procédé d'adressage de la présente invention.

L'invention sera expliquée ci-après en se référant à un écran matriciel à cellules de cristaux liquides, mais il est évident pour l'homme de l'art qu'elle peut être mise en oeuvre pour réaliser des écrans matriciels à cellules faisant appel à des technologies autres que des cristaux liquides. D'autre part la présente invention s'applique plus particulièrement à un écran matriciel à commande active dans lequel l'élément de commutation est constitué par au moins un transistor réalisé, de préférence, en utilisant la technologie couche mince.

Comme représenté sur la figure 1, l'écran utilisé dans la présente invention comporte une matrice de conducteurs-ligne  $L_1,\,L_2,\,L_3,\,\dots$  et de conducteurs-colonne  $C_1,\,C_2,\,C_3,\,\dots$

Chacune des "cases" telles que 1 et 2 délimitées jar deux conducteurs-ligne et deux conducteurs-colonne voisins comportent une cellule de cristal liquide. Cette cellule de cristal liquide est symbolisée de manière connue par un condensateur C sur la figure 1. Comme représenté, le condensateur C est relié respectivement par l'intermédiaire d'un élément de commutation tel qu'un transistor T1 à un premier ensemble ligne-colonne et par l'intermédiaire d'un autre élément de commutation tel que le transistor T2 à un second ensemble de ligne-colonne. De manière plus spécifique, le condensateur C de la case "1" est relié par le transistor T1 au couple ligne-colonne L<sub>1</sub>, C<sub>1</sub> et par le transistor T2 au couple ligne-colonne L2, C2. De même, le condensateur C de la case "2" est relié par le transistor T1 au couple ligne-colonne L<sub>1</sub>, C<sub>2</sub> et par le transistor T2 au couple ligne-colonne L2, C3. Dans les autres cases de la matrice de conducteur représentée à la figure 1, les transistors T1 et T2 sont simplement symbolisés par des traits joignant, près de

5

10

20

25

30

35

45

50

chaque croisement considéré, une ligne et une colonne. De ce fait on s'aperçoit que, dans le mode de réalisation conforme à la présente invention, deux cellules électro-optiques diagonalement opposées sont commandées par un même couple ligne-colonne.

On expliquera maintenant, en se référant plus particulièrement aux figures 2A et 2B, le procédé d'adressage d'un écran matriciel tel que décrit ci-dessus. Comme représenté sur les figures 2, qui concernent un écran matriciel à quatre lignes et à quatre colonnes donné à titre d'exemple, les lignes impaires L<sub>1</sub>, L<sub>3</sub> sont connectées à un circuit d'adressage impair 10 tandis que les lignes paires L2, L4 sont connectées à un circuit d'adressage pair 11. D'autre part, l'écran matriciel représenté dans le cadre de la présente invention comporte deux circuits de commande à savoir les circuits 12, 13. Le circuit de commande 12 est connecté aux colonnes impaires C1, C3 et est alimenté par une tension positive V+ tandis que le circuit de commande 13 est connecté aux colonnes paires C2, C<sub>4</sub> et est alimenté par une tension inverse à savoir une tension négative V<sup>-</sup>. Il est évident pour l'homme de l'art que les tensions des circuits de commande 12 et 13 peuvent être inversées de même que le type de colonnes connectées à l'un ou l'autre desdits circuits représentés sur la figure 2A. Avec ce type de matrice, les échantillons successifs d'une ligne de signal vidéo sont envoyés aux conducteurs de colonnes C<sub>1</sub>, C<sub>2</sub>, ... respectivement par l'intermédiaire des circuits de commande 12 et 13 tandis que l'adressage des lignes est effectué de la manière suivante :

- pour une première trame, par exemple une trame impaire, on adresse successivement les lignes impaires de la matrice de conducteurs en synchronisme avec les lignes impaires du signal vidéo.

De ce fait, comme représenté sur la figure 2A, l'impulsion appliquée par le circuit 10 sur la ligne  $L_1$  ouvre respectivement tous les transistors T1 connectés à cette ligne et les cellules X1.1, X1.2, X1.3 reçoivent respectivement une tension positive, négative, positive en fonction du circuit de commande 12 ou 13 auxquelles elles sont rattachées. Ensuite, l'impulsion appliquée sur la ligne  $L_3$  ouvre les transistors T2 commandant les cellules X2.1, X2.2, X2.3 de telle sorte qu'elles reçoivent respectivement une tension négative, positive, négative. L'impulsion appliquée sur la ligne  $L_3$  ouvre aussi les transistors T1 des cellules X3.1, X3.2, X3.3 de telle sorte qu'une tension respectivement positive, négative, positive est appliquée sur ces cellules, comme représenté sur la figure 2A.

A la trame suivante, à savoir lors d'une trame paire, on adresse les lignes paires en gardant le même procédé d'adressage. Les résultats obtenus dans ce cas sont représentés sur la figure 2B. Ainsi, lorsqu'une impulsion est appliquée sur la ligne L<sub>2</sub>, celle-ci ouvre les transistors T2 correspondant aux cellules X1.1, X1.2, X1.3 sur lesquelles sont appliquées res-

pectivement une tension négative, positive, négative. De même l'impulsion appliquée sur la ligne L2 ouvre les transistors T1 des cellules X2.1, X2.2, X2.3 sur lesquelles sont appliquées des tensions respectivement positive, négative, positive. L'impulsion appliquée alors sur la ligne L<sub>4</sub> ouvre les transistors T2 des cellules X3.1, X3.2, X3.3 sur lesquelles sont appliquées respectivement des tensions négative, positive, négative comme représenté sur la figure 2B. Si l'on compare les tensions appliquées sur chaque cellule à chaque trame, respectivement paire et impaire, on s'aperçoit qu'il y a inversion de la tension à chaque trame. On obtient donc l'inversion de polarité au niveau de chaque cellule nécessaire à son bon fonctionnement. D'autre part, la tension appliquée sur les deux circuits de commande 12 et 13 n'a plus besoin d'être inversée à chaque trame. Il en résulte que l'excursion de tension en sortie est stable et est en général égal à 5V. Par exemple entre 0 et 5V pour le circuit 12 et entre -5V et 0 pour le circuit 13.

Pour simplifier la description, on s'est référé à un écran matriciel comportant quatre lignes et quatre colonnes. Toutefois, il est évident pour l'homme de l'art que le même adressage peut être utilisé quelque soit le nombre de lignes et de colonnes. De manière plus générale, lors de trames impaires, on réalise un adressage des lignes impaires  $L_{2n+1}$ . De ce fait, la ligne  $L_{2n+1}$  et la colonne  $C_m$  permettent d'adresser à la fois le pixel  $X_{2n+1,m}$  et le pixel  $X_{2n,m-1}$  diagonalement appairé. A titre d'exemple d'exemple, l'adressage de la ligne  $L_3$  et de la colonne  $C_2$  active les pixels  $X_2$ .1 et  $X_3$ .2.

Dans le cas d'une trame paire, on adresse les lignes paires  $\mathsf{L}_{2n}$ . La ligne  $\mathsf{L}_{2n}$  et la colonne  $\mathsf{C}_m$  permettent donc d'adresser à la fois les pixels  $\mathsf{X}_{2n,m}$  et  $\mathsf{X}_{2n-1,\ m-1}$ . Ainsi, l'adressage de la ligne  $\mathsf{L}_2$  et de la colonne  $\mathsf{C}_3$  permet d'activer les pixels X1.2 et X2.3 comme décrits précédemment.

On obtient donc un écran matriciel de réalisation simple, puisque la fabrication du deuxième transistor de chaque cellule se fait en même temps que celle du premier transistor, et dont l'adressage est simplifié par rapport à l'état de l'art actuel, puisque d'une part on s'affranchit d'une mémoire de trame lorsque l'écran est un écran de pleine définition TV affichant un signal entrelacé, d'autre part l'excursion de tension en sortie des circuits d'adressage est divisée par 2,

## Revendications

Ecran matriciel à définition améliorée associé à au moins un circuit de commande, caractérisé en ce qu'il comporte à chaque intersection des lignes et des colonnes de la matrice de conducteurs, deux transistors (T<sub>1</sub>, T<sub>2</sub>) de commutation de telle sorte que chaque couple ligne-colonne

55

commande deux cellules électro-optiques diagonalement opposées et en ce que les colonnes paires  $(C_{2m})$  sont reliées à un premier circuit de commande alimenté par une première tension  $(V^+)$  et les colonnes impaires  $(C_{2m+1})$  à un second circuit de commande alimenté par une tension inverse  $(V^-)$ .

2. Ecran matriciel selon la revendication 1, caractérisé en ce que les cellules électro-optiques sont des cellules à cristal liquide.

3. Ecran matriciel selon l'une quelconque des revendications 1 et 2, caractérisé en ce que les transistors de commutation sont des transistors en couche mince (TFT).

**4.** Procédé d'adressage d'un écran matriciel selon l'une quelconque des revendications 1 à 3, caractérisé en ce que les lignes impaires  $(L_{2n+1})$  sont adressées pendant une trame et les lignes paires  $(L_{2n})$  pendant la trame suivante.

5. Procédé selon la revendication 4, caractérisé en ce que la tension alimentant les premier et second circuits de commande est constante d'une trame à la suivante.

## RAPPORT DE RECHERCHE EUROPEENNE Numero de la demande

EP 92 40 0755

| atégorie                     | Citation du document avec in                                                                                                                                            | dication, en cas de hesoin.       | Revendication                                                                                                | CLASSEMENT DE LA                              |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| ategorie                     | des parties perti                                                                                                                                                       |                                   | concernée                                                                                                    | DEMANDE (Int. Cl.5)                           |

| Y                            | FR-A-2 571 913 (RICHARD * revendication 1; figur                                                                                                                        |                                   | 1-5                                                                                                          | G09G3/36                                      |

| Y                            | EP-A-0 241 562 (SANYO EL<br>* page 7, ligne 8 - page<br>revendication 1 *                                                                                               |                                   | 1-5                                                                                                          |                                               |

| Y                            | EP-A-0 373 897 (SHARP K. * revendication 1 *                                                                                                                            | K.)                               | 4,5                                                                                                          |                                               |

| A                            | EP-A-0 402 850 (TOSHIBA * revendications 1,4,5,1                                                                                                                        |                                   | 1-3                                                                                                          |                                               |

| A                            | EP-A-0 274 942 (THOMSON-0<br>* colonne 3, ligne 41 - or<br>revendication 1 *                                                                                            |                                   | 1                                                                                                            |                                               |

|                              |                                                                                                                                                                         |                                   |                                                                                                              |                                               |

|                              |                                                                                                                                                                         |                                   |                                                                                                              | DOMAINES TECHNIQUES<br>RECHERCHES (Int. Cl.5) |

|                              |                                                                                                                                                                         |                                   |                                                                                                              | G09G                                          |

|                              |                                                                                                                                                                         |                                   |                                                                                                              |                                               |

|                              |                                                                                                                                                                         |                                   |                                                                                                              |                                               |

|                              |                                                                                                                                                                         |                                   |                                                                                                              |                                               |

|                              |                                                                                                                                                                         |                                   |                                                                                                              |                                               |

|                              |                                                                                                                                                                         |                                   |                                                                                                              |                                               |

|                              |                                                                                                                                                                         |                                   |                                                                                                              |                                               |

|                              |                                                                                                                                                                         |                                   |                                                                                                              |                                               |

| Le pro                       | ésent rapport a été établi pour toute                                                                                                                                   | es les revendications             |                                                                                                              |                                               |

| Lieu de la recherche Date d  |                                                                                                                                                                         | Date d'achèvement de la recherche |                                                                                                              | Examinateur                                   |

|                              | LA HAYE                                                                                                                                                                 | 14 JUILLET 1992                   | ZENDE                                                                                                        | ER J.J.                                       |

| X : part<br>Y : part<br>autr | CATEGORIE DES DOCUMENTS CI<br>iculièrement pertinent à lui seul<br>iculièrement pertinent en combinaison a<br>e document de la même catégorie<br>ère-plan technologique | E : document de date de dép       | rincipe à la base de l'in<br>e brevet antérieur, mais<br>st ou après cette date<br>demande<br>autres raisons |                                               |

EPO FORM 1503 03.82 (P0402)