11) Publication number:

0 507 061 A2

# EUROPEAN PATENT APPLICATION

(21) Application number: 92102353.7 (51) Int. Cl.<sup>5</sup>: **G09G** 3/36

2 Date of filing: 12.02.92

(12)

③ Priority: 01.04.91 US 678736

43 Date of publication of application: 07.10.92 Bulletin 92/41

Designated Contracting States:

AT BE CH DE DK ES FR GB GR IT LI LU MC

NL PT SE

Applicant: IN FOCUS SYSTEMS, INC. 7770 S.W. Mohawk Street Tualatin Oregon 97062(US)

Inventor: Scheffer, Terry James 1155 S.W. Huntington Avenue Portland, Oregon 97005(US) Inventor: Clifton, Benjamin Robert 12775 S.W. 6th Street Beaverton, Oregon 97005(US)

Representative: Meddle, Alan Leonard et al FORRESTER & BOEHMERT Franz-Joseph-Strasse 38 W-8000 München 40(DE)

54) LCD addressing system.

Department A method and apparatus for addressing faster responding liquid crystal panels (LCDs) so that video rate, high information content LCDs having time constants on the order of 50ms or less, are perceived as having brighter bright states and darker dark states by limiting peak voltage levels across the pixels. A first set of LCD electrodes are continuously driven with signals each comprising a train of pulses that: are periodic in time; have a common period T; are independent of the information to be displayed; and are preferably orthonormal. A plurality of column signals are generated from the collective information state of the pixels defined by the overlap with a second electrode pattern. Each column signal is proportional to the sum obtained by considering each pixel in the column and adding the voltage of that pixel's row at time t to the sum if the pixel is to be "off" and subtracting the voltage of that pixel's row at time t from the sum if the pixel is to be "on". If the row signals only switch between two voltage levels, the sum may be represented as the sum of the exclusive-or (XOR) products of the logic level of the amplitude of each row signal times the logic level of the information state of the pixel corresponding to that row.

Hardware implementation comprises an external video source, a controller that receives and formats video data and timing information, a storage means for storing display data, a row signal generator, a column signal generator, and at least one LCD panel. Alternative embodiments provide gray scale shading and circuits to reduce the magnitude of the column signals, as well as the number of column voltage levels required to generate a displayed image.

Fig. 12

## BACKGROUND OF THE INVENTION

### Field of the Invention

The present invention pertains to a method and apparatus for addressing liquid crystal devices. More particularly the present invention pertains to a method and apparatus for addressing high information content, direct multiplexed, rms responding liquid crystal displays.

# Discussion of the Prior Art

10

Examples of high information content direct multiplexed, rms-responding liquid crystal displays are systems that incorporate twisted nematic (TN), supertwisted nematic (STN), or superhomeotropic (SH) liquid crystal display (LCD) panels. In such panels, a nematic liquid crystal material is disposed between parallel-spaced, opposing glass plates or substrates. In one common embodiment, a matrix of transparent electrodes are applied to the inner surface of each plate, typically arranged in horizontal rows on one plate and vertical columns on the other plate to provide a picture element or "pixel" wherever a row electrode overlaps a column electrode.

High information content displays, such as those used in computer monitors, require large numbers of pixels to portray arbitrary information patterns in the form of text or graphic images. Matrix LCDs having 480 rows and 640 columns forming 307,200 pixels are commonplace although it is expected that matrix LCDs may soon comprise several million pixels.

The optical state of a pixel, e.g. whether it will appear dark, bright or an intermediate shade, is determined by the orientation of the liquid crystal director within that pixel. In so-called rms responding displays, the direction of orientation can be changed by the application of an electric field across the pixel which induces a dielectric torque on the director that is proportional to the square of the applied electric field. The applied electric field can be either a dc field or an ac field, and because of the square dependence the sign of the torque does not change when the electric field changes sign. In the direct multiplexed addressing techniques typically used with matrix LCDs, the pixel sees an ac field which is proportional to the difference in voltages applied to the electrodes on the opposite sides of the pixel. Signals of appropriate frequency, phase and amplitude, determined by the information to be displayed, are applied to the row and column electrodes creating an ac electric field across each pixel which places it in an optical state representative of the information to be displayed.

Liquid crystal panels have an inherent time constant  $\tau$  which characterizes the time required for the liquid crystal director to return to its equilibrium state after it has been displaced away from it by an external torque. The time constant  $\tau$  is defined by  $\tau = \eta d^2/K$ , where  $\eta$  is an average viscosity of the liquid crystal, d is the cell gap spacing or pitch length and K is an average elastic constant of the liquid crystal. For a conventional liquid crystal material in a 7-10  $\mu$ m cell gap, typical for displays, the time constant  $\tau$  is on the order of 200-400 ms.

If the time constant  $\tau$  is long compared to the longest period of the ac voltage applied across the pixel, then the liquid crystal director is unable to respond to the instantaneous dielectric torques applied to it, and can only respond to a time-averaged torque. Since the instantaneous torque is proportional to the square of the electric field, the time-averaged torque is proportional to the time average of the electric field squared. Under these conditions the optical state of the pixel is determined by the root-mean-square or rms value of the applied voltage. This is the case in typical multiplexed displays where the liquid crystal panel time constant  $\tau$  is 200-400 ms and the information is refreshed at a 60 Hz rate, corresponding to a frame period of 1/60 s or 16.7 ms.

One of the main disadvantages of conventional direct multiplex addressing schemes for high information content LCDs arises when the liquid crystal panel has a time constant approaching that of the frame period. (The frame period is approximately 16.7 ms). Recent technological improvements have decreased liquid crystal panel time constants ( $\tau$ ) from approximately 200-400 ms to below 50 ms by making the gap (d) between the substrates thinner and by the synthesis of liquid crystal material which has lower viscosities ( $\eta$ ) and higher elastic constants (K). If it is attempted to use conventional addressing methods for high information content displays with these faster-responding liquid crystal panels, display brightness and contrast ratio are degraded and in the case of SH displays, alignment instabilities are also introduced.

The decrease in display brightness and contrast ratio occurs in these faster panels because with conventional multiplexing schemes for high information content LCDs, each pixel is subjected to a short duration "selection" pulse once per frame period whose peak amplitude is typically 7-13 times higher than the rms voltage averaged over the frame period. Because of the shorter time constant  $\tau$ , the liquid crystal

director instantaneously responds to this high-amplitude selection pulse resulting in a transient change in the pixel brightness, before returning to a quiescent state corresponding to the much lower rms voltage over the remainder of the frame period. Because the human eye tends to average out the brightness transients to a perceived level, the bright state appears darker and the dark state appears brighter. The degradation is referred to as "frame response". As the difference between a bright state and a dark state is reduced, the contrast ratio, the ratio of the transmitted luminance of a bright state to the transmitted luminance of a dark state, is also reduced.

Several approaches have been attempted to reduce frame response. Decreasing the frame period is one approach, but this approach is restricted by the upper frequency limit of the driver circuitry and the filtering effects on the drive waveforms caused by the electrode sheet resistance and the liquid crystal capacitance. Another approach is to decrease the relative amplitude of the selection pulse, i.e., decreasing the bias ratio, but this ultimately reduces the contrast ratio.

Other matrix addressing techniques are known which do not employ high-amplitude row selection pulses and therefore would not be expected to induce frame response in faster-responding panels. However, these techniques are only applicable to low information content LCDs where either there are just a few matrix rows or where the possible information patterns are somehow restricted, such as in allowing only one "off" pixel per column.

One advantage of the faster responding liquid crystal panels is that it makes video rate, high information content LCDs feasible for flat, "hang on the wall" TV screens. However, this advantage cannot be fully exploited with conventional direct multiplexing addressing schemes because of the degradation of brightness and contrast ratio and the introduction of alignment instabilities in these panels caused by frame response.

## SUMMARY OF THE INVENTION

25

30

50

In accordance with the present invention, a novel addressing method and several preferred embodiments of an apparatus for addressing faster-responding, high-information content LCD panels are provided. The present addressing method and preferred embodiments provide a bright, high contrast, high information content, video rate display that is also free of alignment instabilities.

In the method of the present invention, the row electrodes of the matrix are continuously driven with row signals each comprising a train of pulses. The row signals are periodic in time and have a common period T which corresponds to the frame period. The row signals are independent of the information or data to be displayed and are preferably orthogonal and normalized, i.e., orthonormal. The term normalized denotes that all the row signals have the same rms amplitude integrated over the frame period while the term orthogonal denotes that if the amplitude of a signal applied to one row electrode is multiplied by the amplitude of a signal applied to another row electrode, then the integral of this product over the frame period is zero.

During each frame period T, a plurality of column signals are generated from the collective information state of the pixels in the columns. The column voltage at any time t during frame period T is proportional to the sum obtained by considering each pixel in the column and adding the voltage of that pixel's row at time t to the sum if the pixel is to be "off" and subtracting the voltage of that pixel's row at time t from the sum if the pixel is to be "on". If the orthonormal row functions only switch between two voltage levels, the above sum may be represented as the sum of the exclusive-or (XOR) products of the logic level of each row signal at time t times the logic level of the information state of the pixel corresponding to that row.

When LCDs are addressed in the method of the present invention, frame response is drastically reduced because the ratio of the peak amplitude to the rms amplitude seen by each pixel is in the range of 2-5 which is much lower than with conventional multiplexing addressing schemes for high information content LCDs. For LCD panels that have time constants on the order of 50 ms, the pixels are perceived as having brighter bright states and darker dark states, and hence a higher contrast ratio. Alignment instabilities that are introduced by high peak amplitude signals are also eliminated.

Hardware implementation of the addressing method of the present invention comprises an external video source, a controller that receives and formats video data and timing information, a storage means for storing the display data, a row signal generator, a column signal generator, and at least one LCD panel.

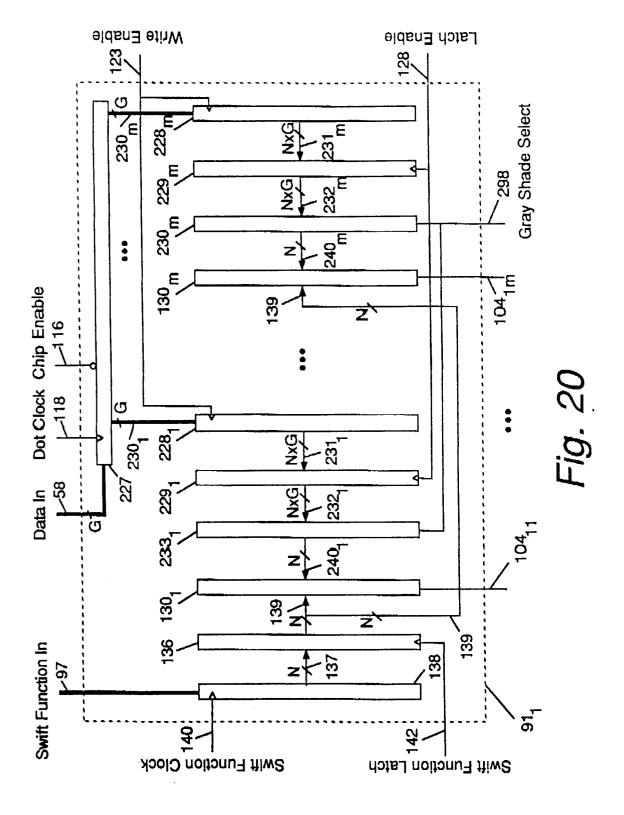

The addressing method of the present invention may be extended to provide gray scale shading, where the information state of each pixel is no longer simply "on" or "off" but a multi-bit representation corresponding to the shade of the pixel. In this method each bit is used to generate a separate column signal, and the final optical state of the pixel is determined from a weighted average of the effect of each bit of the pixel's information state.

## BRIEF DESCRIPTION OF THE DRAWINGS

5

15

25

30

45

55

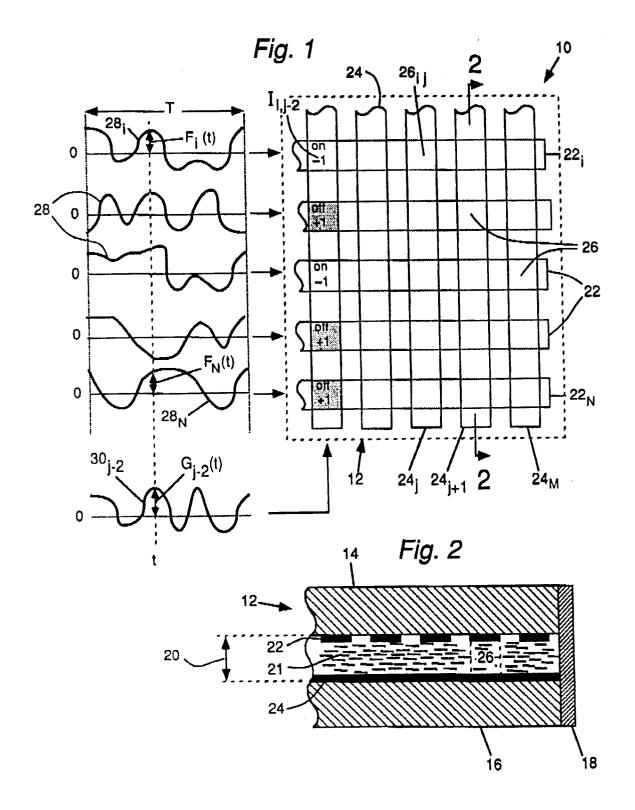

- Fig. 1 is a diagramatic view representing row and column addressing signals being applied to a LCD matrix in a display system according to this invention.

- Fig. 2 is a partial cross-sectional view of the LCD matrix taken along line 2-2.

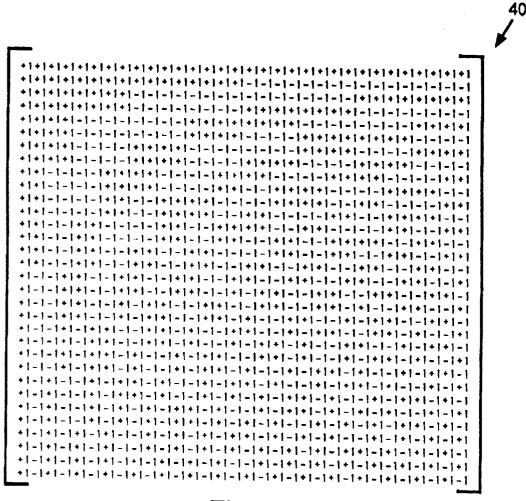

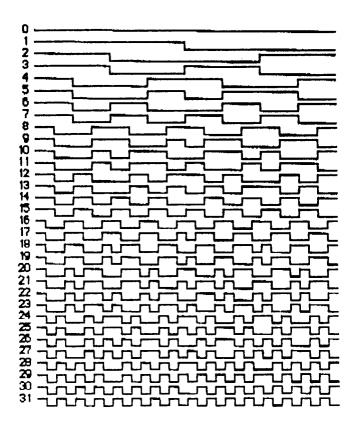

- Fig. 3 is an example of a  $32 \times 32$  Walsh function matrix utilized in connection with the invention of Fig. 1.

- Fig. 4 represents Walsh function waveforms corresponding to the Walsh function matrix of Fig. 3.

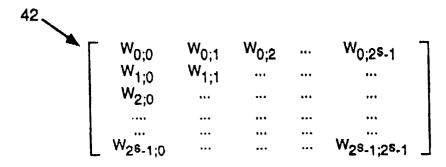

- Fig. 5 is a generalized form of the Walsh function matrix of Fig. 3.

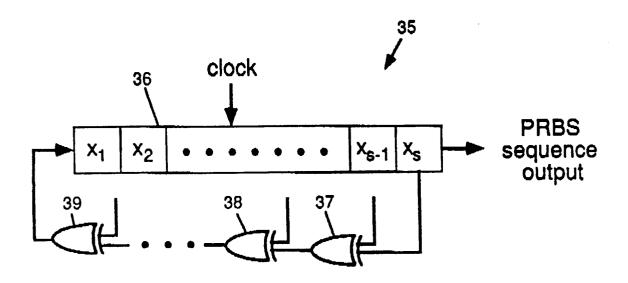

- Fig. 6 is a generalized representation of one embodiment of a circuit used to generate a pseudorandom binary sequence in accordance with the present invention.

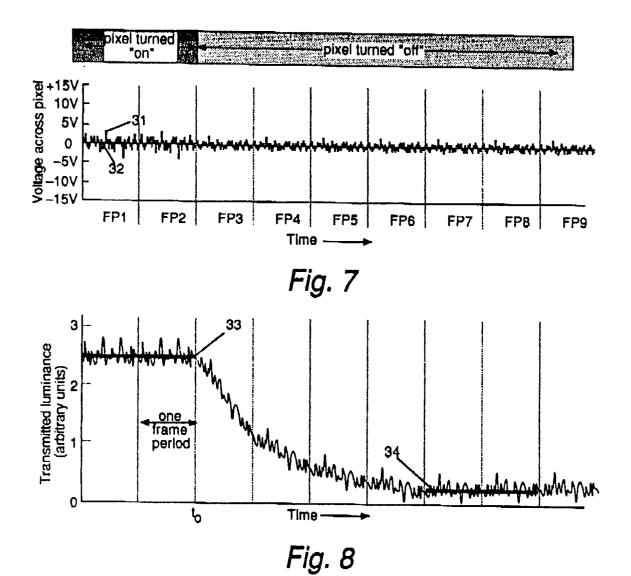

- Fig. 7 shows a voltage waveform across a pixel for several frame periods according to the addressing method of the present invention.

- Fig. 8 represents the optical response of a pixel to the voltage waveform of Fig. 7.

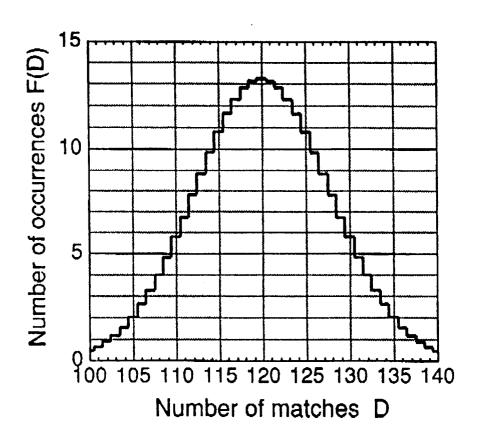

- Fig. 9 is a graph depicting the number of occurrences of D matches between the information vector and the Swift matrix vectors corresponding to one frame period for a 240 row display of this invention.

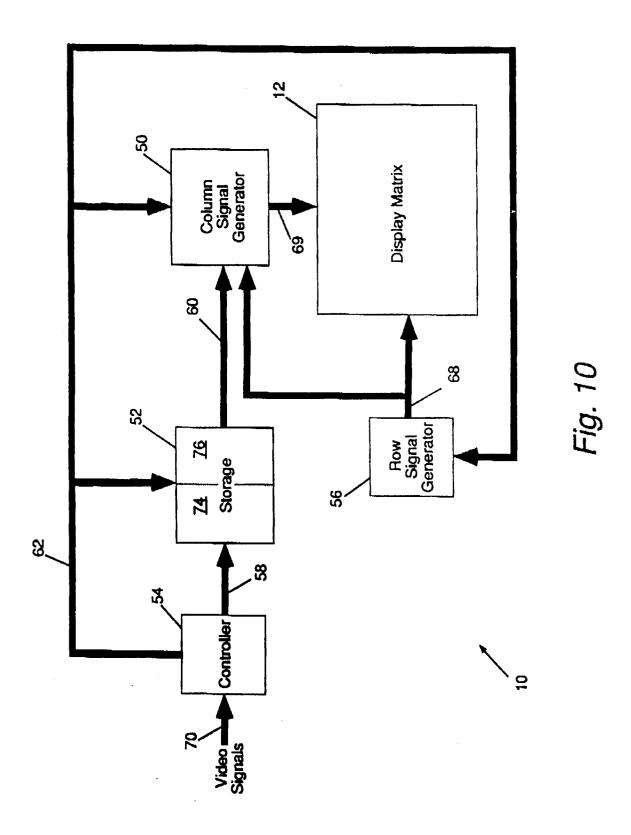

- Fig. 10 is a block diagram of the apparatus of the present invention.

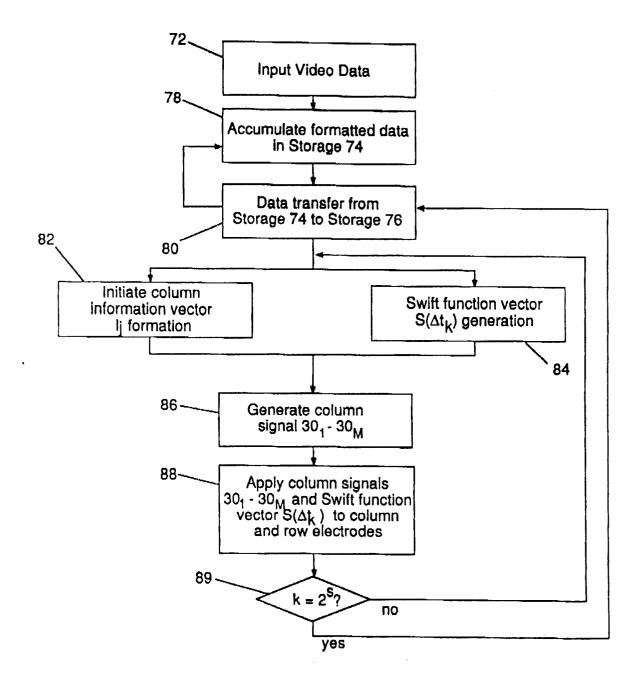

- Fig. 11 is a flowchart of the basic operation of one embodiment of the apparatus of the present invention.

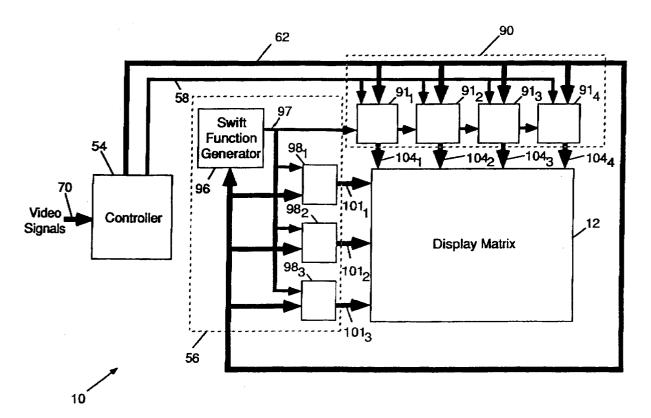

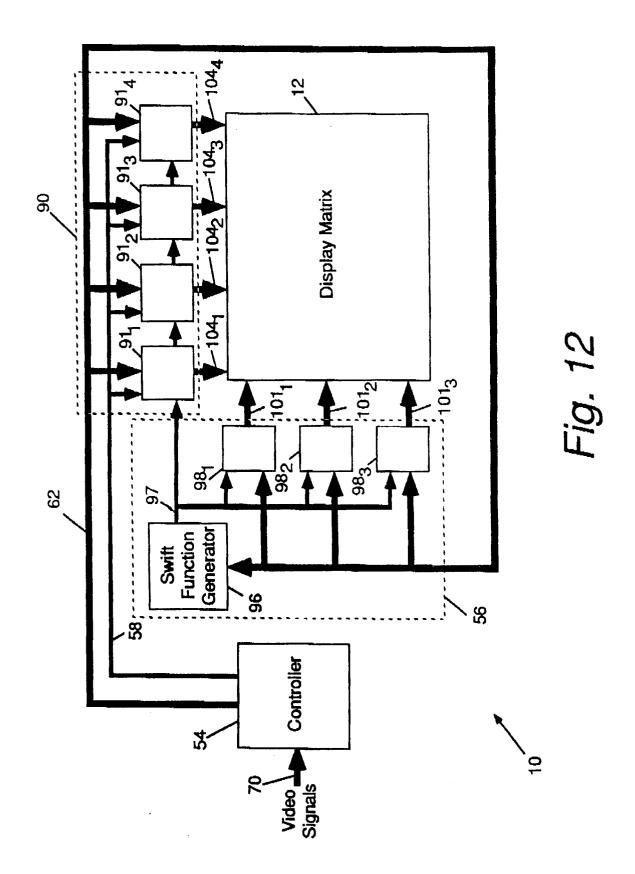

- Fig. 12 is a block diagram of one embodiment of the present invention for addressing an LCD display system.

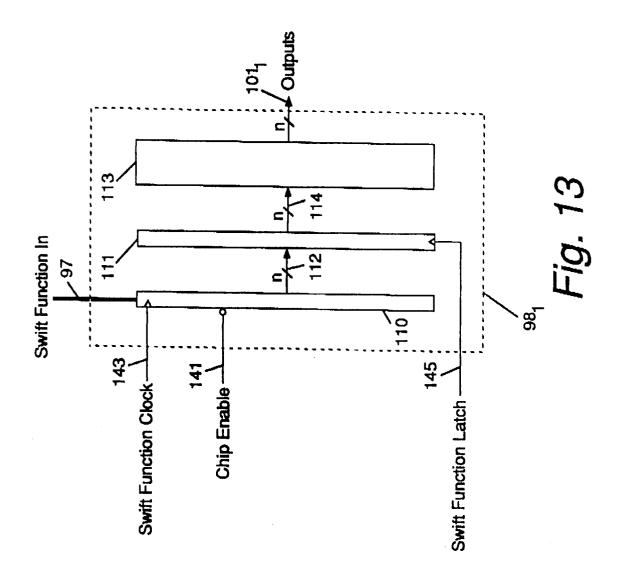

- Fig. 13 is a block diagram of a row driver IC shown in Fig. 12.

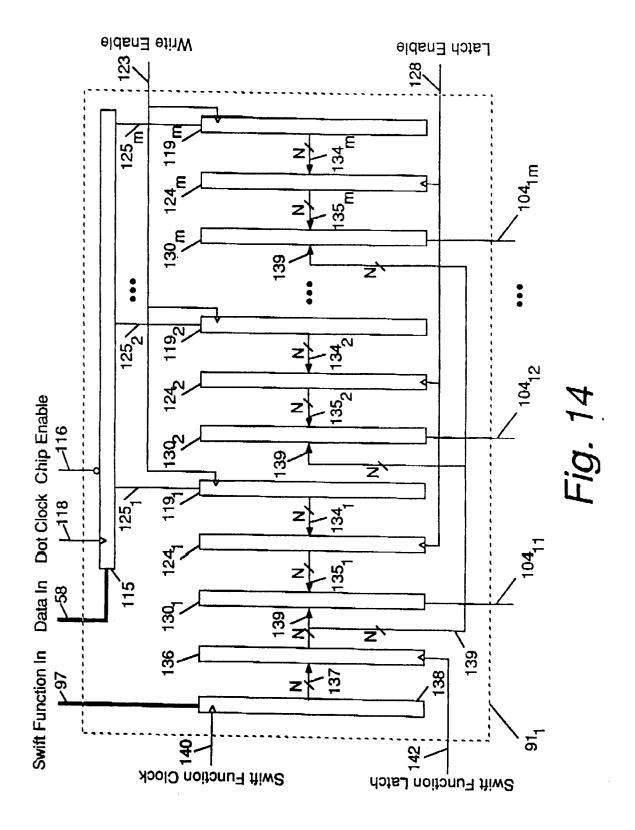

- Fig. 14 is a more detailed block diagram of the integrated column driver IC shown in Fig. 12.

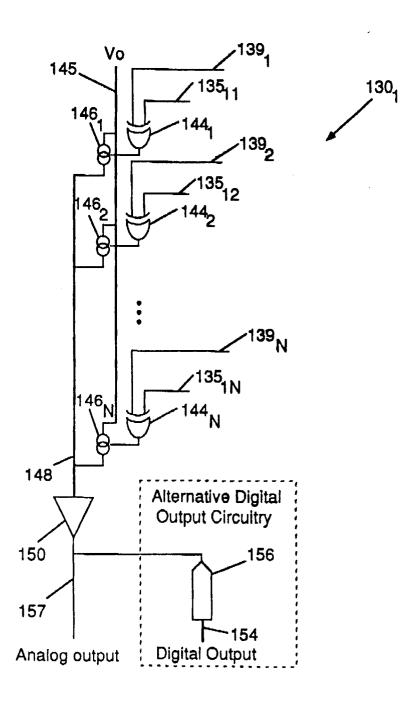

- Fig. 15 is a block diagram of one embodiment of the XOR sum generator shown in Fig. 14.

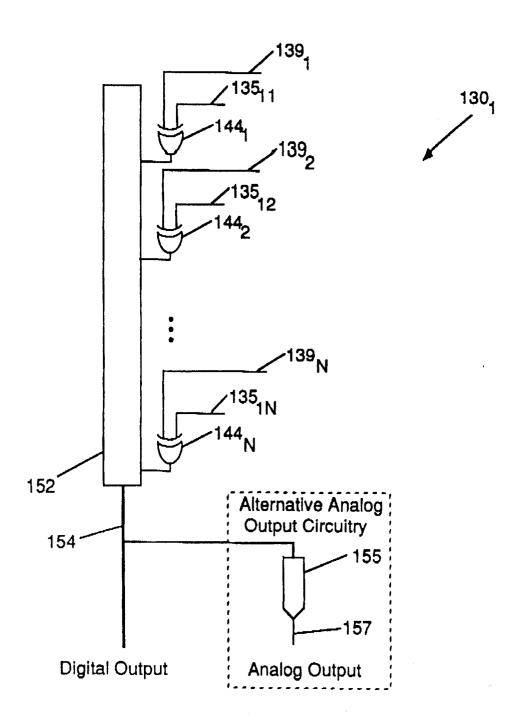

- Fig. 16 is a block diagram of a second embodiment of the XOR sum generator.

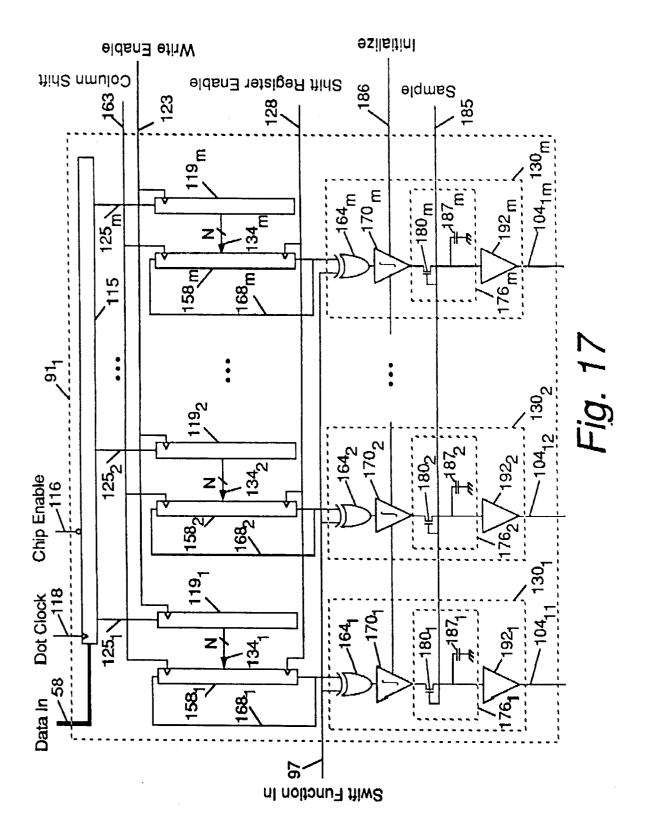

- Fig. 17 is a block diagram of the integrated driver of Fig. 14 with a third embodiment of the XOR sum generator.

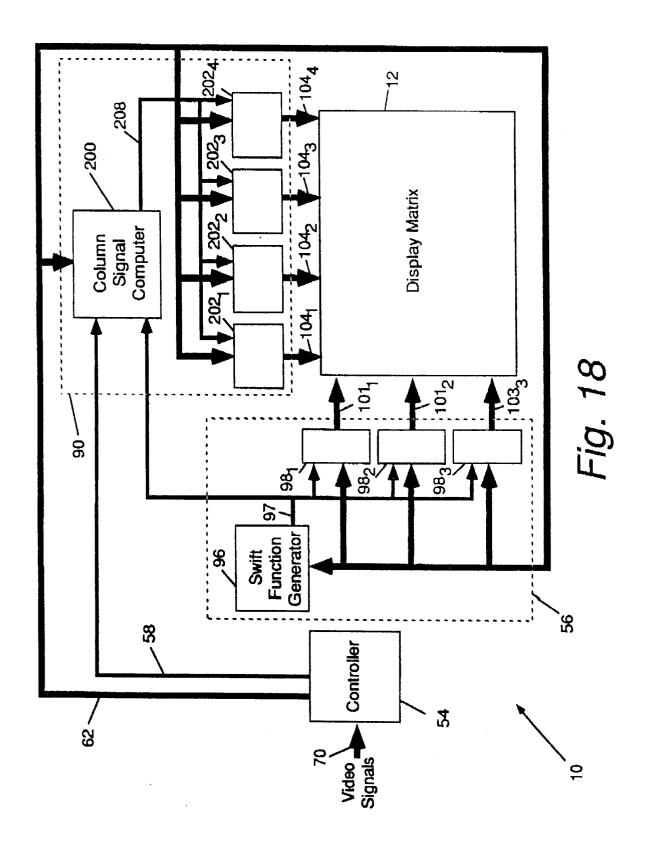

- Fig. 18 is a block diagram of a second embodiment of the present invention for addressing an LCD display system.

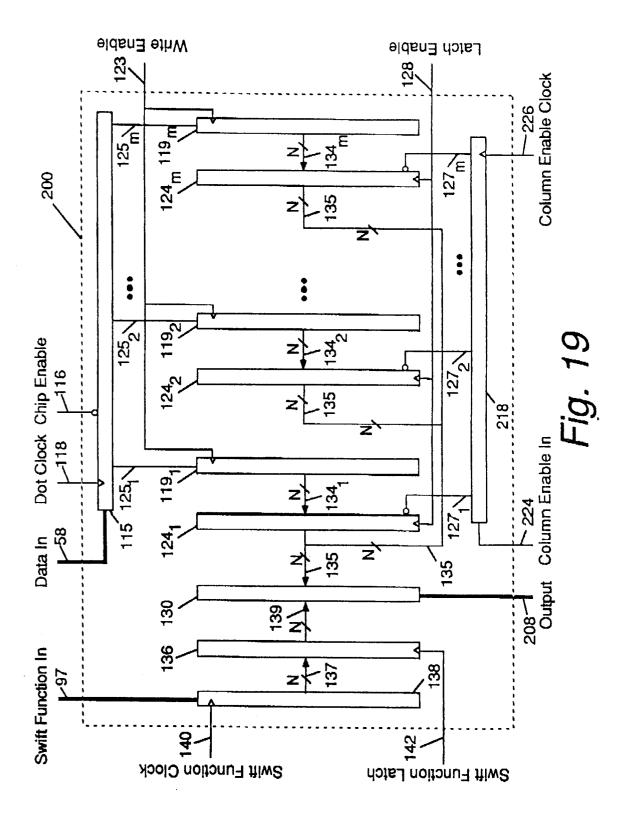

- Fig. 19 is a block diagram showing the column signal computer of Fig. 18.

- Fig. 20 is a block diagram showing an embodiment of the present invention of Fig. 14 incorporating gray shading.

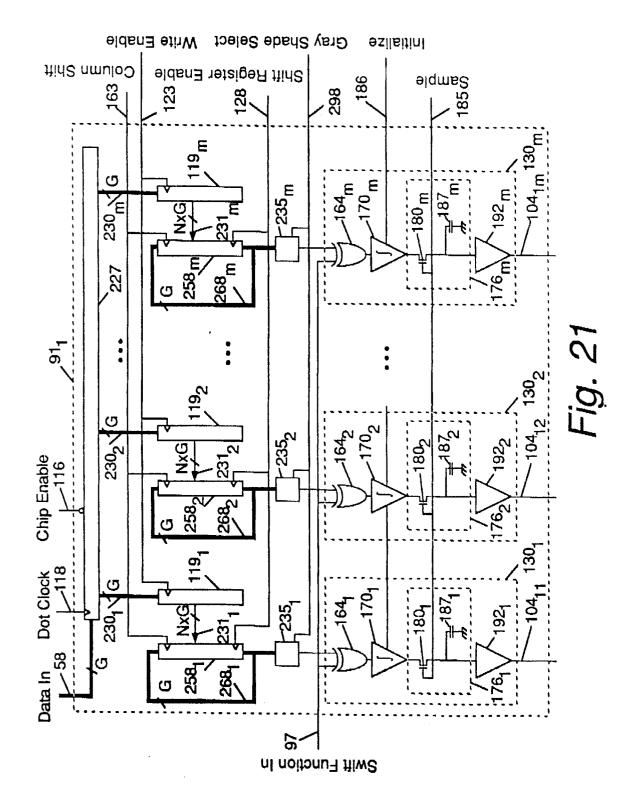

- Fig. 21 is a block diagram showing an embodiment of the present invention of Fig. 17 incorporating gray shading.

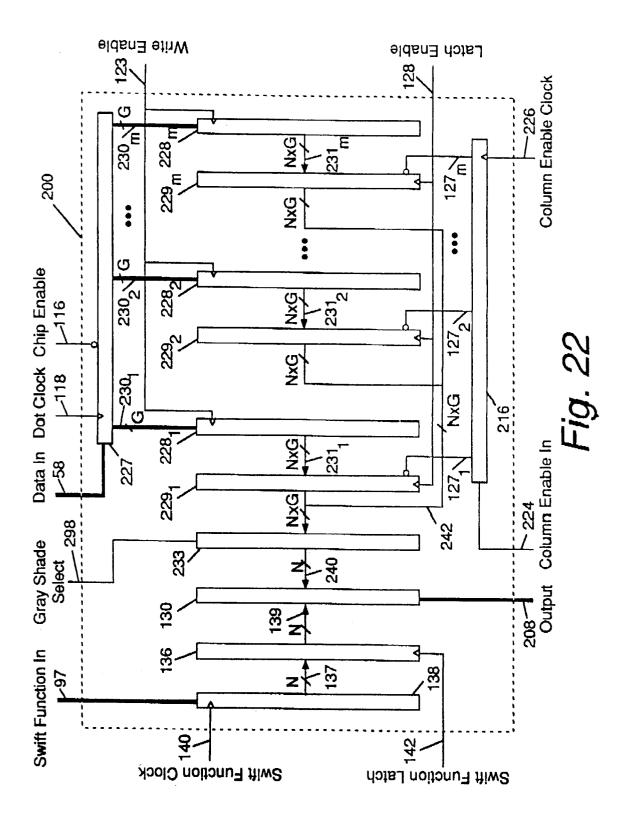

- Fig. 22 is a block diagram showing an embodiment of the present invention of Fig. 19 incorporating gray shading.

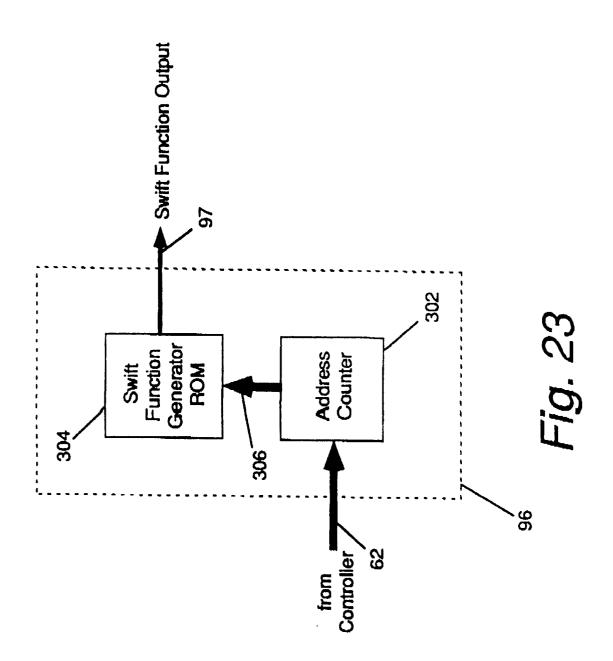

- Fig. 23 is a block diagram of one embodiment of the Swift function generator shown in Fig. 18.

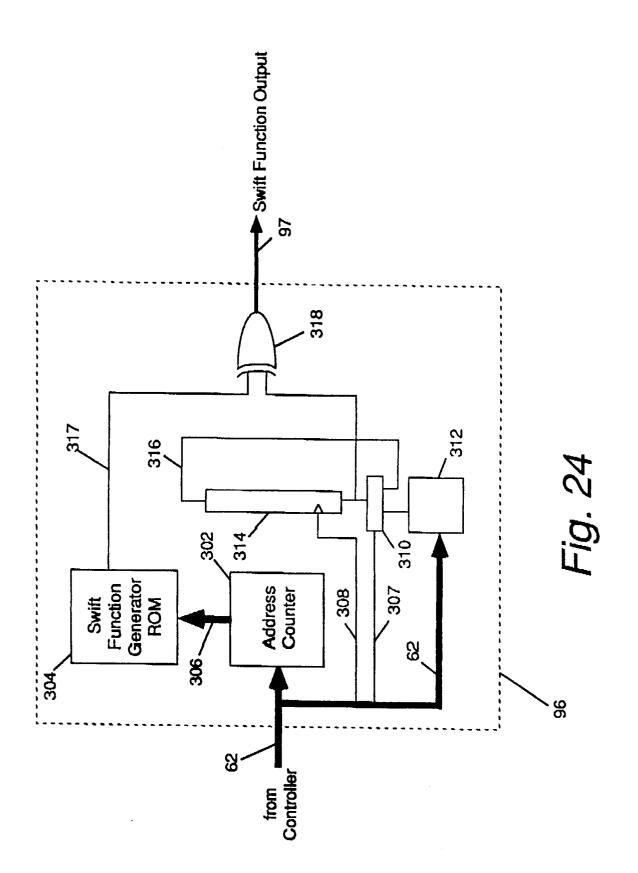

- Fig. 24 is a block diagram of a second embodiment of the Swift function generator which provides random inversion of the Swift functions.

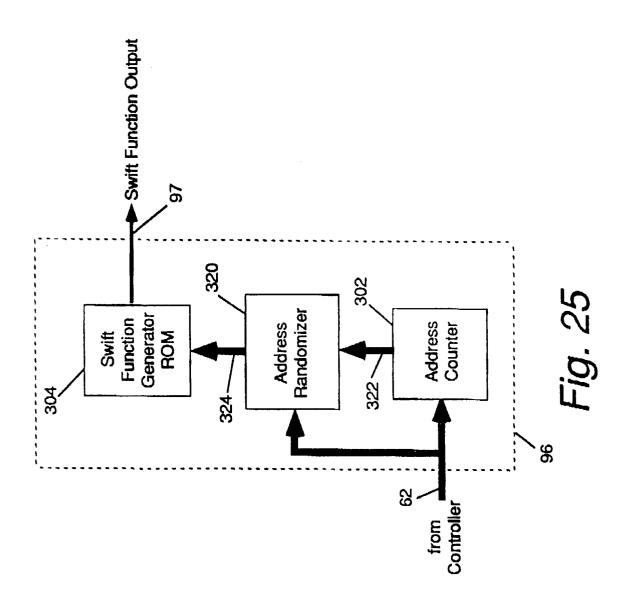

- Fig. 25 is a block diagram of a third embodiment of the Swift function generator which provides random reordering of the Swift functions.

# DESCRIPTION OF THE PREFERRED EMBODIMENTS

According to the principles of the present invention, a new addressing method for high information content, rms responding display systems is provided. In the addressing method of the present invention, the ratio of the magnitude of the peak voltage across an individual pixel during a frame period to the rms voltage averaged over one frame period is substantially lower than conventional addressing methods for high information content displays. In this way, the present addressing method improves display brightness and contrast ratio especially for displays using liquid crystal panels having time constants ( $\tau$ ) below 200 ms. Further, the addressing method eliminates the potentially damaging net dc component across the liquid crystal when averaged over a complete frame period so the displayed image may be advantageously changed every frame period. Still further, the present invention eliminates the occurrence of alignment instabilities.

Reference is now made to the drawings wherein like parts are shown with like reference characters throughout.

The addressing method may be best described in conjunction with a rms responding liquid crystal display (LCD) depicted in Figs. 1 and 2. A display system 10 is shown having a LCD display 12 preferably

comprising a pair of closely spaced parallel glass plates 14 and 16, most clearly shown in Fig. 2. A seal 18 is placed around the plates 14 and 16 to create an enclosed cell having a gap 20 where gap 20 has a dimension (d) of between 4µm and 10µm, although both thinner and thicker cell gaps are known. Nematic liquid crystal material, illustrated at 21, is disposed in cell gap 20.

An NxM matrix of transparent conductive lines or electrodes are applied to the inner surfaces of plates 14 and 16. For illustration purposes, the horizontal electrodes shall be referred to generally as row electrodes  $22_1$ - $22_N$  and the vertical electrodes as column electrodes  $24_1$ - $24_M$ . In some instances, it will be necessary to refer to one or two specific electrodes. In those instances, a row electrode will be referred to as the  $i^{th}$  electrode of the N row electrodes in the NxM matrix, e.g.  $22_i$ , where i=1 to N. Similarly, specific column electrodes will be referred to as the  $j^{th}$  electrode of M column electrodes where j=1 to M. The same nomenclature will also be used to refer to some other matrix elements discussed below.

The electrode pattern shown in Fig. 1 comprises hundreds of rows and columns, and wherever a row and column electrode  $22_1-22_N$  and  $24_1-24_N$  overlap, for example where row electrode  $22_i$  overlaps column electrode  $24_j$ , a pixel  $26_{ij}$  is formed. It should be apparent that other electrode patterns are possible that may advantageously use the features of the addressing method to be described. By way of example, the electrodes may be arranged in a spiral pattern on one plate and in a radial pattern on the other plate, or, alternatively, they may be arranged as segments of an alpha-numeric display.

Each row electrode  $22_1$ - $22_N$  of display 12 is driven with a periodic time-dependent row signals  $28_1$ - $28_N$ , each having a common period T, known as the frame period. In the mathematical equations that follow, the amplitude of row signal  $28_i$  is referred to as  $F_i(t)$ . It is a sufficient condition for the addressing method of the present invention that row signals  $28_1$ - $28_N$  be periodic and orthonormal over the frame period T.

The term "orthonormal" is a combination of "orthogonal" and "normal". In mathematical terms, normal refers to the property that row signals  $28_1$ - $28_N$  are normalized so that all have the same rms amplitude. Orthogonal refers to the property that each row signal  $28_i$  when multiplied by a different row signal,  $28_{i+3}$  for example, results in a signal whose integral over the frame period is zero.

The desired information state of pixels 26 can be represented by an information matrix I whose elements  $I_{ij}$  correspond to the state of the pixel defined by the overlap of the  $i^{th}$  row electrode with the  $j^{th}$  column electrode. If, according to the desired information pattern, pixel  $26_{ij}$  is to be "on", then the pixel state is -1 and  $I_{ij}$  = -1 (logic HIGH). If pixel  $26_{ij}$  is to be "off", then the pixel state is +1 and  $I_{ij}$  = +1 (logic LOW). In Fig. 1, for example, the element  $I_{ij\cdot 2}$  of the information matrix refers to the pixel state of the pixel defined by the  $i^{th}$  row and  $(j\cdot 2)^{th}$  column electrodes. This pixel state is set to a -1 and pixel 26 will be "on". An information vector  $I_j$  may also be defined that is the  $j^{th}$  column of the information matrix I. For the partial column  $j\cdot 2$  illustrated in Fig. 1, the elements  $I_{ij}$  of the information vector  $I_{j\cdot 2}$  are [-1, +1, -1, +1, +1] (for  $i=N\cdot 4$  to N)

Each column electrode  $24_1-24_M$  has a column signal, such as, for example, signal  $30_{j\cdot2}$ , applied thereto. The amplitude of column signal  $30_{j\cdot2}$  depends upon the information vector  $I_{j\cdot2}$  that represents all of the pixels in the column and row signals  $28_1-28_N$ . Similarly, the amplitude of all other column signals  $30_1-30_M$  depend on the corresponding information vector  $I_j$  and row signals  $28_1-28_N$ . In the mathematical equations that follow, the amplitude of column signal  $30_i$  at time t for the  $j^{th}$  column is referred to as

where I<sub>i</sub> is the information vector for the j<sup>th</sup> column.

35

40

50

55

The voltage across pixel  $26_{ij}$  in the  $i^{th}$  row and the  $j^{th}$  column,  $U_{ij}$ , is the difference between the amplitude  $F_i(t)$  of the signal applied to row  $22_i$  and the amplitude

of the signal applied to column 24i, that is:

$$U_{ij}(t) = F_i(t) - G_{I_j}(t)$$

(1)

The root mean square value of the voltage, (i.e., the rms voltage) appearing across pixel 26<sub>ij</sub> is:

$$\langle U_{ij} \rangle = \frac{1}{T} \sqrt{\int_{0}^{T} U_{ij}(t)^{2} dt}$$

(2)

Substituting equation 1 into equation 2 yields:

$$\langle U_{ij} \rangle = \frac{1}{T} \sqrt{\int_{0}^{T} F_{i}(t)^{2} dt - 2 \int_{0}^{T} F_{i}(t) G_{I_{j}}(t) dt + \int_{0}^{T} G_{I_{j}}(t)^{2} dt}$$

(3)

In the method of the present invention, column signals  $30_1-30_M$  are generated as a linear combination of all row signals  $28_1-28_N$  and coefficients of +1 or -1. The coefficients are the pixel states of the pixels in the column. Column signals  $30_1-30_M$  are therefore calculated for each column in the following manner:

$$G_{I_j}(t) = C \sum_{i=1}^{N} I_{ij} F_i(t),$$

(4)

where the  $l_{ij}$  is the information state of the pixel in the  $j^{th}$  column at the  $i^{th}$  row and c is a constant of proportionality.

Substituting equation 4 into equation 3 and assuming that row signals 28<sub>1</sub>-28<sub>N</sub> are orthonormal, i.e.,

$$\frac{1}{T}\sqrt{\int_{0}^{T}F_{p}(t)F_{q}(t)dt} = \begin{cases} \overline{F} & \text{if } p = q \\ 0 & \text{if } p \neq q \end{cases}, \tag{5}$$

provides:

5

10

15

20

25

30

35

55

$$\langle U_{ij} \rangle = \overline{F} \sqrt{1 - 2cI_{ij} + Nc^2}$$

(6)

For an "on" pixel,  $I_{ij}$  = -1 and the "on" rms voltage across the pixel is therefore:

$$\langle U_{on} \rangle = \overline{F} \sqrt{1 + 2c + Nc^2}$$

(7)

For an "off" pixel,  $l_{ij} = +1$  and the "off" rms voltage across the pixel is therefore:

$$\langle U_{off} \rangle = \overline{F} \sqrt{1-2c+Nc^2}$$

(8)

The selection ratio R is the ratio of the "on" rms voltage to the "off" rms voltage that can occur across a pixel. That is:

$$R = \frac{\langle U_{on} \rangle}{\langle U_{off} \rangle} \tag{9}$$

The maximum selection ratio can be found by substituting equations 7 and 8 into equation 9 and

maximizing R with respect to the proportionality constant c. This results in:

$$R_{\text{max}} = \sqrt{\frac{\sqrt{N}+1}{\sqrt{N}-1}} \quad , \tag{10}$$

with

10

5

$$C = \frac{1}{\sqrt{N}} \tag{11}$$

15

Under some circumstances it may be advantageous to use a different value of c which does not maximize the theoretical selection ratio.

Substituting c from equation 11 into equation 8 and setting (Uoff) = 1, i.e., normalizing all voltages with respect to the "off" rms voltage results in

$$\overline{F} = \sqrt{\frac{\sqrt{N}}{2(\sqrt{N}-1)}}.$$

(12)

25

20

Substituting equation 11 into equation 4 gives the expression for the column voltage:

30

$$G_{I_j}(t) = \frac{1}{\sqrt{N}} \sum_{i=1}^{N} I_{ij} F_i(t),$$

(13)

35

45

Referring again to Fig. 1, where row signals 281-28N are analog signals that continuously vary in frequency and amplitude, equation 13 may be easily implemented in a variety of hardware embodiments. For example, display system 10 may incorporate a plurality of analog multipliers that multiply the amplitude F<sub>i</sub>(t) of each row signal 28<sub>i</sub> with the corresponding element of the information matrix I<sub>ii</sub>. An analog summer sums the output of each multiplier to provide a voltage to the corresponding column electrode 24<sub>1</sub>-24<sub>M</sub>.

Those skilled in the art will recognize that a common signal H(t) could be superimposed on all row and column signals 28<sub>1</sub>-28<sub>N</sub> and 30<sub>1</sub>-30<sub>M</sub> to alter their outward appearances, but this does not change the principles of the present invention. This is because, as equation 1 shows and as discussed earlier, it is the voltage difference across a pixel which determines its optical state and this difference is unaffected by superimposing a common signal on all row and column electrodes 22<sub>1</sub>-22<sub>N</sub> and 24<sub>1</sub>-24<sub>M</sub>.

# Walsh Function Matrix Description

50

The generalized analog row signals 28₁-28<sub>N</sub> shown in Fig. 1 could be bilevel signals. Bilevel signals are advantageous because they are particularly easy to generate using standard digital techniques. Walsh functions are one example of bilevel, orthonormal functions that may be used as row addressing signals. Walsh row signals have the form:

$$F_i(t) = \overline{F} \cdot W_{ik} = \overline{F} \cdot W_i(\Delta t_k)$$

(14)

55

where the  $W_{ik}$  are elements of a  $2^sx2^s$  Walsh function matrix which are either +1 or -1. The index i corresponds to the ith row of the Walsh matrix as well as to the signal for the ith row of the display. The Walsh matrix columns correspond to a time axis consisting of 2s equal time intervals  $\Delta t$  over the frame period T, and the index k refers the  $k^{th}$  time interval  $\Delta t_k$  as indicated by the alternate notation in equation 14. The elements of the Walsh matrix are either +1 or -1, so that amplitude  $F_i(t)$  assumes one of two values, i.e. either + $\overline{F}$  or - $\overline{F}$  over each of the time intervals  $\Delta t_k$ .

Column signals 30<sub>1</sub>-30<sub>M</sub> are obtained by substituting equation 14 into equation 13 to give:

$G_{I_j}(\Delta t_k) = \frac{\overline{F}}{\sqrt{N}} \sum_{i=1}^{N} I_{ij} \cdot W_{ik}$  (15)

10

5

An example of a 32x32 (s = 5) Walsh function matrix 40 is given in Fig. 3 and one period of the Walsh waves derived from corresponding rows of this matrix are shown in Fig. 4. At the end of each period the Walsh waves repeat. In the examples of Fig. 3 and 4 the Walsh functions have been ordered according to sequency with each succeeding Walsh wave having a sequency of one greater than the preceding Walsh wave. Sequency denotes the number of times each Walsh wave crosses the zero voltage line (or has a transition) during the frame period. The sequency has been noted in Fig. 4 to the left of each Walsh wave.

Walsh functions come in complete sets of  $2^s$  functions each having  $2^s$  time intervals. If the number of matrix rows N of display 12 is not a power of 2, then row signals  $28_1-28_N$  must be chosen from a Walsh function matrix having an order corresponding to the next higher power of two, that is  $2^{s-1} < N \le 2^s$ . The Walsh matrix must have an equal or greater number of rows than the display because the orthogonality condition prevents the same row signal  $28_i$  from being used more than once. For example, if N = 480 (i.e., display 12 has 480 rows designated  $22_1 - 22_{480}$ ), 480 different or unique row signals are selected from the set of 512 Walsh functions having 512 time intervals  $\Delta t$ . In this instance, s = 9.

It should be apparent that it is possible for display 12 to be configured into several separately addressable screen portions. For example, if a 480 row display 12 were split into two equal portions, each portion of display 12 would be addressed as though it were a 240 row display. In this instance, N = 240 and row signals  $28_1$ - $28_N$  are selected from the set of 256 Walsh functions having 256 time intervals  $\Delta t$ .

The general form of the Walsh function matrix 42 is shown in Fig. 5. The elements  $W_{u,v}$  (where u,v=0, 1, 2, ...  $2^{s-1}$ ) have the sequency ordering described above if each element is defined by the relation:

$$W_{u,v} = (-1)^{\sum_{i=0}^{s-1} r_i(u) \cdot v_i}$$

(16)

35

where subscript i refers to the i<sup>th</sup> digit of the binary representation of the decimal number u that denotes the row location or v that denotes the column location, i.e.,

$$U_{decimal} = (U_{s-1}, U_{s-2}, \cdots U_1, U_0)_{binary}$$

(17)

and

$$v_{decimal} = (v_{s-1}, v_{s-2}, w_1, v_0)_{binary}$$

(18)

where the ui and vi are either 0 or 1; and

55

If the sum in equation 16 is odd, then  $W_{u,v} = -1$  and if it is even, then  $W_{u,v} = +1$ . By using equations 16 - 19, any element in matrix 42 may be determined. For example, to determine

the element in the  $6^{th}$  row and the  $4^{th}$  column (i.e.,  $W_{5,3}$ ) in a Walsh matrix of order 8 (i.e., s = 3), the operations indicated by equations 17 and 18 must be performed. Specifically, since:

$$U_{decimal} = 5 = (101)_{binary}$$

(20)

then:

5

15

25

35

40

50

55

$$u_2 = 1, u_1 = 0, u_0 = 1$$

(21)

10 Similarly,

$$V_{decimal} = 3 = (011)_{binary}$$

(22)

and therefore:

$$v_2 = 0, v_1 = 1, v_0 = 1$$

(23)

Substituting the above values for u as found in equation 21 into the appropriate equations 19 we obtain:

20

$$r_0(u) = u_2 = 1$$

$r_1(u) = u_2 + u_1 = 1 + 0 = 1$  (24)

$r_2(u) = u_1 + u_0 = 0 + 1 = 1$

Combining equations 23 and 24, we obtain:

$$v_0 \cdot r_0 = 1 \cdot 1 = 1$$

$v_1 \cdot r_1 = 1 \cdot 1 = 1$  (25)

$v_2 \cdot r_2 = 0 \cdot 1 = 0$

By summing the results (equation 16), it is found that  $\Sigma = 2$  and  $W_{5,3} = (-1)^2 = 1$ .

The remaining elements of the matrix 42 may be determined by performing similar calculations. The above calculations may be performed in real time for each frame period or, preferably, the calculations may be performed once and stored in read-only memory for subsequent use. The Walsh function waves of matrix 42 form a complete set of orthonormal functions having the property:

$$\frac{1}{2^{s}} \sum_{j=0}^{2^{s}-1} W_{i,j} \cdot W_{k,j} = \delta_{i,k}$$

(26)

where:

$$\delta_{ik} = 0 \text{ if } i=k$$

$$\delta_{ik} = 0 \text{ if } i\neq k.$$

(27)

# Pseudo Random Binary Sequences

Another class of bilevel orthonormal row signals  $28_1$ - $28_N$  may be obtained from a class of functions known as maximal length Pseudo Random Binary Sequences (PRBS) functions.

PRBS functions can be generated from the general shift register circuit 35 having a shift register 36 with exclusive-or feedback gates 37-39 shown in Fig. 6. Such a circuit can be practically implemented as such or it can be used as a model to generate the PRBS functions on a computer with the results stored in a ROM.

Starting with the shift register in some initial logic state designated by  $x_1$  -  $x_s$ , clock pulses are applied to the register which successively shift the logic states of the various stages forward to the output stage and

feed new logic states back to the input stage as determined by the connections to the exclusive-or gates. After a certain number of clock pulses, the shift register returns to its initial state and the binary sequence at the output stage starts to repeat. The length of the output sequence before it repeats is determined by the number and positions of the stages involved in the feedback loop. For an s-stage register, the maximum length L of the nonrepeating sequence is L = 2<sup>s</sup>-1. Examples of feedback connections that generate maximal length sequences are summarized below.

| 10 | shift register<br>stages s | feedback connections<br>at stages | length of sequence $L = 2^S - 1$ |

|----|----------------------------|-----------------------------------|----------------------------------|

|    | 2                          | 2,1                               | 3                                |

| 15 | 3                          | 3,1                               | 7                                |

|    | 4                          | 4,3                               | 15                               |

|    | 5                          | 5,3                               | 31                               |

|    | 6                          | 6,5                               | 63                               |

| 20 | 7                          | 7,6                               | 127                              |

|    | 8                          | 8,6,5,4                           | 255                              |

|    | 9                          | 9,5                               | 511                              |

| 25 | 10                         | 10,7                              | 1023                             |

|    | 11                         | 11,9                              | 2047                             |

|    | 12                         | 12,11,8,6                         | 4095                             |

| 30 | 13                         | 13,12,10,9                        | 8191                             |

Table 1

By considering the logic states as voltage levels, and substituting a +1 for the logic 0 and -1 for the logic 1, the exclusive-or operation is transformed to ordinary multiplication. We will adopt this latter definition of the logic states, as indicated in Table 2, throughout the remainder of this section.

| input 1 | input 2 | output |

|---------|---------|--------|

| +1      | +1      | +1     |

| +1      | -1      | -1     |

| -1      | +1      | -1     |

| -1      | -1      | +1     |

Table 2

Consider the simple example of a 3 stage shift register with feedback connections at 3 and 1 as shown in Table 1. Starting from the initial logic state of -1, +1, +1 for the three stages, the subsequent states of the shift register can be determined from the recursive relations:

$$x_1(n+1) = x_3(n)x_1(n)$$

55  $x_2(n+1) = x_1(n)$  (28)

$x_3(n+1) = x_2(n)$

40

45

50

where  $x_i(n)$  is the logic state of the  $i^{th}$  stage in the register after application of the  $n^{th}$  clock pulse assuming

that the register is initialized with the first clock pulse. The state of the shift register after a first and subsequent clock pulses is summarized in Table 3. For this case, the state of the shift register and output binary sequence repeats after 7 cycles, i.e.,  $x_i(n) = x_i(n+7)$ .

| clock<br>pulse                | 1        | 2        | 3        | 4        | 5        | 6  | 7     | 8        | 9        |

|-------------------------------|----------|----------|----------|----------|----------|----|-------|----------|----------|

| x <sub>1</sub> x <sub>2</sub> | -1<br>+1 | -1<br>-1 | -1<br>-1 | +1 -1 -1 | -1<br>+1 | +1 | +1 +1 | -1<br>+1 | -1<br>-1 |

| <b>x</b> <sub>3</sub>         | +1       | +1       | -1       | - T      | -1       | +1 | -1    | +1       | +1       |

Table 3

As another example, consider a 255 cycle maximal length PRBS function obtained from the following recursive equations based on an 8 stage shift register. Again, making the feedback connections recommended in Table 1 for s = 8 gives:

$$x_{1}(n+1) = x_{8}(n) x_{6}(n) x_{5}(n) x_{4}(n)$$

$$x_{2}(n+1) = x_{1}(n)$$

$$x_{3}(n+1) = x_{2}(n)$$

$$\vdots$$

$$x_{8}(n+1) = x_{7}(n)$$

(29)

30

5

10

15

An LxL matrix of PRBS functions may be defined, where the first row is just the PRBS function itself, i.e.,  $P_{1j} = x_s(j)$ , and each subsequent matrix row is derived from the previous one by a cyclical shift of one cycle. Thus, the second row is  $P_{2j} = x_s(j+1)$  and the i<sup>th</sup> row is  $P_{ij} = x_s(j+i-1)$ . Maximal length PRBS functions are interesting because of the property that they are nearly orthogonal to shifted versions of themselves i.e.

$$\frac{1}{L} \sum_{j=1}^{L} P_{ij} P_{kj} = \begin{cases} 1 & \text{if } i = k \\ -1/L & \text{if } i \neq k \end{cases}$$

(30)

The expression for the column voltage using PRBS functions is similar to equation 15 for the Walsh functions except that the PRBS matrix elements P<sub>ik</sub> are substituted for the Walsh matrix elements W<sub>ik</sub>.

# Swift Functions

50

As discussed above, analog row signals  $28_1$ - $28_N$  of Fig. 1 may be implemented using waveforms generated with analog circuit elements. However, if row signals  $28_1$ - $28_N$  are digital representations of Walsh or PRBS functions, hardware implementation of the present addressing method is possible using digital logic. Further, to improve display performance of display system 10, a fourth class of functions may be described which are called "Swift" functions. Swift functions may be derived, for example, from the Walsh functions or from the PRBS functions.

## Swift functions based on Walsh functions:

A Swift matrix may be derived from Walsh matrix 42 by selecting N rows. Preferably the selected rows are derived from the set of sequency-ordered Walsh waves having the highest sequency.

One advantage of using the higher sequency rows is that the first row of Walsh matrix 42 need not be used. The first row is unique in that it is always  $\pm 1$  while all other rows have an equal number of positive amplitude and negative amplitude time intervals. Eliminating the first row eliminates the potentially damaging net dc component across the pixels of display 12 when the pixel voltage is averaged over a frame period. The average net dc component across a pixel is determined from the difference between the column voltage amplitude  $G_I(t)$  and the row voltage amplitude  $F_I(t)$  averaged over all the time intervals  $\Delta t$  of the period.

Since there is no potentially damaging net dc component when Swift waveforms  $S_i$  are used, it is not necessary to invert row and column signals  $28_1$ - $28_N$  and  $30_1$ - $30_M$  after every frame period. Further, with the present invention, display information may be advantageously changed after every frame period.

The Swift matrix may be further modified by randomly inverting a portion of the N rows in the Swift matrix. Inversion is accomplished by multiplying each element in the selected row by -1. In one preferred embodiment, about half of the rows in the Swift matrix are inverted. Thus for any time interval about half the rows receive a voltage of  $+\overline{F}$  and the remaining rows receive a voltage of  $-\overline{F}$ . For other time intervals, this proportion stays about the same except that different rows are selected for the  $+\overline{F}$  and  $-\overline{F}$  voltages.

Inverting the Swift waves in this way affects neither the orthogonal or normal property but eliminates the possibility that certain common information patterns, such as would occur if stripes or checker-boards of various widths were displayed, might produce an unusually high or low number of matches between information vector  $\mathbf{I}_{i}$  and the Swift function vector, and hence a large

$^{\mathtt{G}_{\mathtt{I}}}{}_{\mathtt{j}}$

voltage for certain time intervals.

25

30

40

45

50

55

The Swift matrix could also be modified by reordering the rows. This does not affect the orthonormal property, and under some circumstances could be used to reduce display streaking effects.

Swift functions based on maximal length PRBS:

Although maximal length PRBS functions are nearly orthogonal for large L, they still would induce crosstalk if used in this form for the matrix addressing of the present invention. To obtain theoretically orthogonal functions from the maximal length PRBS functions, a new set of Swift functions are created by adding an extra time interval to the PRBS functions and forcing the value of the Swift function to always be either +1 or -1 during this interval, i.e.,  $P_{I(L+1)} = +1$  or -1. The resulting pulse sequence now has exactly  $2^s$  timeintervals with the desired orthonormal properties:

$\frac{1}{2^{s}} \sum_{j=1}^{2^{s}} P_{ij} P_{kj} = \begin{cases} 1 & \text{if } i = k \\ 0 & \text{if } i \neq k \end{cases}$  (31)

It is preferable to choose  $P_{i(L+1)} = +1$  in order to ensure that the functions will have no net dc value, i.e.

$\sum_{j=1}^{(L+1)} P_{ij} = 0.$  (32)

Displays addressed with these Swift functions seem to give a more uniform appearance than displays addressed with Swift functions based on Walsh functions. This is because the PRBS functions all have the

same frequency content, and therefore the attenuation of the row waveforms by the RC load of the display is substantially the same for all rows.

In a similar manner to the Swift functions based on Walsh functions, preferably, about half of the rows of the present Swift matrix are inverted by multiplying these rows by -1.

## Swift functions based on other orthonormal bilevel functions:

One skilled in the art will recognize that there is practically a limitless number of orthonormal bilevel functions that could be used for Swift functions. For example the Swift functions based on Walsh functions described above could be transformed into a completely different set of Swift functions simply by interchanging an arbitrary number of columns in the Swift matrix, a procedure which does not affect the orthonormal property. Of course the same holds true for the Swift functions based on maximal length PRBS functions. Swift functions could also be transformed by inverting an arbitrary number of columns, i.e. by multiplying them by -1. But this procedure would be less desirable because, even though the orthonormal property would be retained, this transformation generally would introduce a net dc voltage across the pixel which would necessitate inverting all drive levels every other frame period to remove it.

The expression for the column voltage using Swift functions is similar to equation 15 derived for the Walsh functions except that the Swift matrix elements  $S_{ik}$  are substituted for the Walsh matrix elements  $W_{ik}$ .

## 20 Amplitude of the Column Signals:

5

35

45

Examination of the sum in equation 15 reveals that for any given time interval  $\Delta t_k$ , the amplitude

$$G_{\downarrow}$$

(t)

of column signal  $30_j$  is dependant upon the magnitude of the summation. The sum is the number of times an element in information vector  $I_j$  matches an element in the Swift column vector  $S_k$  (i.e., +1 matches +1 or -1 matches -1) minus the number of times there are mismatches (i.e., +1 and -1 or -1 and +1). Since the total number of matches and mismatches must add up to N, equation 15 becomes:

$$G_I(\Delta t_k) = \frac{\overline{F}}{\sqrt{N}} (2D_k - N), \qquad (33)$$

where  $D_k$  is the number of matches between information vector  $I_j$  and the  $k^{th}$  column of the Walsh, Swift or PRBS function matrix. Thus the column voltage can be as large as  $+\sqrt{N}\cdot F$  or as small as  $-\sqrt{N}\cdot F$  depending upon whether there are N matches or zero matches. However, assuming that sign of the column elements in the matrix  $S_{ik}$  are randomly distributed, as is true in the Swift matrix, the probability of all elements of information vector  $I_j$  exactly matching or exactly mismatching the Swift matrix column  $S_k$  is very low, especially when the number of rows N of display 12 is large, as is the case for a high information content display. The matching probability for certain Walsh matrix columns could be significantly higher for certain information patterns which is one reason the use of a Swift function matrix is preferred.

The probability of D matches occurring P(D) can be expressed as

$$P(D) = \begin{bmatrix} N \\ D \end{bmatrix}$$

(34)

where  $\binom{N}{D}$  ) is the binomial coefficient giving the number of combinations of N distinct things taken D at a time, and is defined by:

$$\begin{pmatrix} N \\ D \end{pmatrix} = \frac{N!}{(N-D) \cdot ! \cdot D!} \tag{35}$$

5

For large N and D, the binomial distribution may be approximated by the normal distribution. Thus, equation 34 becomes:

10

15

55

$$P(D) = \sqrt{\frac{2}{\pi N}} \exp\left[\frac{-(2D-N)^2}{2N}\right]$$

(36)

It is clear from equation 36 that the most probable number of matches will occur for D = N/2 for which, referring to equation 33, the column voltage is zero. The more D deviates from the most probable value of N/2, the larger the magnitude of the column voltage, but this condition becomes less and less likely to occur. The largest column voltage that will occur, on the average, over one complete frame period (i.e., considering every time interval  $\Delta t_k$  where  $1 \le k \le 2^s$ ) can be obtained by solving equation 36 for the value of D' where P(D') =  $2^{-s}$  and substituting this value into equation 33. The resultant most probable peak column signal voltage magnitude that will occur over a complete frame period,  $G_{\text{peak}}$ , is then given by

$$G_{peak} = \overline{F}\sqrt{(2s+1)\ln(2) - \ln(\pi N)}$$

(37)

Since the voltage across the pixel is the difference between the row and column voltages (equation 1), the magnitude of the maximum voltage occurring across a pixel U<sub>peak</sub> is:

$$U_{peak} = \overline{F}[1 + \sqrt{(2s+1)\ln(2) - \ln\pi N}]$$

(38)

which is also the ratio of the magnitude of the peak voltage occurring during a frame period to the "off" rms voltage since  $\langle U_{off} \rangle$  has been normalized, i.e.,  $\langle U_{off} \rangle = 1$ . It is desirable that  $U_{peak}$  be as close to  $\langle U_{off} \rangle$  as possible to minimize the effect of "frame response". By way of example, for a display having 240 multiplexed rows (N = 240) s = 8 and from equations 12 and 38,  $U_{peak} / \langle U_{off} \rangle = 2.39$ . Over many frame periods T, higher peak voltages are likely to occur. However, it is very unlikely that the ratio of  $U_{peak} / \langle U_{off} \rangle$  will exceed 5:1. This ratio is dramatically lower than the value of 12.06 which results from the conventional addressing method for high information content LCDs.

# Optical Response to Swift Function Drive:

Referring now to Figs. 7 and 8, a typical waveform  $U_{ij}(t)$  across a pixel, such as pixel  $26_{ij}$ , of Fig. 1, is shown for several frame periods T for the case of Swift function drive where display 12 is a STN display. Waveform  $U_{ij}(t)$  comprises a plurality of substantially low amplitude pulses such as pulses 31 and 32 that occur throughout the frame period. By providing the pixels with a plurality of low amplitude pulses throughout the entire frame period, frame response is substantially avoided. The resulting improvement in brightness and contrast ratio is especially noticeable for displays 12 having time constants below 200ms.

Fig. 8 represents the optical response of pixel  $26_{ij}$  to waveform  $U_{ij}(t)$ . As shown by the superimposed designators 33 and 34, the transmitted luminance is relatively constant during frame periods FP1 and FP2 when pixel  $26_{ij}$  is in the "on" state and frame periods FP7 and FP8 when the pixel  $26_{ij}$  is in the "off" state. During frame periods FP1 and FP2, the transmitted luminance of pixel  $26_{ij}$  appears bright to an observer because the relatively constant luminance is the result of reduced frame response. Similarly, during frame periods FP7 and FP8, pixel  $26_{ij}$  appears darker than would a pixel exhibiting greater frame response.

# Number of Levels Required for Column Signals:

From equation 33 it is seen that, for each time interval,

assumes a discrete voltage level determined by the total number of matches, D, between corresponding elements in information vector I<sub>j</sub> and the Swift function vector. Since D generally can take any integral value between 0 and N, then there will be a maximum of N+1 possible voltage levels. However according to equations 34 and 36, not all values of D are equally probable, and more particularly values of D near N/2 are much more likely to occur than values of D near the extremes of 0 or N. Thus the actual number of levels required to practically implement the addressing method of the present invention is considerably fewer than N+1. The minimum number of levels required would be those levels which, on the average, occur at least once during the frame period, i.e. after information vector I<sub>j</sub> has been compared with all 2<sup>s</sup> Swift vectors of the frame period. The average number of times that D matches will occur during one frame period, F(D), is determined by multiplying the 2<sup>s</sup> time intervals of the frame period by the probability function P(D) of equation 34 or 36. Thus the values of D that will occur at least once during the frame period are those values of D which satisfy the condition:

$$F(D) = 2^{s}P(D) \ge 1$$

(39)

Adding the number of different values of D that satisfy this condition gives the minimum munber of voltage levels required. Making use of equation 36 results in:

Minimum number of levels =

$$\sqrt{N}\sqrt{(2s+1)\ln(2)-\ln(\pi N)}$$

(40)

Substituting known values into equation 40 shows that only a small fraction of the maximum possible number of levels are actually needed for the addressing scheme of the present invention. For example, substituting N = 240 and s = 8 into equation 40 results in a minimum of 35 levels. This lies considerably below the maximum possible number of 241 levels.

In Fig. 9, F(D) is plotted versus the number of matches D in a 240 row matrix. The plot describes a bell-shaped curve showing that on the average there will be one occurrence of 103 matches for each frame period T. The number of occurrences increases to 13 at 120 matches and decreases again to one occurrence of 137 matches. In view of Fig. 9 a minimum of about 35 levels are required to substantially display a complete image during one frame rather than the 241 levels as would generally be expected.

Of course F(D)<1 does not mean that this value of D will never occur. It just means that more than one frame period must elapse before that value of D is likely to occur. F(D)=0.1 or 0.01, for example, implies that, on the average, 10 or 100 frame periods must elapse before that value of D is likely to occur. The very steep, exponential fall-off of the normal distribution curve insures that the number of levels required to practically implement the addressing scheme of the present invention is not very much larger than the minimum number.

# Reduction of number of levels for special Swift matrices:

45

50

20

25

With some embodiments of the present invention it may be advantageous to reduce the number of voltage levels presented to column electrodes  $24_1$ - $24_M$  to the absolute minimum. This could be particularly important, for example, if column signals  $30_1$ - $30_M$  were generated by the output of an analog multiplexer which is switched between a plurality of fixed voltage levels based on a digital input.

Some Swift matrices have the special property that the total number of +1 elements in any column vector is either always an even number or always an odd number. For example, in the 240 row Swift matrix based on the 256 row Walsh matrix with the 16 lowest sequency waves removed, every column has an even number of +1 elements. This result is preserved if the Swift matrix is modified further by inverting an even number of rows. If an odd number of rows is inverted then the total number of +1 elements in every column would be an odd number.

The number of voltage levels required by column signals  $30_1-30_M$  can be cut in half from the usual number by employing these special Swift matrices and forcing the number of +1 elements in information vector  $I_i$  to be either always an even number or always an odd number. The number of levels is cut in half

because under these conditions the number of matches, D, between Swift column vector  $S_k$  and information column vector  $I_j$  is forced to be either always an even number or always an odd number between 0 and N, inclusive. The possible combinations of column parity, information parity and row parity with their resulting match parity and number of reduced levels are summarized below in Table 4.

| - |  |

|---|--|

| v |  |

|   |  |

10

15

20

45

| number of +1s<br>in Swift<br>column vector | number of +1s<br>in information<br>vector | number of<br>matrix rows<br>N | resulting<br>number of<br>matches<br>D | maximum<br>number<br>of<br>levels |

|--------------------------------------------|-------------------------------------------|-------------------------------|----------------------------------------|-----------------------------------|

| odd                                        | odd                                       | odd                           | odd                                    | (N+1)/2                           |

| odd                                        | odd                                       | even                          | even                                   | (N+2)/2                           |

| even                                       | even                                      | odd                           | odd                                    | (N+1)/2                           |

| even                                       | even                                      | even                          | even                                   | (N+2)/2                           |

| even                                       | odd                                       | odd                           | even                                   | N/2                               |

| even                                       | odd                                       | even                          | odd                                    | (N+1)/2                           |

| odd                                        | even                                      | odd                           | even                                   | N/2                               |

| odd                                        | even                                      | even                          | odd                                    | (N+1)/2                           |

25 Table 4

Of course a general information vector  $\mathbf{l_j}$  is just as likely to have an even number of +1s as an odd number of +1s. So in order to employ this level reduction scheme information vectors  $\mathbf{l_1}$ - $\mathbf{l_M}$  having the wrong parity must be changed to the right parity. One way to accomplish this would be to add an extra matrix row as a parity check and setting its corresponding column information elements to be either +1 or -1 to ensure the correct parity. The information pattern displayed on the last matrix row would necessarily be meaningless, but it could be masked off in order not to disturb the viewer. Or, alternatively, the last matrix row could be implemented as a "phantom" or "virtual" row which would exist electronically but not be connected to a real display row electrode.

Employing this level reduction scheme of the present invention to a 240 row display (N = 240, s = 8), for example, would reduce the minimum number of levels required from 35 to about 18.

Hardware Implementation and Description of Operation of the Present Invention

## A Preferred General Embodiment:

Referring now to Fig. 10, a block diagram of one embodiment for implementing the present invention is shown. Although the embodiments are discussed using Swift functions, it is to be understood that other functions may be used.

Display system 10 comprises display 12, a column signal generator 50, a storage means 52, a controller 54, and a row signal generator 56. A data bus 58 electrically connects controller 54 with storage means 52. Similarly, a second data bus 60 connects storage means 52 with column signal generator 50. Timing and control bus 62 connects controller 54 with storage means 52, column signal generator 50 and row signal generator 56. A bus 68 provides row signal information from row signal generator 56 to column signal generator 50. Bus 68 also electrically connects row signal generator 56 with display 12. Controller 54 receives video signals from an external source (not shown) via an external bus 70.

The video signals on bus 70 include both video display data and timing and control signals. The timing and control signals may include horizontal and vertical sync information. Upon receipt of video signals, controller 54 formats the display data and transmits the formatted data to storage means 52. Data is subsequently transmitted from storage means 52 to column signal generator 50 via bus 60.

Timing and control signals are exchanged between controller 54, storage means 52, row signal generator 56 and column signal generator 50 along bus 62.

Referring now to Fig. 11, the operation of display system 10 will be described in conjunction with the

embodiment shown in Fig. 10. Fig. 11 depicts a flowchart summary of the operating sequence or steps performed by the embodiment of Fig. 10.

As indicated at step 72, video data, timing and control information are received from the external video source by controller 54. Controller 54 accumulates a block of video data, formats the display data and transmits the formatted display data to storage means 52.

Storage means 52 comprises a first storage circuit 74 for accumulating the formatted display data transferred from controller 54 and a second storage circuit 76 that stores the display data for later use.

In response to control signals provided by controller 54, storage means 52 accumulates or stores the formatted display data (step 78) in storage circuit 74. Accumulating step 78 continues until display data corresponding to the N rows by M columns of pixels has been accumulated.

When an entire frame of display data has been accumulated, controller 54 generates a control signal that initiates transfer of data from storage circuit 74 to storage circuit 76 during transfer step 80.

At this point in the operation of display system 10, controller 54 initiates three operations that occur substantially in parallel. First, controller 54 begins accepting new video data (step 72) and accumulating a new frame of data (step 78) in storage circuit 74. Second, controller 54 initiates the process for converting the display data stored in storage circuit 76 into column signals 30<sub>1</sub>-30<sub>M</sub> having amplitudes

$$G_{I_1}(\Delta t_k) - G_{I_M}(\Delta t_k)$$

beginning at step 82. Third, controller 54 instructs row signal generator 56 to supply a Swift vector  $S(\Delta t_k)$  for time interval  $\Delta t_k$  to column signal generator 50 and to display 12. The third operation is referred to as the Swift function vector generation step 84 during which a Swift function vector  $S(\Delta t_k)$  is generated or otherwise selectively provided to column signal generator 50. Swift function vector  $S(\Delta t_k)$  is also provided directly to display 12.

As described above, N Swift functions  $S_i$  are provided by row signal generator 56, one Swift function for each row. The N Swift functions  $S_i$  are periodic in time and the period is divided into at least  $2^s$  time intervals,  $\Delta t_k$  (where k=1 to  $2^s$ ). Therefore, there are a total of N unique Swift functions  $S_i^i$ , one for each row 22 of display 12, with each divided into  $2^s$  time intervals  $\Delta t_k$ . A Swift function vector  $S(\Delta t_k)$  is comprised of all N Swift functions  $S_i^i$  at a specific time interval  $\Delta t_k$ . Because there are at least  $2^s$  time intervals  $\Delta t_k$ , there are at least  $2^s$  Swift function vectors  $S(\Delta t_k)$ . Swift function vectors  $S(\Delta t_k)$  are applied to rows 22 of display 12 by row signal generator 56 so that each element  $S_i^i$  of Swift function vectors  $S(\Delta t_k)$  is applied to the corresponding row  $22_i^i$  of display 12 at time interval  $\Delta t_k$ . Swift function vectors  $S(\Delta t_k)$  are also used by column signal generator 50 in generating column signals  $30_1^i - 30_M^i$  each having a corresponding amplitude

$$G_{I_1}(\Delta t_k)$$

through

40

45

50

55

20

$$G_{I_M}(\Delta t_k)$$

.

Display data stored in storage circuit 76 is provided to the column signal generator 50 at step 82. In this manner, an information vector  $\mathbf{l}_j$  is provided to column signal generator 50 such that each element  $\mathbf{l}_{ij}$  of information vector  $\mathbf{l}_j$  represents the display state of a corresponding pixel in the  $j^{th}$  column. An information vector  $\mathbf{l}_i$  is provided for each of the M columns of pixels of display 12.

During column signal generation step 86, each information vector  $I_j$  is combined with the Swift function vector  $S(\Delta t_k)$  to generate a column signal  $30_j$  for the  $j^{th}$  column during the  $k^{th}$  time interval. Column signals  $30_1$ - $30_M$ , each having amplitude

are generated for each of the M columns of display 12 for each time interval  $\Delta t_k$ . When the amplitude

$$G_{ij}^{(\Delta t_k)}$$

for all column signals  $30_1$ - $30_M$  is calculated for time interval  $\Delta t_k$ , all column signals  $30_1$ - $30_M$  are presented, in parallel, to column electrodes  $24_1$  -  $24_M$  during time interval  $\Delta t_k$  via bus 69. At the same time, the  $k^{th}$  Swift function vector  $S(\Delta t_k)$  is applied to row electrodes  $22_1$  -  $22_N$  of display 12 via bus 68 as indicated by step 88.

After column signals  $30_1$ - $30_M$  have been presented, the k+1 Swift vector  $S(\Delta t_{k+1})$  is selected and steps 82-88 are repeated as indicated by the "no" branch of decision step 89. When all  $2^s$  Swift function vectors  $S(\Delta t_k)$  have been combined with all information vectors  $I_1$ - $I_M$ , the "yes" branch of decision of step 89 instructs controller to return to step 80 and transfer the accumulated frame of information vectors  $I_1$ - $I_M$  to storage means 76 (step 80) and the entire process is repeated.

# Integrated Driver Embodiment:

Referring now to Fig. 12, another preferred embodiment of display system 10 is shown where storage means 52 (Fig. 10) is incorporated with column signal generator 50 in a circuit 90. Circuit 90 comprises a plurality of integrated driver integrated circuits (ICs) 91<sub>1</sub>-91<sub>4</sub>. Row signal generator 56 is shown as comprising a Swift function generator 96 and a plurality of row driver integrated circuits (ICs) 98<sub>1</sub>-98<sub>3</sub>. It should be apparent to one skilled in the art that the actual number of ICs 91<sub>1</sub>-91<sub>4</sub> and 98<sub>1</sub>-98<sub>3</sub> depends on the number of rows and columns of display 12.

Swift function generator 96 may include circuits, such as the circuit of Fig. 6, to generate Swift function vectors  $S(\Delta t_k)$  for each time interval  $\Delta t_k$ . Preferably, however, Swift function generator 96 comprises a read-only memory (ROM) having the Swift functions stored therein. Output bus 97 of Swift function generator 96 is connected to integrated driver ICs  $91_1$ - $91_4$  and to row driver ICs  $98_1$ - $98_3$ .

Row driver ICs  $98_1$ - $98_3$  are preferably similar to the integrated circuit having the part number HD66107T, available from Hitachi America Ltd. In Fig. 12, each row driver IC  $98_1$ - $98_3$  is capable of driving 160 rows of display 12. For the case of N = 480, three such row driver ICs  $98_1$ - $98_3$  are required. Row driver ICs  $98_1$ - $98_3$  are connected to row electrodes  $22_1$ - $22_N$  of display 12 in a known manner as indicated by electrical interconnections  $101_1$ - $101_3$ . Similarly, driver ICs  $91_1$ - $91_4$  are connected to column electrodes  $24_1$ - $24_M$  in a known manner as indicated by electrical interconnections  $104_1$ - $104_4$ .

As in the previous embodiment of Fig. 10, controller 54 receives video data and control signals via bus 70 from the external video source, formats the video data and provides timing control and control signals to integrated driver ICs  $91_1$ - $91_4$ , Swift function generator 96 and row driver ICs  $98_1$ - $98_3$ . Controller 54 is connected to integrated driver ICs  $91_1$ - $91_4$  by control bus 62 and formatted data bus 58. Controller 54 is also connected to row driver ICs  $98_1$ - $98_3$  and to Swift function generator 96 by control bus 62. Signals on control bus 62 causes Swift function generator 96 to provide the next sequentially following Swift function vector  $S(\Delta t_{k+1})$  to integrated driver ICs  $91_1$ - $91_4$  and to row driver ICs  $98_1$ - $98_3$ .

Operation of row driver IC 98<sub>1</sub> is now described in conjunction with Fig. 13. Although only row driver 98<sub>1</sub> is described, it is understood that row driver ICs 98<sub>1</sub>-98<sub>3</sub> operate in a similar manner.

Row driver IC  $98_1$  comprises an n-element shift register 110 electrically connected to an n-element latch 111 by bus 112. Latch 111 is in turn electrically connected to an n-element level shifter 113 by bus 114. Preferably, the n-element registers 110, latches 111, and level shifters 113 are large enough to accommodate all N rows of the display with one row driver IC, that is, n = N. However, a plurality of row driver ICs may be used so that the number of row driver ICs multiplied by n is at least N. In such case, a chip enable input is provided on control line 141 which allows multiple row driver ICs to be cascaded.

A Swift function vector  $S(\Delta t_k)$  is shifted into shift register 110, element by element, from Swift function generator 96 on output bus 97 in response to a clock signal from controller 54 on Swift function clock line 143. When a complete Swift function vector  $S(\Delta t_k)$  is shifted into shift register 110, the vector is transferred from the shift register 110 to latch 111 in response to a clock pulse provided by controller 54 on Swift function latch line 145. Clock line 143 and latch line 145, as is control line 141, are all elements of control bus 62.

The outputs of the n-element Swift function latch 111 are electrically connected to the corresponding inputs of an n-element level shifter 113, which translates the logical value of each element  $S_i(\Delta t_k)$  of the current Swift function vector  $S(\Delta t_k)$  into either a first or a second voltage level, depending on the logical value of  $S_i(\Delta t_k)$ . The resulting level-shifted Swift function vector, which now has values of either first or second voltages, is applied directly to the corresponding row electrodes  $22_1$  through  $22_n$  for the duration of

time interval  $\Delta t_k$  via electrical connections 101<sub>1</sub>.

35

45

The design and operation of integrated driver ICs 91<sub>1</sub>-91<sub>4</sub> is more easily understood with reference to Fig. 14 where integrated driver IC 91<sub>1</sub> is shown in greater detail. It is understood that integrated drivers 91<sub>2</sub>-91<sub>4</sub> operate in a similar manner.

Integrated driver IC  $91_1$  receives formatted data from controller 54 on data bus 58 and control and timing signals on control and clock lines 116, 118, 123, 128, 140 and 142. Control and clock lines 116, 118, 123, 128, 140 and 142 are elements of bus 62. The Swift function vector  $S(\Delta t_k)$  is received by IC  $91_1$  from Swift function generator 96 on output bus 97.

Shift register 115 is adapted to receive the formatted data when enabled by control line 116. The data is transferred into register 115 at a rate determined by the clock signal provided by controller 54 on clock line 118. In the preferred embodiment, register 115 is m bits in length, so that the number of integrated driver ICs  $91_1-91_4$  multiplied by m is at least M, the number of column electrodes  $24_1-24_M$  in display 12.

It should be understood that when register 115 is full with m bits (where m<M), the corresponding register 115 of integrated driver IC  $91_2$  is enabled to receive formatted data. Similarly, the remaining integrated driver ICs  $91_3$  and  $91_4$  are sequentially enabled and formatted data is directed into appropriate registers. In this manner, one row of formatted data comprising M bits of formatted data are transferred from controller 54 to integrated driver ICs  $91_1-91_4$ .

The contents of register 115 are then transferred to a plurality of N-element shift registers  $119_1-119_m$  via connections  $125_1-125_m$  in response to a write enable signal provided by controller 54 on control line 123. In the preferred embodiment, there are m shift registers in each integrated driver IC  $91_1-91_4$  so that the number of integrated driver ICs  $91_1-91_4$  multipled by m provides a shift register corresponding to each of the M columns of display 12.

When registers  $119_1$ - $119_m$  are full, each register  $119_1$ - $119_m$  contains an information vector  $I_j$  for the  $j_{th}$  column. Each bit  $I_{ij}$  of information vector  $I_j$  corresponds to the display state of the  $i^{th}$  pixel in the  $j^{th}$  column. Information vector  $I_j$  is then transferred to a corresponding latch  $124_1$ - $124_m$  via bus  $134_1$ - $134_m$ . One latch  $124_1$ - $124_m$  is provided for each of the m columns drivers  $119_1$ - $119_m$ . A latch enable signal on control line 128 initiates the transfer from registers  $119_1$ - $119_m$  to the corresponding latch  $124_1$ - $124_m$ . Latches  $124_1$ - $124_m$  have N inputs and N outputs and store information vectors  $I_1$ - $I_m$  (that is, one column of N bits for each column j) that represent the display states of the pixels 26 of the corresponding column of display 12 for one frame period T.

The N outputs of latches  $124_1$ - $124_m$  are electrically connected by busses  $135_1$ - $135_m$  to corresponding exclusive-or (XOR) sum generators  $130_1$ - $130_m$  at a first set of N inputs. Each XOR sum generator  $130_1$ - $130_m$  has a second set of N inputs connected to corresponding outputs of an N-element latch 136 by bus 139. Latch 136 provides the Swift function vector  $S(\Delta t_k)$  to each of the XOR sum generators  $130_1$ - $130_m$  to enable generation of column signals 30.

Latch 136 has N inputs electrically connected via bus 137 to an N-element shift register 138. Output bus 97 connects Swift function generator 96 (Fig. 12) to register 138. In response to a Swift function clock 140 provided by controller 54, a Swift function vector  $S(\Delta t_k)$  is sequentially clocked into register 138 via output bus 97 in a manner similar to that described above.

For each frame period, the first Swift function vector  $S(\Delta t_1)$  is transferred, in response to a clock signal on control line 142, to latch 136. Following the transfer to latch 136, the second Swift function vector  $S(\Delta t_2)$  is clocked into register 138 while the first Swift function vector  $S(\Delta t_1)$  is combined by XOR sum generators  $130_1-130_m$  with information vectors  $I_1-I_m$  in latches  $124_1-124_m$  to generate column signals  $30_1-30_M$  each having an amplitude

$$G_{I_j}(\Delta t_1)$$

.

Column signals  $30_1$ - $30_M$  are output on connections  $104_{11}$ - $104_{1m}$  during the time interval  $\Delta t_1$ . At the same time, the Swift function vector  $S(\Delta t_k)$  is output on electrical connections  $101_1$  - $101_3$ .

The process of transferring the Swift function vector  $S(\Delta t_k)$  to latch 136, clocking in the next Swift function vector  $S(\Delta t_{k+1})$  into register 138 and combining the Swift function vector  $S(\Delta t_k)$  with information vector  $I_j$  and outputting the resulting column signals  $30_1$ - $30_M$  to the column electrodes  $24_1$ - $24_M$  and outputting the corresponding Swift function vector  $S(\Delta t_k)$  to row electrodes  $22_1$ - $22_N$  continues until all Swift function vectors  $S(\Delta t_k)$  (i.e., until  $k=2^s$ ) have been combined with the current column information vectors  $I_1$ - $I_M$  held in latches  $124_1$ - $124_M$ . At this point, a new frame of information vectors  $I_1$ - $I_M$  is transferred from registers  $119_1$ - $119_M$  to latches  $124_1$ - $124_M$  and the process is repeated for the next frame period T+1.

## Exclusive-Or (XOR) Sum Generators:

25

55

There are various possible embodiments for implementing the XOR summation performed by XOR sum generators  $130_1$ - $130_m$ . A first embodiment is shown in Fig. 15. For the purpose of explanation, only one XOR sum generator  $130_1$ , will be discussed, it being understood that all m XOR sum generators  $130_2$ - $130_m$  operate in like manner.

The first set of inputs of XOR sum generator  $130_1$  electrically connect, via bus  $135_{11}$ - $135_{1N}$ , each output of latch  $124_1$  to a corresponding input of N two-input XOR logic gates  $144_1$ - $144_N$ . The second input of each XOR gate  $144_1$ - $144_N$  is electrically connected to a corresponding bit of latch 136 by bus  $139_1$ - $139_N$ .

The output of each XOR gate  $144_1$ - $144_N$  is connected to a corresponding input of a current source, designated  $146_1$ - $146_N$ . The outputs of current sources  $146_1$ - $146_N$  are connected in parallel at a common node 148. The single input of a current-to-voltage converter 150 is also connected to node 148.

Current sources  $146_1$ - $146_N$  are designed to provide either a first or second current output level depending on the combination of the inputs at each corresponding XOR gate  $146_1$ - $146_N$ . If the output of the corresponding XOR gate is logic low, the first current output level is provided to common node 148. Similarly, if the output is logic high, the second current output level is provided. In this manner, the magnitude of current at node 148 is the sum of the current levels generated by the N current sources  $146_1$ - $146_N$ . As discussed above, the magnitude of the current will depend on the number of matches D between the Swift vector  $S(\Delta t_k)$  and information vector  $I_l$ . Bus 145 routes power to each current source  $146_1$ - $146_N$ .

Converter 150 converts the total current level at node 148 to a proportional voltage output. The voltage output of converter 150 is the amplitude

of column signal 30<sub>i</sub> for the j<sup>th</sup> column of display 12 at output 157.

In a slightly different embodiment, an A/D converter 156 converts the analog voltage at output 157 to a digital value representative of column signal 30<sub>i</sub>. The output of A/D converter 156 is provided on output 154.

As noted above, there are various embodiments for implementing the XOR sum generators  $130_1$ - $130_m$  of Fig. 14. One such embodiment, shown in Fig. 16, eliminates the N current sources  $146_1$ - $146_N$  by using a digital summing circuit 152. A multi-bit digital word, which is the digital representation of the sum of the outputs of XOR gates  $144_1$ - $144_N$ , is output on bus 154. The digital representation is subsequently processed to generate column signal  $30_j$ . The width of digital word output by circuit 152 will depend on the number of rows in display 12 and the number of discrete voltage levels that will be needed to represent column signals  $30_1$ - $30_M$ .

The digital word provided on bus 154 may be subsequently processed by a digital-to-analog converter (DAC) 155 shown in Fig. 16. DAC 155 produces an analog voltage at its output 157 that is proportional to the value of the digital word on bus 154. This may be done with a conventional digital-to-analog converter, or by using an analog multiplexer to select from a plurality of voltages.

Another embodiment of XOR sum generator  $130_1-130_N$  is shown in Fig. 17. In this embodiment register 138 and latch 136 are eliminated as are the N current sources  $146_1-146_N$ . Register 115 receives formatted data from controller 54 and registers  $119_1-119_m$  are filled in the manner described for the embodiment of Fig. 14. However, when registers  $119_1-119_m$  are filled, the contents are transferred in parallel via busses  $134_1-134_m$  to a second set of N-element shift registers  $158_1-158_m$  in response to a shift register enable signal provided by controller 54 on control line 128. As before, registers  $119_1-119_m$  are available to be updated with the next frame of formatted data.

The output of each register  $158_1$ - $158_m$  is electrically connected to one input of a corresponding two-input XOR gate  $164_1$ - $164_m$ . The second input of each XOR gate  $164_1$ - $164_m$  are connected in parallel to output bus 97 of Swift function generator 96.