① Veröffentlichungsnummer: 0 541 855 A1

# **EUROPÄISCHE PATENTANMELDUNG**

(21) Anmeldenummer: 91119564.2

(51) Int. Cl.5: **G06E** 3/00

2 Anmeldetag: 15.11.91

(12)

43 Veröffentlichungstag der Anmeldung: 19.05.93 Patentblatt 93/20

84 Benannte Vertragsstaaten: AT BE CH DE FR GB IT LI NL SE 7) Anmelder: SIEMENS AKTIENGESELLSCHAFT Wittelsbacherplatz 2 W-8000 München 2(DE)

2 Erfinder: Gruhler, Ulrich Brudermühlstrasse 46a W-8000 München 70(DE) Erfinder: Osborne, Robert Kohlstrasse 2

W-8000 München 5(DE)

(S4) Codewort-detektion in einem seriell übertragenen optischen Signal.

(F) Im Rahmen der optischen Signalverarbeitung wird ein Korrelator vorgeschlagen, der ein vorgegebenes, in einem seriell übertragenen optischen Signal übertragenes Codewort erkennt, indem das optische Signal parallel einer Mehrzahl von Verzögerungsleitungen mit jeweils unterschiedlicher Verzögerungsdauer zugeführt wird und die von den Verzögerungsleitungen abgegebenen Signale jeweils für sich in elektrische Signale umgesetzt werden, deren Auswertung nur bei Übertragung des vorgegebenen Codewortes ein signifikantes Ausgangssignal bewirkt.

FIG 1

#### EP 0 541 855 A1

Zur leitungsgebundenen Nachrichtenübertragung in Kommunikationssystemen werden in zunehmendem Maße Glasfasern als Übertragungsmedium eingesetzt. Ein Vorteil der Glasfasern beruht auf der großen Bandbreite, die prinzipiell Übertragungsbitraten bis in den THz-Bereich ermöglicht. Bei hohen Übertragungsbitraten wird die optische Signalverarbeitung mit Vorteil angewendet.

Die Erfindung betrifft ein Verfahren und eine Schaltungsanordnung zur Durchführung eines Verfahrens zur Erkennung eines eine bestimmte Kombination von Bits aufweisenden Codewortes in einem seriell übertragenen optischen Signal, bei dem das optische Signal auf eine Mehrzahl von Verzögerungsleitungen mit jeweils unterschiedlicher Verzögerungsdauer aufgeteilt wird und bei dem die verzögerten Signale ausgewertet werden.

Aus IEEE LCS MAGAZINE, Mai 1990, Seiten 54 ... 67 ist ein Korrelator bekannt, bei dem ein seriell übertragenes optisches Signal auf eine Mehrzahl paralleler Verzögerungsleitungen mit jeweils unterschied – licher Verzögerungsdauer aufgeteilt wird. Die optischen Leistungen der von den Verzögerungsleitungen abgegebenen Signale werden summiert und einem Schwellwertentscheider zugeführt. Der Schwellwertent – scheider gibt bei Überschreitung eines vorgegebenen Schwellwertes seines Eingangssignals ein Aus – gangssignal ab und zeigt damit eine Autokorrelationsspitze des optischen Eingangssignals des Korrelators an

Dieser Korrelator bedarf, gemessen an der Anzahl der unterscheidbaren Codewörter, einer langen Code – wortlänge, um einen ausreichenden Amplitudenabstand der Autokorrelationsspitze von den durch Kreuz – korrelation bedingten Nebenmaxima zu erzielen, und darüber hinaus eines Schwellwertschalters mit einer hohen oberen Grenzfrequenz zur Erkennung der Autokorrelationsspitze.

Das gleiche gilt auch für eine aus Electronics Letters, November 1990, Vol. 26, Nr. 24, Seiten 1990...1992 bekannten optischen Sende – Empfangseinrichtung, bei der die zu übertragenen Daten senderseitig eine Mehrzahl von Verzögerungsleitungen mit jeweils unterschiedlicher Verzögerungsdauer parallel durchlaufen und empfangsseitig nach Durchlaufen von zu den senderseitigen gleichen Verzögerungsleitungen zu einem Summensignal zusammengefaßt werden. Das Summensignal, dem ein Synchronisationssignal hinzugefügt wird, wird einem Photodetektor zugeführt. Das Signal des Photodetektors wird einem Schwellwertentschei – der zugeführt, der bei Überschreiten eines Schwellwertes des zugeführten Signals ein Ausgangssignal abgibt.

Dieser Korrelator vermag gegenüber dem zuvor genannten Korrelator bei der gleichen relativ langen Codewortlänge eine größere Anzahl von Codewörtern zu unterscheiden, allerdings unter Hinnahme des Aufwands für die Synchronisation.

Der Erfindung liegt das Problem zugrunde, einen Korrelator anzugeben, der bei einer vorgegebenen Anzahl zu unterscheidender Codewörter eine gegenüber den bekannten Korrelatoren deutlich verringerte Codewortlänge benötigt.

Das Problem wird erfindungsgemäß bei einem Korrelator entsprechend dem Oberbegriff gelöst, indem die von den Verzögerungsleitungen abgegebenen optischen Signale jeweils für sich in elektrische Signale umgesetzt werden und die elektrischen Signale logisch verknüpft werden, wobei die logische Verknüpfung nur bei der Übertragung des vorgegebenen Codewortes zur Abgabe eines Ausgangssignal führt.

Die logische Verknüpfung der von den Verzögerungsleitungen abgegebenen inkohärenten Ausgangs – signale bringt neben einer Verkürzung der benötigten Codewortlänge und der damit einhergehenden Einsparung von Übertragungskapazität den Vorteil eines theoretisch unendlich großen Abstandes zwischen Autokorrelationsspitze und der Kreuzkorrelation mit sich, wobei ein entsprechend aufwandsarmer Schwell – wertschalter mit einer niedrigen oberen Grenzfrequenz genügt. Darüber hinaus vermag der erfindungsge – mäße Korrelator asynchron übertragene Codewörter zu erkennen.

Einer Weiterbildung der Erfindung zufolge werden die Bits beiderlei Pegellage des Codewortes ausgewer – tet. Diese Maßnahme bringt neben einer weiteren Verkürzung der notwendigen Codewortlänge den Vorteil der Sicherheit gegen fehlerbedingte Ausgangssignale aufgrund eines Dauersignals am Eingang des Korre – lators mit sich.

Die Erfindung wird nun als Ausführungsbeispiel anhand von Figuren in zum Verständnis erforderlichen Umfang beschrieben.

Dabei zeigt

55

5

10

35

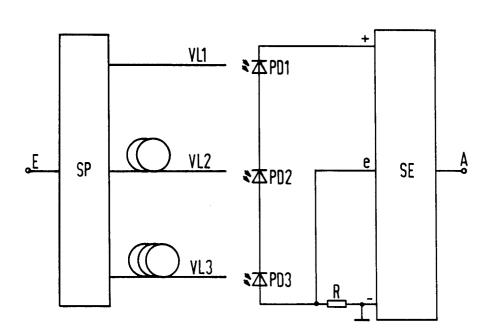

- Fig. 1 eine erfindungsgemäße Einrichtung zur Detektion der durch einen hohen optischen Pegel dargestellten Bits eines Codewortes.

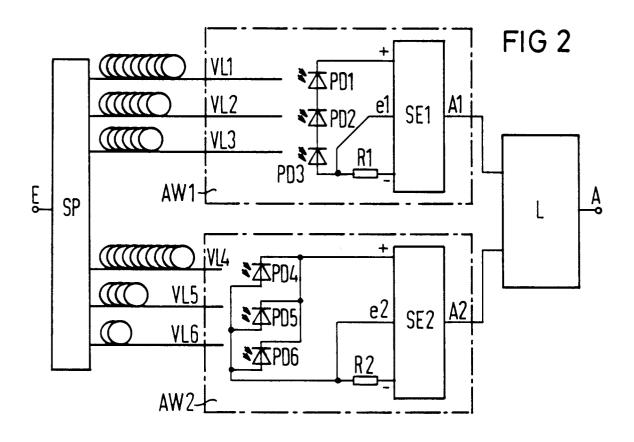

- Fig. 2 eine erfindungsgemäße Einrichtung zur Detektion der durch einen hohen und der durch einen niedrigeren optischen Pegel dargestellten Bits eines Codewortes.

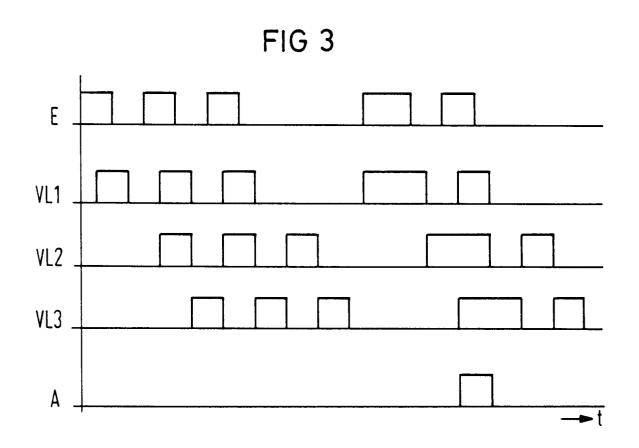

- Fig. 3 mögliche Signalzustände in einer Einrichtung nach Figur 1.

In Figur 1 ist ein Korrelator dargestellt, der die Rangfolge der in einem Codewort enthaltenen, durch einen hohen optischen Pegel dargestellten Bits ("1") auswertet. Über eine Eingangsleitung E, die durch eine

#### EP 0 541 855 A1

Glasfaser gegeben sein kann, werden einem optischen Verzweiger SP optische, seriell übertragene Binärsignale zugeführt, die Codewörter darstellen mögen. Die Codewörter mögen eine bestimmte Anzahl von Bits aufweisen. Die Binärsignale werden von dem Verzweiger einer Mehrzahl von Verzögerungsleitun gen VL1 ... VL3, die jeweils eine unterschiedliche Verzögerungsdauer aufweisen parallel zugeführt. Die Anzahl der Verzögerungsleitungen, die durch Glasfaserleitungen oder andere Lichtwellenleiterstrukturen gegeben sein können, gleicht der Anzahl der charakteristischen, durch einen hohen optischen Pegel dargestellten Bits des vorgegebenen Codewortes. Gegenüber der Verzögerungsleitung mit der geringsten Verzögerungsdauer (in Figur 1 VL1) weisen die anderen Verzögerungsleitungen (in Figur 1 VL2, VL3) jeweils eine um eine Bitübertragungszeitspanne oder ein ganzzahliges Mehrfaches davon erhöhte Verzö gerungsdauer auf. So möge Verzögerungsleitung VL2 gegenüber Verzögerungsleitung VL1 eine um zwei Bitübertragungszeitspannen erhöhte Verzögerungsdauer und Verzögerungsleitung VL3 gegenüber Verzö gerungsleitung VL1 eine um drei Bitübertragungszeitspannen erhöhte Verzögerungsdauer aufweisen. Das von den Verzögerungsleitungen an dem von dem Verzweiger abgewandten Ende abgegebene Signal wird jeweils einem durch eine Photodiode PD gegebenen opto - elektrischen Wandler zugeführt. Die Photodio den PD1 ... PD3 sind gleichsinnig in Reihe geschaltet. Der kathodenseitige Anschluß der Reihenschaltung ist mit der das hohe Potential (+) aufweisenden Klemme einer an ihren beiden Klemmen Gleichstrom liefernden Gleichspannungsquelle verbunden, und der anodenseitige Anschluß der Reihenschaltung ist über einen Widerstand R mit der das niedrige Potential (-) aufweisenden Klemme der Gleichspannungsquelle verbunden. Die in Sperrichtung spannungsbeaufschlagten Photodioden lassen jeweils keinen Stromfluß zu, wenn sie nicht belichtet werden. Werden sämtliche Photodioden der Reihenschaltung gleichzeitig belichtet, so fließt ein Strom vom hohen Potential über die Photodioden und den Widerstand zum niedrigen Potential, wobei der Stromfluß durch den Widerstand R einen Spannungsanstieg über dem Widerstand verursacht. Dieser Spannungsanstieg wird über eine Verbindung e einem Schwellwertentscheider SE zugeführt, der durch einen an sich bekannten Schwellwertschalter mit einer niedrigen oberen Grenzfrequenz gegeben sein kann. Der Schwellwertentscheider liefert also an seinem Ausgang A ein signifikantes Ausgangssignal, wenn sämtliche Photodioden der Reihenschaltung belichtet sind. Figur 3 verdeutlicht für zwei aufeinanderfolgende Binärsignalfolgen Signalzustände in der erfindungsgemä -

ßen Einrichtung nach Figur 1. Dabei stellt die zweite Binärsignalfolge das vorgegebene Codewort dar, bei dem die Einrichtung nach Figur 1 am Ausgang A ein signifikantes Ausgangssignal abgibt. Die erste Binärsignalfolge ist mit fünf Bits gebildet, wobei beginnend mit einem durch einen hohen Pegel dargestell ten Bit durch einen hohen Pegel dargestellte Bits mit durch einen niedrigen Pegel dargestellte Bits aufeinanderfolgen. Diese Binärsignalfolge ist in Figur 3, Zeile E am Zeilenanfang dargestellt und möge dem Eingang E der Einrichtung nach Figur 1 zugeführt werden. Dort wird die Binärsignalfolge über den Verzweiger SP sämtlichen Verzögerungsleitungen VL1 ... VL3 zugeführt. An dem dem Verzweiger abge wandten Ende der Verzögerungsleitung VL1 möge das Binärsignal wie in Zeile VL1, Figur 3 dargestellt um eine halbe Bitübertragungsdauer verzögert sein. Die Verzögerungsleitung VL2 möge, wie in Zeile VL2 dargestellt, gegenüber der Verzögerungsleitung VL1 eine um zwei Bitübertragungsdauern längere Verzö gerungsdauer und die Verzögerungsleitung VL3 möge, wie in Zeile VL3 dargestellt, gegenüber der Verzögerungsleitung VL1 eine um drei Bitübertragungsdauern längere Verzögerungsdauer aufweisen. Aus den Zeilen VL1 ... VL3 ist zu erkennen, daß die Verzögerungsleitungen VL1... VL3 bei der ersten Binärsignalfolge zu keinem Zeitpunkt gleichzeitig an ihrem Ende ein optisches Signal mit einem hohen Pegel abgeben, womit die Photodioden PD1 ...PD3 zu keinem Zeitpunkt gleichzeitig belichtet sind und damit durch die Reihenschaltung der Photodioden PD1 ... PD3 kein Strom fließt und damit am Ausgang A kein signifikantes Ausgangssignal auftritt (Figur 3, Zeile A, linke Zeilenhälfte). Die zweite Binärsignalfolge (Zeile E, rechte Zeilenhälfte), die vier Bits umfaßt beginnt mit zwei aufeinanderfolgenden durch einen hohen Pegel dargestellte Bits, denen eine durch eine niedrigen Pegel dargestelltes Bit folgt, worauf sich ein durch einen hohen Pegel dargestelltes Bit anschließt. Diese Binärsignalfolge wird im Eingang E der Einrichtung nach Figur 1 zugeführt und auf den Verzögerungsleitungen entsprechend verzögert. Bei dieser zweiten Binärsignalfolge treten am Ende der Verzögerungsleitungen der Einrichtung nach Figur 1 gleichzeitig optische Signale mit hohem Pegel auf, so daß die Photodioden PD1 ... PD3 gleichzeitig beleuchtet werden, wodurch durch die Reihenschaltung ein Strom fließt, der durch den Schwellwertentscheider detektiert wird und in ein signifikantes Ausgangssignal umgesetzt wird. (Figur 3, Zeile A, rechte Zeilenhälfte). Wird also die zweite Binärsignalfolge der Einrichtung nach Figur 1 zugeführt, so gibt die Einrichtung am Ausgang A ein signifikantes Ausgangssignal ab. Der beschriebene Korrelator prüft also, ob das Binärsignal die charakteri stischen, durch einen hohen Pegel dargestellten Bits in der entsprechenden Rangfolge des vorgegebenen Codewortes aufweist. Mit diesem Korrelator lassen sich bei einer Codewortlänge von N Bits und einer Anzahl Z von durch einen hohen Pegel dargestellten Bits je Codewort eine Anzahl

$$P = \frac{(N-1)!}{(N-Z)!(Z-1)!} = {N-1 \choose Z-1}$$

5

von Codewörtern darstellen.

Eine Weiterbildung dieses Korrelators für Codewörter mit einer weiter reduzierten Anzahl von Bits je Codewort und mit Immunität gegen fehlerbedingte Binärsignalfolgen mit durchgehender Folge von durch einen hohen Pegel dargestellten Bits ist in Figur 2 dargestellt. Dieser weitergebildete Korrelator wertet neben den durch einen hohen Pegel dargestellten Bits des vorgegebenen Codeworts auch die durch einen niedrigen Pegel dargestellten Bits des Codewortes aus. Figur 2 zeigt eine erfindungsgemäße Einrichtung, bei der in einer Auswerteeinrichtung AW1 die charakteristischen, durch einen hohen Pegeldargestellten Bits des vorgegebenen Codewortes und in einer Auswerteeinrichtung AW2 die charakteristischen, durch einen niedrigen Pegel dargestellten Bits des Codewortes ausgewertet werden. An dem Eingang E werden über eine Glasfaserleitung dem Verzweiger SP seriell übertragene, optische Binärsignale zugeführt. Von dem Verzweiger führt eine den charakteristischen, durch einen hohen Pegel dargestellten Bits eines vorgegebe nen Codewortes entsprechende Anzahl von Verzögerungsleitungen VL1 ... VL3 mit einer jeweils der Rangfolge in dem Codewort eines dieser Bits entsprechenden Verzögerungsdauer zu der Auswerteeinrich tung AW1. Die Auswerteeinrichtung AW1 gibt an ihrem Ausgang A1 nur dann ein signifikantes Ausgangs signal ab, wenn, wie bei dem weiter ober beschriebenen Korrelator, die entsprechend verzögerten, durch den hohen Pegel dargestellten Bits des vorgegebenen Codewortes gleichzeitig die Photodioden PD1 ... PD3 beleuchten. Weiter führt von dem Verzweiger VZ eine den charakteristischen, durch einen niedrigen Pegel dargestellten Bits des vorgegebenen Codewortes entsprechende Anzahl von Verzögerungsleitungen VL4 ... VL6 mit einer jeweils der Rangfolge in dem Codewort eines dieser Bits entsprechenden Verzögerungsdauer zu einer Auswerteeinrichtung AW2. Jede dieser Verzögerungsleitungen VL4...VL6 vermag an ihrem, dem Verzweiger SP abgewandten Ende jeweils eine Photodiode PD4..PD6 zu belichten. Die Photodioden PD4...PD6 der Auswerteeinrichtung AW2 sind gleichsinnig parallelgeschaltet. Die Parallelschaltung der Photodioden kann in einer alternativen Ausgestaltung durch einen optischen Summierer ersetzt werden, bei dem die von den Verzögerungsleitungen abgegebenen optischen Leistungen summiert und mittels einer einzigen Photodiode in ein elektrisches Signal umgesetzt werden. Zurückkommend auf die letzte Ausfüh rungsform bildet die Parallelschaltung der Photodioden mit dem Widerstand R2 eine Reihenschaltung. Die Reihenschaltung ist mit der Kathodenseite der Photodioden mit der das hohe Potential (+) aufweisenden Klemme einer an ihrer beiden Klemmen Gleichstrom liefernden Spannungsquelle verbunden. Widerstands seitig ist die Reihenschaltung mit der das niedrige Potential (-) aufweisenden Klemme der Gleichspan nungsquelle verbunden. Wird nun mindestens eine der Photodioden PD4 ... PD6 belichtet, so fließt ein Strom durch den Widerstand R2. Der Stromfluß durch den Widerstand R2 bewirkt einen Spannungsanstieg über dem Widerstand. Der Spannungsanstieg wird über einen Eingang e2 dem Schwellwertentscheider SE2, der durch einen Schwellwertschalter mit niedriger oberer Grenzfreguenz gegeben sein kann zugeführt. Der Schwellwertentscheider SE2 möge an seinem Ausgang A2 ein signifikantes Ausgangssignal abgeben, wenn an seinem Eingang e2 ein Spannungsanstieg vorliegt. Die Auswerteeinrichtung AW2 liefert also immer dann ein signifikantes Ausgangssignal an ihrem Ausgang A2, wenn eine der Photodioden PD4 ... PD6 belichtet wird. Die Verzögerungsleitungen VL1 ... VL6 sind in ihrer jeweiligen Verzögerungsdauer so untereinander abgestimmt, daß bei der Übertragung des vorgegebenen Codewortes am Eingang E die Verzögerungsleitungen, die zur Auswerteeinrichtung AW1 führen ausgangsseitig gleichzeitig ein optisches Signal mit hohem Pegel abgeben, während die Verzögerungsleitungen, die zur Auswerteeinrichtung AW2 führen im gleichen Zeitpunkt ein optisches Signal mit niedrigem Pegel liefern. Bei der Übertragung des vorgegebenen Codewortes liefert also die Auswerteeinrichtung AW1 an ihrem Ausgang A1 ein signifikantes Ausgangssignal, während die Auswerteeinrichtung AW2 an ihrem Ausgang A2 kein signifikantes Ausgangssignal liefert. Die Ausgänge A1 und A2 werden einer Logikschaltung L zugeführt, die bei Vorliegen der zuletzt genannten Signalkombination an den Eingängen A1 und A2 ein signifikantes Ausgangssignal an ihrem Ausgang A liefert. Der Korrelator liefert also dann ein signifikantes Ausgangssignal am Ausgang A, wenn das vorgegebene Codewort am Eingang E übertragen wird. Mit dem zuletzt beschriebenen Korrelator können bei einer Codelänge von N Bits 2<sup>N</sup> – 1 Codewörter erkannt werden.

55

#### EP 0 541 855 A1

#### Patentansprüche

5

10

15

20

25

30

40

45

50

55

1. Verfahren zur Erkennung eines eine bestimmte Kombination von Bits aufweisenden Codewortes in einem seriell übertragenen optischen Signal, bei dem das optische Signal auf eine Mehrzahl von Verzögerungsleitungen mit jeweils unterschiedlicher Verzögerungsdauer aufgeteilt wird und bei dem die verzögerten Signale ausgewertet werden,

#### dadurch gekennzeichnet,

daß die von den Verzögerungsleitungen abgegebenen optischen Signale jeweils für sich in elektrische Signale umgesetzt werden und die elektrischen Signale logisch verknüpft werden, wobei die logische Verknüpfung nur bei der Übertragung des vorgegebenen Codewortes zur Abgabe eines Ausgangssi – gnals führt.

2. Verfahren nach Anspruch 1,

#### dadurch gekennzeichnet,

daß für jedes charakteristische, durch einen hohen optischen Pegel dargestellte Bit des Codewortes eine Verzögerungsleitung mit einer der Rangfolge des betreffenden Bits entsprechenden Verzöge – rungsdauer vorgesehen ist und die derart verzögerten optischen Signale in entsprechende elektrische Signale umgesetzt werden und diese elektrischen Signale gemäß der logischen UND – Verknüpfung ausgewertet werden.

3. Verfahren nach einem der vorstehenden Ansprüche,

#### dadurch gekennzeichnet,

daß für charakteristische, durch einen niedrigen optischen Pegel dargestellte Bits des Codewortes jeweils eine Verzögerungsleitung mit einer der Rangfolge des jeweiligen Bits entsprechenden Verzögerungsdauer vorgesehen ist und die derart verzögerten optischen Signale in entsprechende elektrischen Signale umgesetzt werden und diese elektrischen Signale gemäß der logischen ODER-Verknüpfung ausgewertet werden.

4. Verfahren nach den Ansprüchen 2 oder 3,

## dadurch gekennzeichnet,

daß für charakteristische, durch einen niedrigen optischen Pegel dargestellte Bits des Codewortes jeweils eine Verzögerungsleitung mit einer der Rangfolge des jeweiligen Bits entsprechenden Verzögerungsdauer vorgesehen ist und die derart verzögerten optischen Signale optische summiert und in entsprechende elektrische Signale umgesetzt werden.

5. Verfahren nach den Ansprüchen 2 und 3.

#### dadurch gekennzeichnet,

daß nur bei gleichzeitigem Anliegen des signifikanten Ausgangssignals der UND – Verknüpfung und der ODER – Verknüpfung ein das Vorliegen des gewünschten Codewortes anzeigendes signifikantes Ge – samtausgangssignal abgegeben wird.

**6.** Schaltungsanordnung zur Durchführung des Verfahrens nach einem der Ansprüche 1 bis 5, **gekennzeichnet durch**,

die Umsetzung eines optischen Signals in ein elektrisches Signal durch eine in Sperrrichtung gepolte Photodiode, die mit dem von der jeweiligen Verzögerungsleitung abgegebenen optischen Signal beaufschlagt ist.

7. Schaltungsanordnung nach Anspruch 2 und Anspruch 6,

### dadurch gekennzeichnet,

daß die UND – Verknüpfung durch eine gleichsinnige Reihenschaltung von Photodioden und Auswer – tung des Stroms durch diese Reihenschaltung gegeben ist.

8. Schaltungsanordnung nach Anspruch 3 und 6,

### dadurch gekennzeichnet,

daß die ODER – Verknüpfung durch eine gleichsinnige Parallelschaltung von Photodioden und Aus – wertung des Stromes durch diese Parallelschaltung gegeben ist.

5

# EUROPÄISCHER RECHERCHENBERICHT

ΕP 91 11 9564

| Kategorie | Kennzeichnung des Dokuments mit z<br>der maßgeblichen Teil                                                                                                                                                                             |                                                               | Betrifft<br>Anspruch | KLASSIFIKATION DER<br>ANMELDUNG (Int. Cl.5)                     |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|----------------------|-----------------------------------------------------------------|

| Y<br>D,Y  | PROCEEDINGS OF THE ULTRASONIC (DENVER, OCT. 1897) Bd. 1, 1987, NEW YORK, IEEE Seiten 471 - 474; Y. MIYAZAKI: 'Integrated Opti Processors Consisting of Col' Switches' * Seite 473 - Seite 474; Abbi ELECTRONICS LETTERS.               | cal Signal<br>linear Acousto-Optic                            | 1,3,8                | G06E3/00                                                        |

| U, Y      | Bd. 26, Nr. 24, 22. November Seiten 1990 - 1992; W. KWONG ET AL.: 'Synchronous for Fibre-Optic Networks with Processing' * das ganze Dokument *                                                                                        | CDMA Demonstration                                            | 1,3,8                |                                                                 |

| D, А      | IEEE LCS - THE MAZINE OF LIGHTSYSTEMS  Bd. 1, Nr. 2, Mai 1990, NEW Y Seiten 54 - 67; P. PRUCNAL ET AL: 'Optically- for Fast Packet Switching' * Seite 57 - Seite 60; Abbild WO-A-8 101 927 (COMMONWEALTH INDUSTRIAL RESEARCH ORGANISAT | ORK, IEEE  Processed Routing ungen 6,7,10,16 * SCIENTIFIC AND | 1                    | RECHERCHIERTE<br>SACHGEBIETE (Int. Cl.5<br>G06E<br>G06F<br>H03K |

|           | * Zusammenfassung; Abbildunge                                                                                                                                                                                                          | -                                                             |                      |                                                                 |

| Der vo    | Prliegende Recherchenbericht wurde für alle<br>Recherchenort                                                                                                                                                                           | e Patentansprüche erstellt Abschlußdatum der Recherche        |                      | Prifer                                                          |

|           |                                                                                                                                                                                                                                        | 02 JULI 1992                                                  | SAAM                 | C.                                                              |

- X: von besonderer Bedeutung allein betrachtet

Y: von besonderer Bedeutung in Verbindung mit einer anderen Veröffentlichung derselben Kategorie

A: technologischer Hintergrund

O: nichtschriftliche Offenbarung

P: Zwischenliteratur

- i : alteres Patentdokument, das jedoch erst am oder Gri

E : älteres Patentdokument, das jedoch erst am oder

nach dem Anmeldedatum veröffentlicht worden ist

D : in der Anmeldung angeführtes Dokument

L : aus andern Gründen angeführtes Dokument

- & : Mitglied der gleichen Patentfamilie, übereinstimmendes Dokument