① Veröffentlichungsnummer: 0 599 072 A2

## EUROPÄISCHE PATENTANMELDUNG

(21) Anmeldenummer: **93117432.0**

(51) Int. Cl.5: H03M 1/66

22 Anmeldetag: 27.10.93

(12)

30 Priorität: 20.11.92 DE 4239140

(43) Veröffentlichungstag der Anmeldung: 01.06.94 Patentblatt 94/22

Benannte Vertragsstaaten:

ES FR GB IT

71 Anmelder: SIEMENS AKTIENGESELLSCHAFT Wittelsbacherplatz 2 D-80333 München(DE)

Erfinder: Feldtkeller, Martin, Dipl.-Ing.

Ouagliostrasse 14

D-81543 München(DE)

- (54) Integrierbare Schaltungsanordnung zum Abgleich eines Steuersignals.

- © Die Schaltungsanordnung weist Zener-Zap-Dioden auf, mittels derer das digitale Ansteuerwort eines Digital-Analog-Wandlers programmierbar ist. Das so erzeugte Ausgangssignal dient zum Abgleich eines Steuersignals der integrierten Schaltung.

10

15

25

30

35

40

50

55

Die Erfindung betrifft eine integrierbare Schaltungsanordnung zum Abgleich eines Steuersignals gemäß dem Oberbegriff des Anspruchs 1.

In vielen integrierten Schaltungen werden heutzutage Steuersignale bzw. Steuergrößen erzeugt bzw. weiterverarbeitet, welche innerhalb eines oftmals relativ kleinen Toleranzbereichs liegen müssen. Durch Fertigungsschwankungen können diese Toleranzbereiche oftmals nicht eingehalten werden. In bipolaren Schaltungen wird zum Ausgleich von Fertigungsschwankungen heute vielfach der sogenannte Zener-Zap-Abgleich verwendet. Dabei werden in der Schaltung eingebaute Zenerdioden bei der Scheibenmessung gezielt durchlegiert, um z.B. eine Bandgap-Referenz abzugleichen.

Die Zenerdioden sind zumeist so angeordnet, daß einem abzugleichenden Widerstand ein zweiter parallel geschaltet werden kann. Muß aufgrund der Fertigungsschwankung dem abzugleichenden Widerstand ein zweiter parallel geschaltet werden, so wird die Zener-Zap-Diode mit einem so hohen Strom beaufschlagt, daß diese durchbrennt und ein Kurzschluß entsteht. Dadurch wird die Parallelschaltung der Widerstände festgelegt. Mittels Zener-Zap-Abgleich können in erster Linie Widerstandsverhältnisse variiert werden.

Oftmals ist es jedoch notwendig auch andere Größen als die Widerstandsverhältnisse zu variieren.

Aufgabe der vorliegenden Erfindung ist es daher, eine integrierbare Schaltungsanordnung anzugeben, die einen flexiblen Ausgleich von Fertigungsschwankungen bei der Herstellung von integrierten Schaltungen erlaubt.

Diese Aufgabe wird durch die kennzeichnenden Merkmale des Anspruchs 1 gelöst. Weiterbildungen sind Kennzeichen der Unteransprüche.

Vorteil der vorliegenden Erfindung ist, daß die Schaltungsanordnung sowohl eine Referenzspannung, oder einen Referenzstrom oder einen spannungsgesteuerten Widerstand etc. verändern kann, wodurch die verschiedensten Einflüsse von Fertigungsstreuungen ausgeglichen werden können.

Ein weiterer Vorteil ist, daß durch die Verwendung eines Digital-Analog-Wandlersnur mit Hilfe eines Inverters, sowohl positive wie negative Ausgleichsgrößen erzeugt werden können.

Die Erfindung wird nachfolgend anhand von zwei Figuren näher erläutert. Es zeigen

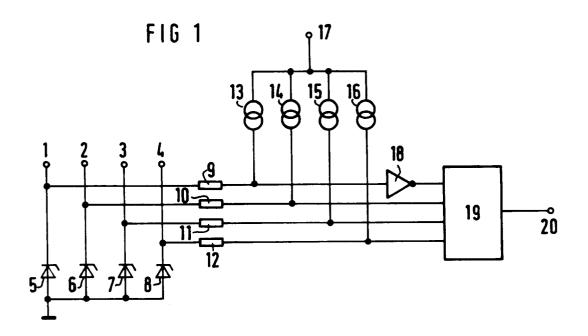

Figur 1 eine Ausführungsform der erfindungsgemäßen Schaltungsanordnung,

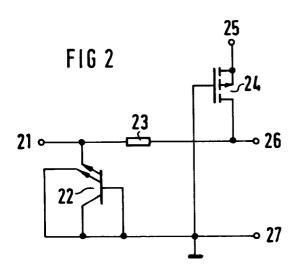

Figur 2 eine Ausführungsform für eine Zener-Zap-Diode sowie einer nachgeschalteten "pull-up"- Stromquelle.

In Figur 1 sind vier Mittel dargestellt, die von einem hochohmigen in einen niederohmigen Zustand programmierbar sind. Diese sind als vier in Sperrichtung geschaltete Dioden 5, 6, 7, 8, die zwischen je einer Eingangsklemme 1, 2, 3, 4 und Masse geschaltet sind, dargestellt. Jede Eingangsklemme 1, 2, 3, 4 ist mit jeweils einem Entkopplungswiderstand 9, 10, 11, 12 verbunden. Der jeweils andere Anschluß jedes Entkopplungswiderstands 9, 10, 11, 12 ist über jeweils eine Stromquelle 13, 14, 15, 16 mit einer Versorgungsspannungsklemme 17 verbunden. Der erste Entkopplungswiderstand 9 ist weiterhin über einen Inverter 18 mit dem ersten Eingang eines Digital-Analog-Wandlers 19 verbunden. Die jeweils zweiten Anschlüsse der Entkopplungswiderstände 10, 11, 12 sind mit den übrigen Eingängen des Digital-Analog-Wandlers 19 verschaltet. Am Analog-Ausgang des Digital-Analog-Wandlers 19 ist die erzeugte Steuergröße abgreifbar.

Im nicht programmierten Zustand sind die Dioden 5, 6, 7, 8 hochohmig, wodurch die Eingänge des Digital-Analog-Wandlers 19 durch die Stromquellen 13, 14, 15, 16 mit einem High-Pegel beaufschlagt werden. Im dargestellten Beispiel wird lediglich der über die Eingangsklemme 1 ansteuerbare Eingang durch das Vorschalten des Inverters 18 mit einem Low-Pegel beaufschlagt. Dieser Eingang stellt den sogenannten MSB (Most Significant Bit) dar. Im dargestellten Beispiel wird dieser Eingang als Vorzeichensteuereingang benutzt. Somit können sowohl positive wie negative Werte erzeugt werden. Ist dies nicht gewünscht, so kann der Inverter auch weggelassen werden. Dadurch stände ein zusätzlicher Eingang zur Verfügung und die Auflösung im jeweiligen positiven oder negativen Bereich wird erhöht.

Nach Fertigstellung der integrierten Schaltung kann noch auf der Scheibe mittels probeweisem Kurzschließen, d.h. durch Verbinden der jeweiligen Eingänge 1, 2, 3, 4 mit Masse die gewünschte Ausgleichsgröße definiert werden. Mittels der dargestellten vier Eingänge wären z.B. 16 verschiedene Ausgleichsgrößen möglich. Wurde die richtige Größe festgestellt, so können die Kurzschlüsse fest programmiert werden. Dies erfolgt z.B. durch Durchbrennen der jeweiligen Zenerdioden 5, 6, 7, 8. Durch den jeweils entstandenen Kurzschluß werden die entsprechenden Eingänge des Digital-Analog-Wandlers 19 auf einen Low-Pegel heruntergezogen und somit das digitale Ansteuerwort für den Digital-Analog-Wandler festgelegt.

Selbstverständlich sind auch andere Mittel zum Programmieren denkbar. So könnte beispielsweise in einer negativen Logik anstelle der Zenerdioden 5, 6, 7, 8 Kurzschlüsse vorgesehen sein, welche beispielsweise mittels eines Lasers auftrennbar wären. Selbstverständlich müßten diese Kurzschlüsse ebenfalls durch Dioden voneinander logisch getrennt werden. Die Lösung mittels Zener-Zap-Dioden stellt deshalb die einfachste Realisierung dar.

5

15

20

25

Figur 2 stellt eine Realisierung einer der Dioden 5, 6, 7, 8 aus Figur 1 sowie der jeweils zugehörigen Stromquelle 13, 14, 15, 6 aus Figur 1 dar. In Figur 2 ist eine der Eingangsklemmen 1, 2, 3, 4 aus Figur 1 mit 21 bezeichnet. Die Diode aus Figur 1 ist durch den bipolaren Transistor 22 dargestellt. Dieser weist zwei Emitteranschlüsse auf. Der erste Emitteranschluß ist mit der Eingangsklemme 21 und der zweite Emitteranschluß ist sowohl mit dem Kollektor wie auch mit der Basis des Transistors 22 und mit Masse verbunden. Die Eingangsklemme 21 ist über einen Widerstand 23 mit einer Ausgangsklemme 26 verschaltet. Diese Ausgangsklemme kann mit einem der Eingänge des Digital-Analog-Wandlers verbunden werden. Die Ausgangsklemme 26 ist weiterhin über die Laststrecke eines p-Kanal-Feldeffekttransistors 24 mit einer Versorgungsspannungsklemme 25 verbunden. Der Gateanschluß des Feldeffekttransistors 24 ist mit Masse und mit einer Ausgangsklemme 27 verschaltet. Die in Figur 2 dargestellte Realisierung der Zener-Zap-Diode sowie der "pull-up" Stromquelle bietet sich vor allem für Analog-Schaltungen in Mischtechnologien an.

## Patentansprüche

1. Integrierbare Schaltungsanordnung zum Abgleich eines Steuersignals mit einer Vielzahl von Mitteln, die zwischen einer Vielzahl von Eingängen und einem Bezugspotential geschaltet sind und die von einem hochohmigen in einen niederohmigen Zustand bzw. umgekehrt programmierbar sind,

dadurch gekennzeichnet, daß die Vielzahl von Eingängen über jeweils zugeordnete Entkoppelwiderstände mit den Digitaleingängen eines Digital-Analog-Wandlers verbunden sind und die Digital-Eingänge über jeweils ein zugeordnetes Mittel zur Potentialverschiebung mit einer Versorgungsspannungsklemme verbunden ist und daß das Ausgangssignal des Digital-Analog-Wandlers zum Abgleich des Steuersignals dient.

- 2. Integrierbare Schaltungsanordnung nach An

- dadurch gekennzeichnet, daß die programmierbaren Mittel eine Zener-Zap-Diode, welche in Sperrichtung geschaltet ist, aufweisen.

- 3. Integrierbare Schaltungsanordnung nach Anspruch 1,

dadurch gekennzeichnet, daß die programmierbaren Mittel eine auftrennbare Verbindung aufweisen.

- 4. Integrierbare Schaltungsanordnung nach einem der vorhergehenden Ansprüche, dadurch gekennzeichnet, daß die Mittel zur Potentialverschiebung eine "pull-up" Stromquelle aufweisen.

- Integrierbare Schaltungsanordnung nach Anspruch 4. dadurch gekennzeichnet, daß die "pull-up" Stromguelle ein Feldeffekttransistor ist, dessen Laststrecke zwischen Versorgungsspannungsklemme und Eingang des Digital-Analog-Wandlers geschaltet ist, und dessen Steueranschluß mit Masse verbunden ist.

- 6. Integrierbare Schaltungsanordnung nach Anspruch 5 in Verbindung mit Anspruch 2, dadurch gekennzeichnet, daß die Zener-Zap-Diode durch einen bipolaren Transistor gebildet wird.

- 7. Integrierbare Schaltungsanordnung nach einem der vorgehenden Ansprüche, dadurch gekennzeichnet, daß vor dem MSB-Eingang des Digital-Analog-Wandlers ein Inverter geschaltet ist.

3

45

50

55