(1) Publication number: 0 600 751 A2

(12)

# **EUROPEAN PATENT APPLICATION**

(21) Application number: 93309730.5

(22) Date of filing: 03.12.93

61 Int. CI.<sup>5</sup>: **H02H 3/093**, H03K 17/16,

H03K 17/08

(30) Priority: 04.12.92 US 985406

04.12.92 US 985411 03.06.93 US 72193

(43) Date of publication of application : 08.06.94 Bulletin 94/23

Ø Designated Contracting States : DE FR GB IT NL

71 Applicant: TEXAS INSTRUMENTS INCORPORATED

13500 North Central Expressway Dallas Texas 75265 (US)

72 Inventor : LeComte, Norman E, 58 Donald Potter Road West Greenwich, RI 02817 (US) Inventor: Maher, Thomas R. 73 Messenger Street,

Apt. 136

Plainville, MA 02762 (US) Inventor: Kawate, Keith W.

12 Virginia Street

Attleboro Falls, MA 02763 (US) Inventor: Nott, Sepideh H.

1170 Wilson Road

Unit No.17, Fall River, MA 02720 (US)

Inventor: Larson, Eric K. 42 King Philip Road Narragansett, RI 02882 (US)

(4) Representative : Abbott, David John et al Abel & Imray Northumberland House 303-306 High Holborn London, WC1V 7LH (GB)

(54) Solid state power controller.

A solid state power controller for switching power on and off to an electrical load which also serves as a circuit protection device protecting the load and/or the wire connected between the load output terminal of the controller and ground from thermal damage due to current overload is shown. When a current overload exists the controller interrupts current to the load in a time inversely proportional to the square of the magnitude of the overload as shown in a trip time vs. load current curve (Fig 4). The controller also limits the load current to a selected maximum level by controlling the drain-source resistance of power MOSFETs (PS1-7) used for switching the power. A secondary interrupt is provided in the event that the junction temperature of the MOSFETs has risen a selected maximum level. A thermal memory feature is included for both interrupt signals. The controller is controlled by a single on/off input line (COMMAND) and provides both a status (STATUS) and trip (TRIP) output line to indicate its state. The status can be configured to monitor load voltage or load current flow as desired. The controller also can be configured to default to either an on or off state in the event the input line is disconnected. The controller is made so that it is externally programmable by providing selected external connection points (MPA, DTA, CLA1, CLA2) and choosing values of certain components (Rd1i, Rd2i, Rii, Cii, Rmpi, C<sub>mpi</sub>) contained within the sealed controller package which results in selected default condition.

## Background of the Invention

5

15

30

35

45

50

Application Serial Nos. 985,411 and 985,406 filed December 4, 1992 assigned to the same assignee as the instant invention relate to a power controller which serves as the basis for the present invention.

This invention relates generally to a solid state circuit controller and more specifically to a solid state circuit controller for switching power to a load and for protecting the switch from damage due to power dissipation.

The controller has utility in many applications, such as, by way of example, in aircraft power distribution systems. Traditionally, such systems have been controlled with electromechanical circuit breakers incorporating a bimetallic element to sense the resistive heating of wire due to current flow. A key inherent quality of the bimetallic sensor is known as "thermal memory". The bimetal stores and dissipates the heat energy in the same manner as the wire and reduces circuit breaker trip time when the wire temperatures remain elevated from a previous overload condition. This protects the wire when exposed to multiple overloads or preload conditions by maintaining the heat energy below the threshold for wire damage as set forth in MS3320 trip time vs. load current curve standard. Such circuit breakers also allow momentary high inrush currents such as motor loads and lamp loads without nuisance tripping. For example, inrush currents of four to fifteen times nominal rating, some lasting several seconds, are typical of motors, power supplies and incandescent filaments.

Advances in solid state and computer technology now offer the potential for fully automatic control resulting in reduced flight crew overload, enhanced maintainability and reliability as well as significant weight savings. One approach in providing such a control is shown and described in U.S. Patent No. 4,866,559 assigned to the assignee of the present invention. In that control an electrothermal sensor is used as a current sensing element. The I²RC power dissipation within a resistive beam of the current sensing element provides a measurable temperature gradient across its surface as a function of current flow and time. An electronic circuit responds to a maximum temperature difference between the center and the edge of the beam resulting in a trip time vs. load current trip characteristic similar to the traditional electromechanical, thermal circuit breakers.

While this approach is effective, the space required for the electromechanical sensor is greater than desirable and the fabrication process employed to maintain the required optimum performance relative to temperature is costly.

It therefore an object of the present invention to provide an improved solid state power controller which includes the performance characteristics of traditional thermal circuit breakers which overcomes the above noted problems of the prior art. Another object is the provision of a solid state power controller having improved accuracy as well as one which is compatible with hybrid manufacturing practices and which is conducive for use with computer control systems. Yet another object is the provision of a solid state power controller which is easily adaptable to a wide variety of applications such as different time current curves, load current curves and the like. Another object is the provision of a solid state controller which can be used for switching high voltage DC.

It is another object of the present invention to provide protection of solid state switches used in such power controllers, such as MOSFETs, from thermal damage due to power dissipation. Another object is the provision of controller apparatus to protect solid state power switches used to limit current flow therethrough, as well as to switch high voltage DC, from thermal damage from power dissipated in the switches.

Yet another object of the present invention to provide in-situ, external programmability of a solid state controller in order to allow adjustment of certain features including current overload protection, MOSFET thermal protection and current limit as desired for different applications.

Various other objects and advantages will appear from the following description of an embodiment of the invention and the novel features will be particularly pointed out hereinafter in connection with the accompanying drawings and the appended claims.

# Summary of the Invention

Briefly, in accordance with the present invention, there is provided a controller comprising two integrated circuits referred to as a Supply ASIC and a Control ASIC along with various discrete external components including resistors, capacitors, a transformer, zener diodes, MOSFETS and the like.

The Supply ASIC comprises a Current Sources section, a Logic With Isolation section and an Oscillator section.

The Logic With Isolation section provides an interface between the external controller and the Control ASIC circuitry and has a COMMAND input and STATUS and TRIP output stages fully TTL compatible. In accordance with the invention, the input COMMAND signal controls the on/off and trip reset functions. According to a feature of the invention in the event the external COMMAND signal is removed as by being open circuited due to harness wire breakage, a default COMMAND high (controller on) or low (controller off) condition can

be set by connecting the COMMAND input to a normally closed pin or a normally open pin respectively. The output STATUS signal reflects whether or not a selected load current or load voltage status exists while an output TRIP signal reflects whether or not a trip condition has occurred. According to a feature of the invention, a trip condition can be caused by either an I<sup>2</sup>RC circuit or a MOSFET Protection circuit, to be discussed below.

The Current Sources section provides temperature stable current sources for the Supply ASIC Logic with Isolation section and the Oscillator section. Bias currents are set by an external resistor.

5

15

55

The Oscillator section produces a drive signal for a transformer which in turn is used to power the isolated Control ASIC circuitry. The oscillator is made up of a modified emitter coupled oscillator with high speed comparator outputs. Frequency of the oscillator is set by an externally mounted resistor and capacitor.

In accordance with the invention, the Control ASIC comprises a MOSFET Drive and Current Limiting section, a MOSFET Protection section, and I<sup>2</sup>RC section, a Logic section, a Status section, a Band Gap Current/Voltage Reference section, an Opto-Isolator Drive section and a Power-Up-Reset section.

The MOSFET Drive and Current Limiting section turns MOSFETs on and off by controlling MOSFET gate-source voltage. Additionally, according to a feature of the invention, this section limits current flow through the MOSFETs to a predetermined level by decreasing and increasing the MOSFETs on resistance through increasing and decreasing the gate-source voltage, respectively. External calibration of the current limit level is effected by trimming a pair of externally mounted resistors. The controller preferably employs N-channel MOSFETs since they have lower on-resistance than comparable sized P-channel MOSFETs.

The MOSFET Protection section produces an analog voltage proportional to the MOSFET temperature rise and provides a trip signal when the allowable temperature rise of the MOSFETs, simulated by a reference voltage, is reached in order to protect the MOSFETs from thermal damage caused by high power dissipation during current limiting. In accordance with a feature of the invention, the MOSFET Protection section includes thermal memory.

According to the invention, a current is generated proportional to the voltage drop across the MOSFET which is converted to a first electrical signal proportional to the power dissipated in the MOSFET. This signal is integrated as a function of time providing a second signal proportional to the temperature rise of the junction of the MOSFET and a trip signal is generated when the preselected allowable temperature rise of the junction has been reached.

The I²RC section produces an analog voltage proportional to the wire temperature rise or equivalently energy stored in the wire and produces a trip signal when the maximum temperature rise of the wire, simulated by a reference voltage, is reached. The section comprises a linear circuit which measures the current flow through the wire, calculates its heating impact on the wire and provides a signal to trip the controller when the wire temperature has risen a selected amount as defined by a selected curve set such as one derived from the MS3320 trip time vs. load current curves. The circuit reads the current in the wire as a voltage signal across a shunt resistor serially connected to the wire, the signal is scaled and converted to a current by an amplifier stage, then squared with the resultant applied to an RC network. The output voltage from the RC network is monitored by a comparator which has a threshold set by the referenced voltage according to the energy equation. When the output voltage of the RC network reaches the threshold level, the comparator output transitions to an opposite state signaling the Logic section of a trip condition in order to interrupt current flow within the wire by turning off the MOSFETs. In accordance with a feature of the invention, the I²RC section includes thermal memory.

The Logic section produces internal control signals for the MOSFET Drive and Current Limiting section, MOSFET Protection section and Opto-isolator Drive section based on COMMAND input and trip signals from the I²RC section and MOSFET Protection section. In accordance with a feature of the invention, this section also contains a trip latch to hold a trip condition until a reset is applied by the COMMAND input signal. The trip latch contains a set and reset delay to prevent false tripping and resetting from induced voltage or current spikes. The delay can be adjusted by an externally mounted capacitor.

The Status section provides a signal indicating whether the voltage at the LOAD terminal, if the voltage status is chosen, or the load current, if the current status is chosen, exceeds predetermined levels. Hysteresis is employed with both voltage and current status thresholds to enhance noise immunity. The voltage status thresholds with hysteresis are set by an external resistor whereas the current status thresholds with hysteresis are internally set.

The Band Gap Current/Voltage Reference section provides a temperature stable voltage reference and current sources to operate the other sections of the Control ASIC circuitry. This section also provides current sources whose values are ratioed to internal ASIC resistors. The ratioed resistor current sources are used to establish temperature stable voltages, other than the voltage reference, within the sections of the Control ASIC. The voltage reference and current sources are established through the use of an inherently temperature stable "band gap voltage" reference. Band Gap current source values are set by an external resistor. The band

gap voltage reference is also used to establish a supply voltage of approximately 7.5 V used by other sections of the ASIC.

The Opto-Isolator Drive section provides the drive signal for opto-isolator photo diodes to transmit status and trip indications to the Supply ASIC. To turn a photo diode on, indicating a status or trip condition, the circuit diverts the 7.5 V supply current through an opto-isolator photo diode.

The Power-Up-Reset section sets the functional sections of the control circuitry to a predetermined state such as MSOFETS off, trip latch reset, trip and status opto-isolator off, MOSFET protection disabled and the like until there is sufficient supply voltage to operate the Control ASIC.

In accordance with the present invention, selected features of the controller are made externally programmable to facilitate customizing the controller in-situ for a particular application. These features include the I²RC circuit, the Current Limit circuit and the MOSFET Protection circuit by calibrating the features to a default level and by adding lines extending out of the sealed package containing the controller to external connecting points. The operation of the I²RC circuit is set by certain components disposed off the integrated circuits (ICs) comprising the controller circuitry including a resistor  $R_i$  and capacitor  $C_i$  used to set the shape of the trip time vs. load current curve where resistor  $R_i$  is used to set the ultimate trip level and  $R_i$  and  $C_i$  together determine the time constant. According to a feature of the invention,  $R_i$  and  $C_i$  are segmented into  $R_{ii}$ ,  $C_{ii}$  (disposed internally in the package) and  $R_{ie}$ ,  $C_{ie}$  (disposed externally outside the package).  $R_{ie}$  and  $C_{ie}$  are connected in parallel to  $R_{ii}$  and  $C_{ii}$ . The internal, off-IC components  $R_{ii}$  and  $C_{ii}$  are selected to provide default values and to fix the lower limits or programmability.

According to another feature of the invention, the current level is also externally programmable. The current limit level is affected by off-IC resistors  $R_{\rm s}$ ,  $R_{\rm cl1}$  and  $R_{\rm cl2}$  Resistor  $R_{\rm cl1}$  is segmented into two parallel resistors with  $R_{\rm cl1}$  disposed within the package and  $R_{\rm cl1e}$  disposed outside the package between external connection points on current paths extending out of the sealed package. The value of resistors  $R_{\rm cl1i}$  and  $R_{\rm cl2}$  selected to a default level, the lowest current limit value in the desired range. Placing external resistor  $R_{\rm cl1e}$  in parallel with internal resistor  $R_{\rm cl1i}$  will result in a lower effective  $R_{\rm cl1}$  value and increase the value the current limit level.

According to another feature of the invention, the MOSFET Protection circuit is externally programmable in a manner similar to the I²RC circuit. Operation of the MOSFET Protection circuit is set by off-IC components, resistors  $R_{mv}$ ,  $R_{mp}$  and capacitor  $C_{mp}$ . Components  $R_{mp}$  and  $C_{mp}$  are used to set the shape of the trip time vs. LINE to LOAD voltage with resistor  $R_{mp}$  used to set the ultimate trip level and components  $R_{mp}$  and  $R_{mp}$  and  $R_{mp}$  and capacitor  $R_{mp}$  are segmented into  $R_{mpi}$ ,  $R_{mpi}$  disposed internally in the package and  $R_{mpe}$ ,  $R_{mpe}$  disposed externally of the package.  $R_{mpe}$  and  $R_{mpe}$  are connected in parallel to  $R_{mpi}$  and  $R_{mpi}$  and the values of  $R_{mpi}$  and  $R_{mpi}$  are chosen as default values to fix the lower limits of programmability.

The shunt resistor referred to above in relation to the I<sup>2</sup>RC section is shown and described in copending application Serial No. (Attorney Docket A18622) filed of even date herewith, the subject matter of which by this reference is incorporated herein.

A safety fuse specifically adapted for use with the controller of the present invention is shown and described in copending application Serial No. (Attorney Docket A18476) filed of even date herewith, the subject matter of which by this reference is incorporated herein.

# **Brief Description of the Drawings**

15

20

40

45

50

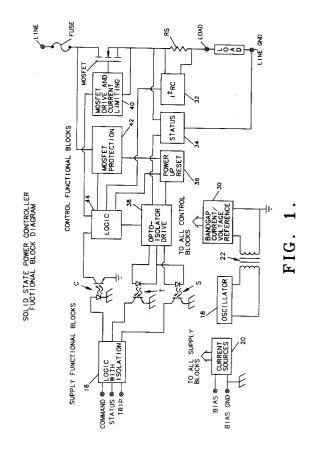

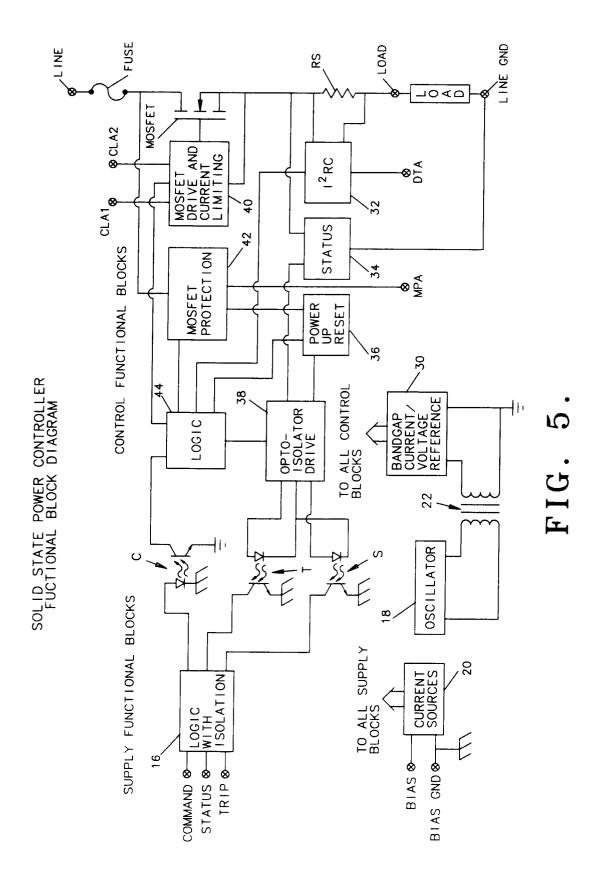

Fig. 1 is a block diagram of a solid state circuit controller made in accordance with the invention;

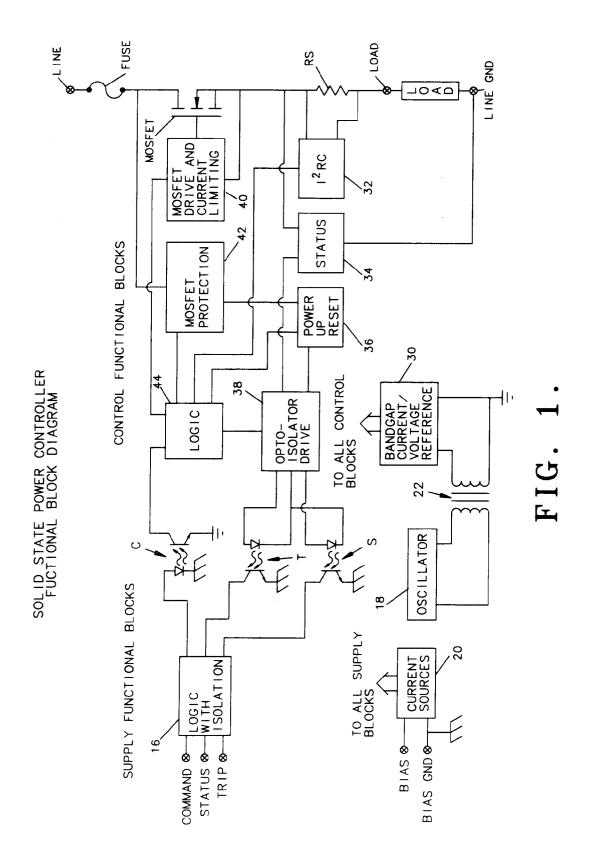

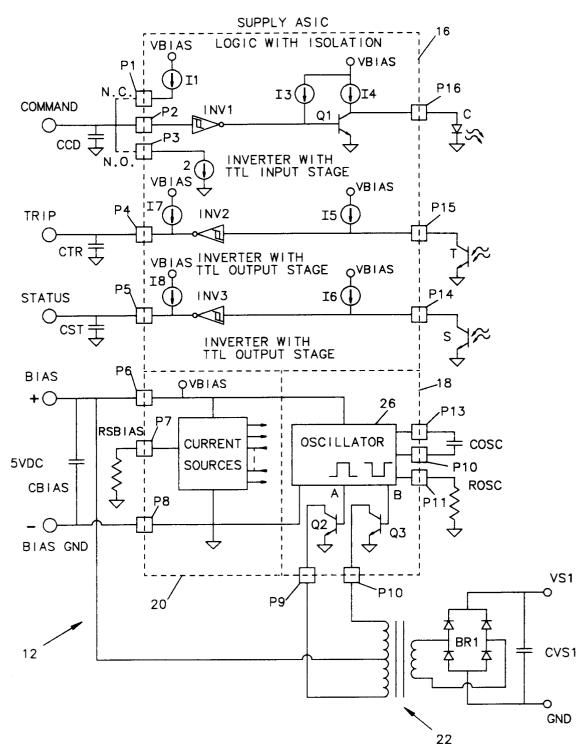

Fig. 2 is a circuit diagram showing a Supply ASIC and associated off-IC components used with the present invention;

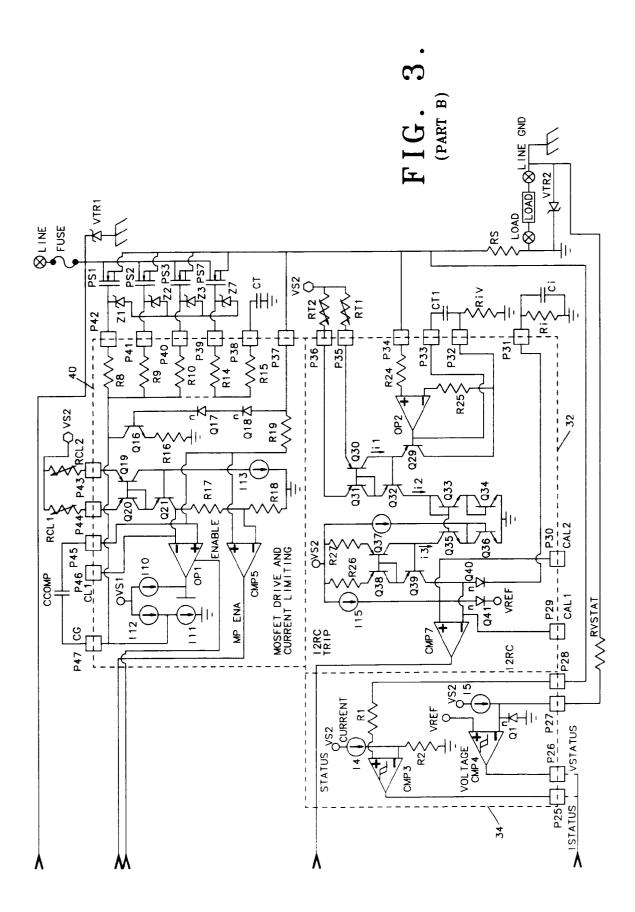

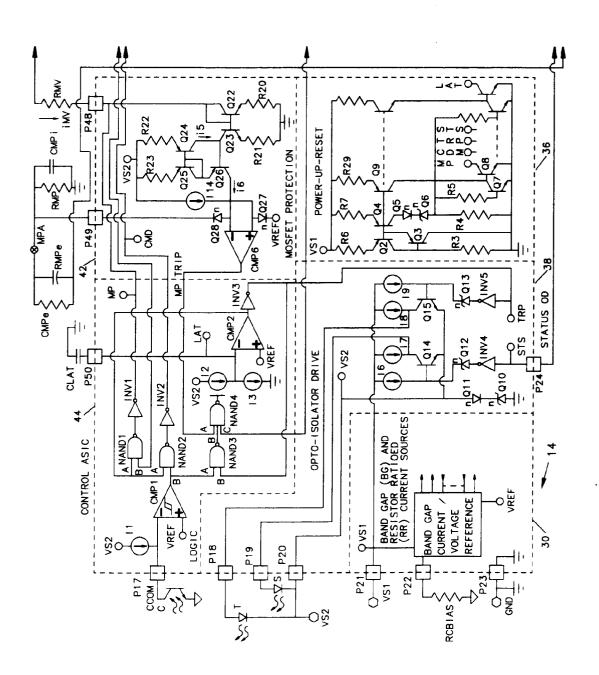

Fig. 3 (parts A and B) is a circuit diagram showing the Control ASIC and associated off-IC components used with the present invention;

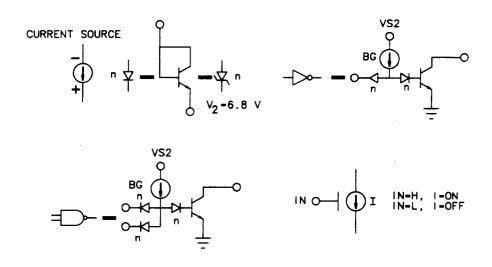

Fig. 3a shows several conventional symbols and their equivalents;

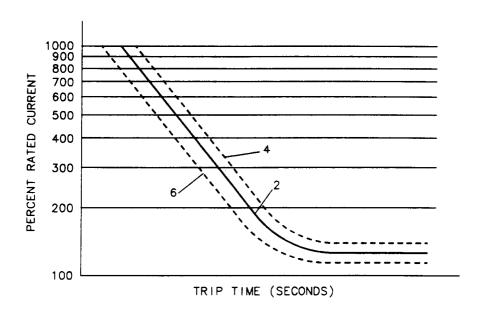

Fig. 4 is a trip time vs load current curve as used in accordance with the present invention.

Fig. 5 is a block diagram of a solid state circuit controller similar to Fig. 1 but showing additional lines used for programming the controller;

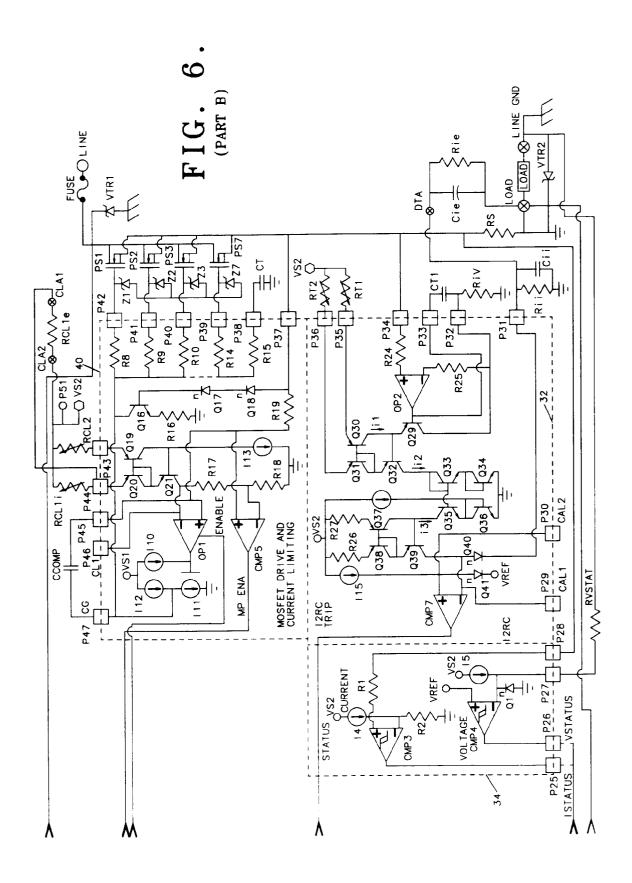

Fig. 6 (parts A and B) is a circuit diagram similar to Fig. 3 but showing internal default components, programming points and external programming components;

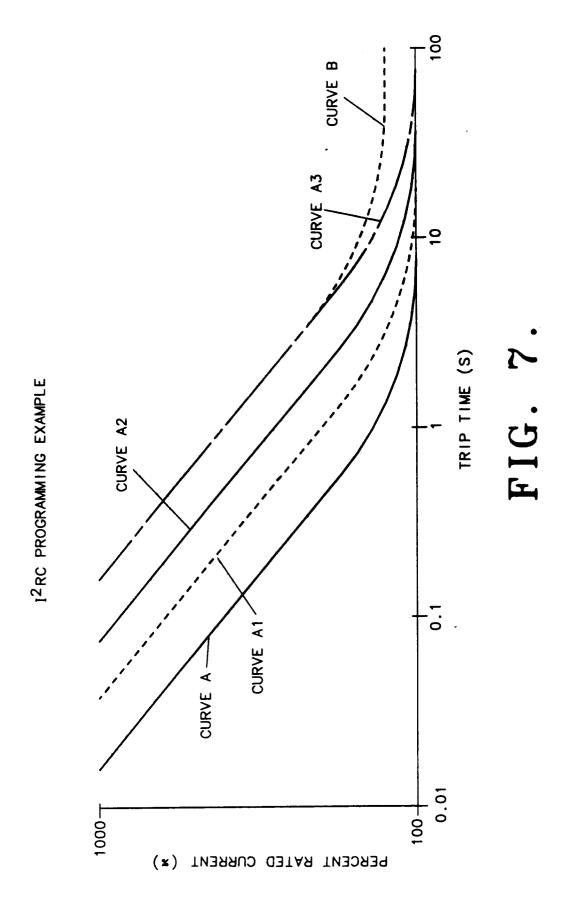

Fig. 7 is similar to Fig. 4 but shows a programming range for trip time vs. load current values; and Fig. 8 shows Line to Load Voltages vs. Trip Time switch protection curves.

## Description of the Preferred Embodiments

With particular reference to Fig. 1 the controller comprises a first supply portion which includes the functional blocks Logic With Isolation section 16, Oscillator section 18 and Current Sources section 20. A second control portion of the controller includes a MOSFET Drive and Current Limiting section 40, a MOSFET protection section 42, I<sup>2</sup>RC section 32, Logic section 44, Status section 34, Band Gap Current/Voltage section 30, Opto-Isolator Drive section 38 and a Power-up Reset section 36.

With reference to the following description it should be noted that all current sources are non-ideal. They are only functional provided the negative terminal of the current source is approximately one diode voltage drop above the positive terminal. If there is less than one diode drop, the output current is effectively zero. Unless otherwise noted, the outputs of each logic gate and comparator is an open collector transistor (NPN), therefore a logic low voltage is equal to the saturation voltage of the output transistor (approximately 0.2V). The inputs of all logic gates are non-ideal current sources, therefore, due to the non-ideal behavior of the current sources a logic high voltage is equal to the voltage at the negative terminal of the current source minus one diode voltage drop. Unless otherwise stated, all voltages within an ASIC are referenced to the local or individual ASIC ground. The stated voltages are assumed to be nominal.

According to a preferred embodiment of the invention, as seen in Figs. 2 and 3, a controller comprises two integrated circuits (ICs) referred to as Supply ASIC 12 and Control ASIC 14 and various discrete off-IC components.

As seen in Fig. 2, the supply circuitry is made up of Supply Asic 12 and various off-IC components including capacitors, resistors, photo transistors/LEDs, transformers and diode bridges. Supply ASIC 12 is made up of functional sections Logic With Isolation 16, Oscillator 18 and Current Sources 20.

The function of Logic With Isolation section 16 is to provide a TTL compatible input stage for a COMMAND line, an LED driver for the COMMAND line opto-isolator C, a TTL compatible output stage for STATUS and TRIP lines, and a photo-transistor receiver for STATUS and TRIP line opto-isolators S and T, respectively. All control signals communicated between ASICS 12 and 14 are passed through opto-isolators to achieve isolation between the two circuits.

TTL input/output standards are as follows:

# 30 Input

35

45

15

20

TTL logic high input voltage

TTL logic low input voltage

TTL logic high input current

TTL logic low output current

400u A maximum

### Output

TTL logic high output voltage

TTL logic low output voltage

TTL logic high output current

TTL logic low input current

The COMMAND input line is tied to an off-IC filter capacitor Ccd to protect against transient damage to ASIC 12 and connected to the input of invertor INV1 having hysteresis to improve noise immunity of the circuit. Depending on the particular load with which the controller is to be used, by tying either the normally closed current source I1 of 10u A or the nominally open current source I2 of 10u A pin to the COMMAND pin, the input of INV1 will be pulled high (one diode drop below BIAS) or low (one diode drop above BIAS GND), respectively in the event the COMMAND line is open circuited, i.e., disconnected.

Current sources I3 and I4 are connected to the base and collector respectively of transistor Q1 whose collector is also connected to opto-isolator C. When the input of invertor INV1 is low the output of invertor INV1 is an open collector NPN transistor and I3 of 200u A supplies base current to transistor Q1. Transistor Q1 is saturated with a collector current of 2m A supplied by I4, therefore no current flows through the LED of the COMMAND opto-isolator C and the LED is off.

When the input of invertor INV1 is high, the output of invertor INV1 is low, a saturated NPN transistor with 200u A current source from I3, and transistor Q1 is off (open collector) so that source I4 supplies current to the LED of the COMMAND opto-isolator C turning the LED on.

Inverters INV2 and INV3 both have input stages incorporating hysteresis to improve the noise immunity of the circuits. Off-IC capacitor  $C_{tr}$  and  $C_{st}$  are tied to the TRIP and STATUS outputs respectively to protect

against transient damage to the ASIC 12.

15

30

45

50

55

When the state of the photo-transistor of the TRIP opto-isolator T is open collector (LED off), the input of invertor INV2 is pulled above the upper threshold by I5 (200u A) and the output of invertor INV2 goes low, a saturated NPN transistor, signifying no trip condition. When the photo-transistor of the TRIP opto-isolator T is saturated (LED on) the input of invertor INV2 is below the lower threshold and the output of invertor INV2 is an open collector NPN transistor and is pulled high by I8 of 800u A signifying a trip condition.

In like manner, when the state of the photo-transistor of the STATUS opto-isolator S is an open collector (LED off), the input of invertor INV3 is pulled above the upper threshold by current source I6 (200u A) and the output of invertor INV3 goes low, a saturated NPN transistor, signifying no status condition. When the photo-transistor of the STATUS opto-isolator is saturated (LED on), the input of invertor INV3 is below the lower threshold and the output of INV3 is an open collector NPN transistor and is pulled high by I7 of 800u A signifying a status condition.

The function of the oscillator section 18 is to produce a transformer drive signal which is used to power ASIC 14, the controller circuitry, by means of an isolation transformer 22, a full wave bridge BR1 and a smoothing capacitor  $C_{vs1}$ .

Oscillator 26 is a standard emitter-coupled oscillator modified with high speed output comparators to drive transistors Q2 and Q3. The oscillator frequency is set by capacitor  $C_{\rm osc}$  and resistor  $R_{\rm osc}$  mounted externally of the ASIC. Oscillator 26 produces two output signals, A and B, which are 250 KHZ square waves 180° out of phase with each other. The oscillator outputs drive transistors Q2 and Q3 into saturation when high; the transistors having an open collector when low. The collector of transistors Q2 and Q3 are tied to the ends of the primary winding of transformer 22 whose center tap is connected to the BIAS line. Driven by transistors Q2 and Q3 the transformer acts as two synchronized 1:4 ratio transformers (1/2:2 primary to secondary ratio). With practical transformer efficiencies, saturation voltages of transistors Q2 and Q3 equal to 0.2V and a BIAS voltage of 5V, a 16.5V peak to peak square wave is produced across the transformer secondary. A full wave rectifier BR1 is placed across the transformer secondary to create a DC output of 15.1V. A capacitor  $C_{\rm vs1}$  is placed across the DC outputs of the rectifier to smooth the output which is connected across VS1 and GND to power the control circuitry of ASIC 14.

The function of the Current Sources section 20 is to provide temperature stable current sources to power other sections of the ASIC. The reference current level used to derive all other current sources is set by off-IC connected resistor  $R_{\rm sbias}$ . The current sources section 20 and other functional sections of ASIC 12 operate at a nominal voltage level of 5V. Off-IC capacitor  $C_{\rm bias}$  is added across the BIAS and BIAS GND lines to minimize noise generated by the switching of the functional blocks of ASIC 12 and to protect against transient damage to ASIC 12.

The function of the control circuitry is to, a) turn the load current on and off by means of a solid state switch made up of MOSFETs in response to a  $C_{com}$  input from ASIC 12, b) provide a primary trip mechanism to remove load current from the load in accordance with a selected trip time vs load current curve, c) limit the maximum load current to a predetermined calibrated level (current limit), d) provide a secondary trip mechanism that protects the MOSFETs from damage when in the current limiting mode, e) provide a trip latching feature which holds a trip, keeping the controller off until reset by the  $C_{com}$  input from ASIC 12, f) provide the required drive signal for an opto-isolator LED to communicate a status indication to ASIC 12 reflecting that either load voltage or load current above a specified threshold is present, and g) provide the required drive signal for an opto-isolator LED to communicate a trip indication to ASIC 12.

As seen in Fig. 3, the control circuitry is made up of Control ASIC 14 and various off-IC components including resistors, capacitors, photo-transistors/LEDs, MOSFETs and semiconductor transient suppressors. Control ASIC 14 comprises the following functional sections: Band Gap Current/Voltage Reference section 30, I²RC section 32, Status section 34, Power-Up-Reset section 36, Opto-Isolator Reference Drive section 38, MOSFET Drive and Current Limiting section 40, MOSFET Protection section 42 and Logic section 44.

Band Gap Current/Voltage Reference section 30 provides a temperature stable voltage reference, temperature stable current sources and resistor ratioed current sources used by other functional sections within ASIC 14.

$V_{\rm ref}$ , the band gap voltage reference, is derived from a standard band gap reference circuit which creates an inherently temperature stable voltage of approximately 1.25V which is scaled up using internal resistor rationing to obtain  $V_{\rm ref}$  of 3.25V which serves as a reference voltage for other functional blocks of ASIC 14.  $V_{\rm ref}$  is also used in conjunction with  $R_{\rm cbias}$  to create temperature stable band gap, BG, current sources used to power other functional blocks within ASIC 14. Resistor ratioed, RR, current sources are also developed within this section whose values are ratioed by internal ASIC resistors to create temperature stable voltage references of values other than  $V_{\rm ref}$ , needed by other functional sections of ASIC 14, by feeding the RR current sources through internal ASIC resistors matched with those used to establish the value of the RR current sources.

I²RC circuit 32 creates an electronic analog of the temperature of a wire as a function of the heating due to current flow through the wire and outputs a trip signal indicating that the temperature of the wire has risen a predetermined amount, simulating a selected trip time vs load current curve. In addition, circuit 32 provides a feature known as "thermal memory". Thermal memory is a term which refers to the feature of shortening the trip time of a given load current level due to previously stored energy in the wire, or equivalently elevated initial wire temperature, as a result of previous load current flow. Without this feature, trip times for a given load current level would remain constant and repeated applications of load current at intervals which did not allow the wire temperature to return to ambient would cause the wire to exceed the maximum specified level.

A thermal model of the wire can be used to determine the time required for a given amount of power dissipation to raise the wire temperature a selected amount. The following first order differential equation models the energy stored in the wire as a function of time  $(E_w(t))$  which is proportional to the temperature rise of the wire as a function of time:

(1)

$$K E_w(t) + d E_w(t) = R_w I_w^2(t)$$

Where:

15

20

25

30

35

40

45

55

R<sub>w</sub> resistance of the wire.

I<sub>w</sub>(t) current through the wire as a function of time.

$R_w I_w^2(t)$  power dissipated within the wire

K 1/ the thermal time constant of the wire.

The solution is as follows:

(2)

$$E_w(t) = \int_0^t R_w I_w^2 (\mathcal{T}) e d\mathcal{T} + E_w(t=0)e$$

Where:

$E_w(t=0)e^{-Kt}$  the thermal memory of the equation where  $E_w(t=0)$  is the energy stored in the wire at time = 0.

The I<sup>2</sup>RC circuit section 32 simulates the temperature rise of the wire and produces a trip signal when the temperature of the wire has risen a specified amount. Circuit 32 produces an electrical signal in the form of voltage which is proportional to the above energy/temperature equation in the manner described below.

Load current  $I_w(t)$  flowing through shunt  $R_s$  causes a voltage to be developed across shunt  $R_s$  as follows:

$$(3) V_s(t) = I_w(t) R_s$$

The non-inverting terminal of ground sensing op-amp OP2 is tied to the positive connection of shunt RS through resistor R24 of 600 ohms. The output of op-amp OP2 is connected to the base of NPN transistor Q29 and to ground through stabilizing capacitor  $C_{t1}$  and serially connected resistor  $R_{iv}$ . The emitter of transistor Q29 is tied to the junction of capacitor  $C_{t1}$  and resistor  $R_{iv}$  and to the inverting terminal of op-amp OP2 through resistor R25 of 600 ohms. This arrangement in the feedback path of the op-amp OP2 forces the voltage of the inverting terminal of op-amp OP2 to equal the voltage at its non-inverting terminal, i.e.,  $R_s$  voltage. Assuming negligible base current flowing at transistor Q29:

(4)

$$i1(t) = V_s(t)/R_{iv} = I_w(t) R_s/R_{iv}$$

Transistors Q30, Q31 and Q32 make up a standard "Wilson" current mirror configuration providing improved collector current matching by minimizing base current error. Off-IC emitter resistors R<sub>t</sub>1 and R<sub>t</sub>2 for transistors Q30 and Q31 respectively provide a means for external calibration of current i2(t). That is,

(5)

$$i2(t) = i1(t) R_t 1/R_t 2 = I_w(t) R_s R_t 1/(R_{iv} R_t 2)$$

Calibration of current i2(t) provides a means of adjusting the ultimate trip of the controller trip time vs load current curve in a highly accurate, quick manner and at low cost. Ultimate trip calibration is performed by disconnecting capacitor  $C_i$ , to be discussed below, from the circuit to make the time constant of the circuit equal to 0, running the selected ultimate trip current through the controller, and trimming resistors  $R_t1$  and  $R_t2$  until the voltage difference between pins  $C_{al}1$  and  $C_{al}2$  (P29, P30), connected respectively to the inverting and non-inverting inputs of comparator CMP7, is 0V. Capacitor  $C_i$  is then connected to complete the circuit.

Due to the fact that resistor trimming procedures such as laser trimming, only increases the value of a resistor, two resistors are needed to adjust current i2(t). Increasing the value of  $R_t$ 1 tied to transistor Q30 will increase i2(t) whereas increasing the value of  $R_t$ 2 tied to transistor Q31 will decrease the value of current i2(t).

NPN transistors Q33, Q34, Q35, Q36 and current source I<sub>ref</sub>, a band gap current source of 300u A, form an approximate current squaring function as follows:

(6)  $i3(t) = i2^2(t)/I_{ref} = I_w^2(t) (R_s R_t^2/R_t^2)^2/I_{ref} = I_w^2(t) Y$  where  $Y = (R_s R_t^2/R_t^2)^2/I_{ref}$  The current to be squared, i2, is fed into diode connected transistors Q33, Q34. Transistor Q36 is fed by

a relatively large current source  $I_{ref}$  (300u A). As a result of the large current source ( $I_{ref}$ ) relative to i3 the diode drop across transistor Q36 is essentially constant and the total of the two  $V_{bes}$  built-up across transistors Q33, Q34 is imposed across the base-emitter of transistor Q35 thereby squaring the Q33, Q34 collector current.

Transistors Q37, Q38, Q39 and resistors R26 and R27 form a standard Wilson current mirror configuration providing improved collector current matching by minimizing base current error with emitter resistors to minimize errors due to transistor  $V_{be}$  mismatch resulting in:

(7)

$$i4(t) = i3(t)$$

Current i4(t) flows through diode connected NPN transistor Q40 to charge the parallel R-C network made-up of resistor  $R_i$  and capacitor  $C_i$ . The voltage across resistor  $R_i$  and capacitor  $C_i$  is as follows:

(8)

$$V_{w}(t) = 1/C_{i} \int_{0}^{t} I4(\tau)e^{-1/(R_{i} C_{i})(t - \tau)} d\tau$$

$$-t/(R_{i} C_{i})$$

$$+ V_{w}(t=0)e$$

By comparing the equations for  $E_w(t)$ , No. 2, and  $V_w(t)$ , Nos. 8 or 9, it can be seen that the two are proportional under the following conditions:

$R_i C_i = 1/K$ , setting the time constants of the two equations equal to each other,

I4(t) is proportional to  $I_w^2(t)$  as shown previously by equation Nos. 6 and 7, and

1/C<sub>i</sub> \* Y (constant) is chosen to be the right proportion to R<sub>w</sub>.

5

10

15

20

25

30

35

40

45

50

55

By way of example, let  $I_w(t)$  be a step function ( $I_w(t) = I_w$  for t > 0,  $I_w(t) = 0$  for t < 0) and  $V_w(t = 0) = 0$ , then the solution for  $V_w(t)$  is:

$$-t/R_{i} C_{i}$$

(10)  $V_{w}(t) = Y/C_{i} I_{w} (1 - e)$

It may be noted that this equation is used to develop the Fig. 4 curve.

Diode connected transistor Q40 is connected to the RC network R<sub>i</sub> C<sub>i</sub> to prevent discharge of the RC network through other circuitry such as comparator CMP7, preserving thermal memory even when power is removed, thereby providing the same memory function as an electromechanical thermal circuit breaker.

Diode connector transistor Q41 connected between  $V_{ref}$  derived from the Current/Voltage Circuit 30 and the non-inverting input of comparator CMP7 provides compensation for the temperature effect on the voltage drop across transistor Q40.

The voltage at the inverting terminal of CMP7 ( $V_{cmp}$  7-) is equal to:

$V_{cmp}$  7- =  $V_{w}(t)$  + V Q40, where VQ40 is the voltage drop across Q40.

The voltage at the non-inverting terminal of CMP7( $V_{cmp}$  7+) is equal to:

$V_{cmp}$  7+ =  $V_{ref}$  + VQ41, where VQ41 is the voltage drop across Q41. Diode Q41 is forward biased by current source I15.

Assuming that the difference between the voltage drop across VQ40 and VQ41 is negligible, when  $V_w(t)$  is less than  $V_{ref}$  then  $V_{cmp}$  7- will be less than  $V_{cmp}$  7+ and the output of comparator CMP7 will be high signifying that the wire temperature has not risen above the selected amount and therefore, a trip condition is not present.

Again, assuming that the difference between the voltage drop across VQ40 and VQ41 is negligible, when  $V_w(t)$  is greater than  $V_{ref}$ ,  $V_{cmp}$  7- will be greater than  $V_{cmp}$  7+ and the output of comparator CMP7 will be low

signifying that the temperature of the wire has risen the selected amount and that a trip condition is present. The output of comparator CMP7 is tied to input C of NAND gate NAND 4 through line I²RC TRIP.

As an example, off-IC component values used to achieve a trip time vs load current curve 2 per MS3320 seen in Fig. 4 are as follows:

R<sub>s</sub> = 10m ohm (10.0 amp rated load current)

$\begin{array}{lll} R_{iv} & = 15.8 \; \text{K ohm} \\ C_t & = 1000 \; \text{pF} \\ R_i & = 15.1 \; \text{M ohm} \\ C_i & = 1 \; \text{uF} \end{array}$

5

15

30

35

45

50

55

$R_t1$  and  $R_t2$  = Adjusted to set the nominal ultimate trip load current percentage (126.5 of rated current). Approximate value for each of  $R_t1$  and  $R_t2$  is 20 K ohms.

Dashed line curves 4 and 6 shown in Fig. 4 represent maximum and minimum trip time vs load current curves, respectively.

Using the  $V_w(t)$  equation (Nos. 8 or 9) it can be seen that adjusting one or more of the off-IC components of circuit 32 can tailor the circuit performance to meet specific requirements of a given application. The current performance characteristics which can be changed by adjusting one or more external components are the trip time vs load current curve time constant, load current rating (i.e., 2.5 amp, 5.0 amp, 10.0 amp, etc.) and ultimate trip load current. For example, for a given load current rating, other trip time vs load current curve time constants can be obtained by adjusting capacitor  $C_i$  and resistor  $R_i$ , for a given trip time vs load current curve time constant, other load current ratings can be used by adjusting  $R_s$ , the ultimate trip load current can be adjusted by resistors  $R_t$ 1,  $R_t$ 2 and  $R_{iv}$ .

Preferably, the resistance of the shunt  $R_s$  has been chosen such that 100% rated current, RI, produces 100m V across the shunt (100m V/100% rated current), i.e., a controller with a rated current of 10A would use a 10m ohm shunt. By choosing the shunt in this way, the voltage produced across the shunt for a given rated current percentage will be the same independently of the rated current value, e.g, x % of R I = x mV across  $R_s$ . However, if desired, other shunt resistances providing other scale factors may be chosen.

The function of Status circuit 34 is to provide an output of either a selected current or a voltage status indication when the load current or load voltage, respectively, exceeds a predetermined threshold. Current status indication is chosen by connecting pin P25 to pin P24 whereas voltage status is chosen by connecting pin P26 to pin P24. With respect to the current status, an 18 mV reference voltage tied to the inverting terminal of the ground sensing comparator CMP3 is set by resistor ratio current source I4 of 30u A and a 600 ohm resistor R2. Comparator CMP3 is designed to have approximately 4 mV of hysteresis to enhance noise immunity of the circuit. The non-inverting terminal of comparator CMP3 is tied to resistor  $R_s$  through 600 ohm resistor R1. When the voltage across shunt  $R_s$  is less than the lower threshold of CMP3 (18 mV) the output of the comparator tied to the ISTATUS pin P25 is low and when the voltage across shunt  $R_s$  exceeds the upper threshold (22 mV) the output is high.

With respect to the voltage status the inverting pin of comparator CMP4 is connected to the positive terminal of band gap current source I5 of 50 u A, to the cathode of diode connected NPN transistor Q1 and through pin P27 to  $R_{vstat}$  and then to LINE GND. The non-inverting terminal of comparator CMP4 is tied to a voltage reference,  $V_{ref}$ , derived from the Current/Voltage circuit 30. Comparator CMP4 is designed having approximately 0.5V of hysteresis for noise immunity enhancement. Resistor  $R_{vstat}$  is chosen so that the upper load voltage threshold,  $V_{up}$ , and lower load voltage threshold,  $V_{lo}$ , are as follows:

$$V_{up} = 15 * R_{vstat} - V_{ref}$$

$V_{i0} = 15 * R_{vstat} - (V_{ref} + 0.5V)$

When the voltage across the load is less than  $V_{l0}$ , the voltage at the inverting terminal of comparator CMP4 will be above the non-inverting terminal and the output, which is tied to the VSTATUS pin P26, is low. When the voltage across the load is greater than  $V_{up}$ , the voltage at the inverting terminal of comparator CMP4 will be less than the non-inverting terminal and the output will be high. Diode Q1 protects ASIC 14 from damage that would result if its voltage rating was exceeded by preventing the voltage at the inverting terminal of comparator CMP4 from going more than one diode drop below GND.

The function of Power Reset circuit 36 is to reset/disable critical sections of the circuitry of ASIC 14 until sufficient operating voltage is present across VS1 (pin P21) and GND (pin P23) for proper operation.

Since the current mirror PNP transistor Q9, current mirror collector resistor R29, the two NPN transistors Q7 and Q8, and the base resistor R5 for output signal MP are duplicated for each of the other output signals CMD, TRP, STS and LAT only the details of the operation of the MP output signal will be described.

Circuit 36 functions such that current flows in the common base PNP current mirrors made up of Q2, Q3, R3 and R6 before any other current sources within ASIC 14. When the collector voltage of transistor Q4 is less than the NPN zener diode of Q6 ( $V_q$ 6 = 6.8V) connected to the collector of Q4, plus one diode voltage

drop of diode Q5 ( $V_q5 = 0.7V$ ) added for temperature compensation (equivalently  $V_q6 + V_q5 = 7.5V$ ), there is no Q4 collector current and, therefore, no base current is available for transistor Q7 which is pulled low by base resistor R5 and common resistor R4, so that transistor Q7 is off and transistor Q8 is on (collector-emitter is saturated due to base current supplied by the portion of the current mirror made-up of transistor Q9 and resistor R29). With output signal MP at the saturation voltage of transistor Q8, the MOSFET Protection circuit 42, to be described infra, will be disabled since all current from resistor  $R_{mv}$  (pin P48) is shorted to ground GND by transistor Q8.

When the collector voltage of transistor Q4 is greater than  $V_q6 + V_q5$ , current from the collector of Q4 will flow into the base of transistor Q7 causing the collector-emitter of transistor Q7 to saturate and turning off transistor Q8 (open collector) causing transistor Q8 to have no effect on the operation of MOSFET Protection circuit 42. The collector voltage of transistor Q4 will be equal  $V_q6 + V_q5$  when VS1 is approximately one additional diode drop higher (8.2 V total).

The function of Opto-Isolator Drive section 38 is to provide a means of re-routing the main current sources, which supply the majority of ASIC 14, through the LED portion of the trip T and status S opto-isolators when required. Circuit section 38 also establishes a voltage supply VS2 from which most of the components within ASIC 14 are powered.

15

20

30

35

55

Voltage source VS2 is established by the zener voltage of NPN transistor Q10 (6.8V) plus a forward biased diode drop of NPN transistor Q11 (0.7V) added for temperature compensation for a total of approximately 7.5V.

The operation of the status opto-drive and the trip opto-drive is identical and therefore only the details of the status opto-drive will be described.

When the input of invertor INV4 is low indicating current flow or load voltage below the thresholds, the output of invertor INV4 is high (open collector). Band gap current source I6 (200u A) will saturate transistor Q14 whose collector is tied to band gap current source I7 (2m A). The Q14 collector current, current I7, and the base current, I6, will flow into VS2 to power a majority of the ASIC 14 electronics.

When the input of invertor INV4 is high, the output of the invertor will be low sinking all of the current from current source I6 causing a zener breakdown of zener diode Q12 which pulls the base of transistor Q14 approximately one diode drop below the emitter turning Q14 off. With transistor Q14 off, current source I7 will flow through the LED portion of the status opto-isolator S (pin P19) and flow through pin P20 into VS2 to provide power for a majority of the ASIC 14 electronics and indicate current flow or load voltage above the thresholds.

The function of MOSFET Drive and Current Limiting circuit section 40 is to control the MOSFETs drain-source resistance by manipulating the MOSFETs gate-source voltage. The MOSFET control functions are designed to turn the MOSFETs on and off and to limit the peak current flow through the MOSFETs to a calibrated or selected level. Limiting the current prevents over-current conditions from damaging the MOSFETs.

A plurality of MOSFETs, PS1-PS7 being indicated in the figure, have their sources and drains connected in parallel with their gates connected respectively to 600 ohm gate resistors R8-R14. Resistors R8-R14, along with another 600 ohm resistor R15 connected to off-IC mounted capacitor  $C_T$  through pin P38 (if required an eighth MOSFET, and a 15V zener diode, can be substituted for  $C_t$  at pin 38), are connected to the junction between current sources I12 and I11 and to pin P47. Current sources I12 and I11 are connected between source VS1 and ground with current source I10 connected between VS1 and the output of op-amp OP1 whose output is adapted to control the state of energization of source I11.

When the ENABLE of op-amp OP1 is low the output of the comparator is pulled high by the band gap current source I10 of 100u A turning on band gap current source I11 of 2.2m A. Band gap current source I12 sources 600u A and current source I11 sinks 2.2m A with a net of 1.6m A flowing from the MOSFET gates and capacitor  $C_T$  through the 600 ohm resistor R8 through R15, discharging the MOSFET gates and capacitor  $C_T$ . When completely discharged the voltage at the negative terminal of source I11, also the positive terminal of source I12, will be approximately one diode drop above ground GND. Since the gates are completely discharged, there will be no current flow through resistors R8 and R15, therefore, the voltage at the MOSFET gates will also be approximately one diode drop above ground GND ensuring that the MOSFETs are off, i.e., their drain-source regions in a state having high impedance. ASIC 14 includes outputs to drive eight MOSFETs directly, that is the gate of eight MOSFETs can be tied directly to outputs of resistors R8 through R15. If additional MOSFETs are desired output CG and off-IC gate resistors are required. Output CG, pin P47, is connected to capacitor  $C_{comp}$  and then through pin P45 to the non-inverting terminal of op-amp OP1.

When the ENABLE of op-amp OP1 is high and the non-inverting terminal of OP1, which is tied to the shunt resistor  $R_s$  through 600 ohms resistor R19, is lower than the inverting terminal of OP1, the current limiting voltage, the output of op-amp OP1 is low diverting all the current from the 100uA source I10 into the output of OP1 and away from the input of current source I11. This causes current source I11, a 22X multiplying current source, to be turned off. 600u A from source I12 flows to charge the gates of the MOSFETs turning the MOS-

FETs on (low drain-source resistance). When the gates are completely charged, there will be no current flow through resistors R8-R15, therefore, the voltage of the MOSFET gates will be approximately one diode drop below VS1 ensuring that the MOSFETs are on. Off-IC 15V zener diodes Z1 through Z7 are connected between the MOSFET gates and the sources to protect the MOSFETs from damage due to excessive gate-source voltage. Typical MOSFETs have a maximum gate-source voltage rating of 20V.

If a load current flows that would cause the voltage drop across shunt resistor  $R_s$  (non-inverting terminal of OP1) to exceed the current limit voltage (inverting terminal of OP1) the output of OP1 will begin to come out of saturation causing some of the 100uA from current source I10 to be diverted into the input of current source I11, causing it to turn on. It should be noted that the output voltage of OP1 has a linear effect on the value of current source I11. For example, OP1 output = 0V, I11 = 0m A; OP1 output = VS2/2, I11 = 1.1m A; OP1 output = VS2, I11 = 2.2m A. As the output of OP1 goes positive turning on I11 current flow from I12 will be diverted away from the MOSFET gates to current source I11. Additional current will also be drawn out of the MOSFET gates to I11 such that the gate-source voltage of the MOSFETs will be lowered causing the source-drain resistance to increase, in turn lowering the load current and voltage across the shunt  $R_s$ . A balanced, steady state condition is reached when the voltage developed across shunt  $R_s$  (non-inverting terminal of OP1) is equal to the current limiting voltage (inverting terminal of OP1).

A load current exceeding the current limit level may occur at two different times. First, the controller may turn on into the load current, in which case the circuit will limit the load current to the current limit level during turn on. Second, an overload current may be applied to the controller while it is fully on, i.e., with the MOSFETs drain-source at low resistance. In this case a large degree of current overshoot will occur while the circuit lowers the MOSFETs gate-source voltage to raise the drain-source resistance. In order to limit this peak overshoot and decrease the overshoot duration, NPN transistor Q16 and emitter resistor R16 are connected between the MOSFET gates and ground with its base tied to the shunt R<sub>s</sub> through diode connected NPN transistors Q17, Q18. If the voltage across the shunt exceeds a level equal to approximately three forward biased diode drops, i.e., approximately 2.1V, base current will flow into transistor Q16 turning the transistor on thereby rapidly removing charge from the MOSFET gates. Once the shunt voltage drops below that level the normal output gate drive circuit made-up of current sources I11 and I12 will take over discharging the MOSFETs gates until the voltage across the shunt equals the current limit voltage.

The inverting terminal of op-amp OP1 is tied to CL1 pin P46. The current limit level percentage is approximately equal to the voltage at CL1 in millivolts when a 100m V/100% rated current shunt is chosen as described supra. For example, 800m V at CL1 will cause the circuit to current limit at approximately 800% of rated load. If a shunt having a different resistance is chosen, the current limit percentage set by the voltage at CL1 must be adjusted accordingly. The current limit voltage is set by resistor ratio current source I13 of 30u A, resistors R17 of 7.2K ohms, R18 of 14.4K ohms,  $R_{cl}1$  and  $R_{cl}2$  Resistors  $R_{cl}1$  and  $R_{cl}2$  are connected off-IC at pins P44, P43 respectively and make up the emitter resistors of Wilson current mirror Q19, Q20, Q21 with the collector of transistor Q19 and base of transistor Q21 connected to current source I13 and the collector of transistor Q21 connected to the inverting terminal of op-amp OP1 and serially connected resistors R17, R18.

The voltage at CL1 (V<sub>cl</sub>1) is as follows:

5

15

30

40

45

55

$$\begin{aligned} V_{cl}1 &= I13 * (R17 + R18) * R_{cl}2/R_{cl}1 \\ &= 30u A * (7.2K ohms + 14.4K ohms) * R_{cl}2/R_{cl}1 \\ &= 648m V * R_{cl}2/R_{cl}1 \end{aligned}$$

Since resistor trimming procedures, such as laser trimming, only increases the value of a resistor as mentioned above, two resistors are required to adjust the voltage at CL1. Increasing the value of  $R_{cl}2$  will increase the voltage at CL1 whereas increasing the value of  $R_{cl}1$  will decrease the voltage at CL1.

Capacitor  $C_t$  is included in the circuit to adjust the turn on and turn off time of the MOSFETs by adjusting the rate of rise and fall of the MOSFETs gate-source voltage. Stabilizing capacitor  $C_{comp}$  is connected in the OP1 feedback path to minimize load current oscillations during current limiting.

The junction of resistors R17 and R18 is tied to the inverting terminal of comparator CMP5 whose non-inverting terminal is connected to shunt  $R_s$  through resistor R19 and whose output is connected to the Logic circuit section 44 through a line labeled MP ENA. The voltage divider formed by resistors R17 and R18 make the voltage at the inverting terminal of comparator CMP5 (CMP5-) equal to 2/3 of the current limit voltage  $V_{cl}$ 1.

When the voltage across the shunt is less than 2/3  $V_{cl}1$ , the output of comparator CMP5 is low. When the voltage across the shunt exceeds 2/3  $V_{cl}1$ , the output of the comparator is high. As mentioned above, the output

of comparator CMP5 is tied to Logic circuit 44 and is used as one of the signals required to enable the MOSFET Protection Circuit 42 to be discussed below.

Transient suppressors VTR1, VTR2 are added across LINE to LINE GND and LOAD to LINE GND respectively to protect the MOSFETs and certain circuitry from damage due to LINE and LOAD voltage transients and from LOAD voltage transients caused by switching inductive loads.

The function of the MOSFET Protection Circuit 42 is to provide a secondary trip signal that indicates when the MOSFET junction temperature has risen a selected amount due to high levels of power dissipation which can occur during current limiting. The circuit also includes a thermal memory feature to prevent repeated applications of current limiting at intervals which would not allow the MOSFET junction temperature to return to ambient preventing the MOSFETs from exceeding the maximum junction temperature.

During the current limiting procedure the resistance of the MOSFETs drain-source is increased to limit the current to a predetermined level as described above. In effect, the controller and the load form a voltage divider where the voltage across the load is such that only the current limit level is passing through the load and the rest of the line voltage is dropped across the controllers' LINE-LOAD terminals. In order to protect the MOSFETs from over heating during current limiting due to the power being dissipated in the MOSFETs, a thermal model of the MOSFET package system encompassing the MOSFETs, packaging materials, and attachment materials, was used to determine the time required for a given power dissipation to raise the junction temperatures of the MOSFETs a selected amount. To approximate the thermal model results, the following first order differential equation was used which models the energy stored in the MOSFETs as a function of time, which is proportional to the temperature rise of the MOSFETs as a function of time:

(11)

$$aEmp(t) + dEmp(t)/dt = P(t)$$

Where:

P(t) = the power dissipated in a single MOSFET as a function of time.

= 1/ the thermal time constant of the MOSFET package system.

The solution is as follows:

$$Emp(t) = \int_{0}^{t} V(\gamma) I(\gamma) e d\gamma + Emp(t=0) e$$

V(t) :

= the voltage across the MOSFETs (Vline-Vload) as a function of time.

l(t)

5

15

20

25

30

35

45

50

55

= the current through a single MOSFET as a function of time. I(t) = the load current/number of MOSFETs (assuming equal load current through the MOSFETS).

V(t) \* I(t)

= the power dissipated within a single MOSFET as a function of time.

EMP(t=0)e-at

= the thermal memory of the equation where EMP(t=0) is the energy stored in the MOSFET at time = 0.

The circuit simulates the temperature of the MOSFETs and trips when the temperature of the MOSFETs has risen the selected amount. The allowable temperature rise is simply the maximum allowable junction temperature of the MOSFET (e.g., 150° C) minus the maximum operating temperature of the controller (e.g., 80° C). Circuit portion 42 produces an electrical signal in the form of a voltage that is proportional to the above energy/temperature equation in the manner described below.

Resistor Rmv is connected to LINE and ground GND through serially connected Q22 and R20.

(12)

$$imv(t) = (Vline(t) - Vload(t) - VQ22)/(Rmv + R20),$$

where: VQ22 is the voltage drop across diode connected transistor Q22.

imv(t) = (Vline(t)-Vload(t))/(Rmv + R20) - VQ22/(Rmv + R20)

imv(t) = V(t)/(Rmv + R20) - VQ22/(Rmv + R20)

Transistors Q22, Q23 and resistors R20 and R21 make-up a standard current mirror with emitter resistors to minimize errors due to transistor  $V_{be}$  mismatch, making:

$$i5(t) = imv(t)$$

Transistors Q24, Q25, Q26 and resistors R22 and R23 make-up a standard "Wilson" current mirror configuration, providing improved collector current matching by minimizing base current error, with emitter resistors to minimize errors due to transistor  $V_{be}$  mismatch, making:

$$i6(t) = i5(t)$$

Current i6(t) flows through diode connected NPN transistor Q28 to charge the parallel R-C network made up of resistor  $R_{mp}$  and  $C_{mp}$ .

The voltage across  $R_{mp}$  and  $C_{mp}$  is as follows:

(13)

$$V_{mp}(t) = 1/C_{mp} \int_{\sigma}^{t} i6(\mathcal{T}) e^{-1/(R_{mp} C_{mp})(t-\mathcal{T})} d\mathcal{T}$$

$-t/(R_{mp} C_{mp})$

$+ V_{mp}(t = 0)e$

It can be seen from the equation for  $V_{mp}(t)$  (13) and  $E_{mp}(t)$  (12),  $V_{mp}(t)$  is proportional to  $E_{mp}(t)$  under the following conditions:

$R_{mp}$   $C_{mp}$  = 1/a; setting the time constants of the two equations equal to each other.

i6(t) is proportional to V(t) \* I(t). This can be seen as follows: i6(t) is approximately proportional to V(t) \* I(t) due to the fact that I(t) is a constant during current limiting (let I(t) = I), and, as can be seen in the equation for i6(t), i6(t) is equal to a term proportional to V(t):

V(t)/(R<sub>mv</sub> + R20) minus an error term: VQ22/(R<sub>mv</sub> + R20)

5

10

15

20

25

30

35

40

45

In practice, the error term is partially compensated for through selection of  $R_{mv}$ ,  $C_{mp}$  and  $R_{mp}$ .

Diode Q28 prevents discharge of the  $R_{mp}$  and  $C_{mp}$  network through other circuitry (i.e., comparator CMP6) preserving thermal memory even in the event power is removed from ASIC 14. Diode connected transistor Q27 tied between the non-inverting terminal of comparator CMP6 and VREF provides compensation for the temperature effect on the voltage drop across diode Q28.

The voltage at the inverting terminal of comparator CMP6 (V<sub>cmp</sub> 6-) is equal to:

$V_{cmp}$  6- =  $V_{mp}(t)$  + vQ28, where VQ28 is the voltage drop across diode Q28.

The voltage at the non-inverting terminal of comparator CMP6 ( $V_{cmp}$  6 +) is equal to:

$V_{cmp}$  6 + =  $V_{ref}$  + VQ27 where VQ27 is the voltage drop across diode Q27. Diode Q27 is forward biased by current source I14.

Assuming that the difference between the voltage drop across diodes VQ27 and VQ28 is negligible, when  $V_{mp}(t)$  is less than  $V_{ref}$ ,  $V_{cmp}$  6 - will be less than  $V_{cmp}$  6 + and the output of comparator CMP6 will be high signifying that the junction temperature of the MOSFETs has not risen the allowable amount and, therefore, a trip condition is not present. Again, assuming that the difference between the voltage drop across diodes VQ27 and VQ28 is negligible, when  $V_{mp}(t)$  is greater than  $V_{ref}$ ,  $V_{cmp}$  6 - will be greater than  $V_{cmp}$  6 + and the output of the comparator will be low signifying that the junction temperature of the MOSFETs has risen the allowable amount and, therefore, a trip condition is present.

When MP is low (i.e., saturated transistors output of invertor INV1 of logic circuit 44 to be discussed below) circuit section 42 is disabled due to the fact that the imv(t) current is diverted through the MP line away from circuit section 42. However, when MP is high (open collector) circuit section 42 operates as described above since none of the imv(t) current will flow into the MP line.

Logic circuit 44 uses the various input signals, i.e., MP ENA, MP TRIP,  $I^2RC$  TRIP and the  $C_{com}$  input from ASIC 12, and provides appropriate output signals, i.e., CMD, MP and TRP, required to coordinate the operation of the other functional circuit sections of ASIC 14. Logic circuit 44 also provides a trip latch feature in which a latch sets upon a trip indication, turning the controller off, and remains set until a reset signal is applied.

As stated supra, the  $C_{com}$  input is the only operator controllable input signal driven by the supply ASIC 12. The  $C_{com}$  input has the following three functions:

- 1) C<sub>com</sub> = High (open collector of photo-transistor); controller off

- 2) C<sub>com</sub> = High; controller reset after trip

- 3) C<sub>com</sub> = Low (photo-transistor saturation voltage); controller on

The  $C_{com}$  signal, along with band gap current source 11 is tied to the inverting input of comparator CMP1 with the non-inverting input connected to  $V_{ref}$ . Comparator CMP1 has approximately 0.5V hysteresis designed into it so that the lower threshold is  $V_{ref}$  and the upper threshold is  $V_{ref} + 0.5$ . The collector of photo-transistor C is tied to the  $C_{com}$  pin P17. When the LED portion of the opto-isolator is off, no collector current flows through the photo-transistor and the inverting terminal of comparator CMP1 is pulled up by current source 11 to approximately one diode drop below VS2. When the voltage at the inverting terminal of comparator CMP1 is higher than the upper voltage threshold at the non-inverting terminal ( $V_{ref} + 0.5V$ ), the output of comparator CMP1 is low. When the LED portion of the opto-isolator is on, the photo-transistor is saturated with a collector current of 150u A pulling the inverting input of comparator CMP1 below the lower threshold voltage of the non-inverting input ( $V_{ref}$ ) and forcing the output of CMP1 high. The output of CMP1 is tied to the B input of gate NAND 2 and

the A input of gate NAND 3.

15

20

30

45

55

Capacitor Clat is tied to the positive terminal of band gap current source I2, the negative terminal of band gap current source I3 and the inverting terminal of comparator CMP2. When the output of gate NAND 4 is low, current source I2 is off and source I3 discharges capacitor Clat pulling it to approximately one diode voltage drop above GND. When the voltage at capacitor Clat, the inverting terminal of comparator CMP2, falls below the voltage at the non-inverting terminal (V<sub>ref</sub>) the output of comparator CMP2 goes high. When the output of gate NAND 4 is high, current source I2 is on and a net current of I2-I3 charges capacitor Clat pulling it to approximately one voltage drop below VS2. When the voltage at capacitor Clat, the inverting terminal of comparator CMP2, rises above the voltage at the non-inverting terminal (V<sub>ref</sub>), the output of comparator CMP2 goes low. Since capacitor Clat is being charged and discharged by constant current sources, the delta time (dT) required to cause a delta change of the voltage (dV) across capacitor Clat is as follows:

```

gate NAND 4 output = low (Clat discharge):

dT = Clat * dV/I3

gate NAND 4 output = high (Clat charge):

dT = Clat * dV/(I2-I3)

```

If the voltage across capacitor Clat is fully discharged to one diode drop above GND (0.7V), the time required to raise the voltage to  $V_{ref}$  (3.25V) when the output of gate NAND 4 goes high is as follows:

```

dT = Clat * (3.25V-0.7V)/(50u A - 5u A).

With a typical value of Clat in a 28VDC controller of 0.0027u F;

```

dT = 0.0027u F \* (3.25V-0.7V)/(50u A - 5u A) = 153 u S.

If the voltage across capacitor Clat is fully charged to one voltage drop below VS2 (6.8V), the time required to discharge capacitor Clat to  $V_{\text{ref}}$  when the output of gate NAND 4 goes low is as follows:

```

dT = Clat * (6.8V - 3.25V)/5 u A

```

dT = 0.0027u F \* (6.8V - 3.25V)/5u A = 1.917m S.

Thus the set and reset time delay of the trip latch within logic circuit 44 is provided by off-IC mounted capacitor Clat. The set and reset time delay enhances noise immunity by making any noise spikes of a duration less than the set and reset time delays unable to change the state of the trip latch.

In the off state the inverting terminal of comparator CMP1 is pulled high by current 11 so that the output of CMP1 and inputs B of gate NAND 2 and A of gate NAND 3 are low. This results in a high output of NAND2 and NAND 3. With regard to NAND 2 the output of invertor INV2 will be low. This is tied to the ENABLE of opamp OP1 and the controller is off.

With regard to gate NAND 3, since the controller is in the off state the outputs of comparator CMP7 of the I²RC section 32 (I²RC TRIP) and comparator CMP6 of the MOSFET Protection section 42 (MP TRIP) are high representing a no trip condition, so the output of NAND 4 is low with current source I2 off. Current source I3 pulls the inverting terminal of comparator CMP2 to one diode drop above ground making the output of CMP2 high and the output of invertor INV3 low. The INV3 output is tied to the opto-isolator drive section 38 TRP line with the low signifying that there is no trip signal to be sent to Supply ASIC 12. The output of invertor INV3 is also tied to input B of NAND 3.

The output of comparator CMP2 (high) is also tied to the A inputs of NAND 1 and NAND 2. The input B of NAND 2, as stated above, is low so that input A has no effect in this state. With respect to gate NAND 1, since the controller is off no voltage is developed across the shunt so that the output of comparator CMP5 is low. The output of NAND 1 then is high which is inverted to low through INV1 with the result that the MOSFET Protection section 42 is disabled.

In the off state the latch is reset, the MOSFET Drive and Current Limiting section is turned off, the TRIP signal is low and the MOSFET Protection section is disabled.

There are two distinct states when the controller is turned on, the first with load current less than two thirds of the current limit level and the second with the load current greater than two thirds of the current limit level. The MOSFET Protection section is enabled only when the load current is greater than two thirds of the current limit level in order to avoid the possibility of nuisance tripping while the MOSFETs are turning on.

When the controller is turned on, the output of comparator CMP1 goes high so that inputs B of NAND 2 and A of NAND 3 are high. With respect to NAND 2 since, as stated above, the input A of NAND 2 is high, the output goes to low which is inverted to high by invertor INV2 thereby enabling op-amp OP1 turning on the controller.

With respect to NAND 3, whose input A is high since its input B, as stated in the description of the off state, it remains with a high output.

Looking at the inputs of NAND 1 since nothing in the latch section changed state, i.e., the output of comparator CMP2 remains high, if the controller is conducting current below the two thirds threshold the output of comparator CMP5 is low along with the input B of NAND 1. The output of NAND 1 is high which is inverted

to low by INV1 which results in the MOSFET Protection section being disabled. If the controller is conducting current above the two thirds threshold the output of comparator CMP5 is high along with input B of NAND 1. The output of NAND 1 will then be low which is inverted to high by INV1 and thereby the MOSFET Protection Circuit 42 is enabled.

As stated above, turning the controller on puts a high on input A of NAND 3. When no trip condition occurs the inputs A, B and C of NAND 4 are all high. If a trip occurs then one of inputs A and C of NAND 4 will turn to a low and the output of NAND 4 will go high. This turns on current source I2, to charge capacitor Clat. When Clat gets above  $V_{ref}$  the output of comparator CMP2 goes low. The output of comparator CMP2 is tied to inputs A of NAND 1 and NAND 2 which turns the outputs of both gates to a high which are inverted to low by inverters INV1 and INV2 respectively. When the output of invertor INV2 goes low the controller shuts off and when the output of invertor INV1 goes low the MOSFET Protection section is disabled.

When the output of comparator CMP2 turns low the output of inverte INV3 goes high thereby turning on the LED portion of the trip opto-isolator T, through the Opto-Isolator Drive section, sending the trip signal to Supply ASIC 12. That same high is fed back to input B of NAND 3 forcing the output to go low which sets the latch. With the controller turned off due to a trip condition the previous trip signal at either of inputs A and C of NAND 4 can be removed but the controller will remain latched off because of the low on input B of NAND 4.

In order to reset the controller, the output of CMP must change to a low via the  $C_{com}$  input which will put the input A of NAND 3 low turning the input B of NAND 4 high. Provided both the  $I_2$ RC TRIP and MP TRIP signals have returned to high states signifying no trip condition present, the output of NAND 4 will go low resetting the latch.

20

30

35

40

45

55

As described above, the solid state power controller provides means for controlling load current through an isolated, solid state, high side switch (turn on and off), through a COMMAND input line. The controller provides a means for tripping in accordance with a specified trip time vs load current curve, for limiting current flow through the load and for protecting the solid state switch from damage due to excessive power dissipation during current limiting. Trip conditions are latched keeping the controller off until a reset signal is applied through the COMMAND input line. The controller also provides a STATUS output reflecting load voltage or current and trip output signals giving an indication of the state of the controller and the load.

The COMMAND, STATUS and TRIP signals operate in accordance with the truth table shown in Table 1 in which 1 = TTL High and 0 = TTL low.

Table 1

|  | COMMAND | STATUS | TRIP | CONTROLLER CONDITION                                        |

|--|---------|--------|------|-------------------------------------------------------------|

|  | 0       | 0      | 0    | Controller off/reset                                        |

|  | 1       | 0      | 0    | Controller on, load current/voltage below circuit threshold |

|  | 1       | 1      | 0    | Controller on, load current/voltage above circuit threshold |

|  | 1       | 0      | 1    | Controller tripped                                          |

Controllers made in accordance with the invention containing solid state sensors and switches coupled with integrated circuit logic can be conveniently disposed in a sealed package and can be remotely mounted near the load they are protecting resulting in significant reduced power line cable weight and bulk. The solid state components significantly increase switching life as compared to conventional circuit breakers. Also, such controllers provide a means for switching high voltage DC, due to the availability of high voltage solid state switch components, not available using mechanical approaches. Such controllers can provide computer controlled load switching while maintaining current overload protection, i.e., they follow selected trip time vs. load current curves such as the standard MS3320 trip time vs. load current relationships thereby enabling optimization of wire size and current rating. The STATUS and TRIP feedback allows continuous monitoring, e.g., via a computer, of each controller circuit. The STATUS can be configured to monitor voltage at the load output terminal or current flow through the controller.

In accordance with the invention, means are provided to facilitate in-application adjustment (programm-ability) of some of the features mentioned herein, by means external to the sealed package. As stated supra, these features include, but are not limited to, the I²RC circuit, the Current Limit circuit and MOSFET Protection circuit. The means for calibrating the performance of these features for a specific application has been described above. The following description relates to modifying the performance of the features through the use

of external components connected outside of the sealed package. This enables the protection features of a single unit to be customized for the requirements of any one of various different circuits.

With reference to Figs. 1 and 5, it can be seen that four additional I/O lines are added to the circuit of Fig. 5 to facilitate external programming. These I/O lines are designated DTA, CLA1, CLA2 and MPA. Unlike control signals COMMAND, STATUS and TRIP these lines are not TTL compatible and are electrically referenced to ASIC 14. I/O line DTA is used in conjunction with the LOAD terminal to facilitate external programming of the I²RC circuit, I/O lines CLA1 and CLA2 are used for external programming of the Current Limit level and line MPA is used in conjunction with the LOAD terminal for external adjustment of the MOSFET Protection Circuit.

As mentioned above, the operation of the  $I^2RC$  circuit is set by off-IC components  $R_s$ ,  $R_{lv}$ ,  $C_t$ ,  $R_l$  and  $C_l$ . Additionally,  $R_{t1}$  and  $R_{t2}$  are used to calibrate the performance to the nominal set point (see Fig. 3). Of these components  $R_l$  and  $C_l$  are used to set the shape of the trip time vs. load current curve, similar to Fig. 4. Resistor  $R_l$  is used to set the ultimate trip level and  $R_l$  and  $C_l$  together determine the time constant. As stated above, the component values are sized to create a curve which is analogous to the temperature rise of the circuit wire. In some applications, other factors such as power dissipation within the load or current output capability of the supply may make it desirable to shorten the time which an overload current will be carried before the trip occurs. It may also be beneficial to relocate the ultimate trip level for particular loads which have steady state current requirements slightly above or below a standard device rating. The  $I^2RC$  performance modification can be accomplished with the proper selection of  $R_l$  and  $C_l$ .

To accomplish this externally to a sealed package  $R_i$  and  $C_i$  are segmented into  $R_{ii}$ ,  $C_{ii}$  (internal to the package) and  $R_{le}$ ,  $C_{le}$  (external to the package).  $R_{le}$  and  $C_{le}$  are connected in parallel to  $R_{ii}$  and  $C_{ii}$  by connecting  $R_{ie}$  and  $C_{le}$  between I/O line DTA and the LOAD terminal. The DTA line is connected to  $R_{ii}$  and  $C_{ii}$  at P31 as shown in Fig. 6. The ground side of  $R_{ii}$  and  $C_{ii}$  is electrically connected to the LOAD terminal therefore the LOAD terminal is used as the return for  $R_{ie}$  and  $C_{ie}$  to reduce the total number of I/O pins required. When manufactured this way the internal, off-IC components  $R_{ii}$  and  $C_{ii}$  are used as default values and fix the lower limits of programmability.  $R_{ii}$  fixes the lower limit of ultimate trip,  $C_{ii}$  along with  $R_{ii}$  fix the lower limit of the trip delay.

The performance of the circuit is still determined in the same manner developed above in equation 10. However, now the "effective"  $R_i$  and  $C_i$  is used along with the internal default components  $R_{ii}$  and  $C_{ii}$  to calculate the external programming component values  $R_{ie}$  and  $C_{ie}$  for the desired  $I^2$ t performance where:

$$R_{ie} = (R_{ii} * R_{i})/(R_{ii} - R_{i})$$

$C_{ie} = C_{i} - C_{ii}$

As an example, let the range of operation desired for I²t performance be described by the curves of Fig. 7 which describe a range of nominal operation. The ultimate trip programmable range is from 100% to 125% of the device current rating while the time constant for each limit curve shown is 1.55 sec. and 9.75 sec., respectively. The lower limit curve A performance will define the default, internal component values per equation 10.

$$R_i = R_{ii} = 24.3 \text{ M Ohms}$$

$C_i = C_{ii} = 63.8 \text{ nF}$

To achieve the performance defined by the upper curve B limit, equation 10 yields the following:

$$R_i = 15.6 \text{ M Ohms}$$

$C_i = 625 \text{ nF}$

This results in external programming values of:

15

30

35

40

45

50

55

$$R_{ie}$$