① Veröffentlichungsnummer: 0 623 866 A2

# EUROPÄISCHE PATENTANMELDUNG

(21) Anmeldenummer: 94106982.5 (51) Int. Cl.<sup>5</sup>: **G05F** 3/24

22) Anmeldetag: 04.05.94

(12)

3 Priorität: 07.05.93 DE 4315296

(43) Veröffentlichungstag der Anmeldung: 09.11.94 Patentblatt 94/45

Benannte Vertragsstaaten:

DE FR GB IT

71 Anmelder: SIEMENS AKTIENGESELLSCHAFT Wittelsbacherplatz 2 D-80333 München (DE)

Erfinder: Draxelmayr, Dieter, Dr. Dipl.-Ing. Tschinowitscherweg 46 A-9500 Villach (AT)

- Stromquellenanordnung zur Erzeugung mehrfacher Referenzströme.

- Für die Versorgung verteilter Schaltungsanordnungen mit vorzugsweise gleichen Strukturen mit Referenzströmen wird eine Stromquellenanordnung mit einer Stromquelle vorgeschlagen, die einen Bezugsstrom erzeugt, der mit Hilfe einer Mehrzahl parallel liegender Transistoren, die räumlich beieinan-

der angeordnet sind, in eine der Mehrzahl entsprechende Zahl Referenzströme aufgeteilt wird. Die Transistoren sind in einer Regelung für den Bezugsstrom, d. h. für die Summe der Referenzströme einbezogen und sind ausgangsseitig an die verteilten Schaltungsanordnungen angeschlossen.

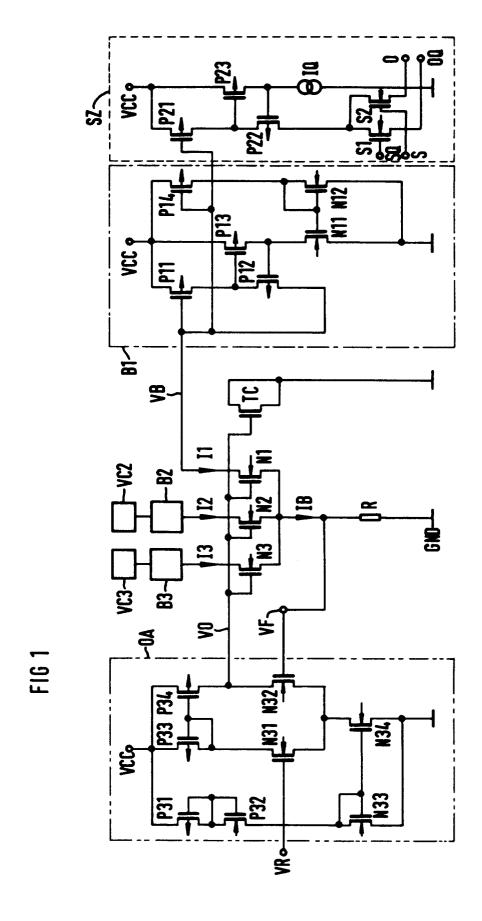

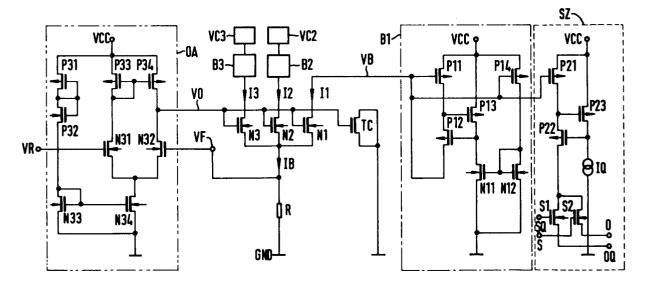

FIG 1

20

Die Erfindung betrifft eine Stromquellenanordnung zur Erzeugung mehrfacher Referenzströme für verteilte Schaltungsanordnungen mit einer Stromquelle, die einen Bezugsstrom erzeugt.

Stromquellen zur Erzeugung von Referenzbzw. Bezugsströmen sind hinlänglich bekannt, beispielsweise aus dem Buch Tietze/Schenk: Halbleiter-Schaltungstechnik, Springer-Verlag, 7. Auflage, 1985, Seite 356 ff. Die in der vorgenannten Literaturstelle beschriebenen Präzisions-Stromquellen enthalten einen Operationsverstärker, der ausgangsseitig einen Transistor steuert, dessen einer Ausgangsanschluß einerseits über einen Widerstand an Bezugspotential und andererseits an den Rückkopplungseingang des Operationsverstärkers gelegt ist. An dem positiven Eingang des Operationsverstärkers liegt eine Referenzspannung. Am freien Ausgang des Transistors wird eine Last angeschaltet. Die Ausgangsspannung des Operationsverstärkers stellt sich dabei so ein, daß die Spannung an dem Widerstand gleich der Referenzspannung wird, so daß der Ausgangsstrom präzise definiert wird.

In Anwendungsschaltungen mit mehrfach gleichen Strukturen, wie z. B. einem Mehrfach-DA-Umsetzer ist eine zuvor beschriebene Präzisionsstromquelle entsprechend mehrfach erforderlich, was sehr aufwendig ist. Üblicherweise erfolgt die Stromversorgung derartiger Mehrfachstrukturen deshalb mit Hilfe einer Stromspiegelschaltung, bei der an zentraler Stelle ein Referenzstrom in einen als Diode geschalteten MOS-Transistor geleitet wird. Der Referenzstrom wird häufig mittels einer externen Quelle oder mit Hilfe eines Widerstandes erzeugt. Weitere zu dem als Diode geschalteten MOS-Transistor gleichartige Transistoren werden dann als Stromguellen in den einzelnen Schaltungsanordnungen der Mehrfachstrukturen an das erhaltene Referenzpotential geschaltet. Durch die Anordnung der Stromquellen mit Hilfe eines Referenztransistors, der als Diode geschaltet ist, und der weiteren, den Mehrfachstrukturen zugeordneten Transistoren ergibt sich ein (räumlich) verteilter Stromspiegel. Die Anpassung (matching) der Mehrfachstrukturen im Hinblick auf gleiche oder vergleichbare Eigenschaften sind aufgrund des verteilten Stromspiegels und der verteilten Schaltungsanordnungen schlecht definiert und können zu Verkopplungen über die gemeinsame Vorspannungsleitung führen.

Der Erfindung liegt die Aufgabe zugrunde, eine Stromquellenanordnung anzugeben, mit der die Anpassungseigenschaften verteilter Schaltungsanordnungen verbessert und gegenseitige Verkopplungen der verteilten Schaltungsanordnungen verringert werden können. Weiterhin soll eine Verwendung für eine derartige Anordnung angegeben werden.

Diese Aufgabe wird durch die Merkmale der Patentansprüche 1 und 8 gelöst.

Die Erfindung hat den Vorteil, daß durch die Aufteilung des Bezugsstroms mit Hilfe parallel liegender, räumlich beieinander angeordneter Transistoren, die zudem in eine Regelung für die Summe der Referenzströme einbezogen sind, die Anpassungseigenschaften (matching) durch die lokal in einem begrenzten Gebiet beieinander angeordneten Transistoren verbessert werden. Weiterhin werden die verteilten Schaltungsanordnungen weitgehend entkoppelt, da Störungen auf einer Leitung praktisch nicht auf eine andere Versorgungsleitung für eine andere der verteilten Schaltungsanordnungen überkoppeln kann. Somit ergeben sich bei weitgehender Entkopplung der verteilten Schaltungsanordnungen verbesserte globale Anpassungseigenschaften. Unterschiedliche Technologiegradienten können sich damit nicht stark negativ auswirken.

Ausgestaltungen der Erfindung sind in Unteransprüchen gekennzeichnet.

Die Erfindung wird nachfolgend anhand eines Ausführungsbeispiels näher erläutert, das in Figur 1 dargestellt ist.

Die in der Figur gezeigte Stromquellenanordnung wird z. B. von einer positiven Spannung versorgt, wobei die Klemmen VCC auf 5 V liegen, während das Bezugspotential GND auf 0 V liegt.

Eine an einem als Operationsverstärker ausgebildeten Schaltungsteil OA an der Klemme VR anliegende Referenzspannung und ein Widerstand R bestimmen einen Bezugsstrom IB. Die Klemme VR ist mit einem Eingang eines Transistors N31 verbunden, der in Verbindung mit einem Transistor N32 einen Differenzverstärker bildet. Dieser Differenzverstärker wird von einer Stromquelle aus den Transistoren P31, P32, N33 und N34 versorgt. Der durch die Transistoren P31 und P32 definierte Strom wird dabei durch den Stromspiegel aus N33 und N34 in den Differenzverstärker gespiegelt. Im Lastkreis der Differenzverstärkertransistoren N31 und N32 sind Transistoren P33 und P34 angeordnet, die ebenfalls als Stromspiegel geschaltet sind. Der Verbindungspunkt der Ausgangskreise der Transistoren N32 und P34 bildet den Ausgang VO des Operationsverstärkers OA.

Der Ausgang VO steuert eine Mehrzahl parallel geschalteter Transistoren, die im Ausführungssbeispiel durch die Transistoren N1 bis N3 dargestellt sind. Ein gemeinsamer Ausgangsanschluß jeder der Transistoren ist mit einem Anschluß des Widersstands R verbunden, dessen anderer Anschluß auf Bezugspotential GND liegt. Der Verbindungspunkt der Transistoren N1 bis N3 mit dem Widerstand R ist andererseits mit dem Steuereingang des Transistors N32 verbunden und bildet den Rückkoppelungseingang VF des Operationsverstär-

55

25

kers OA. In Betrieb arbeitet der Regelkreis so, daß das Potential VF am Steuereingang des Transistors N32 dem Potential an der Klemme VR entspricht, d. h., daß am Widerstand R die Referenzspannung anliegt. Referenzspannung und Widerstand R bestimmen präzise den Bezugsstrom IB.

Der Bezugsstrom IB wird mit Hilfe der Mehrzahl parallel liegender Transistoren, im Ausführungsbeispiel mit Hilfe der Transistoren N1 bis N3 in drei Referenzströme I1 bis I3 geteilt. Die Referenzströme I1 bis I3 dienen dann ihrerseits zur Versorgung verteilter Schaltungsanordnungen B1 bis B3, von denen aus Gründen der Übersichtigkeit lediglich die Schaltungsanordnung B1 detailliert dargestellt sind. Es ist selbstverständlich, daß den Schaltungsanordnungen B1 bis B3 weitere Schaltungsteile, z. B. SZ, VC2 bzw. VC3, die ihrerseits ebenfalls verteilt sein dürfen, nachgeschaltet sein können. Man kann deshalb auch den jeweiligen Schaltungsteil B1, B2 oder B 3 zusammen mit dem jeweils nachgeschalteten Schaltungsteil SZ, VC2 oder VC3 als jeweilige verteilte Schaltungsanordnung ansehen.

Die drei Transistoren N1 bis N3 sind räumlich beieinander, vorzugsweise eng beieinander angeordnet, so daß für die Referenzströme I1 bis I3 die Anpassungseigenschaften in einem lokal eng begrenzten Gebiet ausschlaggebend sind. Eventuelle Störeinflusse wirken sich auf jeden der Transistoren in gleicher Weise aus. Die auf diese Weise gut definierten Referenzströme werden zu den verteilten Schaltungsanordnungen, z. B. drei Digital-Analog-Umsetzern geleitet. Insbesondere bei gleichen Strukturen, z. B. einem Dreifach-Digital-Analog-Umsetzer können mit gleich ausgelegten Transistoren N1 bis N3 aus dem zentralen Bezugsstrom IB drei gut definierte und angepaßte Referenzströme I1 bis 13 erzeugt werden, die einen optimalen Gleichlauf der verteilten Schaltungsanordnungen gewährleisten. Weiterhin wird mit einer derartigen Referenzstromerzeugung sichergestellt, daß Störungen auf einer Leitung, d. h. Störungen bezuglich einer der verteilten Schaltungsanordnungen praktisch nicht auf die anderen verteilten Schaltungsanordnungen überkoppeln können.

Eine weitere Verbesserung bei der Erzeugung der Referenzströme I1 bis I3 sieht vor, daß vom Ausgang VO des Operationsverstärkers OA, der die Steueranschlüsse der die Referenzströme erzeugenden Transistoren N1 bis N3 steuert, ein als Kapazität geschalteter Transistor TC nach Bezugspotential geschaltet ist. TC übt eine Glattungsfunktion aus.

Jeder einzelne Referenzstrom I1 bis I3 wird in der durch ihn versorgten verteilten Schaltungsanordnung lokal einer Stromquellenanordnung zugeführt, wie sie beispielsweise in dem Block B1 dargestellt ist, und steuert diese. Die Blöcke B2 und B3 sind in gleicher Weise wie B1 aufgebaut.

Die lokal in der jeweiligen verteilten Schaltungsanordnung realisierte Stromquelle wird im Ausführungsbeispiel anhand des Blockes B1 beschrieben. Die Stromquelle besteht im wesentlichen aus den Transistoren P11 und P12, die mit ihren Ausgangskreisen in Reihe geschaltet sind und eine Kaskodestufe bilden. Ein Anschluß des Transistors P11 wird von der Klemme VCC versorgt. Der das Potential VB führende Anschluß des Transistors N1 ist mit dem Steuereingang des Transistors P11 und mit einem Ausgangsanschluß des Transistors P12 verbunden. P11 ist ein p-Kanal-Transistor, der vergleichsweise groß ausgelegt ist. Der Transistor P12 hat im wesentlichen die Aufgabe, den Verbindungspunkt des Transistors P11 mit dem Transistor P12 vom Steuereingang des Transistors P11 bzw. dem damit verbundenen Ausgangsanschluß des Transistors P12 weitgehend zu entkoppeln und die statische Kennlinie der Stromquelle durch Vergrößerung des differentiellen Ausgangswiderstands zu verbessern. Damit werden Störeinflüsse auf den Steueranschluß des Transistors P11 und damit auf den Referenzstrom I1 verringert und die Gateanschlüsse der Transistoren P13 und P23 auf jeweils gleiches Potential gelegt. Fur die Entkopplung ist eine Regelschleife vorgesehen, die im wesentlichen aus den Transistoren P12 und P13 besteht. Dazu ist der an VCC angeschlossene Transistor P3 mit seinem Steueranschluß am Verbindungspunkt der Transistoren P11 und P12 angeschlossen, während der Steueranschluß des Transistors P12 am Ausgang des Transistors P13 angeschlossen ist. P13 wird von der aus den Transistoren P14 und N11 sowie N12 gebildeten Stromguelle versorgt. Dazu wird P14 vom Potential VB, d. h. dem Ausgangsanschluß des Transistors N1 gesteuert. Der von VCC durch P14 fließende Strom wird mit Hilfe der Transistoren N12 und N11 in den Kreis von P13 gespiegelt.

Dem Block B1 nachgeschaltet ist eine Schaltungsanordnung SZ, die beispielsweise eine Stromzelle für einen Digital-Analog-Umsetzer bildet. Die Stromquelle ist im Ausführungsbeispiel vorteilhaft ähnlich wie der Kreis B1 aufgebaut. Dazu entsprechen die Transistoren P21 bis P23 den Transistoren P11 bis P13. Die den Transistor P23 versorgende Stromquelle IQ ist z. B. entsprechend wie die Transistoren P14, N11 und N12 ausgebildet. Anders als der Transistor P12 ist der eine Ausgangsanschluß des Transistors P22 mit dem gemeinsamen Verbindungspunkt der Ausgangskreise zweier Schaltertransistoren S1 und S2 verbunden. S1 und S2 werden von antivalenten bzw. komplementären Signalen S und SQ gesteuert. Entsprechend führen die Ausgangsanschlüsse O und OQ der Schaltertransistoren S1 und S2 abwechselnd den durch P21 und P22 fließenden Strom. Durch

55

5

15

20

25

30

40

45

50

die in gleicher Weise wie beim Block B1 mit Hilfe des Regeltransistors P23 vorgenommene Entkopplung des Verbindungspunktes der Transistoren P21 und P22 vom Verbindungspunkt des Transistors P22 mit den Transistoren S1 und S2 können sich transiente Schaltvorgänge der Schaltertransistoren S1 und S2 höchstens in geringem Maße auf die Ansteuerung von P21 und damit auf den Referenzstrom I1 auswirken.

Funktionell wird also der Referenzstrom I1 über den Transistor P12 in den Transistor P11 eingespeist, der mit P21 einen Stromspiegel bildet.Durch die vorzugsweise gleiche Struktur des Blocks B1 und der in Figur 1 dargestellten nachgeschalteten Stromzelle SZ, insbesondere die darin ausgeführte Regelschleife wird erreicht, daß die Drainpotentiale der Transistoren P11 und P21 weitgehend gleich sind. Somit wird ein optimaler Gleichlauf dieser beiden Schaltungsteile erzielt. Es ist selbstverständlich, daß dem Block B1 weitere Stromzellen in gleicher Weise nachgeschaltet werden können, die beispielsweise für einen Digital-Analog-Umsetzer vorgesehen sind. Dies ist schematisch anhand der den Blöcken B2 und B3 nachgeschalteten Blöcke VC2 und VC3 dargestellt, die dementsprechend dann jeweils einen Digital-Analog-Umsetzer repräsentieren.

## Patentansprüche

Stromquellenanordnung zur Erzeugung mehrfacher Referenzströme für verteilte Schaltungsanordnungen mit einer Stromquelle, die einen Bezugsstrom erzeugt,

# dadurch gekennzeichnet,

daß der Bezugsstrom (IB) mit Hilfe einer Mehrzahl parallel liegender Transistoren (N1 bis N3), die räumlich beieinander angeordnet sind, in eine der Mehrzahl entsprechende Zahl Referenzströme (I1 bis I3) aufgeteilt wird.

2. Anordnung nach Anspruch 1,

# dadurch gekennzeichnet,

daß die Transistoren (N1 bis N3) vom Ausgang (VO) eines Operationsverstärkers (OA) gesteuert werden, dessen einer Eingang an einem Referenzpotential (VR) liegt und dessen zweiter Eingang (VF) an einem gemeinsamen Verbindungspunkt der Transistoren und eines Widerstandselements (R) liegt.

3. Anordnung nach Anspruch 1 oder 2,

# dadurch gekennzeichnet,

daß die Transistoren (N1 bis N3) gleich ausgebildet sind.

**4.** Anordnung nach einem der vorhergehenden Ansprüche,

#### dadurch gekennzeichnet,

daß parallel zu den Transistoren (N1 bis N3) eine Kapazität (TC) geschaltet ist.

Anordnung nach einem der vorhergehenden Ansprüche.

#### dadurch gekennzeichnet,

daß jeder der Transistoren (N1 bis N3) ausgangsseitig mit einer der verteilten Schaltungsanordnungen verbunden ist, welche jeweils eine von dem zugeordneten Transistor gesteuerte Stromquellenanordnung (P11, P12; P21, P22) aufweist.

6. Anordnung nach Anspruch 5,

## dadurch gekennzeichnet,

daß die Stromquellen als Kaskodestufen ausgebildet sind und daß der Ausgang jedes der Transistoren (N1 bis N3) einen ersten Transistor (P11) der Kaskodestufe steuert und mit einem Ausgangsanschluß des zweiten Transistors (P12) verbunden ist, der mit einem Regeltransistor (P13) zur Regelung des Potentials an dem Verbindungspunkt des ersten und des zweiten Transistors (P11, P12) verbunden ist.

Anordnung nach einem der vorhergehenden Ansprüche,

## dadurch gekennzeichnet,

daß jeder der Referenzströme (I1 bis I3) in die jeweils zugeordnete verteilte Schaltungsanordnung (B1, SZ; B2, VC2; B3, VC3) gespiegelt wird.

35 **8.** Verwendung einer Stromquellenanordnung nach einem der Ansprüche 1 bis 7 in einem Mehrfach-Digital-Analog-Umsetzer.

55