## (12)

## **DEMANDE DE BREVET EUROPEEN**

(21) Numéro de dépôt : 95470007.6

(51) Int. Cl.<sup>6</sup>: **G09G 1/16**, H04N 5/46

(22) Date de dépôt : 24.02.95

(30) Priorité: 28.02.94 FR 9402557

(43) Date de publication de la demande : 27.09.95 Bulletin 95/39

84) Etats contractants désignés : **DE FR GB IT**

7) Demandeur: SGS-THOMSON MICROELECTRONICS S.A. 7, Avenue Galliéni F-94250 Gentilly (FR)

(72) Inventeur: Gaigneux, Frédéric Cabinet Ballot Schmit, 18 Place du Forum F-57000 Metz (FR) Inventeur: Lee, Yong-Uk Cabinet Ballot Schmit, 18 Place du Forum F-57000 Metz (FR)

Mandataire: Schmit, Christian Norbert Marie Cabinet Ballot-Schmit, 18 Place du Forum F-57000 Metz (FR)

- (54) Procédé de reconnaissence de standard vidéo, et circuit mettant en oeuvre ce procédé.

- L'invention concerne un procédé de reconnaissance de standard vidéo, caractérisé en ce qu'on mémorise une valeur représentative d'une durée, on produit une valeur de comptage (Q), cette valeur étant incrémentée quand un signal binaire de synchronisation (INCI) est dans un état, et décrémentée quand ce signal est dans l'autre état, on effectue une comparaison de la valeur représentative de la durée et de la valeur de comptage, à un moment donné du signal de synchronisation, et on produit un signal représentatif du standard en fonction du résultat de la comparaison. Ce procédé est mis en oeuvre par un circuit comprenant un microcontrôleur (8), un circuit de détection (18) produisant un signal logique de commande de capture (CAP), un compteur (25) produisant une valeur de comptage (Q), et un registre (24) pour charger la valeur de comptage quand le signal de commande de capture est actif.

EP 0 674 302 A1

10

20

25

30

35

40

45

50

L'invention concerne un procédé de détermination de caractéristiques de signaux de synchronisation, et un circuit mettant en oeuvre un tel procédé. Elle peut trouver son application dans tous les domaines, et notamment dans les domaines impliquant un affichage d'images sur un écran (télévision, informatique). Dans ces derniers, elle servira de préférence au traitement de signaux de synchronisation dédiés au balayage horizontal et au balayage vertical d'un écran de visualisation.

L'invention va être décrite dans le contexte du traitement des signaux vidéo en informatique, sans qu'on puisse y voir une quelconque limitation de la portée de l'invention.

On connaît, dans les signaux vidéo pour visualiser des images sur des écrans cathodiques, des signaux de balayage horizontal, ainsi que de balayage vertical. Le signal de balayage horizontal est un signal appliqué sur des électrodes ou des bobines de déflexion d'un ou plusieurs canons à électrons projetant des électrons d'une cathode vers un écran électroluminescent. Pour constituer une image, on provoque ainsi le balayage de l'écran afin de constituer un certain nombre de lignes empilées les unes en-dessous des autres de haut en bas de l'écran. Chaque ligne est formée d'un certain nombre de points, communément appelés pixels, alignés les uns à côté des autres.

Selon la résolution de l'écran, ainsi que selon les protocoles de visualisation envisagés, le nombre de lignes visualisées sur l'écran et le nombre de points affichés par ligne varient. Par ailleurs, la fréquence de rafraîchissement des images sur l'écran dépend également des standards utilisés et des qualités recherchées. Par exemple, le standard VGA3 (Video Graphics Array) permet d'afficher 480 lignes de 640 points, la fréquence de rafraîchissement d'écran étant de 60 Hertz et la fréquence des lignes de 31.5 kHz. Le standard XGA (eXtented Graphics Array) permet d'afficher 768 lignes de 1024 points, avec un fréquence de rafraîchissement d'écran de 43.48 Hz et une fréquence de ligne de 35.52 kHz.

Pour permettre un affichage satisfaisant d'une image il est nécessaire, en plus de l'information à afficher transmise sous forme de signaux électriques, de fournir aux électrodes de déflexion des signaux de synchronisation afin de repérer les débuts de signe et les fins d'écran.

Il existe donc deux types de signaux de synchronisation: des signaux de synchronisation horizontale et des signaux de synchronisation verticale. Ces signaux sont des signaux logiques impulsionnels définis par trois caractéristiques fondamentales qui sont la polarité de leurs impulsions (positive ou négative), la fréquence de récurrence de ces impulsions, et la durée de ces impulsions.

Typiquement, les signaux de synchronisation horizontale ont des impulsions d'une durée de quelques microsecondes et une fréquence de récurrence de quelques dizaines de kiloHertz. Les signaux de synchronisation verticale ont des impulsions d'une durée de quelques dizaines de microsecondes et une fréquence de récurrence de quelques dizaines de Hertz.

Pour un même standard, on pourra avoir des signaux de synchronisation horizontale et verticale de polarités identiques ou opposées.

Ces signaux de synchronisation sont transmis sur des lignes de transmission séparées ou sur une même ligne de transmission. Dans ce dernier cas, on parle de signal composite, celui-ci comprenant à la fois des impulsions de synchronisation verticale et celles de synchronisation horizontale (standard MAC II par exemple).

Ces signaux de synchronisation sont transmis, suivant le standard, sur la même ligne de transmission que le signal vidéo à afficher ou sur des lignes séparées. Dans ce dernier cas on transmettra par exemple le signal de synchronisation horizontale sur la même ligne que le signal vidéo, et le signal de synchronisation verticale sur une ligne différente. Si le signal de synchronisation est composite, on pourra choisir de n'utiliser qu'une seule ligne de transmission

Suivant le standard utilisé (VGA, XGA, etc.) les signaux de synchronisation auront des caractéristiques données différentes d'un standard à l'autre.

Dans les écrans, outre le matériel d'affichage (électrodes etc.), on trouve des circuits électroniques qui ont pour but de commander ce matériel d'affichage (production des signaux appliqués aux électrodes, de signaux de correction de distorsion, de signaux de commande de gain etc.). Une tendance actuelle est d'intégrer dans les écrans un microcontrôleur programmable pour produire divers signaux de commande tels que ceux décrits ci-dessus. Cette solution permet une plus grande souplesse d'utilisation (par exemple de permettre l'emploi de télécommandes pour régler les paramètres d'affichage).

Classiquement, on filtre les signaux reçus pour séparer les signaux vidéo contenant les informations à afficher et les signaux de synchronisation.

A partir des signaux de synchronisation, un certain nombre de signaux sont produits. Par exemple on doit séparer les impulsions de synchronisation horizontale et verticale dans le cas où le signal reçu est composite. Par ailleurs, les signaux électriques correspondant aux informations à afficher sur une ligne sont référencés par rapport à un niveau de tension dit niveau de noir, ce niveau étant stable durant un intervalle de temps entre la fin de l'impulsion horizontale correspondant à cette ligne et le signal correspondant à l'information à afficher en début de ligne (typiquement cet intervalle de temps est de 10  $\mu S$  à 1 mS). On produit donc un signal impulsionnel qui permet de repérer l'intervalle de temps pendant lequel on peut mesurer le niveau de noir, afin que les

10

15

20

25

30

35

40

45

50

couleurs affichées à l'écran soient stables d'une ligne à l'autre.

On a donc vu que l'écran nécessite des moyens pour produire, à partir du ou des signaux de synchronisation reçus, des signaux de synchronisation compatibles avec le matériel d'affichage et divers signaux logiques ou analogiques de commande. Ces signaux sont fonction du standard utilisé.

Auparavant, on produisait ces signaux en utilisant des circuits discrets ou des ASICs, ces signaux étant par la suite pris en compte par le matériel d'affichage et éventuellement par un microcontrôleur. Ces circuits étaient ou non utilisables avec divers standards. Ces solutions présentent l'inconvénient d'être coûteuses (prix de dévoloppement) et encombrantes (deux circuits distincts si on utilise un microcontrôleur et un ASIC).

Les fabriquants souhaitent, pour des raisons économiques, pouvoir développer des écrans dits multistandards, aptes à afficher des signaux vidéo de standards différents existants, voire à venir, qui soient peu coûteux et peu encombrants.

Dans l'invention, on veut développer un circuit intégré (gain de place et de coût) de traitement des signaux de synchronisation vidéo qui soit utilisable sans qu'on soit lié par la connaissance préalable du ou des standards des signaux vidéo qu'on aura à afficher, et qui pourra s'adapter, dans le futur, à n'importe quel standard qui pourrait apparaître (multistandard).

On se propose donc de développer un circuit intégré comprenant à la fois un microcontrôleur tel qu'on en trouve dans les écrans, et les moyens nécessaires pour reconnaître quel standard est utilisé, et produire les signaux adéquats.

Un tel circuit devra donc offrir les fonctionnalités suivantes :

- détection de présence d'un ou de signaux de synchronisation de type composite ou monofréquentiel,

- détermination de la ou des polarités du ou des signaux de synchronisation recus,

- détermination de la fréquence et la durée des impulsions des signaux de synchronisation recus,

- détermination du standard utilisé à partir des informations ci-dessus,

- extraction de signaux de synchronisation verticale et horizontale à partir d'un signal de synchronisation composite,

- génération d'un signal impulsionnel permettant de synchroniser une acquisition de niveau de noir

Pour ce qui concerne la fréquence des impulsions, il est classique de procéder à sa détermination à l'aide d'un microcontrôleur comprenant un compteur produisant deux valeurs de comptage correspondant à un début et une fin de période. Dans

l'invention, on s'attachera plus particulièrement à la réalisation des autres fonctionnalités, en cherchant à minimiser la charge de travail du microcontrôleur.

L'invention a pour but un procédé de reconnaissance de standard vidéo, caractérisé en ce qu'on mémorise une valeur représentative d'une durée, on produit une valeur de comptage, cette valeur étant incrémentée quand un signal binaire de synchronisation est dans un état, et décrémentée quand ce signal est dans l'autre état, on effectue une comparaison de la valeur représentative de la durée et de la valeur de comptage, à un moment donné du signal de synchronisation, et on produit un signal représentatif du standard en fonction du résultat de la comparaison.

On procédera ainsi à la détection de polarité, à la mesure de durée d'impulsion et à l'extraction de signaux à partir d'un signal composite.

On pourra déterminer simultanément la polarité et la durée des impulsions. La comparaison sera typiquement effectuée par le microcontrôleur, programmé adéquatement.

Suivant la fonctionnalité envisagée, le signal produit sera représentatif d'une caractéristique du standard utilisé (information de polarité par exemple) ou du standard lui-même (ensemble des caractéristiques de polarité, de fréquence, de largeur d'impulsion etc.).

L'invention a également pour but de définir un circuit de mise en oeuvre du procédé décrit ci-dessus.

L'invention concerne donc un circuit de reconnaissance de standard vidéo, caractérisé en ce qu'il comprend au moins une borne d'entrée pour recevoir un signal d'entrée de synchronisation, une borne de sortie pour fournir un signal de sortie de synchronisation, un microcontrôleur, un circuit de détection recevant sur une entrée le signal d'entrée de synchronisation et comportant des moyens pour produire d'une part un signal interne de synchronisation retardé par rapport au signal d'entrée de synchronisation, et d'autre part un signal logique de commande de capture, un compteur cadencé par un signal d'horloge de comptage et produisant une valeur de comptage qui est incrémentée ou décrémentée suivant l'état du signal interne de synchronisation, cette valeur de comptage étant accessible sur un port de sortie parallèle du compteur, un registre comprenant un port d'entrée/sortie parallèle pour charger la valeur de comptage quand le signal de commande de capture est dans un état dit actif.

Ainsi, quand un front sera détecté sur un signal de synchronisation, on chargera dans un registre une valeur de comptage, le chargement se produisant en début ou en fin d'impulsion suivant le type de front détecté et la polarité du signal. La valeur de comptage est représentative de la durée des impulsions et donc de la polarité de celles-ci, du fait qu'une impulsion peut être caractérisée par un changement d'état provisoire et de faible durée par rapport à la durée de la

10

15

20

25

30

35

40

45

50

période correspondant à la fréquence de récurrence des impulsions.

5

Dans un mode de réalisation préféré, le circuit comprendra un circuit de contrôle pour comparer la valeur de comptage à des seuils minimum et maximum, de telle façon que cette valeur de comptage soit bloquée si un seuil est atteint et que le signal d'entrée est à niveau haut ou bas. Il suffira de charger dans le registre, avant de mettre en oeuvre la détection de front, une valeur correspondant à l'un des seuils. Selon lors que, après chargement de la valeur de comptage dans ce registre, la valeur contenue dans le registre est identique ou différente à la valeur chargée initialement, on en déduire que le signal a une polarité positive ou négative.

En ce qui concerne l'extraction de signaux, on comparera la valeur de comptage à une valeur programmée et chargée dans le registre. La valeur programmée sera représentative d'une durée supérieure à la durée d'une impulsion de synchronisation horizontale. Quand la valeur de comptage sera égale à cette valeur programmée, on en déduira qu'on est en présence d'une impulsion de synchronisation verticale, étant entendu que celle-ci se distingue d'une impulsion de synchronisation horizontale par une durée plus importante.

L'invention sera mieux comprise à la lecture de la description qui suit et l'examen des figures qui l'accompagnent. Celles-ci ne sont données qu'à titre indicatif et nullement limitatif de l'invention. Les figures montrent :

- figure 1 : circuit permettant de déterminer les caractéristiques d'un signal de synchronisation vidéo afin de déterminer quel protocole est utilisé,

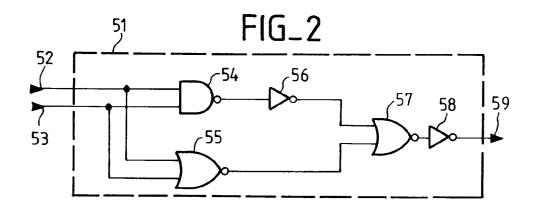

- figure 2 : un circuit destiné à comparer si deux signaux binaires sont égaux (dans le même état) ou différents (états différents),

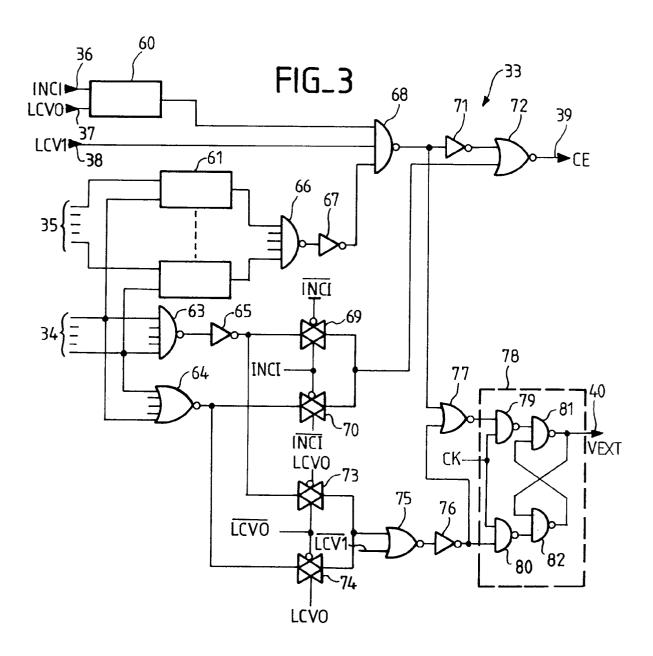

- figure 3 : circuit de contrôle destiné à valider ou non un comptage dans un compteur, et à fournir un signal de synchronisation verticale extrait à partir d'un signal de synchronisation composite,

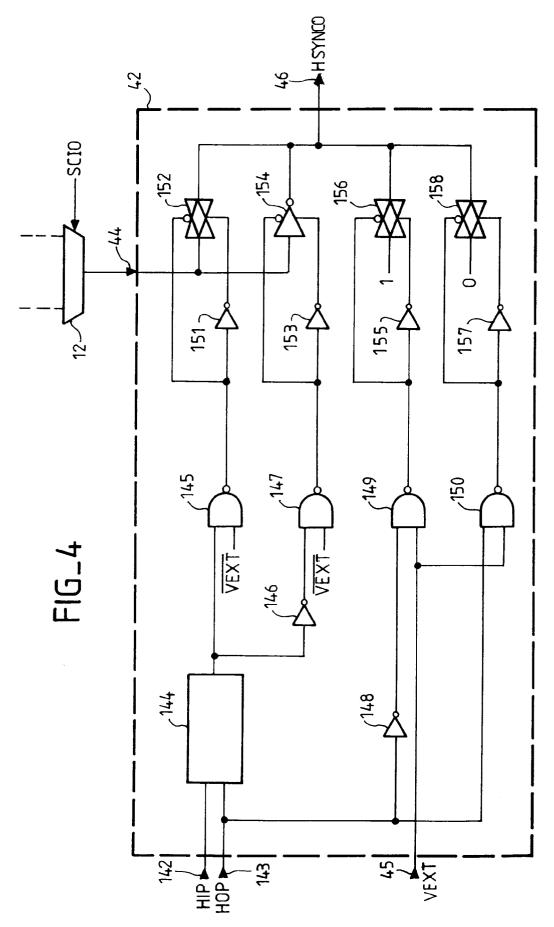

- figure 4 : circuit de sortie de signal destiné à fournir un signal de synchronisation horizontal de manière à ce que celui-ci soit inactif quand, dans le cas d'un signal d'entrée composite, le signal de synchronisation verticale extrait est actif.

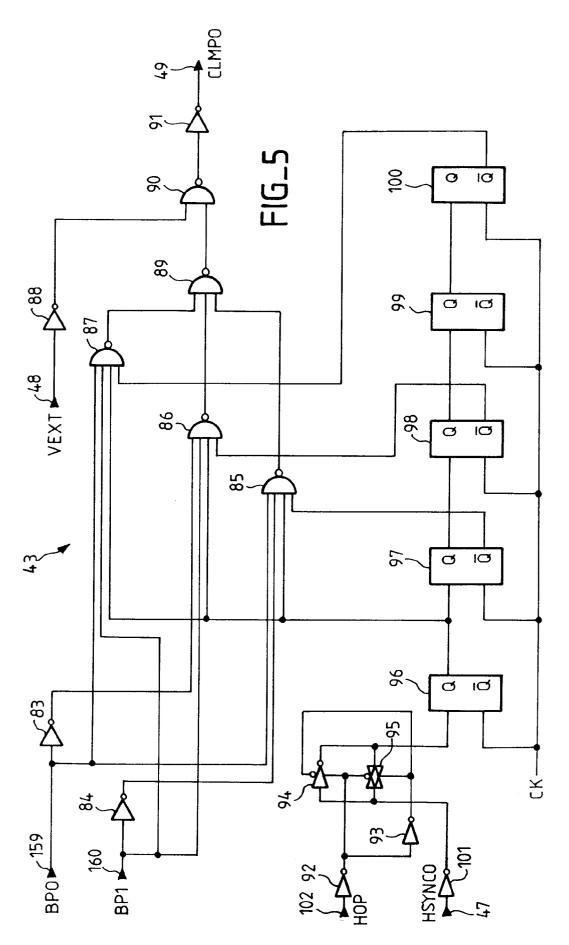

- figure 5 : circuit de génération d'un signal d'acquisition de niveau de noir,

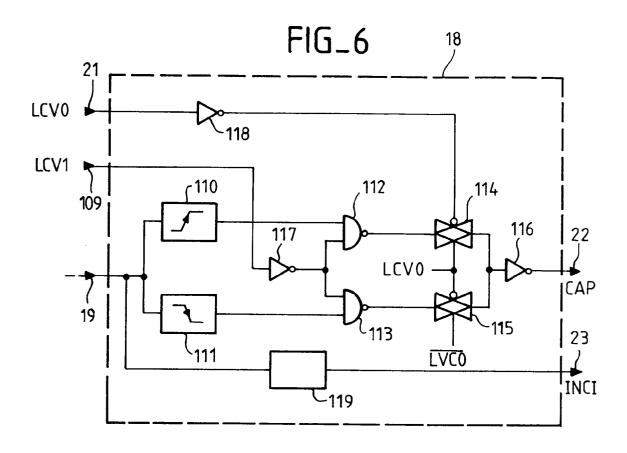

- figure 6 : circuit de détection,

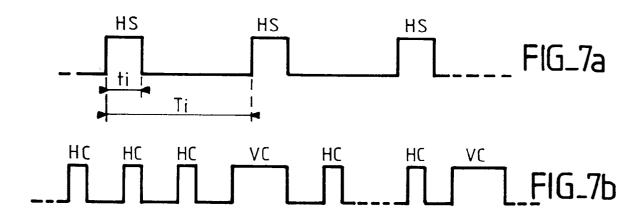

- figures 7a et 7b : signal de synchronisation monofréquentiel, et signal composite,

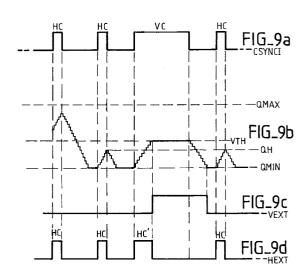

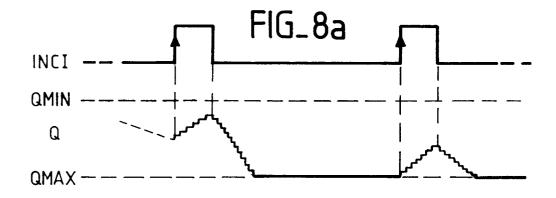

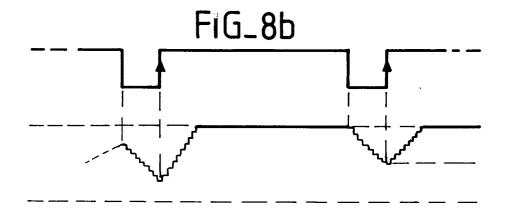

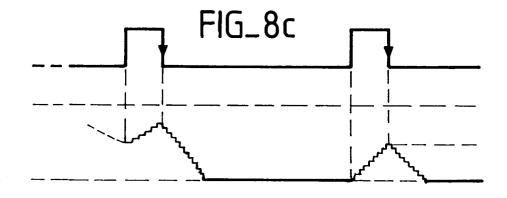

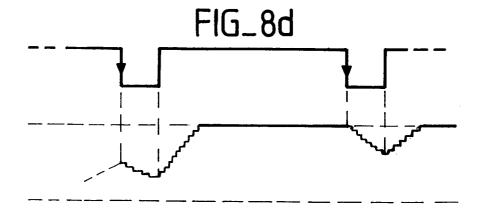

- figures 8a à 8d : signaux de polarité et évolution du contenu d'un compteur par rapport à l'état d'un signal de commande,

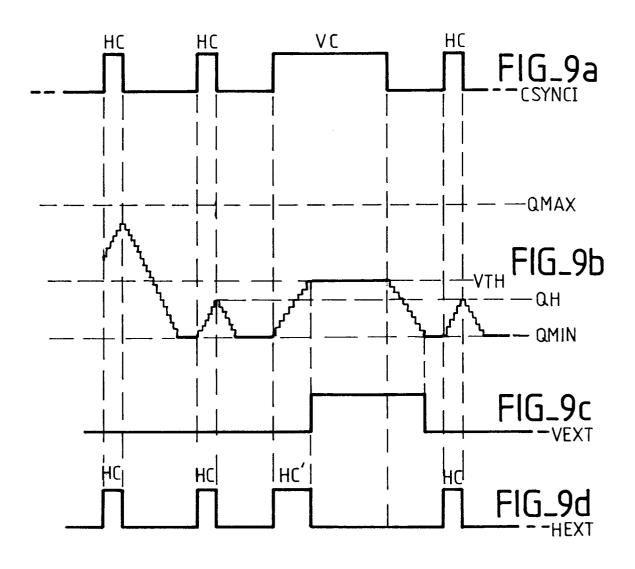

- figures 9a à 9d : signal composite, évolution du

- contenu du compteur par rapport à l'état de ce signal, signaux de synchronisation verticale et horizontale extraits du signal composite,

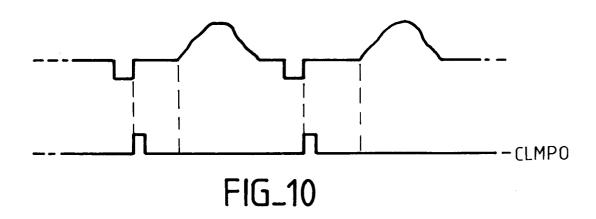

- figure 10 : signal vidéo et illustration d'un signal de référence de niveau de noir associé,

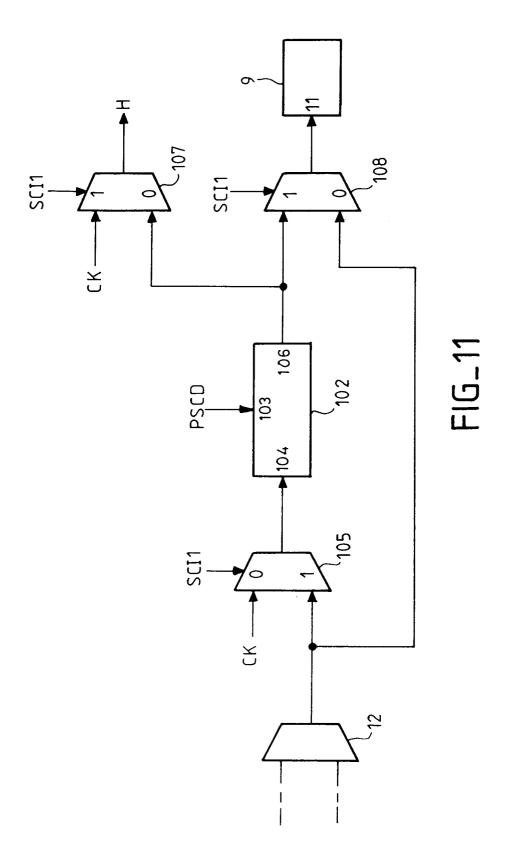

- figure 11 : montage diviseur de fréquence d'horloge ou de signal de synchronisation,

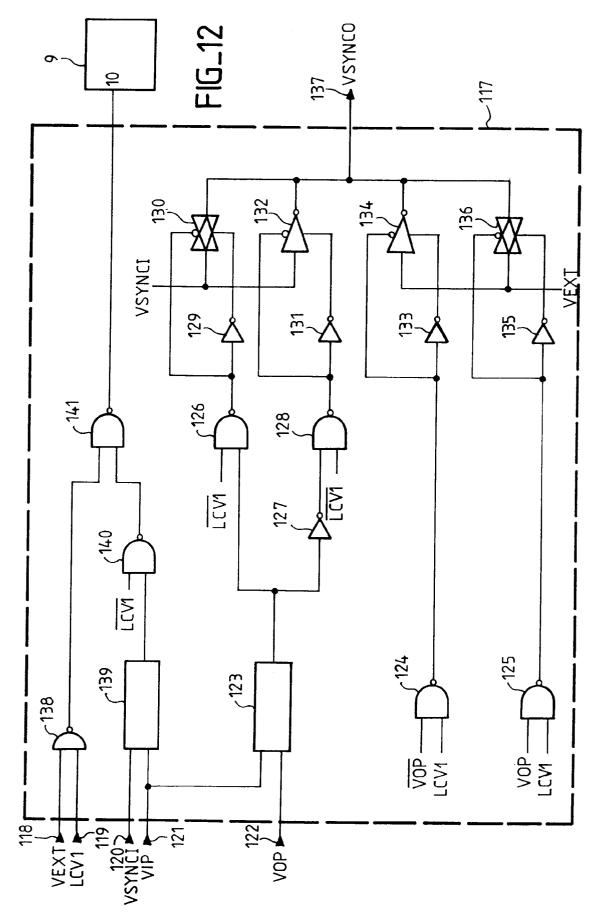

- figure 12 : circuit inverseur de polarité de signal de sortie de synchronisation horizontale.

La figure 1 représente un exemple de circuit 1 réalisé suivant l'invention.

Il comprend trois bornes d'entrées 2, 3 et 4 pour recevoir un ou des signaux de synchronisation.

Il existe en effet deux possibilités en ce qui concerne la synchronisation vidéo :

- utiliser un signal de synchronisation verticale et un signal de synchronisation horizontale (mode dit monofréquentiel) ou

- utiliser un seul signal de synchronisation, dit composite, pour la synchronisation verticale et la synchronisation horizontale (mode dit bifréquentiel).

Un signal de synchronisation verticale ou horizontale est un signal binaire constitué d'impulsions. Il est caractérisé par une polarité, une largeur (durée) d'impulsion, une fréquence de récurrence des impulsions

Un signal de synchronisation composite est également un signal binaire constitué d'impulsions. Il est caractérisé par une polarité, deux largeurs (durée) d'impulsion, suivant que ces impulsions soient utilisées pour la synchronisation verticale ou horizontale, deux fréquences de récurrence des impulsions, suivant que ces impulsions soient utilisées pour la synchronisation verticale ou horizontale.

Dans la suite de la description :

- la borne d'entrée 2 est dédiée à la réception de signaux de synchronisation verticale VSYNCI,

- la borne d'entrée 3 est dédiée à la réception de signaux de synchronisation verticale HSYNCI,

- la borne d'entrée 4 est dédiée à la réception de signaux de synchronisation composite CSYN-CI.

Les figures 7a et 7b représentent des signaux de synchronisation de polarité positive.

La polarité est dite positive si le signal est à un niveau logique 1 pendant la durée des impulsions, et à niveau logique 0 le reste du temps. Dans le cas contraire, elle est dite négative.

On dira qu'un signal de synchronisation est actif durant la durée des impulsions, et inactif sinon.

En pratique, pour les signaux de synchronisation horizontale (tels que représentés figure 7a), les impulsions HS ont une durée ti de l'ordre de 1 à 4 microsecondes et une fréquence de récurrence de l'ordre de 15 à 30  $\mu s$ . Un signal de synchronisation est donc inactif durant à peu près 90 % de la durée de la période Ti correspondant à la fréquence de récurren-

10

20

25

30

35

40

45

50

ce.

Pour un signal de synchronisation vertical une impulsion a une durée de l'ordre de 40 à 100  $\mu s$  pour une période d'une durée de 10 à 15 mS.

Un signal composite, représenté figure 7b, comprend des impulsions HC du type horizontal (durée de quelques microsecondes, fréquence de quelques kiloHertz) et des impulsions VC de type vertical (durée de quelques dizaines de microsecondes, fréquence de quelques Hertz).

Le circuit comprend par ailleurs deux bornes de sortie 5 et 6.

La borne de sortie 5 fournit un signal de synchronisation verticale VSYNCO. Le signal VSYNCO est soit le signal VSYNCI (mode monofréquentiel), soit un signal de synchronisation verticale VEXT produit à partir des impulsions de synchronisation verticale du signal composite CSYNCI.

La borne de sortie 6 fournit un signal de synchronisation horizontale HSYNCO. Le signal HSYNCO est soit le signal de synchronisation horizontale HSYNCI, soit un signal de synchronisation horizontale HEXT, produit à partir des impulsions de synchronisation horizontale du signal composite CSYNCI.

Le but du circuit 1 est de :

- détecter la présence d'un ou plusieurs signaux de synchronisation sur la ou les bornes d'entrée 4, ou 2 et 3,

- reconnaître ces signaux par comparaison avec des signaux de synchronisation standards mémorisés dans une mémoire 7 connectée par le biais d'un bus de données 17 à un microcontrôleur 8, compris tous trois dans le circuit,

- fournir pour le traitement de l'affichage des informations sur le standard détecté et éventuellement, dans le cas d'un signal composite, des signaux de synchronisation horizontale et verticale,

- fournir un signal de commande permettant à d'autres circuits une acquisition du niveau de noir des signaux à afficher.

Pour ce faire, le circuit 1 comprend un premier compteur 9 cadencé par un signal d'horloge CK, ayant deux entrées 10 et 11. L'entrée 10 est connectée à la borne d'entrée 2. L'entrée 11 est connectée à la sortie d'un multiplexeur 12. Ce multiplexeur 12 a deux entrées connectées aux bornes d'entrée 3 et 4, et une entrée de commande pour recevoir du microcontrôleur 8 un signal logique de sélection SCIO. Si SCIO=0, la sortie du multiplexeur 12 est reliée à la borne d'entrée 3. Si SCIO=1, cette sortie est reliée à la borne d'entrée 4.

Bien que le compteur 9 soit figuré de manière distincte par rapport au microcontrôleur 8, il sera en pratique un périphérique interne de ce microcontrôleur 8. En effet, tout microcontrôleur comprend un compteur. On pourrait néanmoins choisir d'utiliser un compteur 9 externe au microcontrôleur 8, afin de ne l'utiliser

que pour la détermination des caractéristiques d'un ou plusieurs signaux de synchronisation et non pas pour d'éventuelles tâches internes au microcontrôleur 8.

Le premier compteur 9 une sortie 13 connectée à une entrée d'interruption 14 du microcontrôleur 8, et un port de sortie parallèle 15 connecté à un port d'entrée/sortie parallèle 16 du microcontrôleur 8 par le biais du bus de données 17.

Ce premier compteur 9 compte en comptage binaire naturel. Dans un exemple il sera composé de 8 cellules en cascades. Classiquement, il fournit au microcontrôleur 8 un signal d'interruption INT et éventuellement une valeur de comptage C (dans un exemple C est codée sur 8 bits C0 à C7) quand un front est détecté une des entrées 10 et 11. On supposera que le signal d'interruption est produit sur front montant ou descendant des signaux de synchronisation VSYNCI, HSYNCI, ou CSYNCI.

Ce premier compteur 9 permet de détecter la présence de signaux de synchronisation sur une ou deux des bornes d'entrée. En effet, classiquement, il induit une procédure de gestion d'interruption du microcontrôleur quand il détecte un front sur une de ses entrées

On pourrait également détecter cette présence en connectant les bornes d'entrées à des entrées du microcontrôleur. Il suffirait de lire régulièrement l'état de ces entrées, un changement d'état impliquant la présence d'un signal de synchronisation sur au moins une des bornes d'entrée. Cette méthode présente l'inconvénient de mobiliser les ressources du microcontrôleur et n'est donc pas recommandée. En effet, ce microcontrôleur est utilisé concrètement pour commander l'ensemble des circuits utilisés pour gérer l'affichage.

En ce qui concerne le traitement du signal d'interruption INT, on prendra soin de le connecter à une entrée d'interruption 14 qui soit inhibable (c'est à dire qui n'implique pas automatiquement une séquence de gestion d'interruption du microcontrôleur 8). En effet, les signaux de synchronisation sont périodiques et des interruptions régulières pénaliseraient la gestion du microcontrôleur 8 (augmentation du temps nécessaire pour effectuer une tâche donnée).

Le premier compteur 9 est également utilisé, de façon classique, pour mesurer la fréquence de récurrence des impulsions de synchronisation. En pratique, on calculera la fréquence de récurrence des impulsions de synchronisation horizontale, que celles-ci soient comprises dans un signal composite ou qu'elles soient seules (mode monofréquentiel). On calculera ainsi la fréquence la plus rapide, ce qui permet un gain de temps. Dans le cas d'un signal composite, on prendra soin d'effectuer plusieurs mesures successives, afin de s'affranchir d'erreurs dues à la présence d'impulsions de synchronisation verticale dans le signal composite. On pourra tout de même

10

15

20

25

30

35

40

45

50

mesurer la fréquence des impulsions de synchronisation verticale, si cela est nécessaire, dans la détermination d'un standard.

Pour effectuer la mesure, le microcontrôleur lit et mémorise la valeur de C lors d'un front montant ou descendant. Puis il mémorise la valeur de C sur le front de même type suivant. Connaissant la fréquence d'horloge du premier compteur 9, on peut calculer la fréquence de récurrence des impulsions de synchronisation traitées. Ce type de procédure étant classique, on ne la développera pas en détail.

Un problème peut se poser du fait de la fréquence élevée (quelques dizaines de kiloHertz) des impulsions de synchronisation horizontale. Afin de ne pas produire un nombre important d'interruptions du microcontrôleur, on pourra choisir de diminuer la fréquence des impulsions reçues par le compteur 9. La solution la plus simple consiste à connecter la sortie du multiplexeur 12 à l'entrée 11 du compteur 9 par le biais d'un diviseur de fréquence. Dans un exemple on pourra ainsi cadencer le compteur par une horloge CK issue du microcontrôleur (de 4 MHz dans un exemple) et d'utiliser un diviseur de fréquence divisant la fréquence d'un facteur 256. Cela permet également d'effectuer des mesures plus précises.

Le circuit 1 comprend également un circuit de détection 18. Ce circuit de détection 18 a une entrée 19 connectée à la sortie d'un multiplexeur 20 à deux entrées. Les entrées de ce multiplexeur 20 sont connectées respectivement à la borne d'entrée 2 et à la sortie du premier multiplexeur 12. Le multiplexeur 20 a une entrée de commande pour recevoir du microcontrôleur un signal logique de sélection SCI1. Si SCI1=0, la sortie du multiplexeur 20 est reliée à la borne d'entrée 2. Si SCI1=1, cette sortie est reliée à la sortie du multiplexeur 12.

Le circuit de détection 18 a par ailleurs :

- une entrée 21 pour recevoir du microcontrôleur

8 un signal logique de sensibilité LCV0,

- une entrée 109 pour recevoir du microcontrôleur 8 un signal logique d'acquisition/extraction I CV1

- une sortie 22 pour fournir un signal logique de commande de capture CAP,

- une sortie 23 pour fournir un signal interne de synchronisation INCI correspondant au signal de synchronisation reçu sur l'entrée 19 avec un certain retard.

Ce circuit de détection 18 comprend typiquement un détecteur de front montant et un détecteur de front descendant. Il fonctionne de la manière suivante :

- le signal de capture CAP est dit actif si il est à 1, et inactif si il est à 0,

- si LCV0=0 et LCV1=0 alors CAP=1 quand on détecte un front descendant sur l'entrée 19 du circuit de détection,

- si LCV0=1 et LCV1=0 alors CAP=1 quand on détecte un front descendant,

- sinon CAP=0.

On dira que le signal d'acquisition/extraction est actif si LVC1=1, et inactif si LVC1=0.

Un mode de réalisation schématique est représenté figure 6.

L'entrée 19 du circuit de détection 18 est connectée à une entrée d'un détecteur de front montant 110 et à une entrée d'un détecteur de front descendant 111. Ces détecteurs de front 110 et 111, classiques par ailleurs, ne sont pas décrits. Ces détecteurs de front 110 et 111 ont chacun une sortie. On choisira ces détecteurs de front 110 et 111 de telle manière qu'ils produisent sur leur sortie respective un signal logique de niveau 1 quand ils détectent un front, et de niveau 0 sinon.

La sortie du détecteur de front 110 est connectée à l'entrée d'une porte NAND 112 à deux entrées. L'autre entrée de cette porte NAND 112 est connectée à la sortie d'un inverseur 117 dont l'entrée est connectée à l'entrée 109.

La sortie du détecteur de front 111 est connectée à l'entrée d'une porte NAND 113 à deux entrées. L'autre entrée de cette porte NAND 113 est connectée à la sortie de l'inverseur 117.

La sortie de la porte NAND 112 est connectée à l'entrée d'un interrupteur MOS 114. La grille de commande du transistor P de cet interrupteur 114 est connectée à la sortie d'un inverseur 118 dont l'entrée est connectée à l'entrée 21. La grille de commande du transistor de type N de l'interrupteur 114 est connectée à l'entrée 21.

La sortie de la porte NAND 113 est connectée à l'entrée d'un interrupteur MOS 115. La grille de commande du transistor N de cet interrupteur 115 est connectée à la sortie de l'inverseur 118. La grille de commande du transistor de type P de l'interrupteur 115 est connectée à l'entrée 21.

Bien sûr, les notions d'entrée et de sortie d'interrupteur, qu'on retrouvera par la suite, sont uniquement fonctionnelles.

Les sorties de ces interrupteurs 114 et 115 sont connectées à l'entrée d'un inverseur 116 dont la sortie correspond à la sortie 22 du circuit de détection 18.

Par ailleurs l'entrée 19 du circuit de détection 18 est connectée à la sortie 23 de ce circuit 18 par le biais d'une bascule à retard 119.

Le signal de capture CAP est utilisé pour charger sélectivement dans un registre 24 une valeur de comptage Q quand un front montant ou descendant est détecté sur le signal de synchronisation présent à l'entrée 19 du circuit de détection 18.

Le circuit 1 comprend un deuxième compteur 25, cadencé par un signal d'horloge de comptage H. Il comprend une entrée 26 pour recevoir le signal interne de synchronisation INCI, une entrée de validation de comptage 27 pour recevoir un signal logique de validation de comptage CE, et un port de sortie parallèle 28.

15

20

25

30

35

40

45

50

C'est ce deuxième compteur 25 qui produit la valeur de comptage Q. Ce compteur 25 compte en langage binaire naturel si CE=1, sinon il est bloqué (CE=0).

Il incrémente ou décrémente la valeur de comptage Q suivant l'état du signal interne de synchronisation INCI.

Si INCI=1, alors il incrémente Q.

Si INCI=0, alors il décrémente Q.

Le registre 24 comprend :

- un port d'entrée/sortie parallèle 29 connecté par le biais d'un multiplexeur 30 soit au port de sortie parallèle 28 du compteur 25, soit au bus de données 17,

- une entrée de commande de lecture/écriture 31 pour recevoir du microcontrôleur 8 un signal logique de commande de lecture/écriture R/W et une entrée de commande de capture 32 pour recevoir le signal de capture CAP du circuit de détection 18.

On appellera CV la valeur contenue dans le registre 24.

Le multiplexeur 30 reçoit, du microcontrôleur 8, sur une entrée de commande, un signal logique de sélection CS pour connecter le port parallèle 29 du registre 24 au bus 17 (CS=1) ou au port de sortie parallèle 28 du deuxième compteur 25 (CS=0).

Quand CS=1, on supposera que le microcontrôleur lit le contenu du registre 24 si R/W=0 et écrit dans ce registre 24 si R/W=1.

Le circuit 1 comprend également un circuit de contrôle 33.

Ce circuit de contrôle 33 comprend :

- un port d'entrée parallèle 34 pour recevoir la valeur de comptage Q du compteur 25,

- un port d'entrée parallèle 35 pour recevoir le contenu CV du registre 24,

- une entrée 36 pour recevoir le signal interne de synchronisation INCI,

- deux entrées 37 et 38 pour recevoir du microcontrôleur 8 le signal de sensibilité LCV0, et le signal d'acquisition/extraction LCV1,

- une sortie 39 pour fournir le signal de validation de comptage CE au compteur 25.

Ce circuit de contrôle 33 permet de comparer la valeur de comptage Q à des seuils (valeurs) minimum QMIN et maximum QMAX et de bloquer respectivement l'incrémentation ou la décrémentation de Q si le seuil maximum ou minimum est atteint, en fournissant CE=0 au compteur 25.

Ce circuit de contrôle 33 comprend également une sortie 40 pour fournir le signal de synchronisation verticale VEXT à partir d'un signal de synchronisation CSYNCI composite.

Le circuit 1 comprend également un multiplexeur de sortie 41, un circuit de sortie 42, et un circuit de verrouillage 43.

Le multiplexeur de sortie 41 a deux entrées. Une

entrée est connectée à la borne d'entrée 2. L'autre entrée est connectée à la sortie 40 du circuit de contrôle 33. Le multiplexeur 41 reçoit également le signal d'acquisition/extraction LCV1.

Ce multiplexeur de sortie 41 a une sortie connectée à la borne de sortie 5.

Si LCV1=0 alors VSYNCO=VSYNCI (cas où les signaux reçus sont monofréquentiels).

Si LCV1=1 alors VSYNCO=VEXT (cas où le signal reçu est composite).

Le circuit de sortie 42 a une entrée 44 connectée à la sortie du multiplexeur 12, une entrée 45 connectée à la sortie 40 du circuit de contrôle 33, et une sortie 46 connectée à la borne de sortie 6.

Le circuit de verrouillage 43 a une entrée 47 connectée à la borne de sortie 6, une entrée 48 connectée à la sortie 40 du circuit de contrôle 33 et une sortie 49 connectée à une borne de sortie 50 pour fournir un signal impulsionnel de référence de niveau de noir CLMPO.

Après avoir sommairement décrit le circuit 1, nous allons aborder son fonctionnement.

Comme on l'a vu précédemment, la détection de la présence d'un ou deux signaux de synchronisation sur une ou deux bornes d'entrée est effectuée à l'aide du premier compteur 9. De même, on peut à l'aide de ce compteur 9 mesurer une fréquence de récurrence d'impulsions.

Il nous reste à envisager la détection de polarité, la mesure de largeur d'impulsion, l'extraction de deux signaux de synchronisation verticale et horizontale à partir d'un signal composite, et la production du signal de référence de niveau de noir CLMPO.

La détection de polarité s'effectue en trois étapes, de la manière suivante :

- 1) écriture depuis le microcontrôleur 8 d'une valeur donnée dans le registre 24,

- 2) chargement dans ce registre 24 de la valeur de comptage Q du compteur 25,

- 3) lecture de la valeur chargée depuis le compteur 25 et comparaison avec la valeur chargée initialement depuis le microcontrôleur 8.

Dans un exemple, le compteur 25 est un compteur 5 bits. Le registre 24 comporte donc au moins 5 bascules de mémorisation. Il peut en compter plus, et servir pour stocker des signaux de commande tels que LCV0, LCV1 par exemple. En pratique, c'est le cas puisque le port d'entrée/sortie parallèle 29 de ce registre 24 est connecté via le multiplexeur 30 à un bus de données 17 du microcontrôleur 8. Or ce bus de données 17 comporte classiquement 8 bits (dans le cas d'un microcontrôleur classique 8 bits).

Le compteur 25 est apte à compter entre deux valeurs QMIN et QMAX. Dans un exemple, QMIN=00000 (=00 en langage hexadécimal) et QMAX=11111 (=1F).

En pratique, pour déterminer la polarité d'un signal de synchronisation, le microcontrôleur 8 écrit

10

15

20

25

30

35

40

45

50

dans le registre 24 la valeur QMIN ou la valeur QMAX. Pour ce faire, il fournit CS=1 au multiplexeur 30 et R/W=1 au registre 24.

Puis il fixe CS=0 et LCV0=0 si CV=QMIN ou LCVO=1 si CV=QMAX.

Dans le premier cas, le circuit de détection 18 fournit CAP=1 au registre 24 quand un front montant apparait sur son entrée 19, et CAP=0 sinon.

Dans le second cas, le circuit de détection 18 fournit CAP=1 au registre 24 quand un front descendant apparait sur son entrée 19, et CAP=0 sinon.

Les figures 8a à 8d illustrent l'évolution de la valeur Q du compteur en fonction du signal de synchronisation INCI reçu à l'entrée 26 du compteur 25.

Sur les figures 8a et 8c, le signal de synchronisation INCI a une polarité positive. Sur les figures 8b et 8d, il a une polarité négative.

Sur les figures 8a et 8b, la valeur Q du compteur 25 est chargée dans le registre 24 quand un front montant apparaît sur le signal INCI. Sur les figures 8c et 8d, la valeur Q du compteur 25 est chargée dans le registre 24 quand un front descendant apparaît sur le signal INCI.

A priori, on ne connaît pas la valeur Q du compteur au moment où un premier front apparaît sur le signal INCI.

On choisit une fréquence d'horloge de comptage H telle que Q ne puisse pas passer de QMIN à QMAX, ou inversement, pendant la durée d'une impulsion. La valeur Q peut prendre 32 valeurs discrètes différentes (Q est codée sur cinq bits Q0 à Q4).

Compte-tenu des durées d'impulsions respectives, on pourra utiliser une fréquence d'horloge de comptage H de 4 MHz par exemple (identique à CK) pour des impulsions de synchronisation horizontale. En effet, il faudra alors 32 \* 250 nS, soit 8 µS pour que Q passe de QMIN à QMAX, ou inversement. Or, on pratique, les impulsions de synchronisation horizontales ont une durée ne dépassant pas, à l'heure actuelle, 4 µS.

Pour des impulsions de synchronisation verticale, cette fréquence d'horloge de comptage H est trop rapide. On pourra générer une fréquence plus lente en divisant cette fréquence à l'aide d'un diviseur de fréquence sélectionné par le signal de sélection SCI1 (division si SCI1=0, fréquence de 4 MHz si SCI1=1) . Par exemple, on pourra utiliser un diviseur de fréquence d'un facteur fixe de 256. Il faudra alors 32 \* 64  $\mu$ S, soit 2.048 mS, pour que Q passe de QMIN à QMAX, ou inversement, ce qui est compatible avec les valeurs standard de durée d'impulsion verticale.

Pour un signal composite, on choisira de préférence d'utiliser la fréquence d'horloge de comptage H la plus rapide et de détecter la polarité des impulsions de synchronisation horizontale, étant entendu qu'un signal composite n'a qu'une polarité. Cela permet de diminuer le temps de détection.

Suivant que le signal est de polarité positive ou

négative, la valeur Q atteindra QMIN ou QMAX pendant la durée où le signal de synchronisation INCI est inactif (temps entre la fin d'une impulsion de synchronisation et le début de l'impulsion de synchronisation suivante).

Le circuit de contrôle 33 (décrit dans la suite de la description) est agencé de telle manière que Q ne puisse passer de QMAX à QMIN qu'en décrémentant, et non directement. Ainsi, quelle que soit la valeur de Q au début d'une impulsion de synchronisation, à partir de l'impulsion de synchronisation suivante, la valeur de Q sera égale à une valeur donnée sur les fronts montants des impulsions (QMIN si la polarisation est positive) et à une autre valeur donnée sur les fronts descendants des impulsions (QMAX si la polarité est négative).

Si le signal de synchronisation INCI est de polarité positive, alors, sur les fronts montant des impulsions, Q=QMIN=00. Sur les fronts descendants, Q est différent de QMIN (Q > QMIN).

Si le signal de synchronisation INCI est de polarité négative, alors, sur les fronts descendants des impulsions, Q=QMAX=1F. Sur les fronts montants, Q est différent de QMAX (Q < QMAX).

Il suffit que le microcontrôleur 8 lise la valeur de CV pour déterminer si la polarité est positive ou négative. Si on a écrit CV=QMAX dans le registre 24 et qu'on charge Q dans le registre 24 sur front descendant, CV est inchangée si la polarité est négative (positive sinon). De même, si on a écrit CV=QMIN et qu'on charge Q sur front montant dans le registre 24, la polarité est positive si CV est inchangée (négative sinon).

L'avantage d'effectuer la lecture et la comparaison de CV à la valeur initialement écrite dans le registre 24 à l'aide du microncontrôleur 8 est de permettre plusieurs lectures et comparaisons avant de décider de la polarité du signal de synchronisation INCI.

Dans le cas d'un signal composite, on prendra en effet soin d'effectuer plusieurs lectures du registre 24 afin de s'affranchir de la lecture de valeurs erronées dues à la présence d'impulsions de synchronisation verticale (de durées supérieures à celles des impulsions de synchronisation horizontale). En effet, Q passera d'un extremum à l'autre lorsque le signal de synchronisation sera actif (si l'horloge de comptage H a une fréquence rapide bien sûr).

On pourrait néanmoins utiliser des circuits de comparaison de type logique tels qu'on en trouve dans le circuit de contrôle 33.

Du fait du retard de INCI par rapport au signal de synchronisation VSYNCI, HSYNCI, ou CSYNCI présent à l'entrée 19 du circuit de détection 18, on est certain que le chargement de Q dans le registre 24 est effectué à un moment précédant les fronts des impulsions. Cela garantit que l'on ne charge pas dans le registre 24 une valeur toujours différente de QMIN ou

15

20

25

30

35

40

45

50

QMAX.

Par ailleurs, on prendra soin d'inactiver le signal de capture CAP quand le microcontrôleur accède au registre 24 par le biais du bus de données 17.

On pourra au choix prévoir un signal de commande supplémentaire pour le registre 24 qui inactive le signal CAP, multiplexer les signaux R/W et CAP et les sélectionner par le biais du signal CS, inactiver CAP au niveau du circuit de détection par le biais du signal

Une fois que la polarité des impulsions est définies, le microcontrôleur peut aisément mesurer la durée de ces impulsions de synchronisation. Il suffit de fixer l'état de LCV0 tel que la valeur de Q chargée dans le registre 24, quand on détecte un front, est différente de QMIN ou QMAX. On détecte alors un front correspondant à la fin d'une impulsion. Si la polarité est positive, on chargera sur front descendant. Si la polarité est négative, on chargera sur front montant. Il suffit alors de multiplier la valeur de Q lue dans le registre 24 par le temps nécessaire au compteur 25 pour incrémenter ou décrémenter Q d'une unité, connaissant la fréquence du signal d'horloge de comptage H.

La figure 3 illustre une réalisation possible du circuit de contrôle 33.

Pour la comparaison de Q à QMIN (00) et QMAX (1F) il comprend une porte NAND 63 et une porte NOR 64. Schématiquement ces portes 63 et 64 sont représentées avec cinq entrées. Les entrées de ces portes 63 et 64 sont connectées au port d'entrée parallèle 34 du circuit de contrôle 33. La porte NAND 63 reçoit donc sur ses entrées la valeur Q (Q0 à Q4). Il en est de même pour la porte NOR 64.

La sortie de la porte NAND 63 est connectée à l'entrée d'un inverseur 65. La sortie de cet inverseur 65 est connectée à l'entrée d'un interrupteur MOS 69. La grille de commande du transistor de type N de l'interrupteur 69 est connectée à l'entrée 36 (qui reçoit le signal interne de synchronisation INCI). La grille de commande du transistor de type P de l'interrupteur 69 est connectée à cette même entrée via un inverseur (non représenté), et reçoit donc /INCI.

La sortie de la porte NOR 64 est connectée à l'entrée d'un interrupteur MOS 70. La grille de commande du transistor de type P de l'interrupteur 70 est connectée à l'entrée 36 (qui reçoit INCI). La grille de commande du transistor de type N de l'interrupteur 70 recoit /INCI.

Les sorties des interrupteurs 69 et 70 sont connectées à l'entrée d'une porte NOR 72 à deux entrées. La sortie de la porte NOR 72 correspond à la sortie 39 du circuit de contrôle 33. Cette porte 72 fournit donc le signal de validation de comptage CE.

Ainsi, si Q=QMIN et que le signal de synchronisation INCI est à l'état bas, le compteur 25 est bloqué à Q=QMIN (CE=0).

De même, si Q=QMAX et que le signal de syn-

chronisation INCI est à l'état haut, le compteur 25 est bloqué à Q=QMAX (CE=0).

Dans le cas d'un signal de synchronisation composite CSYNCI, on mesurera la durée des impulsions de synchronisation horizontale. Cela permet de procéder ultérieurement à l'extraction du signal de synchronisation verticale VEXT et du signal de synchronisation HSYNCO à partir de ce signal composite CSYNCI.

Pour ce faire on utilise le circuit de contrôle 33 et le circuit de sortie 42, de la manière suivante :

1) connaissant la polarité du signal composite et la durée des impulsions de synchronisation horizontale, on fixe une valeur seuil binaire VTH, codée sur le même nombre de bits que Q, telle que :

- si la polarité est positive, VTH représente une durée supérieure ou égale à la durée nécessaire pour le compteur 25 pour incrémenter Q pendant la durée d'une impulsion de synchronisation horizontale (front montant au début de l'impulsion).

- si la polarité est négative, VTH représente une durée supérieure ou égale à la durée nécessaire pour le compteur 25 pour décrémenter Q pendant la durée d'une impulsion de synchronisation horizontale (front descendant au début de l'impulsion).

A l'aide des schémas 9a à 9d, on va décrire une extraction des signaux VEXT et HEXT à partir d'un signal composite.

La figure 9a représente un signal de synchronisation composite CSYNCI de polarité positive, composée d'impulsions HC de synchronisation horizontale et d'impulsions VC de synchronisation verticale.

On ne connaît pas, a priori, la valeur Q, et la fréquence d'horloge de comptage H utilisée est la fréquence rapide (4 MHz dans l'exemple).

La figure 9b représente l'évolution de la valeur Q. Comme on l'a vu lors de la description de la détection de polarité, Q va se stabiliser à Q=QMIN lorsque les signaux de synchronisation horizontale sont inactifs (entre la fin d'une impulsion HC et le début de la suivante) et à une valeur donnée QH > QMIN à la fin des impulsions de synchronisation horizontale HC.

Le seuil VTH est fixé tel que VTH > QH.

Quand Q est inférieure à VTH, le circuit de contrôle 33 produit un signal de synchronisation verticale extrait VEXT de niveau bas (état 0, inactif) sur sa sortie 40 (figure 9c).

Lorsqu'une impulsion de synchronisation verticale VC apparaît, Q est incrémentée entre QMIN et VTH. Lorsque Q=VTH, le circuit de contrôle 33 bloque le compteur (CE=0) et simultanément, le signal VEXT passe à l'état 1 (actif).

A la fin de l'impulsion de synchronisation verticale VC (front descendant), Q est décrémentée. Quand

10

15

20

25

35

40

45

50

Q=QMIN, le signal de synchronisation verticale extrait VEXT est désactivé (0, inactif).

En pratique, il faut donc que l'intervalle de temps entre la fin d'une impulsion de synchronisation verticale et le début de l'impulsion de synchronisation horizontale suivante soit assez important pour permettre à Q de passer de VTH à QMIN. Cela impose qu'on ne fixe pas une valeur de seuil VTH qui soit excessivement supérieure à QH.

D'autre part, il existe un retard du signal de synchronisation verticale extrait VEXT par rapport au signal de synchronisation verticale compris dans le signal composite CSYNCI. En pratique ce n'est pas gênant pour l'utilisateur puisqu'il correspond à un rafrachissement d'écran légèrement retardé mais non perceptible à l'oeil humain. Néanmoins, on aura intérêt à fixer un seuil VTH le plus proche possible de QH pour limiter ce retard.

On va décrire ci-dessous le reste du circuit de contrôle 33.

La figure 2 illustre un mode de réalisation d'un circuit de comparaison 51. Il comprend deux entrées 52 et 53 pour recevoir deux signaux logiques. Les deux entrées 52 et 53 sont connectées à deux entrées d'une porte NAND 54 à deux entrées, et à deux entrées d'une porte NOR 55 à deux entrées. La sortie de la porte NAND 54 est connectée à l'entrée d'un inverseur 56. La sortie de cet inverseur 56 est connectée à une entrée d'une porte NOR 57 à deux entrées. L'autre entrée de cette porte NOR 57 est connectée à la sortie de la porte NOR 55. La sortie de la porte NOR 57 est connectée à l'entrée d'un inverseur 58. La sortie de cet inverseur 58 est connectée à une sortie 59 du circuit comparateur 51.

Le signal logique présent sur la sortie 59 est donc à l'état 1 si les signaux logiques présents sur les entrées 52 et 53 sont dans le même état, et à l'état 0 sinon

Le circuit de contrôle 33 comprend un circuit de comparaison 60 du même type que le circuit de comparaison 51 décrit précédemment. Les entrées de ce comparateur sont connectées aux entrées 36 et 37 du circuit de contrôle 33 et reçoivent donc, d'une part le signal de synchronisation INCI, et d'autre part le signal de sensibilité LCV0. La sortie de ce comparateur 60 est connectée à une entrée d'une porte NAND 68 à trois entrées. Une autre entrée de cette porte NAND 68 est connectée à l'entrée 38 du circuit de contrôle 33 et reçoit donc le signal d'acquisition/extraction LCV1.

Le circuit de contrôle 33 comporte également cinq autres circuits de comparaison 61. Les entrées de ces circuits de comparaison 61 sont connectées aux ports d'entrée parallèle 34 et 35 de telle manière que chaque circuit de comparaison 61 compare un bit de CV au bit correspondant de Q (CV étant codée sur 5 bits CV0 à CV4). On compare ainsi CV0 à Q0, CV1 à Q1 etc. Les sorties de ces cinq circuits de compa-

raison 61 sont connectées aux entrées d'une porte NAND 66 à cinq entrées (il s'agit d'une représentation schématique). La sortie de cette porte NAND 66 est connectée à l'entrée d'un inverseur 67, dont la sortie est connectée à la dernière entrée de la porte NAND 68. La sortie de cette porte NAND 68 est connectée à l'entrée d'un inverseur 71 dont la sortie est connectée à l'autre entrée de la porte NOR 72.

Ainsi, le circuit de contrôle permet de bloquer le compteur 25 quand on a à la fois :

- un signal de synchronisation INCI actif (action du circuit de comparaison 60),

- Q=CV=VTH

- LCV1=1

La première condition permet au compteur 25 de ne pas rester bloqué si Q atteint le seuil VTH alors que le signal INCI est inactif.

Par exemple il se pourrait que Q > VTH au moment où on passe en mode d'extraction, alors que le signal INCI a une polarité positive (figure 9b). Il est nécessaire, pour que l'extraction soit efficace, que Q puisse franchir le seuil VTH (et devienne donc inférieure à VTH) quand le signal INCI est inactif.

Pour générer le signal de synchronisation verticale VEXT, le circuit de contrôle 33 est agencé de la manière suivante.

Il comprend deux interrupteurs MOS 73 et 74.

L'entrée de l'interrupteur MOS 73 est connectée à la sortie de l'inverseur 65. La grille de commande du transistor P de cet interrupteur 73 est connectée à l'entrée 37 et reçoit le signal de sensibilité LCV0. La grille de commande du transistor N de cet interrupteur 73 est connectée à l'entrée 37 par le biais d'un inverseur (non représenté) et reçoit le signal /LCV0.

L'entrée de l'interrupteur MOS 74 est connectée à la sortie de la porte NOR 64. La grille de commande du transistor N de cet interrupteur 74 est connectée à l'entrée 37 et reçoit le signal de sensibilité LCV0. La grille de commande du transistor P de cet interrupteur 73 reçoit le signal /LCV0.

Les sorties de ces interrupteurs 73 et 74 sont connectées à une entrée d'une porte NOR 75 à deux entrées. l'autre entrée de cette porte NOR 75 est connectée à l'entrée 38 par le biais d'un inverseur non représenté et reçoit le signal d'acquisition/extraction /LCV1. La sortie de la porte NOR 75 est connectée à l'entrée d'un inverseur 76 dont la sortie est connectée à une entrée d'une port NOR 77 à deux entrées. L'autre entrée de cette porte NOR 77 est connectée à la sortie de la porte NAND 68.

La sortie de la porte NOR 77 est connectée à une entrée d'une porte NAND 79 à deux entrées. La sortie de l'inverseur 76 est connectée à une entrée d'une porte NAND 80 à deux entrées. Les autres entrées des portes NAND 79 et 80 reçoivent le signal d'horloge /CK. La sortie de la porte NAND 79 est connectée à une entrée d'une porte NAND 81 à deux entrées, dont la sortie correspond à la sortie 40 du circuit de

10

20

25

30

35

45

50

55

contrôle 33. La sortie de la porte NAND 80 est connectée à une entrée d'une porte NAN 82 à deux entrées. La deuxième entrée de la porte NAND 82 est connectée à la sortie de la porte NAND 81. La deuxième entrée de la porte NAND 81 est connectée à la sortie de la porte NAND 82. L'ensemble des portes NAND 79 à 82 forme donc une bascule 78.

On remarquera que le signal VEXT produit est toujours de polarité positive. On pourra choisir de l'inverser ou non, cette fonctionnalité étant proposée dans la suite de la description quand on abordera un circuit d'inversion 117 illustré figure 12.

Le signal de synchronisation extrait VEXT a toujours la même largeur d'impulsion et la même fréquence de récurrence d'impulsion que le signal de synchronisation INCI et n'est activé que lorsque INCI présente des impulsions de synchronisation verticale.

En ce qui concerne le signal de synchronisation horizontale HSYNCO extrait du signal composite CSYNCI et fourni par le circuit de sortie 42, il est illustré figure 9d.

Lorsque ce circuit de sortie 42 reçoit sur son entrée 44 un signal de synchronisation horizontale HSYNCI (SCI0=0), il reproduit fidèlement ce signal. S'il en était de même lorsqu'il reçoit un signal composite CSYNCI (SCI0=1), il produirait un signal de synchronisation horizontal inadéquat, comportant des impulsions de synchronisation verticale non désirées. Le circuit de sortie 42 donc est agencé pour inactiver le signal HSYNCO fourni sur sa sortie 46 (connectée à la borne de sortie 6) quand le signal de synchronisation verticale extrait est actif. Le signal de synchronisation HSYNCO comportera donc les impulsions de synchronisation horizontale HC du signal composite reproduites fidèlement, et des impulsions HC' parasites. Le début de ces impulsions parasites HC' coïncide avec le début des impulsions de synchronisation verticale VC du signal composite. La fin de ces impulsions parasites HC' coïncide avec l'activation du signal de synchronisation verticale VEXT (Q=VTH). En pratique, ces impulsions parasites ne sont pas gênantes car elles sont produites juste avant le rafraîchissement de l'écran par l'activation du signal de synchronisation verticale VEXT.

Dans le cas d'un signal composite CSYNCI de polarité négative, l'extraction des signaux VEXT et HSYNCO est similaire. On a alors décrémentation de Q entre QMAX et une valeur QH lors des impulsions de synchronisation horizontale, et le seuil VTH est fixé de telle manière qu'il soit inférieur à QH.

En ce qui concerne la production du signal de niveau de noir CLMPO, elle est faite à l'aide du circuit de verrouillage 43 (figure 5).

Le signal impulsionnel de niveau de noir CLMPO est activé dans l'intervalle de temps compris entre la fin des impulsions de synchronisation horizontale du signal HSYNCO d'une part, et le début du signal vidéo

à afficher sur la ligne correspondante d'autre part (voir figure 10). On a représenté un signal vidéo contenant à la fois des signaux représentatifs d'informations à afficher sur des lignes, et des impulsions de synchronisation horizontale associées à ces lignes. Il s'agit d'un signal reçu par circuits de filtrage, ceux-ci ne fournissant que les signaux de synchronisation au circuit 1.

Le signal CLMPO, dans le mode de réalisation choisi, est mis dans un état dit actif à la fin des impulsions de synchronisation horizontale de HSYNCO, et mis dans l'autre état (dit inactif) après un certain délai.

On choisit de fournir un signal CLMPO dont le niveau actif est 1, et le niveau inactif est 0 (polarité positive). Rien n'empêche de concevoir un circuit de verrouillage qui permette d'inverser ce choix, voire de proposer à l'utilisateur de choisir l'une ou l'autre des possibilités.

Dans l'exemple de réalisation traité, on choisit de programmer la durée pendant laquelle le signal CLMPO est actif afin que celle-ci soit de 250, 500, ou 1000 nS. Cette programmation est prise en compte par le circuit de verrouillage 43 au travers de signaux logiques BP0 et BP1 reçus du microcontrôleur sur des entrées 159 et 160, de la manière suivante :

- BP0=0, BP1=0: signal CLMPO inactif,

- EP0=1, BP1=0 : signal CLMPO actif durant 250nS.

- BP0=0, BP1=1 : signal CLMPO actif durant 500 nS,

- BP0=1, BP1=1 : signal CLMPO actif durant 1000 nS.

Un mode de réalisation de ce circuit est illustré figure 5.

L'entrée 159 est connectée à :

- l'entrée d'un inverseur 83 dont la sortie est connectée à une entrée d'une porte NAND 86 à quatre entrées,

- une entrée d'une porte NAND 85 à quatre en-

- une entrée d'une porte NAND 87 à quatre entrées

L'entrée 160 est connectée à :

- l'entrée d'un inverseur 84 dont la sortie est connectée à une autre entrée de la porte NAND 85,

- une autre entrée de la porte NAND 87,

- une autre entrée de la porte NAND 86.

Les sorties des portes NAND 85, 86, et 87 sont connectées à trois entrées d'une porte NAND 89 à trois entrées. La sortie de cette porte NAND 89 est connectée à une entrée d'une porte NAND 90 à deux entrées. L'autre entrée de cette porte NAND 90 est connectée à l'entrée 48 par le biais d'un inverseur 88. La sortie de cette porte NAND 90 est connectée à l'entrée d'un inverseur 91 dont la sortie correspond à la sortie 49 du circuit de verrouillage 43.

20

25

30

35

40

45

50

L'entrée 47 est connectée à l'entrée d'un inverseur 101. La sortie de cet inverseur 101 est connectée à l'entrée d'un interrupteur MOS 95 et à l'entrée d'une porte de transmission inverseuse 94.

Le circuit reçoit sur une entrée 102 un signal logique de sélection HOP représentatif de la polarité de HSYNCO. Cette entrée 102 est connectée à l'entrée d'un inverseur 92. La sortie de cet inverseur 92 est connectée à l'entrée d'un inverseur 93, à la grille de commande du transistor P de l'interrupteur 95, et à la grille de commande du transistor de type N de sortie de la porte de transmission inverseuse 94.

La sortie de l'inverseur 93 est connectée à la grille de commande du transistor de type N de l'interrupteur 95 et à la grille de commande du transistor de type P de sortie de la porte de transmission inverseuse 94.

La sortie de la porte de transmission inverseuse 94 est connectée à l'entrée d'une bascule à verrouillage 96 cadencée par le signal d'horloge CK.

Si HOP=1 l'entrée de la bascule 96 reçoit/HSYN-CO (HSYNCO de polarité positive).

Si HOP=0 l'entrée de la bascule 96 reçoit HSYN-CO (HSYNCO de polarité négative).

La sortie non inverseuse de la bascule 96 est connectée à une autre entrée de la porte NAND 87, à une autre entrée de la porte NAND 85, à une autre entrée de la porte NAND 86, et à l'entrée d'une bascule à verrouillage 97 cadencée par le signal d'horloge CK.

La sortie non inverseuse de cette bascule 97 est connectée à l'entrée d'une bascule à verrouillage 98 cadencée par le signal d'horloge CK. La sortie inverseuse de la bascule 97 est connectée à la dernière entrée de la porte NAND 85.

La sortie non inverseuse de la bascule 98 est connectée à l'entrée d'une bascule à verrouillage 99 cadencée par le signal d'horloge CK. La sortie inverseuse de la bascule 98 est connectée à la dernière entrée de la porte NAND 86.

La sortie non inverseuse de la bascule 99 est connectée à l'entrée d'une bascule à verrouillage 100 cadencée par le signal d'horloge CK. La sortie inverseuse de cette bascule 100 est connectée à la dernière entrée de la porte NAND 87.

On notera qu'étant donné le système de bascule employé, on ne considère que des impulsions de synchronisation horizontale de polarité négative, les bascules étant classiquement déclenchées sur front montant. C'est pourquoi on inverse la polarité du signal d'entrée HSYNCO si celle-ci est positive.

La figure 4 illustre une réalisation possible du circuit de sortie 42. Par rapport à la figure 1, il comporte deux entrées supplémentaires 142 et 143 pour recevoir un signal logique HIP et le signal logique HOP, de manière à permettre de choisir la polarité du signal de sortie de synchronisation HSYNCO. Rappelons par ailleurs que le circuit de sortie 42 est agencé de telle

manière que les impulsions de synchronisation horizontale de sortie sont inactivées quand le signal de synchronisation verticale VEXT est actif.

HIP et HOP sont tels que s'ils sont dans le même état, la polarité du signal de sortie de synchronisation horizontale est identique à celle du signal d'entrée, sinon la polarité est inversée.

Le circuit de sortie 42 comprend un circuit de comparaison 144 analogue au circuit de comparaison 51. Les deux entrées de ce circuit de comparaison 144 sont connectées aux entrées 142 et 143.

La sortie de ce circuit 144 est connectée à :

- une entrée d'une porte NAND 145 à deux entrées, dont l'autre entrée est connectée à l'entrée 45 par le biais d'un inverseur non représenté (et reçoit donc /VEXT),

- une entrée d'un inverseur 146 dont la sortie est connectée à une entrée d'une porte NAND 147 à deux entrées. L'autre entrée de cette porte NAND 147 reçoit /VEXT.

La sortie de la porte NAND 145 est connectée d'une part à l'entrée d'un inverseur 151, et d'autre part à la grille de commande d'un transistor de type P d'un interrupteur MOS 152. La sortie de l'inverseur 151 est connectée à la grille de commande du transistor de type N de l'interrupteur 152.

La sortie de la porte NAND 147 est connectée d'une part à l'entrée d'un inverseur 153, et d'autre part à la grille de commande d'un transistor de type P de sortie d'une porte de transmission inverseuse 154. La sortie de l'inverseur 153 est connectée à la grille de commande du transistor de type N de sortie de la porte de transmission inverseuse 154.

Les entrées de l'interrupteur 152 et de la porte de transmission inverseuse 154 sont connectées à la borne 44. Les sorties de l'interrupteur 152 et de la porte de transmission inverseuse 154 sont connectées à la borne 46.

Le circuit de sortie 42 comprend également un inverseur 148 dont l'entrée est connectée à la borne 143. La sortie de cet inverseur 148 est connectée à une entrée d'une porte NAND 149 à deux entrées, dont l'autre entrée est connectée à l'entrée 45. Cette entrée 45 est par ailleurs connectée à une entrée d'une porte NAND 150 à deux entrées, dont l'autre entrée est connectée à la borne 143.

La sortie de la porte NAND 149 est connectée d'une part à l'entrée d'un inverseur 155, et d'autre part à la grille de commande d'un transistor de type P d'un interrupteur MOS 156. La sortie de l'inverseur 155 est connectée à la grille de commande du transistor de type N de l'interrupteur 156. L'entrée de cet interrupteur 156 est maintenue au niveau logique 1 (typiquement par connexion à une borne d'alimentation logique du circuit 1).

La sortie de la porte NAND 150 est connectée d'une part à l'entrée d'un inverseur 157, et d'autre part à la grille de commande d'un transistor de type

10

15

20

25

30

35

45

50

P d'un interrupteur MOS 158. La sortie de l'inverseur 157 est connectée à la grille de commande du transistor de type N de l'interrupteur 158. L'entrée de cet interrupteur 158 est maintenue au niveau logique 0 (typiquement par connexion à une borne de masse du circuit 1).

Les sorties des interrupteurs 156 et 158 sont connectées également à la borne 46.

On pourrait, dans une variante, réaliser un circuit de sortie 42 qui intègre les fonctions du multiplexeur d'entrée 12 afin de minimiser les temps de transfert entre les bornes d'entrée et la borne de sortie. Il suffit d'utiliser des portes NAND 145 et 147 à trois entrées en sortie du circuit de comparaison 144. Par exemple on connecterait les troisièmes entrées des portes 145 et 147 à la sortie d'un inverseur recevant SCI0 en entrée, et les entrées des éléments de sorties (interrupteur, porte de transmission) à la borne d'entrée 3. Par ailleurs on dédoublerait ces portes 145 et 147 avec des portes NAND associées recevant SCI0, et dont les éléments de sortie seraient connectés à la borne 4 en entrée.

Dans un mode de réalisation préféré, illustré figure 11, le circuit 1 comporte un diviseur de fréquence 102 qui permet :

- d'une part de produire un signal d'horloge de comptage H pour le compteur 25 qui soit compatible avec le traitement de signaux de synchronisation verticale au niveau de ce compteur 25,

- d'autre part de fournir au compteur 9, sur son entrée 11, un signal de synchronisation ayant une fréquence plus faible que le signal de synchronisation fourni en sortie du multiplexeur 12.

Le diviseur de fréquence 102 comprend une entrée 104. Cette entrée 104 est connectée à la sortie d'un multiplexeur 105 à deux entrées. Ce multiplexeur 105 reçoit sur une entrée le signal d'horloge CK, et son autre entrée est connectée à la sortie du multiplexeur 12. Ce multiplexeur est commandé par le signal de sélection SCI1 pour fournir à l'entrée 104 du diviseur 102 pour le signal d'horloge CK si SCI1=0 (INCI=VSYNCI), et HSYNCI ou CSYNCI si SCI1=1.

Le diviseur 102 comprend également une entrée 103 pour recevoir du microcontrôleur 8 une commande de validation de division PSCD qui inhibe ou active le diviseur 102.

Ce diviseur 102 comprend enfin une sortie 106 pour fournir soit le signal d'horloge désiré, soit le signal de synchronisation désiré, suivant l'état du signal de sélection SCI1. Cette sortie 106 est connectée à une entrée d'un multiplexeur 107 à deux entrées. L'autre entrée de ce multiplexeur 107 reçoit le signal d'horloge CK. Ce multiplexeur 107 est commandé par le signal de sélection SCI1. Il fournit en sortie le signal d'horloge de comptage H, H ayant la fréquence de CK si SCI1=1 et à une fréquence

moindre si SCI1=0.

La sortie 106 du diviseur 102 est par ailleurs connectée à une entrée d'un multiplexeur à deux entrées 108. L'autre entrée de ce multiplexeur 108 est connectée à la sortie du multiplexeur 12. Le multiplexeur 108 est commandé par le signal de sélection SCI1. Il connecte l'entrée 11 du compteur 9, soit à la sortie 106 du diviseur 102 si SCI1=1, soit à la sortie du multiplexeur 12 si SCI1=0.

On pourrait bien sûr choisir de découpler les multiplexeurs 105 et 107 d'une part, et 108 d'autre part.

Il suffit pour cela de commander ce dernier multiplexeur 108 à l'aide d'un signal de sélection différent de SCI1.

On pourrait envisager que le circuit 1 comporte un circuit d'inversion de la polarité de sortie VSYNCO 117, comme c'est le cas pour le circuit de sortie 42. Il permet également de fournir un signal de synchronisation à l'entrée 10 du deuxième compteur 9 qui est toujours de polarité positive, si tant est qu'on souhaite fixer la polarité du signal reçu sur l'entrée 10. Il permet également de fournir à cette entrée 10 le signal de synchronisation VEXT, quand on un signal d'entrée de synchronisation CSYNCI composite. Cela permet de calculer la fréquence de récurrence des impulsions du signal VEXT.

Un tel circuit d'inversion 117 est représenté figure 12.

Ce circuit d'inversion de polarité 117 peut être placé en lieu et place du multiplexeur 41 de la figure 1, et entre la borne d'entrée 2 et l'entrée 10 du compteur 9.

Le circuit d'inversion de polarité 117 comprend :

- une entrée 118 pour recevoir le signal de synchronisation verticale VEXT,

- une entrée 119 pour recevoir le signal d'acquisition/extraction LVC1,

- une entrée 120 pour recevoir le signal de synchronisation verticale VSYNCI,

- une entrée 121 pour recevoir un signal logique VIP issu du microcontrôleur 8,

- une entrée 122 pour recevoir un signal logique VOP issu du microcontrôleur 8,

- une sortie 137 pour fournir le signal de synchronisation verticale VSYNCO.

Les signaux logiques VIP et VOP sont tels que :

- si VOP=VIP alors VSYNCO=VSYNCI si LCV1=0, et VSYNCO=VEXT si LCV1=1,

- sinon VSYNCO=/VSYNCI si LCV1=0 et VSYN-CO=/VEXT si LCV1=0,

- si LCV1=1 le compteur 9 reçoit VEXT (qui est toujours de polarité positive),

- si LCV1=0 et VIP=1 le compteur 9 reçoit VSYN-CI,

- si LCV1=0 et VIP=0 le compteur 9 recoit/VSYNCI.

Le circuit d'inversion 117 comprend :

- un circuit de comparaison 123, analogue au cir-

10

15

20

25

30

35

45

50

- cuit 51, dont les entrées sont connectées aux entrées 121 et 122 (VIP, VOP),

- une porte NAND 124 à deux entrées qui reçoit sur ses entrées /VOP (inverseur connecté à l'entrée 122 non représenté) et LCV1,

- une porte NAND 125 à deux entrées qui reçoit sur ses entrées VOP et LCV1.

La sortie du circuit de comparaison 123 est connectée d'une part à une entrée d'une porte NAND à deux entrées 126, et d'autre part à l'entrée d'un inverseur 127. La porte NAND 126 est connectée par le biais d'un inverseur non représenté à l'entrée 119 (LCV1). La sortie de l'inverseur 127 est connectée à une entrée d'une porte NAND 128 à deux entrées. Cette porte NAND 128 reçoit /LCV1 sur son autre entrée

La sortie de la porte NAND 126 est connectée d'une part à l'entrée d'un inverseur 129, et d'autre part à la grille de commande d'un transistor P d'un interrupteur MOS 130. La sortie de l'inverseur 129 est connectée à la grille de commande du transistor N de l'interrupteur 130.

La sortie de la porte NAND 128 est connectée d'une part à l'entrée d'un inverseur 131, et d'autre part à la grille de commande du transistor P de sortie d'une porte de transmission inverseuse 132. La sortie de l'inverseur 131 est connectée à la grille de commande du transistor N de sortie de la porte de transmission inverseuse 132.

La sortie de la porte NAND 124 est connectée d'une part à l'entrée d'un inverseur 133, et d'autre part à la grille de commande du transistor P de sortie d'une porte de transmission inverseuse 134. La sortie de l'inverseur 133 est connectée à la grille de commande du transistor N de sortie de la porte de transmission inverseuse 134.

La sortie de la porte NAND 125 est connectée d'une part à l'entrée d'un inverseur 135, et d'autre part à la grille de commande d'un transistor P d'un interrupteur MOS 136. La sortie de l'inverseur 135 est connectée à la grille de commande du transistor N de l'interrupteur 136.

Les sorties des interrupteurs 130 et 136 sont connectées à la sortie 137, de même que les sorties des portes de transmission inverseuses 132 et 134.

Le circuit d'inversion 117 comprend également un autre circuit de comparaison 139 dont les entrées sont connectées aux entrées 120 et 121 (VSYNCI et VIP). La sortie de ce circuit de comparaison est connectée à une entrée d'une porte NAND 140 à deux entrées, qui reçoit /LCV1 sur son autre entrée.

Il comprend également une porte NAND 138 à deux entrées, ses entrées étant connectées aux entrées 118 et 119 (VEXT et LCV1).

Les sorties des portes NAND 138 et 140 sont connectées aux deux entrées d'une porte NAND 141 à deux entrées, et dont la sortie est connectée à l'entrée 10 du compteur 9.

On ne décrira pas ici les interfaces entre le circuit 1 décrit et les circuits nécessaires par ailleurs au fonctionnement du matériel d'affichage, et particulièrement les liaisons entre le microcontrôleur et ces circuits. De même, on ne proposera pas d'information particulière concernant la programmation du microcontrôleur, étant entendu que la description est suffisamment précise quant à la suite des tâches à effectuer et à la définition des signaux de commande à générer pour les mener à bien.

Il apparaît clairement que la reconnaissance d'un standard n'est limitée que par la capacité du microcontrôleur à en connaître l'existence, c'est-à-dire par le fait que les caractéristiques de ce standard sont ou non mémorisées dans la mémoire associée à ce microcontrôleur.

On pourra également prévoir des moyens de multiplexage en entrée pour recevoir des signaux de synchronisation arrivant de lignes de transmissions différentes, si l'écran est pour vu de différentes prises de connexion. Cela permettrait par exemple de connecter deux ordinateurs sur un même écran, l'un étant par exemple, une station de travail et l'autre un microordinateur, l'utilisateur utilisant ces moyens pour des tâches distinctes. Dans l'état actuel de la technique, on ne peut afficher simultanément des informations provenant de deux ordinateurs. Néanmoins, rien ne l'interdirait dans l'avenir, dans la mesure où l'écran serait pourvu de prises de connexion différentes.

## Revendications

- **1 -** Procédé de reconnaissance de standard vidéo, caractérisé en ce que :

- on mémorise une valeur représentative d'une durée.

- on produit une valeur de comptage (Q), cette valeur étant incrémentée quand un signal binaire de synchronisation (INCI) est dans un état, et décrémentée quand ce signal est dans l'autre état,

- on effectue une comparaison de la valeur représentative de la durée et de la valeur de comptage, à un moment donné du signal de synchronisation,

- et on produit un signal représentatif du standard en fonction du résultat de la comparaison.

- 2 Procédé suivant la revendication 1, caractérisé en ce que la valeur représentative d'une durée est programmable.

- **3 -** Procédé suivant selon l'une des revendications 1 à 2, caractérisé en ce que la comparaison est effectuée un temps donné après qu'une transition d'un type donné ait eu lieu dans le signal de synchronisation.

- 4 Procédé selon l'une des revendications 1 à 3, caractérisé en ce que le signal représentatif du pro-

10

15

20

25

30

35

40

45

50

tocole est produit après un certain nombre de transistions de type donné.

- **5 -** Procédé selon l'une des revendications 1 à 4, caractérisé en ce que la valeur de comptage est maintenue entre deux valeurs fixes (QMIN, QMAX).

- **6 -** Procédé selon la revendication 5, caractérisé en ce que la valeur représentative d'un temps est programmée pour être égale à l'une des valeurs fixes.

- 7 Procédé selon l'une des revendications 5 à 6, caractérisé en ce qu'on maintient la valeur de comptage entre une valeur choisie parmi les deux valeurs fixes et une valeur programmée (VTH) comprise entre ces valeurs fixes.

- **8 -** Procédé selon la revendication 7, caractérisé en ce que la valeur programmée est représentative d'une durée supérieure à la durée pendant laquelle le signal de synchronisation est dans un état donné.

- 9 Procédé selon l'une des revendications 7 à 8, caractérisé en ce que, quand la valeur de comptage atteint la valeur programmée, on change l'état d'un signal binaire extrait (VEXT), celui-ci passant dans un état dit actif, ce signal binaire extrait changeant à nouveau d'état, pour passer dans un état dit inactif, quand la valeur de comptage atteint la valeur fixe choisie.

- 10 Procédé selon la revendication 9, caractérisé en ce qu'on produit un signal de synchronisation (HSYNCO) de sortie à partir du signal de synchronisation, et en ce qu'on inactive ce signal de synchronisation de sortie quand la valeur de comptage atteint la valeur programmée.

- 11 Procédé selon l'une des revendications 1 à 10, caractérisé en ce qu'à partir du signal de synchronisation de sortie, on produit un signal de référence binaire (CLMPO) de telle manière que celui-ci est activé quand le signal de synchronisation de sortie est désactivé.

- **12 -** Procédé selon la revendication 11, caractérisé en ce qu'on désactive le signal de référence quand le signal binaire extrait est actif.

- 13 Circuit de reconnaissance de standard vidéo (1), caractérisé en ce qu'il comprend :

- au moins une borne d'entrée (2) pour recevoir un signal d'entrée de synchronisation (VSYN-CI), une borne de sortie (5) pour fournir un signal de sortie de synchronisation (VSYNCO), un microcontrôleur (8),

- un circuit de détection (18) recevant sur une entrée (19) le signal d'entrée de synchronisation et comportant des moyens pour produire d'une part un signal interne de synchronisation (INCI) retardé par rapport au signal d'entrée de synchronisation, et d'autre part un signal logique de commande de capture (CAP),

- un compteur (25) cadencé par un signal d'horloge de comptage (H) et produisant une valeur de comptage (Q) qui est incrémentée ou décrémentée suivant l'état du signal interne de

- synchronisation, cette valeur de comptage étant accessible sur un port de sortie parallèle (28) du compteur,

- un registre (24) comprenant un port d'entrée/sortie parallèle (29) pour charger la valeur de comptage quand le signal de commande de capture est dans un état dit actif.

- 14 Circuit selon la revendication 13, caractérisé en ce qu'il comprend un circuit de contrôle (33) recevant sur une entrée (34) la valeur de comptage et comportant des moyens de comparaison pour comparer cette valeur de comptage à des seuils minimum (QMIN) et maximum (QMAX).

- 15 Circuit selon la revendication 14 caractérisé en ce que le circuit de contrôle produit un signal logique de validation de comptage (CE) qui bloque l'incrémentation ou la décrémentation de la valeur de comptage si le seuil maximum ou minimum est atteint par la valeur de comptage.

- 16 Circuit selon l'une des revendications 13 à 15, caractérisé en ce que le circuit de détection met le signal de commande de capture dans son état actif quand il détecte un front d'un type donné dans le signal d'entrée de synchronisation, le type de front étant défini par l'état d'un signal logique de sensibilité (LCV0) issu du microcontrôleur.

- 17 Circuit selon l'une des revendications 13 à

16, caractérisé en ce qu'il comporte des moyens (17,

30) pour écrire une valeur dans le registre partir du microcontrôleur.

- **18 -** Circuit selon l'une des revendications 13 à 17, caractérisé en ce qu'il comprend un second compteur (9) recevant sur une première entrée le signal d'entrée de synchronisation.

- 19 Circuit selon la revendication 18, caractérisé en ce que le second compteur est apte à fournir au microcontrôleur une valeur de comptage (C), par le biais d'un bus de données (17), et un signal d'interruption (INT).

- 20 Circuit selon l'une des revendications 14 à 19, caractérisé en ce que le circuit de contrôle comprend des moyens pour produire et fournir sur la borne de sortie un signal de synchronisation verticale extrait (VEXT) à partir d'un signal interne de synchronisation composite.

- 21 Circuit selon la revendication 20, caractérisé en ce que le circuit de contrôle produit le signal de synchronisation verticale extrait quand un signal logique d'acquisition/extraction (LCV1) issu du microcontrôleur est dans un état dit actifs.

- 22 Circuit selon l'une des revendications 14 à 21, caractérisé en ce qu'il comporte des moyens de comparaison pour comparer la valeur de comptage du premier compteur à une valeur de seuil programmable (VTH) issue du microcontrôleur.

- 23 Circuit selon la revendication 22, caractérisé en ce que la valeur de seuil programmable est écrite par le microcontrôleur dans le registre et en ce que

10

15

20

25

30

35

45

50

le circuit de contrôle comprend une entrée (35) pour recevoir le contenu du registre.

- 24 Circuit selon l'une des revendications 21 à 23, caractérisé en ce que le circuit de détection inactive le signal de commande de capture quand le signal d'acquisition/extration est actif.