**Europäisches Patentamt European Patent Office**

Office européen des brevets

EP 0 730 214 A2 (11)

**EUROPÄISCHE PATENTANMELDUNG** (12)

(43) Veröffentlichungstag: 04.09.1996 Patentblatt 1996/36 (51) Int. Cl.6: G05F 3/26

(21) Anmeldenummer: 96102646.5

(22) Anmeldetag: 22.02.1996

(84) Benannte Vertragsstaaten: DE FR GB IT NL

(71) Anmelder: Deutsche ITT Industries GmbH D-79108 Freiburg (DE)

(30) Priorität: 01.03.1995 DE 19507155

(72) Erfinder: Theus, Ulrich, Dr.-Ing. D-79194 Gundelfingen (DE)

## (54)Stromspiegel in MOS-Technik mit weit aussteuerbaren Kaskodestufen

(57)Ein Stromspiegel in MOS-Technik ermöglicht weit aussteuerbare Kaskodestufen (t2, t4) in seinen Stromein- und -ausgängen (em bzw. om), indem das gemeinsame Steuerpotential (u3) für den Stromspiegel (m, mb) von einer stromgesteuerten Stromquelle (q) gebildet wird. Ihr Ansteuerstrom ist ein Differenzstrom (id), der durch Differenzschaltung eines dem Stromspiegeleingang (em) zugeführten Eingangsstromes (ie) und eines mit dem Stromspiegeleingang (em) verkoppelten Strombankstromes (i1) gebildet wird. An den Ausgang (k3) der Stromquelle (q) ist eine gemeinsame Steuerleitung (cl) angeschlossen, die mit den kapazitiv belasteten Gate-Anschlüssen der Steuertransistoren (t1, t3) einer n-Kanal-Strombank (mb) verbunden ist, in der die eigentliche Stromspiegelung (ie, ia) stattfindet.

Fig.3

30

40

## **Beschreibung**

Die Erfindung betrifft einen Stromspiegel in MOS-Technik mit weit aussteuerbaren Kaskodestufen, eine Strombank enthaltend, die mittels einer Regelschaltung von einem Differenzstrom gesteuert ist, der an einem Schaltungsknoten zwischen dem Stromspiegeleingang und einem zugehörigen, hochohmigen Kaskodeausgang abgegriffen ist, vgl. den Oberbegriff des Anspruchs 1.

In monolithisch integrierten Schaltungen, insbesondere in analog arbeitenden Stufen, werden Stromspiegel mit gleicher oder unterschiedlicher Stromübersetzung und mit einem oder mit mehreren Stromausgängen für eine Vielzahl von Hilfsfunktionen verwendet. Um die Ausgangskennlinien der Stromspiegel möglichst spannungsunabhängig, also möglichst hochohmig zu machen, werden die einzelnen Stromspiegelausgänge als Kaskodestufen ausgebildet, wobei das Festpotential für die Steuerelektroden der Kaskodetransistoren mittels einer Hilfsspannungsquelle erzeugt wird. Ein sehr einfacher, oft verwendeter Stromspiegel mit Kaskodestufen in MOS-Technik ist in Fig. 1 dargestellt. Ein Nachteil dieser bekannten Schaltung ist, daß die Sättigung einiger Transistoren unter speziellen betriebs- und technologieabhängigen Bedingungen nicht gewährleistet ist. Dabei ist der Sättigungsbereich für einen n- bzw. p - Kanal-Transistor durch die bekannten Sättigungsgleichungen definiert:

$$V_{DS} \ge (V_{GS} - V_{T})$$

beim n-Kanal-Transistor und

$$V_{\,DS} \leqq \left(V_{\,GS} - V_{\,T}\right)$$

beim p-Kanal-Transistor.

Hauptursache für den kritischen Betriebszustand des n-Kanal-Stromspiegels in Fig. 1 ist das Gate-Potential der gemeinsamen n-Kanal-Strombanksteuerleitung, die direkt an den Stromspiegeleingang angeschlossen ist. Da an diesem Anschlußpunkt auch die Serienschaltung der beiden Drain-Source-Strompfade des kasko-Stromspiegeleingangs dierten liegt, ist erkennbar, daß das Gate-Potential des Strombanktransistors t1, der im folgenden auch als Stromspiegelsteuertransistor bezeichnet wird, um die Drain-Source-Spannung des Kaskodetransistors t2 höher liegt als sein Drain-Potential. Da die Transistoren t1 und t2 beide in Sättigung betrieben werden sollen, folgt aus den Sättigungsgleichungen:

$$V_{DSt2} < V_{Tt1}$$

wobei  $V_{DSt2}$  die Drain-Source-Spannung des Kaskodetransistors t2 und  $V_{Tt1}$  die Schwellenspannung des Strombanktransistors t1 bezeichnet.

Die Größe der Schwellenspannung  $V_T$  ist durch die Technologie vorgegeben, wobei ihr negativer Temperaturkoeffizient dem positiven Temperaturkoeffizient der effektiven Gate-Spannung - für gleichen Strom aber

zunehmende Kristalltemperatur - leider gerade entgegenläuft.

Eine gewisse Abhilfe stellt die bekannte Schaltung nach Figur 2 dar, bei der die Gate-Elektrode des Stromspiegelsteuertransistors von einer Regelschaltung gesteuert wird, deren Eingang von einem am Stromspiegeleingang abgegriffenen Signal gespeist wird. Hierzu wird gleichsam der Eingangsstrompfad des eigentlichen Stromspiegels elektronisch aufgetrennt und ein Differenzstrom aus dem zugeführten Stromspiegeleingangsstrom und dem Ausgangsstrom des Stromspiegelsteuertransistors gebildet. Wenn der Differenzstrom zu Null wird, dann ist der zugeführte Eingangsstrom gleich dem Ausgangsstrom Stromspiegelsteuertransistors und damit der Sollwert des Regelvorgangs erreicht. Durch diese Maßnahme stellt sich die Ansteuerspannung für den Gate-Anschluß des Stromspiegelsteuertransistors und damit das Potential der gemeinsamen Strombanksteuerleitung von selbst auf einen unkritischen Wert ein. Eine einfache Betrachtung der resultierenden Potentialverhältnisse zeigt, daß das Potential der gemeinsamen Strombanksteuerleitung deutlich niedriger als das Potential der Hilfsspannungsquelle sein kann und damit der gewünschte Sättigungszustand für den Stromspiegelsteuertransistor und für die Kaskodestufen des Stromspiegels sichergestellt wird.

Ein wesentlicher Nachteil der in Fig. 2 dargestellten Schaltung, die als Regelschaltung einen gegengekoppelten Operationsverstärker enthält, ist das kritsche Stabilitätsverhalten, das ohne geeignete Dämpfungsmaßnahmen zu Regelkreisschwingungen führen kann.

Andererseits beeinflussen die üblichen Dämpfungsmaßnahmen das Frequenzverhalten des Stromspiegels, so daß er für viele Signalanwendungen zu langsam wird. Zudem erfordert die Schaltung zur Stabilisierung mindestens einen zusätzlichen Kondensator, der insbesondere bei der monolithischen Integration der Schaltung von Nachteil ist.

Aufgabe der in Anspruch 1 gekennzeichneten Erfindung ist es daher, eine verbesserte Regelung für einen Stromspiegel in MOS-Technik mit weit aussteuerbaren Kaskodestufen anzugeben, mit dem Ziel, den erforderlichen Schaltungsaufwand gering und die Geschwindigkeit des Stromspiegels möglichst hoch zu halten.

Die Lösung dieser Aufgabe folgt entsprechend den kennzeichnenden Merkmalen des Patentanspruchs 1 dadurch, daß die Regelschaltung als wesentliche Einheit eine stromgesteuerte Stromquelle enthält, deren Steuereingang mit dem Differenzstromabgriff im Stromspiegeleingang und deren Stromausgang mit der gemeinsamen Strombanksteuerleitung verbunden ist, wobei die Regelzeitkonstante durch eine kapazitive Belasung des Stromquellenausgangs eingestellt ist.

Die Verwendung einer Stromquelle in der Regelschaltung hat den Vorteil, daß die kapazitive Last der gemeinsamen Strombanksteuerleitung, die je nach der Größe und Anzahl der angeschlossenen Gate-Elektroden sehr unterschiedlich groß sein kann, die dominante

Polstelle des gesamten Regelkreises darstellt und daher im wesentlichen das Regelkreisverhalten bestimmt. Die anderen Polstellen treten in ihrer Wirkung dahinter zurück. In der Regel erübrigt sich wegen der kapazitiven Last der gemeinsamen Strombanksteuerleitung eine zusätzliche interne oder externe Kapazität.

Das Stabilitätsverhalten hängt ferner von der Schleifenverstärkung und damit vom Stromübersetzungsverhältnis der stromgesteuerten Stromquelle ab. Es ist daher vorteilhaft, wenn das Stromübersetzungsverhältnis den Wert 10 nicht überschreitet, wobei ein bevorzugter Wert etwa bei 1 liegt, so daß die Ein- und Ausgangsströme etwa gleich groß sind. Über das W/L-Verhältnis der mit der Stromquelle und Strombank verkoppelten Transistoren läßt sich das Stromübersetzungsverhältnis leicht einstellen.

Die Festlegung des Potentials des niederohmigen Stromquellensteuereingangs erfolgt in der Art einer Gate-Schaltung, deren Bezugseingang, der Gate-Anschluß, an einer Referenzspannung liegt und deren niederohmiger Signaleingang, der Source-Anschluß, den Stromquellensteuereingang bildet. Es wird darauf hingewiesen, daß der Ein- und Ausgang der Stromquelle, damit auch der Ausgang des Spannungsfolgers, in bidirektionaler Richtung arbeitet, d.h. die Flußrichtung der jeweiligen Ströme kann positiv oder negativ sein. Eine derartige Stromquelle kann beispielsweise zwei zusammenwirkende komplementäre Stromspiegel enthalten, eine Anordnung, die besonders die CMOS-Technik berücksichtigt. Eine derartige Anordnung verbindet beispielsweise einen n- und einen p-Kanal-Stromspiegel derart miteinander, daß der Ausgang des p-Kanal-Stromspiegels mit dem Eingang des n-Kanal-Stromspiegels direkt oder über Kaskodetransistoren verbunden ist. In gleicher Weise ist der Ausgang des n-Kanal-Stromspiegels mit dem Eingang des p-Kanal-Stromspiegels direkt oder über Kaskodetransistoren verbunden. Über die Kaskodetransistoren in den beiden Quer-Strompfaden können Ströme niederohmig einund hochohmig ausgekoppelt werden. Eine derartige Stromspiegelanordnung eignet sich daher besonders zur Differenzstrombildung, wobei der Differenzstrom positiv oder negativ sein kann. Kapazitive Beeinflussungen des Frequenzverhaltens von Stromspiegeln sind an sich aus der DE 42 01 155 C1 bekannt, die einen schaltbaren Stromspiegel mit MOS-Transistoren von jeweils gleichem Kanaltyp betrifft.

Die Erfindung und weitere vorteilhafte Ausgestaltungen werden nun anhand der Figuren der Zeichnung näher erläutert:

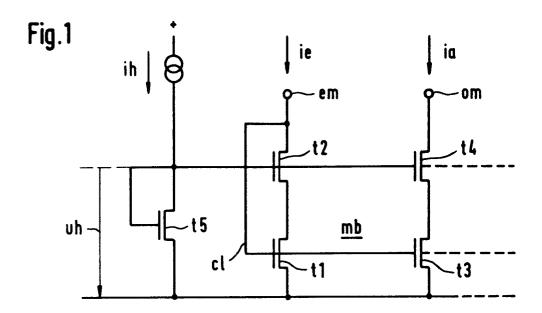

Fig. 1 zeigt einen bekannten Stromspiegel mit Kaskodestufen,

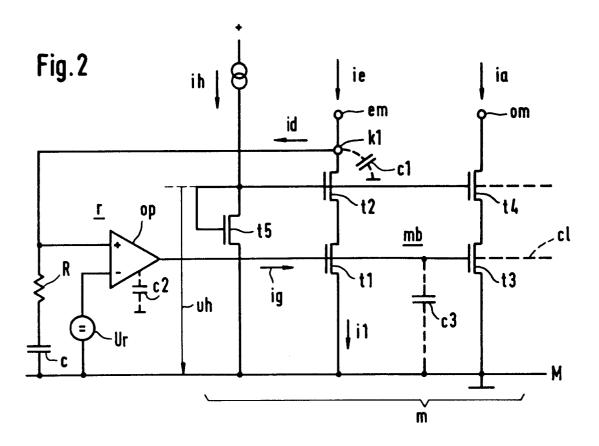

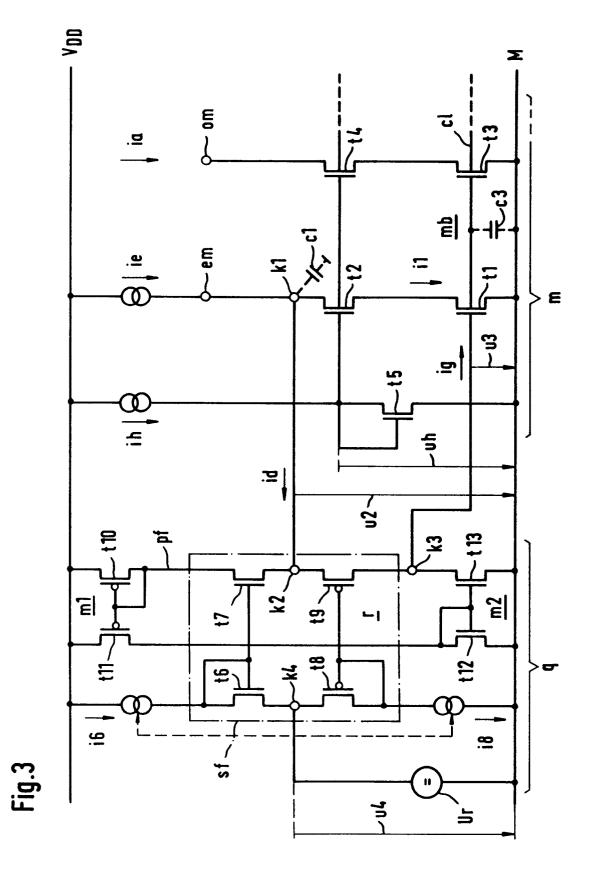

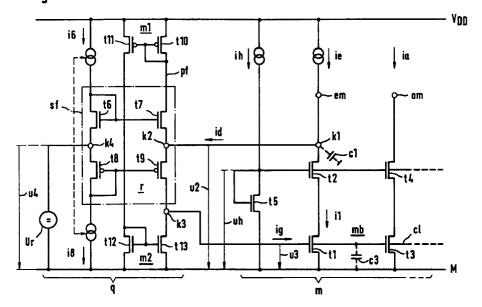

Fig. 2 zeigt einen bekannten Stromspiegel mit Kaskodestufen, wobei das Gate-Potential der eigentlichen Strombank von einer Regelschaltung erzeugt wird und Fig. 3 zeigt ein vorteilhaftes Ausführungsbeispiel eines Stromspiegels mit Kaskodestufen, wobei die Pegelregelung der Strombank nach der Erfindung erfolgt.

Der bekannte Stromspiegel in Fig. 1 bewirkt, daß ein von einer nicht dargestellten Quelle erzeugter Eingangsstrom ie an einer n-Kanal-Strombank mb mit den Transistoren t1, t3 als Ausgangsstrom ia gespiegelt wird. Zur Entkopplung des Ausgangsstromes ia von der jeweiligen Ausgangsspannung wird ein Kaskodetransistor t4 zwischen den Stromspiegelausgang om und die Drain-Elektrode des Transistors t3 geschaltet. Aus Symmetriegründen wird der Eingangsstrom ie ebenfalls über einen Kaskodetransistor t2 geführt, der zwischen dem Stromspiegeleingang em und dem Drainanschluß des Strombanktransistors t1 liegt, der auch als Stromspiegelsteuertransistor dient. Das gemeinsame Gate-Potential der Kaskodetransistoren t2, t4 liegt an einer Hilfsspannung uh, die mittels eines Hilfsstromes ih und eines als Diode geschalteten n-Kanal-Transistors t5 gebildet ist. Die gemeinsame Strombanksteuerleitung cl der Strombank mb ist an die Drain-Elektrode des Kaskodetransistors t2 angeschlossen. Es ist leicht einsehbar, daß durch die Serienschaltung der beiden n-Kanal-Transistoren t2, t1 das Drain-Potential des Strombanktransistors t1 im Vergleich zu seinem Gate-Potential bei bestimmten Betriebszuständen zu klein wird, so daß die vorausgesetzte Sättigung der Transistoren t1 und t2 nicht mehr vorhanden ist, wodurch die Stromsymmetrie zwischen den Strombanktransistoren t1, t3 und gegebenenfalls weiteren Strombanktransistoren nicht mehr gewahrt bleibt.

In Fig. 2 ist der Hauptnachteil gemäß Fig. 1 - nämlich das relativ hohe Gate-Potential des Strombanktransistors t1 beseitigt, indem beim eigentlichen Stromspiegel m, die gemeinsame Strombank-Steuerleitung von einer Regelschaltung rangesteuert wird. Die Hilfsspannung uh für die beiden Kaskodetransistoren t2, t4 ist identisch mit der Realisierung gemäß Fig. 1. Aufwendigere Schaltungen, die der Stabilisierung der Hilfsspannung uh dienen, sind bekannt, haben mit der eigentlichen Erfindung jedoch nichts zu tun. Bei der bekannten Strombankregelung nach Fig. 2 wird die gemeinsame Strombanksteuerleitung an den Ausgang eines Operationsverstärkers op angeschlossen, dessen nichtinvertierender Eingang mit dem Stromspiegeleingang em und dessen invertierender Eingang mit einer Referenzspannung Ur gekoppelt ist. Der nichtinvertierende Eingang ist über ein RC-Glied R,C mit der gemeinsamen Massebezugsleitung M verbunden. Der vom Strombanksteuertransistor t1 gesteuerte Drain-Source-Strom i1, der auch über den Kaskodetransistor t2 fließt, hängt in seiner Größe von der Ausgangsspannung des Operationsverstärkers op ab. Demgegenüber wird der Stromspiegeleingang em von dem zeitlich beliebigen Eingangsstrom ie aus einer nicht dargestellten Quelle gespeist. Sind beide Ströme ie, i1 ungleich, dann muß dies einen Differenzstrom id zur Folge

50

haben, der an einem ersten Schaltungsknoten k1 abgreifbar ist oder in diesen Punkt eingespeist werden muß. Bei dem hier verwendeten Operationsverstärker wird wie üblich davon ausgegangen, daß die Ausgangsspannung unabhängig von der Gleichtaktspannung an den beiden Operationsverstärkereingängen ist. Damit wird erreicht, daß die Ansteuerspannung für die Strombanksteuerleitung unabhängig von der Spannung am Stromspiegeleingang em wird. Insbesondere kann durch diese Entkopplung die Spannung am Stromspiegeleingang em auch höher liegen als die Spannung der Strombanksteuerleitung. Das RC-Glied R, C ist notwendig, um die Stabilität der Schaltung sicherzustellen. Durch die Regelwirkung ändert sich der Drain-Source-Strom i1 und gleicht sich dem Eingangsstrom ie an. Das Regelziel ist erreicht, wenn kein Differenzstrom id mehr fließt und damit die Strombanksteuerleitung cl ihr richtiges Potential erreicht hat. Mit der Größe des Stromes i1 hat sich selbstverständlich auch der Ausgangsstrom ia der Strombank mb und damit des eigentlichen Stromspiegels m proportional mitgeändert.

Wie bereits angegeben, ist die Schaltung nach Fig. 2 sehr aufwendig, wobei für stationäre oder sich langsam ändernde Eingangsströme ie das Verhalten der Schaltung zufriedenstellend ist. Wenn sich die Eingangsströme ie jedoch rasch ändern und die Ausgangsströme ia diesen Änderungen folgen sollen, dann ist das zeitliche Verhalten der Regelschleife zu beachten. Kritisch ist hierbei die Verteilung der Pole und Nullstel-Ien der geschlossenen Regelschleife in der komplexen Frequenzebene, die mit den Kapazitäten c1, c2, c3 verkoppelt sind. Der erste Schaltungsknoten k1 ist z.B. ein hochohmiger Auskoppelpunkt und bildet mit der zugehörigen parasitären Kapazität c1 eine erste Polstelle. Eine zweite Polstelle wird durch den gegengekoppelten Operationsverstärker op und das RC-Glied R,C gebildet, wobei die Frequenzgegenkopplung des Operationsverstärkers durch den Kondensator c2 schematisch angedeutet ist. Im normalen Frequenzbereich des Operationsverstärkers ist sein Ausgangssignal in jedem Fall um 90° gegenüber seinem Eingangssignal in der Phase gedreht. Schließlich stellen die Gate-Kapazitäten c3 der Strombanktransistoren t1, t3 und zugehörige parasitäre Kapazitäten eine dritte Polstelle dar, die in Verbindung mit dem Ausgangswiderstand des Operationsverstärkers wirksam wird. Die drei Zeitkonstanten der Polstel-Ien bewirken eine Phasendrehung, die den Regelkreis leicht zum Schwingen bringen kann. Dies ist insbesondere dann kritisch, wenn die resultierenden Nullstellen/Pole für den Regelkreis frequenzmäßig benachbart sind und die Schleifenverstärkung dort noch groß genug ist. Als Abhilfe wird entweder die Schleifenverstärkung reduziert oder durch Vergrößerung der Kapazität c2 eine dominante Polstelle erzeugt oder eine Polstelle wird durch eine Nullstelle, hier das RC-Glied R, C, teilweise kompensiert. Alle Maßnahmen beeinflussen das Regelverhalten jedoch ungünstig, weil die Regelgeschwindigkeit verlangsamt wird.

In Fig. 3 ist ein Ausführungsbeispiel für einen Stromspiegel nach der Erfindung dargestellt. Schaltungsteile, die identisch zu denen in Fig. 1 oder Fig. 2 sind, werden mit gleichen Bezugszeichen dargestellt, insbesondere fallen hierunter die Schaltungsteile des eigentlichen Stromspiegels m. Wie in Fig. 2 wird der Eingangsstrompfad des Stromspiegels m aufgetrennt und aus dem zugeführten Eingangsstrom ie und dem Strom i1 der Strombank mb ein Differenzstrom id gebildet, der über eine Regelschaltung r das Potential der Strombanksteuerleitung cl regelt. Die Regelschaltung r enthält dabei eine stromgesteuerte Stromquelle q, deren niederohmiger Steuereingang mit dem Differenzstrom id gespeist ist und deren hochohmiger Ausgang, der Schaltungsknoten k3, direkt mit der Strombanksteuerleitung cl verbunden ist. Die Verwendung einer Stromquelle q zur Ansteuerung der Strombanktransistoren t1, t3 ist ein wesentlicher Punkt der Erfindung, denn in der Regel wird davon ausgegangen, daß MOS-Transistoren über die Gate-Elektroden spannungs- und nicht stromgesteuert sind und ihre Ansteuerung daher möglichst niederohmig sein sollte, insbesondere wenn die Aufoder Entladung der Gate-Kapazitäten sehr schnell sein soll. Der gesteuerte Ausgangsstrom der Stromquelle q dient indessen bei der Strombank mb als Gate-Strom ig für die Gate-Kapazitäten c3, um die Strombank mb den Schwankungen des Eingangstromes ie nachzuführen. Durch den Gate-Strom ig wird das Ansteuerpotential u3 der Strombanktransistoren t1, t3 geändert. Wenn das Regelziel erreicht ist, also der Eingangsstrom ie gleich dem Strombankstrom i1 ist, dann ist der am ersten Schaltungsknoten k1 abgegriffene Differenzstrom id zu Null geworden, wodurch auch der Ausgangsstrom ig der Stromquelle q zu Null wird. Das Gate-Ansteuerpotential u3 hat dann seinen Sollwert erreicht - der Regelvorgang ist abgeschlossen.

Die beschriebene Funktionsweise des Regelvorgangs macht deutlich, daß sowohl der Differenzstrom id als auch der Gate-Strom ig nicht unidirektional sein dürfen, sondern die Ströme müssen in positiver oder negativer Richtung fließen können. Dies wird durch die Implementierung der Stromquelle q in Fig. 3 erreicht. Die in CMOS-Technik ausgeführte Schaltung ist sehr vorteilhaft, da die Stromaufnahme wegen der geringen Anzahl der Querstrompfade gering ist. Insbesonders fügt sich eine Viertransistorzelle t6, t7, t8, t9 als Spannungsfolger sf in die Stromquelle q so ein, daß allen vier Transistoren eine Doppelfunktion zukommt. Der Spannungsfolger sf dient dazu, den Spannungspegel des ersten Schaltungsknotens k1, und damit Eingang em des eigentlichen Stromspiegels m in seinem Potential festzulegen. Dies wird durch die Verbindung des Spannungsfolgereingangs k4 mit einer Referenzspannungsquelle Ur erreicht, deren Potential u4 auf den Ausgang k2 des Spannungsfolgers sf übertragen wird. Die symmetrische Ausbildung der Viertransistorzelle mit den n-Kanal-Transistoren t6, t7 und den p-Kanal-Transistoren t8, t9 bewirkt, daß am Ausgang k2 des Spannungsfolgers sf positive oder negative Ströme abgreifbar sind. Da der Ausgang k2 des Spannungsfolgers sf zugleich der Steuereingang der Stromquelle q ist, wird der in den Schaltungsknoten k2 eingespeist Differenzstrom id über zwei zusammenwirkende komplementäre Stromspiegel m1, m2 in den Querstrompfad pf mit dem Schaltungsknoten k2 zurückgespiegelt. Der in den Schaltungsknoten k2 eingekoppelte Differenzstrom id stört das vorgegebene Stromgleichgewicht der zusammenwirkenden Stromspiegel m1, m2 und erzeugt einen Differenzstrom ig, der an einem Schaltungsknoten k3 abgegriffen werden kann. Dies ist der Gate-Strom ig. Der hochohmige Abgriff k3 wird durch den gemeinsamen Verbindungspunkt der Drain-Anschlüsse eines n-Kanal-Transistors t13 und des p-Kanal-Transistors t9 gebildet. Der n-Kanal-Transistor t13 ist der Ausgangstransistor des n-Kanal-Stromspiegels m2 und der Transistor t9 ist der p-Kanal-Ausgangstransistor der Viertransistorzelle. Der Schaltungsknoten k3 stellt damit den Ausgang der Stromquelle q dar. Um die Funktionsweise des eigentlichen Stromspiegels m und der Stromquelle q in getrennter Form besser beschreiben zu können, ist in Fig. 3 und zugehöriger Beschreibung der gemeinsame Verbindungspunkt k1, k2 als getrennter Schaltungsknoten k1, k2 dargestellt.

Das Potential u4 der Referenzspannungsquelle Ur bestimmt wie beschrieben den Pegel u2 des Stromspiegeleingangs em. Durch entsprechende Wahl der Hilfsspannung uh kann auf einfache Weise das Gate-Ansteuerpotential für die Kaskodestufen t2, t4 niedriger als die Stromspiegeleingangsspannung u2 eingestellt werden. Die Ausgangsspannung u3 der Stromquelle q entspricht bis auf die Sättigungsspannungen der Transistoren t13 bzw. t9 dem gesamten Bereich der Spannung u2.

Der Ruhestrom der in Kette geschalteten beiden Stromspiegel m1, m2 wird durch die Stromquellenströme i6, i8 im Eingang des Spannungsfolgers sf eingestellt. Eine interne Verkopplung der beiden Stromquellen macht die Ströme i6 und i8 gleichgroß. Da die Potentiale der Schaltungsknoten k2 und k4 einander gleich sind, können die n-Kanal-Transistoren t6, t7 bzw. die p-Kanal-Transistoren t8, t9 jeweils als Stromspiegel angesehen werden, die den Stromquellenstrom i6 bzw. den gleichgroßen Strom i8 auf den jeweiligen Ausgang spiegeln. Diesen Strömen überlagert sich der Differenzstrom id, der in der einen Richtung über die Stromspiegel m1, m2 und in der anderen Richtung über den Transistor t9 dem Schaltungsknoten k3 zugeführt wird. Wenn die Stromspiegel m1, m2 jeweils ein Stromübersetzungsverhältnis 1:1 aufweisen, dann ist der abgreifbare Ausgangsstrom ig identisch mit dem zugeführten Differenzstrom id. Es sind auch aufwendigere Stromquellenschaltungen realisierbar, die zwischen dem Einund Ausgang ein von 1 unterschiedliches Stromübersetzungsverhältnis aufweisen, beispielsweise zwischen 0,1 und 10. Dies beeinflußt die Auf oder Entladung der Strombanktransistoren t1, t3, verändert aber auch die Stabilitätsreserve. Die ist indessen bei der gewählten Schaltungsanordnung von Fig. 3 sehr groß, da die

dominante Zeitkonstante durch die Gate-Kapazität c3 der Strombanksteuerleitung cl in Verbindung mit dem hochohmigen Anschlußpunkt k3 gebildet wird. Denn die mit dem Schaltungsknoten k1 verkoppelte parasitäre Kapazität c1 "sieht" lediglich den niederohmigen Ausgang k2 des Spannungsfolgers sf.

Die schematische Darstellung der Hilfsspannungsquelle t5, der Referenzspannungsquelle Ur und der Stromquellen für die Ströme i6, i8 in Fig. 3 schließt bekannte Maßnahmen zur Verbesserung der jeweiligen Schaltungsfunktion nicht aus, z.B. die Verwendung von Bandgap-Schaltungen zur Erzeugung von stabilen Spannungen oder Strömen. Ferner zeigt Fig. 3 vom eigentlichen Stromspiegel m lediglich einen einzigen Ausgangsstrompfad für den Strom ie. Weitere Stromausgänge, auch mit beliebigen Stromübersetzungsverhältnissen, sind der besseren Übersicht wegen nicht dargestellt. Das Ausführungsbeispiel von Fig. 3 enthält in der stromgesteuerten Stromquelle q CMOS-Transistoren. Selbstverständlich ist eine stromgesteuerte Stromquelle auch in reiner n-bzw. p-Kanal-Technik realisierbar.

## Patentansprüche

## 1. Stromspiegel in MOS-Technik mit

- einer Strombank (mb), die ein- und ausgangsseitig weit aussteuerbare Kaskodestufen (t2, t4) enthält,

- einer Regelschaltung (r, p), die das Festpotential der Kaskodestufen (t2, t4) erzeugt und deren Steuereingang ein Differenzstrom (id) zugeführt ist, und

- einem ersten Schaltungsknoten (k1), der zwischen einem Stromspiegeleingang (em) und einer mit einem zugehörigen Ausgang der Strombank (mb) gekoppelten ersten Kaskodestufe (t2) liegt und an dem der Differenzstrom (id) abgreifbar ist, dadurch gekennzeichnet, daß

- die Regelschaltung (r) eine stromgesteuerte Stromquelle (q) enthält, deren Steuereingang, der zweite Schaltungsknoten (k2), mit dem ersten Schaltungsknoten (k1) und deren Ausgang, der dritte Schaltungsknoten (k3), mit einer gemeinsamen Steuerleitung (cl) für die Strombank (mb) verbunden ist, und

- am dritten Schaltungsknoten (k3) eine kapazitive Last (c3), die insbesondere durch die kapazitive Belastung der gemeinsamen Steuerleitung (cl) gebildet ist, zur Einstellung einer Regelzeitkonstanten angeschlossen ist.

20

10

- Stromspiegel nach Anspruch 1, dadurch gekennzeichnet, daß die Stromquelle (q) zwischen ihrem Ein- und Ausgang, dem zweiten bzw. dritten Schaltungsknoten (k2 bzw. k3), ein Stromübersetzungsverhältnis aufweist, das zwischen 0,1 und 10, 5 insbesondere im Bereich von 1 liegt.

- 3. Stromspiegel nach Anspruch 2, dadurch gekennzeichnet, daß die Stromquelle (q) zur Festlegung des Potentials am zweiten Schaltungsknoten (k2) einen Spannungsfolger (sf) enthält, dessen Eingang, ein vierter Schaltungsknoten (k4), mit einer Referenzspannungsquelle (Ur) verbunden ist und dessen niederohmiger Ausgang identisch mit dem Eingang (k2) der Stromquelle (q) ist.

- Stromspiegel nach Anspruch 3, dadurch gekennzeichnet, daß die Stromquelle (q) zwei zusammenwirkende komplementäre Stromspiegel (m1, m2) enthält.

- 5. Stromspiegel nach Anspruch 4, dadurch gekennzeichnet, daß ein Strompfad (pf) der zusammenwirkenden komplementären Stromspiegel (m1, m2) den Ausgang des Spannungsfolgers (sf) enthält, indem in den Strompfad (pf) ein komplementäres Transistorpaar (t7, t9) in Serienschaltung eingefügt ist, deren gemeinsamer Source-Anschluß den zweiten Schaltungsknoten (k2) bildet und deren Gate-Anschlüsse über jeweils eine MOS-Diode (t6 bzw t8) mit dem vierten Schaltungsknoten (k4) verbunden sind.

- 6. Stromspiegel nach Anspruch 5, dadurch gekennzeichnet, daß der als Ausgang der stromgesteuerten Stromquelle (q) dienende dritte Schaltungsknoten (k3) durch den gemeinsamen Drain-Anschluß zwischen zwei komplementären, in Serie geschalteten Transistoren (t9, t13) im Strompfad (pf) gebildet ist.

- 7. Stromspiegel nach einem der Ansprüche 3 bis 6, dadurch gekennzeichnet, daß der Spannungsfolger (sf) eine Viertransistorzelle aus zwei komplementären Transistorpaaren (t6, t8 bzw. t7, t9) enthält, deren Transistoren unabhängig vom Leitungstyp zueinander in ihren elektrischen Eigenschaften gepaart sind.

50

40

55