Europäisches Patentamt

European Patent Office

Office européen des brevets

EP 0 743 586 A1

(12)

### **DEMANDE DE BREVET EUROPEEN**

(43) Date de publication:20.11.1996 Bulletin 1996/47

(51) Int. Cl.<sup>6</sup>: **G05F 3/26**, G05F 3/24

(11)

(21) Numéro de dépôt: 96401074.8

(22) Date de dépôt: 15.05.1996

(84) Etats contractants désignés: CH DE FR GB LI

(30) Priorité: 17.05.1995 FR 9505920

(71) Demandeur: C.S.E.M. CENTRE SUISSE

D'ELECTRONIQUE ET DE MICROTECHNIQUE

SA

CH-2007 Neuchâtel (CH)

(72) Inventeur: Chevroulet, Michel Alain 2000 Neuchatel (CH)

(74) Mandataire: Caron, Gérard et al CABINET DE BOISSE, L.A. DE BOISSE - J.P. COLAS, 37 avenue Franklin D. Roosevelt 75008 Paris (FR)

# (54) Circuit intégré dans lequel certains composants fonctionnels sont amenés à travailler avec une même caractéristique de fonctionnement

(57) Dans ce circuit intégré un générateur de référence central (3) élabore une information de consigne déterminant la caractéristique de fonctionnement devant être commune à certains composants fonctionnels du circuit.

Des moyens (4-1 à 4-n) distribuent cette information parmi des unités du circuit comprenant chacune un composant fonctionnel (2-n).

Dans chaque unité, des moyens locaux d'ajustement (5-n) reçoivent l'information de consigne et élabo-

rent une valeur d'ajustement. Des moyens de correction ajustent la caractéristique de fonctionnement d'un dispositif prévu dans les moyens locaux d'ajustement (5-n), en fonction de la valeur d'ajustement. Le dispositif est placé à proximité du composant fonctionnel et configuré de telle sorte que la caractéristique de fonctionnement qui lui est ainsi imposée, s'impose également à ce composant.

10

15

25

40

### Description

La présente invention concerne les circuits intégrés dans lesquels certains ou tous les composants ou groupes de composants fonctionnels doivent travailler dans les mêmes conditions pour assurer le bon fonctionnement du circuit dans son ensemble.

Lorsque dans un circuit intégré tel qu'un circuit MOS, deux composants, par exemple deux transistors, se trouvent à proximité l'un de l'autre, ii est relativement facile de leur donner les mêmes conditions de fonctionnement, par exemple la même courbe caractéristique du courant de drain  $I_D$  en fonction de la tension de grille  $V_{\alpha}$ .

En revanche, lorsque les composants sont éloignés l'un de l'autre dans le circuit, ou à fortiori, lorsque de nombreux composants doivent travailler dans les mêmes conditions, les paramètres des composants seront alors tributaires de leur éloignement topographique dans le circuit, celui-ci ne pouvant pratiquement pas être fabriqué avec l'uniformité nécessaire. D'ailleurs d'autres facteurs, tels que des différences de température d'un endroit à l'autre d'un circuit, peuvent induire une non-uniformité des paramètres de fonctionnement des composants.

Une technique actuellement utilisée pour imposer des caractéristiques de fonctionnement identiques à des transistors éloignés d'un circuit intégré consiste à leur imposer un paramètre (par exemple un courant) et on règle une grandeur déterminant la caractéristique (par exemple la tension de grille). Cette méthode présente l'inconvénient que le courant de commande ne peut pas être exploité simultanément par les deux transistors et il faut alors les commander alternativement. De ce fait les transistors ne sont disponibles pour effectuer la fonction qui leur est assignée dans le circuit que lorsqu'ils ne sont pas en régime de régulation. En outre, le nombre de transistors que l'on peut ainsi faire travailler dans les mêmes conditions est forcément limité, car sinon la fréquence avec laquelle le courant de commande est distribué séquentiellement deviendra trop élevée vis-à-vis de celle du signal utile à traiter.

Cette méthode connue présente donc des inconvénients certains.

L'invention a pour but de fournir un circuit intégré comportant des moyens pour imposer à une pluralité de ses composants ou groupes de composants une même caractéristique de fonctionnement, ce circuit étant dépourvu des inconvénients de la technique antérieure décrite brièvement ci-dessus.

L'invention a donc pour objet un circuit intégré caractérisé en ce qu'il comprend:

des moyens formant un générateur de référence central destiné à élaborer au moins une information de consigne qui détermine la caractéristique de fonctionnement devant être commune à tous les composants fonctionnels du circuit;

- des moyens pour distribuer l'information de consigne parmi une pluralité d'unités du circuit comprenant chacune au moins un desdits composants fonctionnels;

- chacune desdites unités comprenant des moyens locaux d'ajustement connectés pour recevoir ladite information de consigne et pour élaborer une valeur d'ajustement;

- des moyens de correction dans chaque unité pour ajuster la caractéristique de fonctionnement d'un dispositif prévu dans lesdits moyens locaux d'ajustement, en fonction de ladite valeur d'ajustement, ledit dispositif étant placé à proximité du ou des composant(s) fonctionnel(s) et configuré de telle sorte que la caractéristique de fonctionnement qui lui est ainsi imposée, s'impose également au(x)dit(s) composant(s) fonctionnel(s);

- des moyens de correction dans chaque unité pour ajuster la caractéristique de fonctionnement de son ou ses composant(s) fonctionnel(s) en fonction de ladite valeur d'ajustement.

D'autres caractéristiques et avantages de l'invention apparaîtront au cours de la description qui va suivre, donnée uniquement à titre d'exemple et faite en se référant aux dessins annexés sur lesquels:

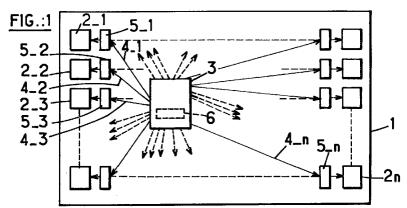

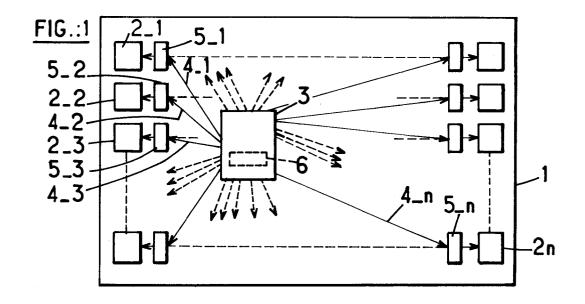

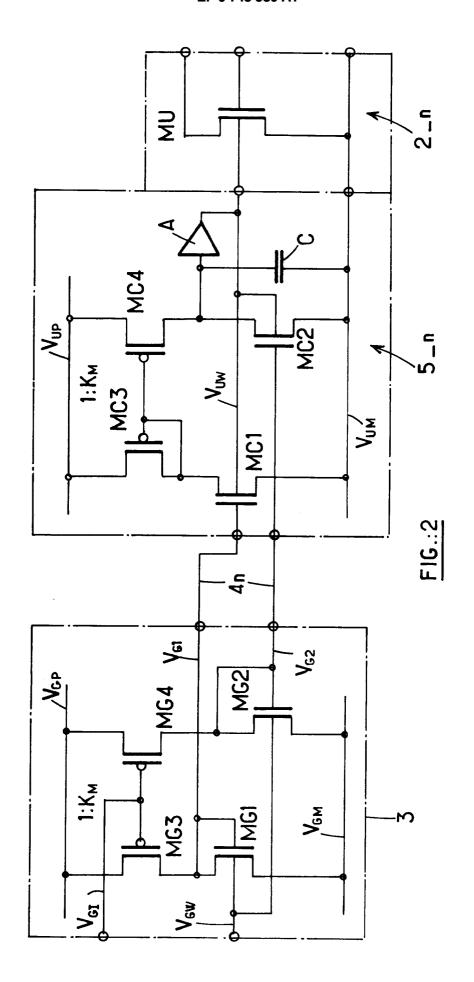

- la figure 1 est un schéma très simplifié d'un circuit intégré pour mettre en évidence les caractéristiques essentielles de l'invention; et

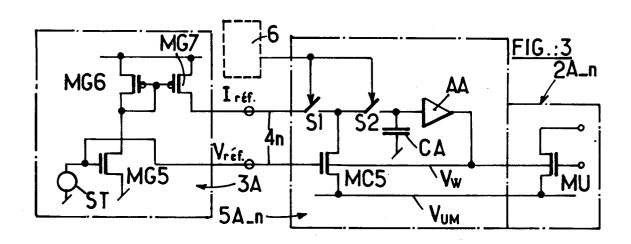

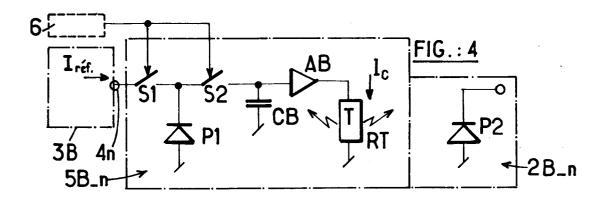

- les figures 2 à 4 montrent trois exemples d'application de l'invention.

Sur la figure 1, on a représenté un schéma général très simplifié d'un circuit intégré comportant un système selon l'invention.

Le circuit intégré symbolisé par le rectangle 1, comporte une pluralité d'unités fonctionnelles 2-1 à 2-n réparties sur le circuit intégré et dont on suppose qu'elles doivent toutes travailler avec une même caractéristique de fonctionnement.

Dans ce contexte, il faut noter que l'on entend par circuit intégré tout ensemble fonctionnel pouvant comprendre une ou plusieurs puces, les unités fonctionnelles pouvant être des composants ou groupes de composants de toute nature tels que des transistors, des diodes, des groupes de transistors, des groupes de diodes, des parties de circuit composées d'assemblages de tels composants etc. Par ailleurs, bien que la figure 1 montre une répartition régulière de ses unités fonctionnelles, ceci n'est pas un élément limitatif du concept de l'invention, ces unités pouvant être implantées dans le circuit uniquement en fonction des besoins et des tâches spécifiques que le circuit intégré doit accomplir.

Selon l'invention, le circuit intégré comporte un générateur de consigne central 3 implanté à un endroit approprié de ce circuit et destiné à élaborer un signal de consigne en fonction duquel la caractéristique de fonc-

20

25

40

45

tionnement des unités fonctionnelles va être élaborée. Ce générateur comporte n sorties reliées à autant de lignes 4-1 à 4-n qui sont respectivement connectées à des cellules locales d'ajustement 5-1 à 5-n. Ces cellules sont respectivement associées aux unités fonctionnelles 2-1 à 2-n en étant placées près de leur unité respective.

L'information de consigne élaborée dans le générateur central 3 peut être appliquée simultanément aux cellules d'ajustement 5-1 à 5-n, mais selon une caractéristique particulière de l'invention, elle peut également être envoyée séquentiellement à ces cellules, cas dans lequel le générateur central 3 comporte un séquenceur 6 représenté en pointillés dans le rectangle qui symbolise le générateur de consigne 3. Cette variante de l'invention est surtout utile lorsque l'information de consigne ne peut être utilisée sans être altérée par plusieurs cellules d'ajustement à la fois.

Il est à noter que dans un circuit intégré comprenant un système selon l'invention, les unités fonctionnelles restent opérationnelles en permanence, même si l'information de consigne ne parvient que séquentiellement à leur cellule d'ajustement associée.

On va maintenant décrire plusieurs exemples d'application du concept selon l'invention.

Concernant un premier de ces exemples, on remarquera que souvent, du fait de certains aléas technologiques, les tensions de seuil des transistors d'un circuit intégré MOS ne sont pas les mêmes sur toute l'étendue du circuit. Le premier exemple décrit vise par conséquent à imposer à tous les transistors du circuit une même tension de seuil dite "apparente". Dans ce premier exemple, on suppose ainsi que la caractéristique devant être imposée aux transistors du circuit (qui sont ici les unités fonctionnelles) est cette tension de seuil apparente. L'ajustement des tensions de seuil de tous les transistors à une même valeur, permet l'échange simplifié d'informations analogiques entre différentes parties du circuit intégré, ces informations étant ainsi interprétées de la même façon partout dans le circuit.

On sait qu'un transistor MOS de type n fonctionnant en forte inversion laisse passer un courant de drain  $I_D$  qui présente la relation suivante:

$$I_D = k(V_G - V_{TA})^2 \tag{1}$$

dans laquelle  $I_D$  est le courant de drain du transistor,  $V_G$  sa tension de grille et  $V_{TA}$  sa tension de seuil apparente pour autant que  $V_G >> V_{TA}$ , c'est-à-dire lorsque le transistor travaille en forte inversion.

On sait également que la tension de seuil apparente  $V_{TA}$  d'un transistor MOS est définie par la relation suivante:

$$V_{TA} = V_T + nV_S - (n-1)V_W$$

(2) 55

dans laquelle  $V_{\mathsf{T}}$  est la tension de seuil "physique" du transistor,  $V_{\mathsf{S}}$  sa tension de source,  $V_{\mathsf{W}}$  la tension de

caisson et n le coefficient de couplage défini comme suit:

$$n = 1 + \frac{C_D}{C_i} \tag{3}$$

Dans la relation (3), C<sub>D</sub> est la capacité de déplétion du transistor et C<sub>i</sub> sa capacité d'oxyde.

Il est à noter que l'on peut écrire les mêmes relations, mutatis mutandis, pour un transistor de type p.

Il résulte de la relation (2) ci-dessus, que la tension de seuil apparente  $V_{TA}$  de tous les transistors du circuit peut être déterminée en ajustant la tension de caisson  $V_{W}$ .

Dans le premier exemple d'application de l'invention décrit, c'est cette propriété qui est exploitée pour ajuster la tension de seuil de tous les transistors utiles du circuit intégré et à cet effet on utilise le circuit qui va maintenant être décrit en référence à la figure 2.

Par souci de simplification, cette figure ne représente que le générateur de consigne 3, ainsi qu'un seul transistor utile 2-n avec sa cellule locale d'ajustement 5-n associée.

Le générateur de consigne 3 représenté sur la figure 2 est destiné à des transistors de type n. Il comporte deux transistors MG1 et MG2 dont les sources sont reliées à un conducteur d'alimentation négative de tension  $V_{GM}$ . Leurs drains sont reliés à leurs grilles respectives, et aux drains de deux transistors respectifs MG3 et MG4 montés en miroir de courant. Les caissons des transistors MG1 et MG2 sont reliés à une borne d'alimentation  $V_{GW}$ . Les grilles des transistors MG3 et MG4 sont connectées à une borne de tension de polarisation  $V_{GI}$ , tandis que leurs sources sont reliées à une tension d'alimentation positive  $V_{GP}$

Comme les transistors MG1 à MG4 sont placés très près l'un de l'autre sur le circuit intégré, leurs tensions de seuil apparentes sont identiques deux à deux.

Par ailleurs, les transistors ayant un rapport de largeur déterminé, ils conduisent des courants  $I_{MG3}$  et  $I_{MG4}$  ayant ce rapport:

$$K_m = \frac{I_{MG4}}{I_{MG3}} \tag{4}$$

Les transistors MG1 et MG2 conduiront des courants  $I_{MG3}$  et  $I_{MG4}$  qui déterminent les tensions de grille  $V_{G1}$  et  $V_{G2}$  respectifs. En effet, il résulte des équations (1) et (2) ci-dessus que ces tensions sont liées en régime de forte inversion par la relation:

$$K_{M} = \left(\frac{V_{G1} - V_{T} - nV_{S} + (n-1)V_{W}}{V_{G2} - V_{T} - nV_{S} + (n-1)V_{W}}\right)^{2}$$

(5)

Ainsi, les tensions  $V_{G1}$  et  $V_{G2}$  peuvent constituer une information de consigne qui peut être exploitée

35

dans la cellule locale d'ajustement 5-n pour déterminer, pour le transistor utile 2-n qui y est associé, une tension de seuil apparente  $V_{TA}$  identique en utilisant la tension de caisson  $V_W$  comme paramètre d'ajustement, les tensions de seuil réelles de tous les transistors utiles pouvant être différentes d'une cellule à l'autre.

La cellule locale d'ajustement 5-n comporte un miroir de courant formé des transistors MC3 et MC4 dont les largeurs sont dans un rapport  $K_{\rm M}$ . Ceci est relativement facile à réaliser même si la distance qui sépare le générateur de consigne 3 de cette cellule locale est relativement grande.

Les sources de ces transistors MC3 et MC4 sont reliées à une tension d'alimentation  $V_{UP}$  tandis que leurs drains sont reliés respectivement aux drains de deux transistors MC1 et MC2 dont les sources sont reliées à une tension  $V_{UM}.$  La grille du transistor MC3 est connectée à son drain. Les grilles des transistors MC1 et MC2 sont connectées respectivement aux tensions  $V_{G1}$  et  $V_{G2}$  provenant du générateur de consigne 3.

Le point commun des transistors MC2 et MC4 est raccordé à l'entrée d'un amplificateur A et à une borne d'un condensateur C. La sortie de l'amplificateur A est reliée aux caissons des transistors MC1, MC2 et MU.

Dans cette cellule d'ajustement 5-n, les transistors MC1 et MC2 fonctionnent en forte inversion et engendrent des courants respectifs déterminés par la relation (1) ci-dessus. Le miroir de courant formé par les transistors MC3 et MC4 fait une copie du courant engendré par le transistor MC1 en le multipliant par la constante K<sub>M</sub>. En régime d'ajustement, le condensateur C intègre la différence entre le courant traversant le transistor MC4 et le courant traversant MC2. L'amplificateur transmet la valeur correspondant sur les caissons des transistors MC1 et MC2 et également sur celui du transistor utile MU. Le régime se stabilise lorsque la différence de ces courants est nulle. Dans ces conditions, le transistor MU présente une tension de seuil apparente qui est identique à celle des transistors MG1 et MG2 du générateur de consigne.

Ainsi en associant à chaque transistor utile ou à chaque groupe de transistors utiles se trouvant à proximité l'un de l'autre une cellule d'ajustement telle que la cellule 5-n, on peut leur donner la même tension de seuil dont la valeur est imposée par le générateur central de consigne 3.

On remarquera que, dans ce premier exemple d'application de l'invention, tous les transistors utiles 2-1 à 2-n peuvent travailler en permanence et ne sont pas perturbés par l'ajustement de la tension de leur caisson.

Dans un second exemple d'application de l'invention, on suppose qu'il soit souhaitable de faire fonctionner un certain nombre de transistors d'un circuit intégré sur un même point de travail en dépit des disparités de leurs courbes caractéristiques  $I_{drain}/V_{grille}$  en fonction des emplacements des transistors dans le circuit intégré.

Sur la figure 3, on a représenté un générateur central de consigne 3A qui élabore dans ce cas en tant que consigne, une tension de référence  $V_{ref}$  et un courant de référence  $I_{ref}$ . Comme il s'agit ici de transmettre une consigne de courant, il est nécessaire de distribuer ce courant de référence  $I_{ref}$  de façon séquentielle.

Le générateur de consigne 3A comprend une source de tension ST qui est reliée à la grille d'un transistor MG5 et à une sortie du générateur délivrant la tension de référence  $V_{\rm ref}$ . Le drain du transistor MG5 est connecté à un miroir de courant formé des transistors MG6 et MG7, ce dernier délivrant le courant de référence  $I_{\rm ref}$ .

La cellule locale d'ajustement 5A-n comporte un transistor MC5 dont la grille reçoit la tension V<sub>ref</sub>. Son drain est raccordé à deux interrupteurs S1 et S2 commandés par le séquenceur 6. L'interrupteur S1 reçoit le courant de référence l<sub>ref</sub> du générateur de consigne 3A. L'interrupteur S2 est connecté au point commun d'un condensateur CA et d'un amplificateur AA. La sortie de ce dernier est reliée aux caissons des transistors MC5 et MU (2A-n).

Lorsque la cellule 5A-n est en phase d'ajustement, ces interrupteurs S1 et S2 étant alors fermés par le séquenceur 6, le courant l<sub>ref</sub> peut parvenir au condensateur CA et à l'entrée de l'amplificateur AA. La tension sur le condensateur CA se stabilise, lorsque le courant qui traverse le transistor MC5 est égal au courant de référence l<sub>ref</sub>. Les interrupteurs S1 et S2 peuvent alors de nouveau être ouverts, le condensateur CA mémorisant la tension d'ajustement à l'entrée de l'amplificateur AA. Le courant de référence l<sub>ref</sub> peut alors être envoyé à une autre cellule locale d'ajustement du circuit intégré.

On voit donc que, dans ce cas également, le transistor utile peut continuer à fonctionner qu'il soit en régime d'ajustement ou non.

Le troisième exemple d'application de l'invention est représenté sur la figure 4. Ici, les composants utiles ne sont pas des transistors, mais des diodes ou des photodiodes, ces dernières pouvant, par exemple faire partie d'un réseau de détecteurs ou analogue. Il peut alors être important que toutes ces diodes aient le même courant de fuite. Or, on sait que le courant de fuite d'une diode est fortement dépendant de la température.

Le générateur central de consigne 3B engendre, par exemple au moyen du montage représenté sur la figure 3 en 3A, un courant de référence l<sub>ref</sub> qui est distribué aux cellules locales d'ajustement telles que la cellule 5B-n, au moyen du séquenceur 6.

La cellule locale d'ajustement 5B-n comporte une diode P1 qui est connectée aux interrupteurs S1 et S2, ceux-ci étant fermés en régime d'ajustement. L'interrupteur S2 est connecté également au point commun d'un condensateur CB et de l'entrée d'un amplificateur AB. La sortie de ce dernier est reliée à une résistance de dissipation de chaleur RT placée près de la diode P1 et de la diode utile P2 (2B-n). Un courant  $I_{\rm C}$  est donc

10

15

25

envoyé en tant que valeur d'ajustement dans cette résistance dissipatrice RT. La diode P2 (et éventuellement d'autres diodes se trouvant à proximité) recevra(ont) ainsi un apport calorique qui détermine un même courant de fuite pour toutes les diodes.

Le courant passe dans la résistance dissipatrice RT tant que le courant dans la diode P1 n'est pas égal au courant de référence I<sub>ref</sub>. Le séquenceur 6 permet de desservir d'autres montages de chauffage analogue répartis dans le réseau de photodiodes.

Il est à noter que si les diodes P1 et P2 sont identiques (elles se trouvent à proximité l'une de l'autre) et si seulement la photodiode P2 est exposée à la lumière, ce montage permet en outre de commander le courant "noir" de la photodiode P2.

Par ailleurs, les cellules locales d'ajustement doivent être isolées thermiquement l'une de l'autre.

Il est à noter que dans ce cas également, le condensateur CB joue le rôle de mémoire et conserve la valeur de consigne entre deux adressages effectués par le séquenceur 6.

#### Revendications

- 1. Circuit intégré caractérisé en ce qu'il comprend:

- des moyens formant un générateur central de référence (3, 3A, 3B) destiné à élaborer au moins une information de consigne (V<sub>G1</sub>, V<sub>G2</sub>; I<sub>ref</sub>, V<sub>ref</sub>; I<sub>ref</sub>) qui détermine la caractéristique de fonctionnement devant être commune à au moins une pluralité des composants fonctionnels du circuit;

- des moyens (4-1 à 4-n; 6) pour distribuer l'information de consigne parmi au moins une pluralité d'unités du circuit, comprenant chacune au moins un desdits composants fonctionnels (2-n; 2A-n; 2B-n);

- chacune desdites unités comprenant des moyens locaux d'ajustement (5-n; 5A-n; 5B-n) connectés pour recevoir ladite information de consigne (V<sub>G1</sub>, V<sub>G2</sub>; I<sub>ref</sub>, V<sub>ref</sub>; I<sub>ref</sub>) et pour élaborer une valeur d'ajustement (V<sub>W</sub>, I<sub>C</sub>);

- des moyens de correction (C, A; CA, AA; CB, AB) dans chaque unité pour ajuster la caractéristique de fonctionnement d'un dispositif (MC1, MC2; MC5; P1) prévu dans lesdits moyens locaux d'ajustement (5-n; 5A-n; 5B-n), en fonction de ladite valeur d'ajustement, ledit dispositif étant placé à proximité du ou des composant(s) fonctionnel(s) et configuré de telle sorte que la caractéristique de fonctionnement qui lui est ainsi imposée, s'impose également au(x)dit(s) composant(s) fonctionnel(s) (2-n; 2A-n; 2B-n).

- Circuit intégré suivant la revendication 1, comportant des transistors MOS caractérisé en ce que ladite caractéristique de fonctionnement est la ten-

- sion de seuil apparente (V<sub>TA</sub>) d'au moins certains de ses transistors MOS (2-1 à 2-n; figure 2).

- Circuit intégré suivant la revendication 1, comportant des transistors MOS, caractérisé en ce que ladite caractéristique de fonctionnement est un point de travail prédéterminé de la courbe courant de drain/tension de grille d'au moins certains de ces transistors MOS (2A-n; figure 3).

- 4. Circuit intégré suivant la revendication 2, comportant des diodes ou des photodiodes, caractérisé en ce que ladite caractéristique de fonctionnement est le courant de fuite desdites diodes (P2; figure 4).

- Circuit intégré suivant l'une quelconque des revendications 2 et 3 prises ensemble, caractérisé en ce que ladite valeur d'ajustement est la tension de caisson (V<sub>W</sub>) d'au moins certains desdits transistors MOS (2-1 à 2-n).

- Circuit intégré suivant les revendications 2 et 5 prises ensemble, caractérisé en ce que ledit générateur central de référence (3) comporte des moyens (MG2, MG4) pour établir un premier rapport de deux courants (K<sub>M</sub>) représentatif de la valeur de ladite tension de seuil apparente (V<sub>TA</sub>) souhaitée et des moyens (MG1, MG2) pour, en fonction d'une valeur de tension de caisson prédéterminée (V<sub>GW</sub>), convertir ce premier rapport de courants en une paire de tensions (VG1, VG2) formant ladite information de consigne, et en ce que lesdits moyens locaux d'ajustement (5-1 à 5-n) comprennent des moyens (MC3, MC4) pour établir localement un second rapport de courants et des moyens (MC1, MC2, C, A) pour engendrer en fonction de ladite information de consigne, un signal de modification de la tension de caisson (VIIW) du ou desdits composants fonctionnels (2-1 à 2-n) associés auxdits moyens d'ajustement local considérés (5-1 à 5-n), pour ajuster ledit second rapport de courants audit premier rapport de courants.

- Circuit intégré suivant la revendication 6, caractérisé en ce que

- ledit générateur central de référence (3) comporte un miroir de courant formé de deux transistors MOS (MG3, MG4) dont les largeurs ont ledit premier rapport de courants et deux autres transistors MOS (MC1, MC2) montés respectivement en série avec les transistors du miroir de courant et dont la tension de caisson (V<sub>GW</sub>) présente ladite valeur prédéterminée de tension de caisson, lesdits deux autres transistors (MG1, MG2) étant agencés pour fonctionner en forte inversion et fournir ladite information de consigne (V<sub>G1</sub>, V<sub>G2</sub>) sur leurs grilles, et en ce que

45

- lesdits moyens locaux d'ajustement (5-1 à 5-n) comprennent un montage identique à celui dudit générateur central de référence (3), le point de jonction entre l'un (MC4) des transistors de leur miroir de courant et ledit autre transistor (MC2) correspondant étant raccordé à un amplificateur (A) fournissant ladite valeur d'ajustement (V<sub>UW</sub>), la sortie de cet amplificateur étant raccordée aux caissons desdits autres transistors (MC1, MC2) de ces moyens locaux d'ajustement et à celui du composant fonctionnel (MU) associé à ces moyens.

- 8. Circuit intégré suivant la revendication 3 et 5 prises ensemble, caractérisé en ce que ledit générateur central de référence (3A) comporte une source de tension (ST) délivrant une tension de référence (V<sub>ref</sub>) et une source de courant (MG5, MG6 et MG7) délivrant un courant de référence (I<sub>ref</sub>), en ce que lesdits moyens locaux d'ajustement (5A-n) comprennent un transistor (MC5) connecté pour recevoir ladite tension de référence sur sa grille, et un amplificateur (AA) connecté pour amplifier la différence entre ledit courant de référence et le courant traversant ce transistor (MC5), la sortie dudit amplificateur (AA) étant connectée au caisson de ce dernier et celui dudit composant fonctionnel (MU) pour leur fournir ladite valeur d'ajustement (V<sub>W</sub>).

- 9. Circuit intégré suivant la revendication 8, caractérisé en ce qu'il comprend un séquenceur (6) pour envoyer ledit courant de référence (I<sub>ref</sub>) tour à tour vers lesdits moyens locaux d'ajustement, et en ce que lesdits moyens locaux d'ajustement comprennent des moyens de mémoire (CA) pour conserver ladite valeur d'ajustement (V<sub>W</sub>) entre deux envois dudit courant de référence à ces moyens.

- Circuit intégré suivant la revendication 4, caractérisé en ce que ladite valeur d'ajustement est la température (T) dudit circuit.

- 11. Circuit intégré suivant la revendication 10, caractérisé en ce que ledit générateur central de référence (3B) comprend une source de courant de référence (1<sub>ref</sub>), et en ce que lesdits moyens locaux d'ajustement comprennent une diode de référence (P1), ainsi qu'un amplificateur (AB) pour amplifier la différence entre le courant de référence et le courant circulant dans ladite diode (P1), la sortie dudit amplificateur (AB) étant connectée à un composant dissipateur de chaleur (RT) placé près de ladite diode (P1) et de la diode (P2)) qui forme ledit composant fonctionnel.

- 12. Circuit intégré suivant la revendication 11, caractérisé en ce qu'il comporte un séquenceur (6) pour envoyer ledit courant de référence (I<sub>ref</sub>) tour à tour auxdits moyens locaux d'ajustement (5B-n).

# RAPPORT DE RECHERCHE EUROPEENNE Numero de la demande

EP 96 40 1074

| Catégorie                                                                                                                                                                                                | Citation du document avec<br>des parties per                      | indication, en cas de besoin,<br>tinentes                            | Revendication<br>concernée                                                                 | CLASSEMENT DE LA<br>DEMANDE (Int.Cl.6)     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--------------------------------------------|

| Х                                                                                                                                                                                                        | EP-A-0 459 715 (AME<br>TELEGRAPH) 4 Décemb                        | re 1991                                                              | 1                                                                                          | G05F3/26<br>G05F3/24                       |

| Y<br>A                                                                                                                                                                                                   | * le document en en                                               | tier *                                                               | 2-4,8<br>5-7,9-12                                                                          |                                            |

| γ                                                                                                                                                                                                        | US-A-5 157 285 (ALL<br>Octobre 1992                               | EN MICHAEL J) 20                                                     | 2,8                                                                                        |                                            |

| A                                                                                                                                                                                                        |                                                                   | 64 - colonne 9, ligne (                                              | 5 10                                                                                       |                                            |

| Υ                                                                                                                                                                                                        | 1981                                                              | LIPS NV) 23 Septembre                                                | 3                                                                                          |                                            |

|                                                                                                                                                                                                          | * page 1, ligne 6 -                                               | ligne 109 *                                                          |                                                                                            |                                            |

| Y                                                                                                                                                                                                        | 23 Novembre 1989                                                  | SUBISHI ELECTRIC CORP)  1 - colonne 4, ligne 8                       | 4                                                                                          |                                            |

| X,P                                                                                                                                                                                                      | EP-A-0 674 252 (C S<br>ELECTR) 27 Septembr<br>* le document en en |                                                                      | 1,5                                                                                        | DOMAINES TECHNIQUES RECHERCHES (Int. Cl.6) |

| A                                                                                                                                                                                                        | 1991                                                              | LIPS NV) 30 Octobre  1 - colonne 4, ligne 8                          | 1-12                                                                                       |                                            |

| A                                                                                                                                                                                                        | ;PHILIPS ELECTRÓNIC<br>1995                                       | LIPS ELECTRONICS UK LTI<br>S NV (NL)) 12 Avril<br>page 6, ligne 15 * | 1-12                                                                                       |                                            |

| Α                                                                                                                                                                                                        | US-A-4 471 292 (SCH<br>11 Septembre 1984<br>* le document en en   | TENCK STEPHEN R ET AL)                                               | 1-12                                                                                       |                                            |

|                                                                                                                                                                                                          |                                                                   | -/                                                                   |                                                                                            |                                            |

|                                                                                                                                                                                                          |                                                                   |                                                                      | _                                                                                          |                                            |

|                                                                                                                                                                                                          | ésent rapport a été établi pour to                                | utes les revendications  Date d'achèvement de la recherche           | 1                                                                                          | Examinateur                                |

|                                                                                                                                                                                                          |                                                                   | 23 Août 1996                                                         | Sch                                                                                        | obert, D                                   |

| CATEGORIE DES DOCUMENTS CITES  T: théorie ou E: document X: particulièrement pertinent à lui seul 4: particulièrement pertinent en combinaison avec un autre document de la même catégorie  L: cité pour |                                                                   |                                                                      | cipe à la base de l'<br>revet antérieur, ma<br>ou après cette date<br>mande<br>res raisons | invention<br>is publié à la                |

## RAPPORT DE RECHERCHE EUROPEENNE

Numero de la demande EP 96 40 1074

| atégorie | Citation du document avec ind<br>des parties pertin                                                                                                                                            | ication, en cas de besoin,<br>entes                                    | Revendication concernée | CLASSEMENT DE LA<br>DEMANDE (Int.Cl.6)       |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|-------------------------|----------------------------------------------|

| 4        |                                                                                                                                                                                                | (AWA TAKESHI) 21 Mars                                                  | - <del> </del>          |                                              |

|          |                                                                                                                                                                                                |                                                                        |                         | DOMAINES TECHNIQUES<br>RECHERCHES (Int.Cl.6) |

|          |                                                                                                                                                                                                |                                                                        |                         |                                              |

| Lep      | résent rapport a été établi pour touto<br>Lieu de la recherche<br>LA HAYE                                                                                                                      | es les revendications  Date d'achèvement de la recherche  23 Août 1996 | Scho                    | Examinateur<br>Obert, D                      |

| Y:pa     | CATEGORIE DES DOCUMENTS CITES  X: particulièrement pertinent à lui seul Y: particulièrement pertinent en combinaison avec un autre document de la même catégorie A: arrière-plan technologique |                                                                        |                         | nvention                                     |