**Europäisches Patentamt**

**European Patent Office**

Office européen des brevets

EP 0 748 055 A2 (11)

## **EUROPÄISCHE PATENTANMELDUNG** (12)

(43) Veröffentlichungstag: 11.12.1996 Patentblatt 1996/50 (51) Int. Cl.6: H03M 13/00, H04H 1/00

(21) Anmeldenummer: 96106156.1

(22) Anmeldetag: 19.04.1996

(84) Benannte Vertragsstaaten: **DE GB IT SE**

(30) Priorität: 07.06.1995 DE 19520685

(71) Anmelder: BLAUPUNKT-WERKE GMBH 31132 Hildesheim (DE)

(72) Erfinder:

- · Nyenhuis, Detlev, Dipl.-Mathematiker 31079 Sibbesse (DE)

- · Hegler, Wilhelm, Dipl.-Phys. 31134 Hildesheim (DE)

## (54)Verfahren zur Decodierung von mit einem RDS-Empfänger empfangenen Datenblöcken

(57)Es wird ein Verfahren zur Decodierung von mit einem RDS-Rundfunk-Empfänger empfangenen Datenblöcken beschrieben, bei dem der in einem 26-Bit-Schieberegister zwischengespeicherte Datenblock zweimal ausgelesen wird, so daß bei einer Fehlerkorrektur auch das Prüfwort erfaßt wird. Ferner wird eine Schaltungsanordnung zur Durchführung dieses Verfahrens erläutert.

20

35

40

## **Beschreibung**

Gegenstand des Schutzrechts ist ein Verfahren zur Decodierung von mit einem RDS-Empfänger empfangenen Datenblöcken gemäß dem Oberbegriff des Anspruchs 1 und eine zur Durchführung dieses Verfahrens geeignete Schaltungsanordnung gemäß dem Oberbegriff des Anspruchs 3.

Empfänger für das Radio-Daten-System (RDS) sind in der DIN EN 50 067 definiert. In der Unterlage dieser Norm ist auf Seite 5 im Bild 2 die Struktur eines an den MPX-Ausgang eines üblichen Rundfunkempfängers angeschlossenen RDS-Empfängers als Blockschaltbild gezeigt und auf Seite 34 im Bild B 4 ein Ausführungsbeispiel eines Decoders in dem Datenprozessor des RDS-Empfängers dargestellt und dessen Arbeitsweise erläutert.

Von der Arbeitsweise des bekannten auch fehlerkorrigierenden Decoders, die in dem Oberbegriff des Hauptanspruchs erfaßt ist, unterscheidet sich das erfindungsgemäße Verfahren durch die im Kennzeichen des Hauptanspruchs genannten Merkmale.

Das neue Verfahren bietet den Vorteil höherer Sicherheit, da bei der Fehlerkorrektur auch die Prüfbits erfaßt werden, d. h. erst ein nicht korrigierbarer Fehlerauch in den Prüfbits - führt zur Verwerfung der Daten.

Zum besseren Verständnis der Erfindung werden zunächst einige Begriffe aus der DIN EN 50 067 und die Arbeitsweise des bekannten Decoders erläutert und danach anhand der Zeichnung der erfindungsgemäße Verfahrensablauf in dem abgewandelten Decoder dargelegt. In der Zeichnung zeigt

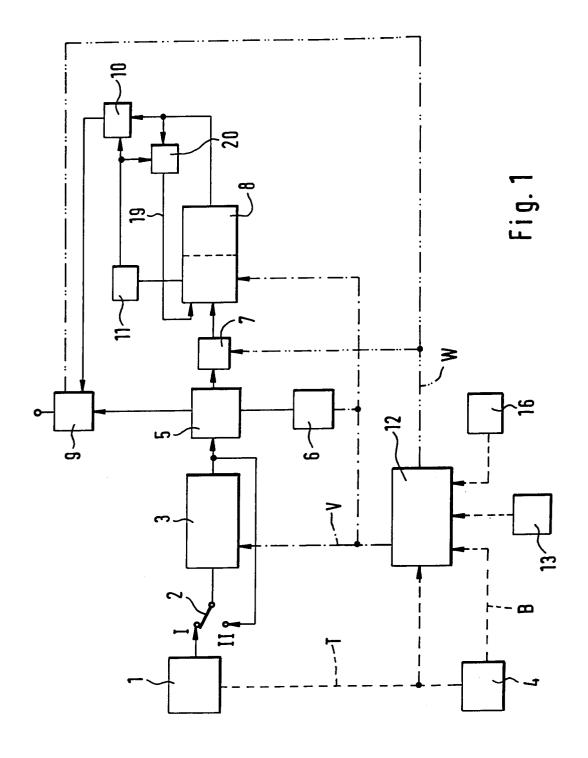

Fig. 1 das Blockschaltbild eines neuen Decoders,

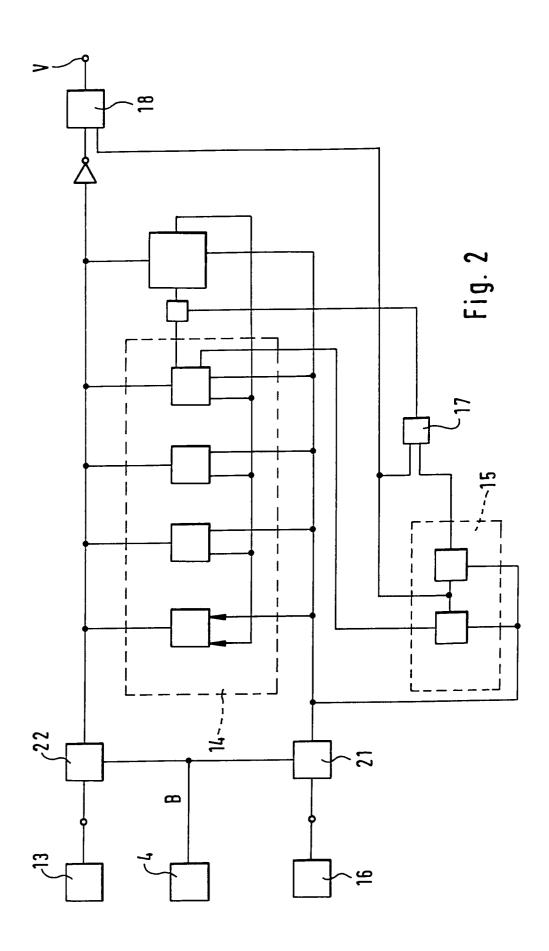

Fig. 2 das Blockschaltbild einer Takteinheit in der Steuereinheit für diesen Decoder.

Nach der DIN EN 50 067 wird auf der Senderseite dem im Empfänger an sich interessierenden Informationswort, das aus sechzehn Bits besteht, ein Prüfwort angehängt, das aus zehn Bits besteht, und diesem eines von sechs definierten Offsetworten überlagert, das ebenfalls aus zehn Bits besteht. Auf dem Weg vom Sender zum Empfänger können in den zu übertragenen Bits Fehler entstehen.

Im Empfänger muß der bekannte Decoder aus dem empfangenen unendlichen Bitstrom das Informationswort zurückgewinnen. Er ist dazu derart ausgelegt, daß er das ihm im synchronisierten Zustand bekannte Offsetwort in einer X-OR-Stufe von dem Prüfwort trennt und das Informationswort und das Prüfwort einem Syndromregister zur Fehlerprüfung zuführt und die Bits des Informationswortes derweilen zwischenspeichert. Nach der Fehlerprüfung wird das gegebenenfalls in einer weiteren X-OR-Stufe korrigierte Informationswort ausgegeben.

In dem Syndromregister sind die Speicherzellen zur Syndromberechnung derart miteinander verknüpft,

daß bei fehlerfreiem Empfang eines Codewortes das Syndrom am Blockende zu Null berechnet wird. Danach werden in der dem letzten Bit des jeweiligen Blocks zugehörigen Periode die sechzehn Informationsbit mit schnellem Takt aus dem Zwischenspeicher ausgelesen. Zugleich wird der Inhalt des Syndromregisters in diesem zum Umlauf gebracht, bei dem die Verknüpfungen zwischen den Speicherzellen wirksam bleiben. Werden dabei in die ersten fünf Zellen des Syndromregisters Nullen eingeschrieben, so wird der Umlauf des Inhalts im Syndromregister unterbrochen und danach der Inhalt des Syndromregisters Bit für Bit ausgelesen und zu dem Datenstrom aus dem Zwischenspeicher addiert. Dabei ergibt sich gegebenenfalls eine Fehlerkorrektur.

Wird der Inhalt der ersten fünf Zellen nicht Null bevor der Zwischenspeicher ausgelesen ist, so ist entweder ein nichtkorrigierbarer Fehler aufgetreten oder der Fehler liegt in den Prüfbits. Mit Beginn des nächsten Blocks wird das Syndromregister wieder auf Null gesetzt.

Im Unterschied hierzu werden in dem Verfahren nach der Erfindung die von dem RDS-Empfänger 1 über einen Datenumschalter 2 in dessen Stellung I seriell empfangenen Bits in ein 26-Bit-Schieberegister 3 eingelesen. Am Ende eines Blocks, wenn alle sechsundzwanzig Bits, die zu einem durch das Offsetwort verschlüsselten Codewort gehören, im Schieberegister 3 gespeichert sind, wird der Inhalt des Schieberegisters 3, gesteuert von Verschiebetakten V, ausgelesen, nachdem der Datenumschalter 2 in seine Stellung II geschaltet ist, in welcher der Ausgang des Schieberegisters 3 mit seinem Eingang verbunden ist, so daß der Inhalt auch im Schieberegister 3 rotiert.

Zur Erkennung eines Blockendes werden die von dem RDS-Empfänger regenerierten Bittakte T in einem Bitzähler 4 gezählt, an dessen Überlauf sich nach sechsundzwanzig Bittakten der Blocktakt B abnehmen läßt. Bei der weiteren Beschreibung des Verfahrens wird von einem synchronisierten Zustand des Decoders ausgegangen.

Der Ausgang des Schieberegisters 3 ist mit dem ersten Eingang einer ersten X-OR-Stufe 5 verbunden, deren zweiter Eingang an den Ausgang eines Offsetwortgenerators 6 angeschlossen ist. Dieser Offsetwortgenerator 6 erzeugt während der Dauer des Auslesens der letzten zehn Bits des im Schieberegister 3 gespeicherten Blocks die zehn Bits des zu dem Block gehörenden Offsetwortes.

Über eine beim ersten Auslesen geöffnete Sperrstufe 7 werden die Bits am Ausgang der ersten X-OR-Stufe 5 in ein Syndromregister 8 eingelesen, in dem das zu dem Codewort gehörende Syndrom berechnet wird. Die genaue Beschaltung des Syndromregisters mit den Elementen einer Verknüpfungsschleife 19 für die Syndromberechnung und für eine eventuelle Fehlerkorrektur ist in der DIN EN 50 067 ausführlich erläutert und begründet, so daß sie hier als bekannt vorausgesetzt wird und daher auf ihre nähere Darlegung verzichtet

20

werden kann.

Der Ausgang der ersten X-OR-Stufe 5 ist parallel zum Eingang der Sperrstufe 7 mit dem einen Eingang einer zweiten X-OR-Stufe 9 verbunden, deren zweiter Eingang an den Ausgang des Syndromregisters 8 angeschlossen ist, in dem eine Torschaltung 10 liegt, die von einer NOR-Torschaltung 11 freigegeben werden kann. An dem Ausgang der zweiten X-OR-Stufe 9 lassen sich beim zweiten Auslesen des Schieberegisters 3 die Bits des fehlerfreien Informationswortes abnehmen.

3

Bei dem hier beschriebenen Ausführungsbeispiel des erfindungsgemäßen Verfahrens ersetzt das 26-Bit-Schieberegister 3 vor der ersten X-OR-Stufe 5 den im bekannten Decoder hinter der ersten X-OR-Stufe vorgesehenen 16-Bit-Zwischenspeicher für das Informationswort.

Das zeimalige Auslesen der Bits aus dem Schieberegister 3 und die übrigen Vorgänge, wie die Sperrung der Sperrstufe 7, wird durch eine Steuereinheit 12 bewirkt, für deren Takteinheit ein Ausführungsbeispiel in Figur 2 dargestellt ist. Anhand der Fig. 2 wird die Takteinheit näher erläutert.

Für die Steuerung der Vorgänge werden jeweils zwei Pakete von sechsundzwanzig Takten innerhalb der letzten Bitperiode eines Blocks benötigt, die erkennbar voneinander getrennt sind. Dazu ist an den Eingang der Takteinheit ein 114-kHz-Generator 13 angeschlossen. Seine Impulse takten einen 4-Bit-Zähler 14, dessen Überlauf wiederum einen 2-Bit-Zähler 15 taktet. Beide Zähler werden durch einen am Reset-Eingang angelegten Reset-Impuls eines 2,37-kHz-Generators 16 gelöscht. Die Takteinheit ist derart aufgebaut, daß der 4-Bit-Zähler 14 abwechselnd bis zehn oder bis sechzehn zählt. Die Steuerung der Zählweise erfolgte durch den Ausgang einer dritten X-OR-Stufe 17 im Ausgang des 2-Bit-Zählers 15.

In dem ersten Zustand (0.0) des 2-Bit-Zählers 15 zählt der 4-Bit-Zähler 14 bis zehn. Sein Überlauf schaltet den 2-Bit-Zähler 15 in dessen zweiten Zustand (1.0). In diesem Zustand des 2-Bit-Zählers 15 zählt der 4-Bit-Zähler 14 bis sechzehn. Während dieses Zustands (1.0) und des dritten Zustands (1.1) des 2-Bit-Zählers 15, - in welchem der 4-Bit-Zähler 14 wieder bis zehn zählt - ist eine Torschaltung 18 geöffnet, an der insgesamt sechsundzwanzig Verschiebetakte V (sechzehn plus zehn) mit einer Frequenz von 114 kHz auf der Verschiebetaktleitung V erscheinen. Diese Verschiebetakte V steuern das Auslesen des Schieberegisters 3 und das Syndromregister 8. Die in dem dritten Zustand (1.1) des 2-Bit-Zählers 15 abgegebenen zehn Verschiebetakte V steuern auch die Ausgabe des Offsetwortes aus dem Offsetwortgenerator 6.

Bei dem zwölften Zählimpuls des 4-Bit-Zählers 14 im vierten Zustand (0.1) des 2-Bit-Zählers 15 ist eine 2,37-kHz-Periode abgelaufen. Damit erscheint ein Reset-Impuls aus dem 2,37-kHz-Generator 16 am Reset-Eingang und beide Zähler 14 und 15 werden gelöscht. Dabei wird ein Impuls auf die Wiederholungsleitung W gegeben. Danach beginnt der zweite Zyklus

der Takteinheit.

Die Torschaltungen 21 und 22 im Eingang und im Reseteingang der Takteinheit werden jeweils erst durch den Blocktakt B geöffnet, den der Bitzähler 4 liefert. Sie vermeiden eine Decodierung vor der letzten Bitperiode eines Blocks.

Die Steuereinheit 12 ist derart programmiert, daß nach dem Einlesen des letzten Bits eines Blocks in das Schieberegister 3, wenn der Blocktakt B erscheint, der Eingang des Schieberegisters 3 von dem RDS-Empfänger 1 getrennt und mit dem Ausgang des Schieberegisters 3 verbunden wird und das Syndrom-Register 8 gelöscht wird; z. B. wenn der 4-Bit-Zähler 14 im ersten Zustand des 2-Bit-Zählers 15 bis vier gezählt hat. Danach wird mit dem ersten Paket von 26 Verschiebetakten V der Inhalt des Schieberegisters 3 erstmals ausgelesen. Zugleich rotiert der Inhalt im Schieberegister 3. Während des Auslesevorganges wird der ausgelesene Block in der ersten X-OR-Stufe 5 mit dem aus dem Offsetwort-Generator 6 taktgleich ausgelesenen Offsetwort verknüpft und dabei das Codewort von dem überlagerten Offsetwort befreit. Das Codewort wird über die offene Sperrstufe 7 in das zuvor gelöschte Syndromregister 8 eingelesen. In dem Syndromregister 8 wird das zugehörige Syndrom durch die Verknüpfung der Zellen in der bekannten Weise errechnet und dabei eine eventuelle Fehlerkorrektur vorbereitet.

An den ersten Auslesevorgang schließt sich eine zweiter Auslesevorgang des Schieberegisters während des zweiten Zyklus der Takteinheit an. Zu Beginn des zweiten Zyklus wird, beispielsweise wenn der 4-Bit-Zähler 14 im ersten Zustand des 2-Bit-Zählers 15 bis zwei gezählt hat, die Sperrstufe 7 über die Wiederholungsleitung W gesperrt und die zweite X-OR-Stufe 9 zur Ausgabe des Codewortes freigegeben. Die Löschung des Syndromregisters 8 und eine Umschaltung des Datenumschalters 2 bei dem vierten Zähltakt wird im zweiten Zählzyklus unterdrückt. Die Sperrung der Sperrstufe 7 verhindert, daß bei dem zweiten Paket von sechsundzwanzig Verschiebetakten erneut Bits in das Syndromeingelesen werden. register Nur die Verknüpfungsschleife 19 in dem Syndromregister bleibt geschlossen, so lange das Schleifentor 20 geöffnet ist.

Sobald in den ersten fünf Zellen des Syndromregisters 8 eine Null steht, wird die Torschaltung 10 im Ausgang des Syndromregisters 8 über die NOR-Torschaltung 11 freigegeben und zugleich die Verknüpfungsschleife 19 im Syndromregister durch Sperrung des Schleifentores 20 unterbrochen. Nach der Freigabe des Syndromregisterausganges werden diejenigen Bits, welche anschließend die erste X-OR-Stufe 5 verlassen, bitweise mit den aus dem Syndromregister 8 ausgelesenen Bits in der zweiten X-OR-Stufe 9 verknüpft.

Bei dem fehlerfreien Empfang eines Codewortes ergibt schon die Syndromberechnung bei dem ersten Auslesen den Wert Null, d. h., daß in allen Zellen des Syndromregisters eine Null steht und somit auch in deren ersten fünf Zellen. Dann ist die Torschaltung 10

10

im Ausgang des Syndromregisters bereits zu Beginn des zweiten Pakets von sechsundzwanzig Taktimpulsen durch die NOR-Torschaltung 11 freigegeben und das Schleifentor 20 gesperrt.

Bei fehlerhaftem Empfang eines Codewortes ist 5 eine Korrektur immer dann möglich, wenn spätestens bis zum zweiten Auslesen des fünftletzten Bits aus dem Schieberegister die Torschaltung 10 freigegeben ist.

Die hier nur angedeuteten Vorgänge zur Fehlerkorrektur sind an sich aus dem Anhang der bereits angezogenen DIN-Norm bekannt. Mit dem erfindungsgemäßen Verfahren wird jedoch im Gegensatz zum Stand der Technik erreicht, daß zur Fehlerkorrektur auch die Prüfbits im Codewort mit herangezogen werden, was zu der eingangs erwähnten höheren Sicherheit führt, weil bei korrigierbaren Fehlern in den Prüfbits die Datenbits nicht verworfen zu werden brauchen.

Nach der Datenausgabe wird bis zum Beginn des nächsten Blocktakts die Takteinheit in der Steuereinheit 20 12 stillgesetzt.

Das erfindungsgemäße Verfahren ist nicht auf dem Ausführungsbeispiel angegebene Generatorfrequenzen beschränkt, diese können durchaus auch wesentlich höher gewählt werden, wenn das Programm des Datenprozessors in dem Decoder dies erfordert.

## Patentansprüche

- Verfahren zur Decodierung von mit einem RDS-Empfänger empfangenen Datenblöcken, bei dem die dem Prüfwort im einzelnen Datenblock zugeordneten Bits in einer ersten X-OR-Stufe mit den Bits des zu dem Datenblock gehörenden Offsetwort verknüpft werden und danach der fehlerfreie Empfang des Datenblocks in einem Syndromregister geprüft und dabei gegebenenfalls eine Fehlerkorrektur vorbereitet wird, für welche die dem Informationswort zugeordneten Bits zur Ausgabe über eine zweite X-OR-Stufe zwischengespeichert werden, dadurch gekennzeichnet,

- daß alle empfangenen Bits des Datenblocks zunächst in einem der ersten X-OR-Stufe (5) vorgeschalteten Zwischenspeicher (3) eingelesen werden, nach Speicherung eines vollständigen Datenblocks aus dem Zwischenspeicher (3) während der letzten Bitperiode des Datenblocks zweimal ausgelesen werden und bei dem ersten Auslesen über die erste X-OR-Stufe (5) in das Syndromregister (8) eingelesen werden, daß beim zweiten Auslesen der Eingang des Syndromregisters (8) durch eine Sperrstufe (7) gesperrt ist und daß das in der ersten X-OR-Stufe (5) vom überlagerten Offsetwort befreite Codewort über die dem Ausgang der ersten X-OR-Stufe (5) direkt nachgeschaltete zweite X-OR-Stufe (9) ausgegeben wird.

- 2. Verfahren nach Anspruch 1, dadurch gekennzeichnet,

- daß die empfangenen Bits nacheinander in einem 26-Bit-Schieberegister (3) zwischengespeichert werden und beim ersten Auslesen des Schieberegisters (3) auch zum Eingang des Schieberegisters (3) zurückgeführt werden.

- 3. Schaltungsanordnung zur Durchführung des Verfahrens nach Anspruch 1 oder 2 mit einer dem RDS-Empfänger (1) nachgeschalteten ersten X-OR-Stufe (5), die im Eingang eines Syndromregisters (8) liegt, mit einer zweiten X-OR-Stufe (9), deren zweiter Eingang über eine Torschaltung (10) mit dem Ausgang des Syndromregisters verbunden ist, und mit einer Steuereinheit, gekennzeichnet

durch ein zwischen dem Ausgang des RDS-Empfängers (1) und der ersten X-OR-Stufe (5) eingefügten 26-Bit-Schieberegister (3), durch eine von der Steuereinheit (12) steuerbare Sperrstufe (7) zwischen dem Ausgang der ersten X-OR-Stufe (5) und dem Eingang des Syndromregisters (8) und durch eine Verbindungsleitung zwischen dem Ausgang der ersten X-OR-Stufe (5) und dem ersten Eingang der zweiten X-OR-Stufe (9).

40