# Europäisches Patentamt European Patent Office Office européen des brevets

(11) **EP 0 756 223 A1**

### **DEMANDE DE BREVET EUROPEEN**

(43) Date de publication:

29.01.1997 Bulletin 1997/05

(51) Int Cl.6: G05F 3/24

(21) Numéro de dépôt: 96401646.3

(22) Date de dépôt: 24.07.1996

(84) Etats contractants désignés: **DE FR GB IT**

(30) Priorité: 25.07.1995 FR 9509023

(71) Demandeur: SGS-THOMSON MICROELECTRONICS S.A. 94250 Gentilly (FR)

(72) Inventeurs:

• Do, Tien-Dung 94230 Cachan (FR)

Naura, David

94230 Cachan (FR)

(74) Mandataire: Schmit, Christian Norbert Marie

Cabinet BALLOT-SCHMIT,

16, avenue du Pont Royal

94230 Cachan (FR)

## (54) Générateur de référence de tension et/ou de courant en circuit intégré

(57) Un générateur de référence en circuit intégré en technologie MOS comprend un dispositif à miroir de

courant à trois branches, pour obtenir une tension stable  $V_B$  au point milieu B de la deuxième branche. Ce générateur peut être utilisé pour délivrer un courant stable.

EP 0 756 223 A1

#### Description

La présente invention concerne un générateur de référence en circuit intégré pour délivrer une tension et/ou un courant de référence stables avec le procédé de fabrication, stables en température et indépendants de la tension d'alimentation.

Les générateurs de courant ou de tension de référence sont utilisés dans les circuits intégrés, notamment pour la lecture ou l'écriture de cellules mémoires. Notamment, il est connu d'utiliser deux paires de transistors MOS dans un montage à deux miroirs de courant pour générer un courant indépendant de la tension d'alimentation du montage. Cependant, le courant de référence obtenu est très dépendant de la température.

L'invention a pour objet de proposer un générateur de référence particulièrement stable, malgré les variations en procédé, température ou tension d'alimentation.

Telle qu'elle est caractérisée, l'invention concerne un générateur de référence en circuit intégré en technologie MOS qui comprend un dispositif à miroir de courant.

Ce dispositif comporte:

15

20

10

une première branche source de courant avec un premier transistor monté en diode, en série avec un deuxième transistor natif et résistif;

une deuxième branche avec un troisième transistor, en série avec un quatrième transistor monté en diode.

Selon l'invention, ce dispositif comporte encore une troisième branche, connectée à un point milieu de la deuxième branche, avec un cinquième transistor, en série avec un sixième transistor, monté en diode et connecté au dit point milieu;

25

les premier, troisième et cinquième transistors ayant le même type de conductivité et leurs grilles reliées ensemble, les deuxième, quatrième et sixième transistors ayant le même type de conductivité et les deuxième et quatrième transistors ayant leurs grilles reliées ensemble,

le quatrième transistor ayant un seuil de conduction supérieur à celui du deuxième et du sixième transistors, pour fournir une tension stable au dit point milieu de la deuxième branche.

30

Dans une variante, le générateur de référence selon l'invention permet aussi de fournir un courant stable. Le générateur comprend alors une quatrième branche comprenant un septième transistor, du même type de conductivité que le deuxième transistor, peu résistif, en série avec une résistance,

35

ce septième transistor ayant une tension de seuil inférieure à celle du quatrième transistor et recevant la tension stable sur sa grille,

pour obtenir un courant stable dans cette quatrième branche.

D'autres caractéristiques et avantages de l'invention sont détaillés dans la description suivante, faite à titre indicatif et non limitatif de l'invention et en référence aux dessins annexés, dans lesquels :

40

45

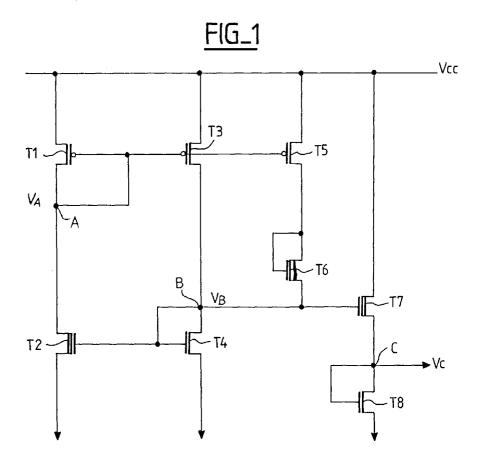

la figure 1, représente un schéma électronique d'un générateur de référence selon l'invention,

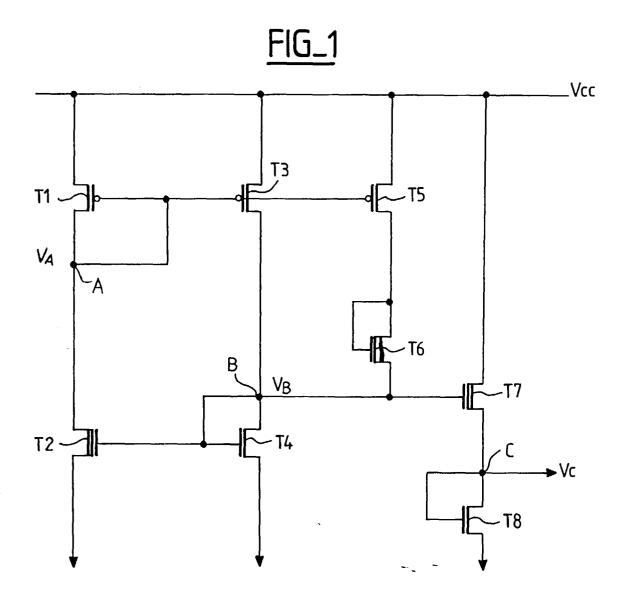

la figure 2 représente un schéma électronique d'un générateur de référence selon l'invention, pour délivrer un courant stable.

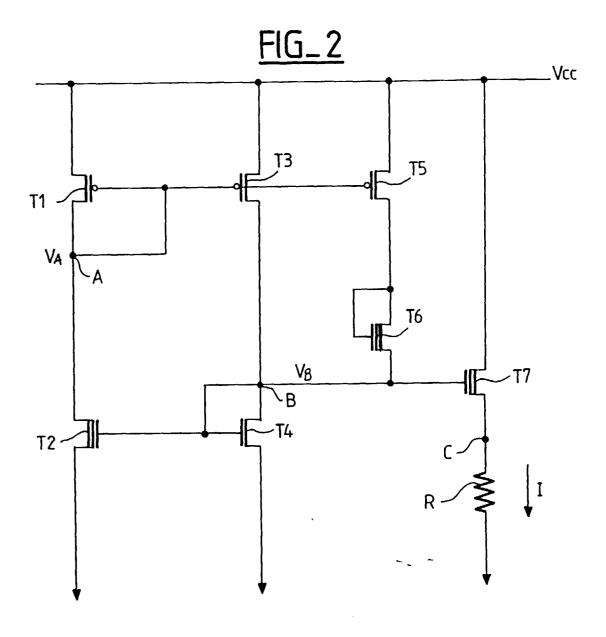

la figure 3 représente une variante du générateur représenté à la figure 2 et

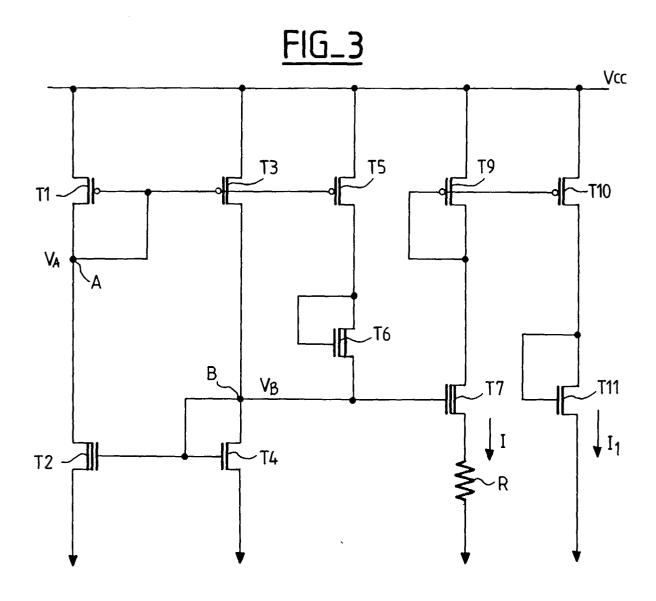

les figures 4 et 5 sont des schémas plus détaillés des figures 1 et 3, avec des circuits de polarisation.

La figure 1 représente un schéma d'un générateur de tension en circuit intégré selon l'invention. Dans cet exemple représenté, tous les transistors sont en technologie MOS.

Le générateur comprend un dispositif à miroir de courant à trois branches.

50

Une première branche est source de courant. Elle comprend un premier transistor T1, monté en diode en direct (c'està-dire avec sa grille reliée à son drain) et en série avec un deuxième transistor T2 résistif (W/L <<1).

Une deuxième branche comprend un troisième transistor T3 en série avec un quatrième transistor T4, monté en diode

Une troisième branche comprend un cinquième transistor T5 en série avec un sixième transistor T6, monté en diode en direct, et connecté à un point milieu B de la deuxième branche.

Le troisième transistor et le cinquième transistor sont respectivement montés en miroir de courant par rapport au

Le deuxième transistor est monté en miroir de courant par rapport au quatrième transistor.

#### EP 0 756 223 A1

Le transistor T4 à une tension de seuil  $Vt_n$  supérieure à celles des transistors T2 et T6. Dans l'exemple, le transistor T4 est enrichi et les transistors T2 et T6 sont natifs (c'est à dire avec une tension de seuil  $Vt_{na}$  positive et proche de zéro volt).

On rappelle qu'un montage en miroir de courant consiste à commander la grille d'un transistor par un transistor du même type de conductivité et monté en diode en direct (grille reliée au drain). De cette manière on contrôle le flux de courant dans le premier transistor. Le rapport des courants dans les deux transistors dépend essentiellement du rapport de leurs géométries W/L. Les premier, troisième et cinquième transistors sont ainsi du même type de conductivité et les deuxième, quatrième et sixième transistors sont du même type de conductivité.

Dans les figures, le générateur de référence selon l'invention est représenté en technologie CMOS. Ainsi les premier, troisième et cinquième transistors sont du type de conductivité P. Leurs sources sont reliées à une tension d'alimentation logique Vcc. Les deuxième, quatrième et sixième transistors sont du type de conductivité N. Les sources des deuxième et quatrième transistors sont reliées à la masse électrique. La source du sixième transistor est reliée au noeud B de la deuxième branche, c'est à dire aux drains des troisième et quatrième transistors.

Le fonctionnement du générateur de référence en régime établi est décrit ci-après.

On suppose que l'on a :  $Vt_p = Vt_1 = Vt_3 = Vt_5$  et  $Vt_{na} = Vt_2 = Vt_6$

et on note : Vt<sub>n</sub> = Vt<sub>4</sub>

20

25

30

35

40

45

50

15

5

10

Où  $Vt_p$  est la tension de seuil d'un transistor de type P, de l'ordre de 1 volt, où  $Vt_{na}$  est la tension de seuil d'un transistor de type N natif, de l'ordre de 0.2 volt et où  $Vt_n$  est la tension de seuil d'un transistor de type N enrichi, de l'ordre de 0.8 volt. Les valeurs sont données à titre d'exemple non limitatif pour une technologie 1,2 et 1,0 microns et à température ambiante (25°C).

Le transistor T2 est résistif (W/L<<1), en sorte que le transistor T1 se retrouve avec une tension de drain proche de Vcc -  $Vt_p$ . C'est la tension  $V_A$  au noeud A. Le transistor T3 est résistif, en sorte que l'on retrouve sur son drain une tension  $V_B$ , proche de la tension de seuil du transistor T4.

Comme par ailleurs la tension  $V_A = Vcc - Vt_p$  est appliquée sur la grille du transistor T3, ce dernier se retrouve polarisé en limite de conduction (tension grille-source de l'ordre de sa tension de seuil). Ceci accentue son caractère résistif pour maintenir  $V_B$  égale à  $Vt_n = Vt_4$ .

Comme le transistor T2 est monté en miroir de courant par rapport au transistor T4, on retrouve la tension  $V_B$  sur la grille du transistor T2. Or on a vu que la tension de seuil du transistor T2 est inférieure à la tension de seuil du transistor T4. Dans l'exemple on a  $Vt_n = 0.8V$  et  $Vt_{na} = 0.2V$ .

Le transistor T2 est donc fortement conducteur. Comme il a été choisi suffisamment résistif pour avoir  $V_A = Vcc - Vt_p$  sur son drain, le transistor T2 a aussi une tension drain-source  $V_{DS} = Vcc - Vt_p$  très supérieure à sa tension grille-source  $V_{GS} = Vt_4$ . Le transistor T2 est donc saturé, ce qui assure un courant relativement constant dans la branche T1, T2 et donc aussi dans la branche T3, T4, même si la tension d'alimentation varie.

Le transistor T5 est polarisé comme le transistor T3, c'est à dire en limite de conduction.

Le transistor T6 est monté en diode en direct. Comme sa tension de seuil est faible, proche de zéro, la branche (T5, T6) qui est en parallèle sur le transistor T3, a tendance à faire diminuer la résistance équivalente (T3//T5+T6) qui charge le transistor T4 et donc à faire légèrement remonter le niveau de la tension V<sub>B</sub>.

Que se passe t-il, quand il y a des variations de température, de procédé ou de tension d'alimentation?

Si la température augmente, on sait que les tensions de seuil diminue, environ de 2 millivolts par degré Celsius. La tension  $V_A$  augmente donc, ce qui rendrait le transistor T3 plus résistif, de même pour le transistor T5, mais leurs tensions de seuil diminuent aussi. Comme la tension de seuil du transistor T4 diminue, le niveau de la tension  $V_B$  a donc tendance à diminuer. Mais la tension de seuil du transistor T6 diminue aussi, (le transistor est presque équivalent à un court-circuit) : la résistance équivalente à T3//T5+T6 diminue donc, ce qui tend à tirer le niveau de  $V_B$  vers le haut et à le stabiliser.

En pratique, on a pu vérifier que la variation avec la température du niveau de V<sub>B</sub> suivait au pire celle d'une tension de seuil de transistor. On a pu ainsi obtenir une variation de 13% entre 25°C et 90°C, ce qui est très satisfaisant.

Au procédé de fabrication des transistors correspond un intervalle de valeurs des tensions de seuil, sachant que deux transistors proches auront en pratique la même tension de seuil.

Dans un exemple, on obtient pour Vt<sub>p</sub> l'intervalle [0.9V - 1.3V] et pour Vt<sub>n</sub> l'intervalle [0.7V - 1.0V].

Si on obtient pour tous les transistors des tensions de seuil correspondant aux valeurs maximum du procédé, la tension  $V_A$  a tendance à diminuer, ce qui fait augmenter le courant dans le transistor T3. Mais dans le même temps la tension de seuil du transistor T3 est aussi plus élevée, ce qui fait diminuer le courant dans le transistor T3. Dans le même temps, la tension de seuil du transistor T4 augmente, et le niveau de la tension  $V_B$  a tendance à augmenter. Comme

la tension de seuil du transistor T6 augmente aussi, la résistance équivalente de T3//T5+T6 augmente, ce qui tend à stabiliser le niveau de la tension  $V_B$ . En pratique, on a pu vérifier que la tension  $V_B$  suivait au pire la variation d'une tension de seuil d'un transistor de type N (T4).

Le raisonnement inverse s'applique dans le cas où les tensions de seuil sont minimum.

5

10

15

20

25

30

35

40

45

55

On peut aussi avoir des variations croisées, par exemple des  $Vt_n$  maximum et des  $Vt_p$  minimum. Dans ce cas, il y a auto-compensation dans le transistor T3, comme vu précédemment. Le niveau de  $V_B$  a donc tendance à augmenter, comme la tension de seuil du transistor T4. Mais comme le transistor T6 a aussi sa tension de seuil plus grande, la résistance équivalente de T3//T5+T6 diminue, ce qui empêche le niveau de la tension  $V_B$  d'augmenter.

Le raisonnement inverse s'applique pour des  $Vt_n$  minimum et des  $Vt_p$  maximum.

Cette stabilité de la tension V<sub>B</sub> avec le procédé permet d'avoir un générateur de référence parfaitement reproductible d'un circuit intégré à l'autre. Il n'y a pas de réglage à faire. Il y a moins de rejet dans la fabrication.

Si c'est la tension d'alimentation qui varie, c'est la résistance d'entrée Ron des transistors qui varie. Notamment, si Vcc augmente, la résistance d'entrée de tension du transistor T1 augmente et V<sub>A</sub> diminue. V<sub>A</sub> étant appliquée sur la grille du transistor T3, la tension V<sub>B</sub> aurait tendance à augmenter, mais comme dans le même temps, la résistance d'entrée du transistor T3 augmente, les effets se compensent.

La structure a trois branches selon l'invention permet en pratique d'obtenir un niveau de tension  $V_B$  qui varie au pire comme la tension de seuil d'un transistor.

Dans un perfectionnement représenté sur la figure 1, on prévoit une quatrième branche connectée au noeud B pour compenser la variation de là tension  $V_B$  avec la tension de seuil  $V_{t_n}$ .

La théorie et l'expérience montrent en effet que les tensions de seuil différentes de deux transistors de même type de conductivité ayant subit une implantation ionique différente varient avec la température et le procédé, mais que leur différence ne varie pas, ni en température, ni en procédé.

Dans l'invention, on propose d'exploiter cette propriété pour obtenir une tension de référence V<sub>C</sub> invariante avec la température et le procédé.

La quatrième branche comprend ainsi un transistor T7 de type N en série avec un transistor T8 de type N et enrichi (normalement dopé). Et le transistor T7 a une tension de seuil inférieure à celle du transistor T8. Dans l'exemple le transistor T7 est natif.

Le transistor T7 reçoit la tension  $V_B$  sur sa grille. Le transistor T8 est monté en diode en direct (grille reliée à son drain). On obtient une tension de référence  $V_C$  au point C entre les deux transistors T7 et T8, égale à :

$$V_C = V_B - Vt_{na} = Vt_n - Vt_{na}$$

Cette tension est de plus faible niveau que V<sub>B</sub>, mais elle est complètement auto-compensée en température. En pratique on montre qu'elle est aussi auto-compensée en procédé.

Si de plus on choisit un transistor T8 suffisamment résistif, et un transistor T7 avec une faible résistance d'entrée Ron (forte conductance), on obtient également une bonne compensation pour les variations de tension d'alimentation. Les tensions de référence obtenues  $V_B$  ou  $V_C$  sont assez faibles (par exemple, de l'ordre de 1 volt pour  $V_B$  et 0,8 volt pour  $V_C$ ), mais elles sont suffisantes pour la polarisation des grilles de cellules mémoires.

On peut obtenir des niveaux un peu plus élevés (1,2 à 1,6 volt) en augmentant le rapport W/L de l'un ou l'autre transistor T3, T5.

On perd alors un peu de stabilité en tension d'alimentation, mais sans perdre de stabilité en procédé ni en température, ce qui est intéressant.

Dans une variante, le générateur de référence selon l'invention permet aussi de délivrer un courant de référence. C'est ce qui est représenté sur la figure 2. On utilise les mêmes éléments de la figure 1, sauf à remplacer le transistor T8 par une vraie résistance dans un matériau résistif choisi pour être très stable en température dans la technologie utilisée, par exemple de la diffusion N.

On obtient un courant invariant avec la tension d'alimentation Vcc, avec la température et le procédé de fabrication. Le courant I obtenu est proportionnel au rapport de la tension au noeud C,  $V_C = Vt_n - Vt_{na}$  sur la résistance R.

La seule variation du courant est donc celle due à la résistance R.

Avantageusement, pour obtenir plusieurs courants de référence aptes à alimenter plusieurs dispositifs, il suffit d'utiliser des montages successifs à miroir de courant par rapport à cette quatrième branche.

C'est ce qui a été représenté sur la figure 3.

Pour cela, on place un transistor T9 en série entre la tension d'alimentation Vcc et le transistor T7. Ce transistor est monté en diode en direct et il est de type P dans l'exemple.

Une cinquième branche comporte un transistor T10 en série avec un transistor T11. Le transistor T10 est du même type de conductivité que le transistor T9 et il a sa grille connectée à celle du transistor T9. Le transistor T11 est de même type de conductivité que le transistor T7, mais avec une tension de seuil supérieure (Vt<sub>n</sub>) et il est monté en

diode en direct. On peut mettre à la suite plusieurs autres branches de même type que cette cinquième branche, pour obtenir autant de courants de référence.

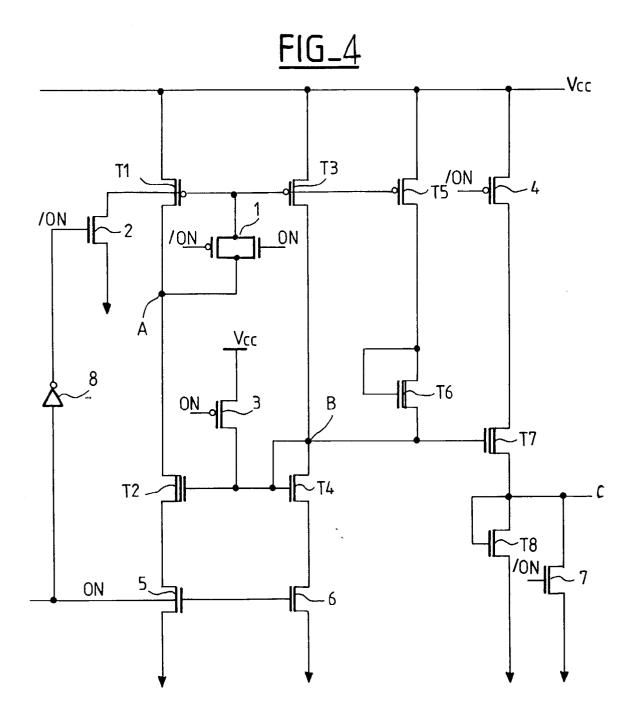

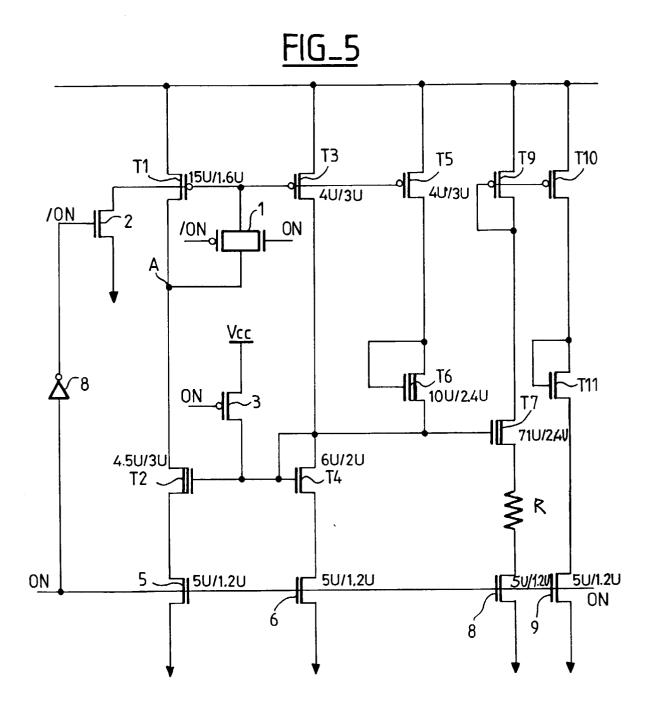

Les figures 4 et 5 représentent des schémas plus détaillés que ceux des figures 1 et 3. Elles montrent en effet un exemple d'un circuit de polarisation du générateur de référence selon l'invention.

Ainsi, sur la figure 4, une paire 1 de transistors de types de conductivité opposés est placée en parallèle entre la grille et le drain (A) du transistor T1. Quand le générateur est activé (ON=1), cette paire 1 tire la tension VA vers un potentiel positif. Ce phénomène est accentué par un transistor 2, ici de type N, qui isole dans le même temps la tension de grille du transistor T1, de la masse.

Un autre transistor 3, ici de type P, lui isole la tension de grille des transistors T2 et T4, de la tension d'alimentation Vcc, pour l'empêcher de s'élever trop.

Un transistor 4, ici de type P, transmet la tension d'alimentation sur le drain du transistor T7. Ce transistor 4 permet d'empêcher la consommation de courant quand le générateur n'est pas actif (ON=0). Des transistors 5 et 6, ici de type N, chacun respectivement en série avec les transistors T2 et T4, tirent les sources de ces deux transistors vers la masse

Enfin, un transistor 7 en parallèle sur le transistor T8 tire le noeud C vers la masse, quand le générateur n'est pas sous tension (ON=0).

Dans l'exemple, le signal d'activation ON du générateur, délivré par un circuit de commande non représenté du circuit intégré, commande la grille des transistors 5 et 6 et du transistor de type N de la paire 1. Un inverseur 8 permet d'obtenir la commande inverse /ON correspondante pour les transistors 2, 4, 7, et le transistor de type P de la paire 1.

Le circuit de polarisation permet de polariser les transistors T1 et T4 en limite de conduction, tout en empêchant la consommation du courant quand le générateur n'est pas activé.

La figure 5 représente un circuit de polarisation pour le générateur de référence utilisé pour délivrer un courant stable tel que représenté sur la figure 2. Ce circuit de polarisation comprend les éléments 1,2,5 et 6, du circuit de polarisation de la figure 4. Il comprend en outre deux transistors 8 et 9, ici de type N, en série sur chaque branche de génération du courant de référence pour les tirer vers la masse. Il ne comprend pas les éléments 4 et 7 du circuit de polarisation de la figure 4.

Les différentes figures représentent un générateur de référence réalisé en technologie CMOS. Mais l'invention ne se limite pas à cette technologie particulière. L'invention est réalisable plus généralement en technologie MOS, avec comme seules contraintes que les transistors montés en miroir de courant soient de même type de conductivité, et que la cinquième branche utilise deux transistors (T7, T8) de même type pour obtenir la compensation en température recherchée.

La seule contrainte technologique pour utiliser le générateur de référence selon l'invention concerne la tension d'alimentation Vcc.

En effet, pour les figures 1 et 2, il faut :

Vcc > V<sub>C</sub>

soit

10

15

20

25

30

35

40

45

50

55

Vcc > Vt<sub>n</sub> - Vt<sub>na</sub>

et pour la figure 3, il faut:

Vcc > Vc

soit

$Vcc > Vt_p + Vt_n - Vt_{na}$

#### Revendications

Générateur de référence en circuit intégré en technologie MOS comprenant un dispositif à miroir de courant comportant:

#### EP 0 756 223 A1

une première branche source de courant avec un premier transistor (T1) monté en diode en direct, en série avec un deuxième transistor (T2) natif et résistif;

une deuxième branche avec un troisième transistor (T3), en série avec un quatrième transistor (T4) monté en diode en direct:

5

caractérisé en ce que ledit dispositif comporte une troisième branche, connectée à un point milieu (B) de la deuxième branche, avec un cinquième transistor (T5), en série avec un sixième transistor (T6), monté en diode en direct et connecté au dit point milieu; les premier, troisième et cinquième transistors ayant le même type de conductivité et leurs grilles reliées ensemble,

10

- et les deuxième, quatrième et sixième transistors ayant le même type de conductivité et les deuxième et quatrième transistors ayant leurs grilles reliées ensemble,

- le quatrième transistor ayant un seuil de conduction (Vtn) supérieur à celui du deuxième et du sixième transistors (Vt<sub>na</sub>),

- pour fournir une tension stable (V<sub>B</sub>) au-dit point milieu de la deuxième branche.

20

15

- 2. Générateur de référence selon la revendication 1, caractérisé en ce qu'il comporte un étage de sortie comprenant en série un septième transistor (T7), et un huitième transistor (T8) de mêmes types de conductivité que le deuxième transistor, le septième transistor étant peu résistif, et recevant sur sa grille la tension stable (V<sub>R</sub>), le huitième transistor (T8) étant monté en diode en direct et très résistif, et ayant un seuil de conduction (Vtn) supérieur à celui du septième transistor (Vt<sub>na</sub>),

- pour fournir une tension de sortie (V<sub>C</sub>) sur un point de sortie (C) pris entre les septième et huitième transistors.

25

3. Générateur de référence selon la revendication 2, caractérisé en ce que le septième transistor a une faible résistance d'entrée.

4. Générateur de référence selon la revendication 1, caractérisé en ce qu'il comporte une quatrième branche comprenant un septième transistor (T7), du même type de conductivité que le deuxième transistor, peu résistif, en série avec une résistance (R),

30

- ce septième transistor ayant une tension de seuil (Vt<sub>na</sub>) inférieure à celle (Vt<sub>n</sub>) du quatrième transistor et recevant la tension stable (V<sub>B</sub>) sur sa grille,

- pour obtenir un courant stable (I) dans cette quatrième branche.

35

5. Générateur de courant selon la revendication 4, caractérisé en ce qu'il comporte au moins une cinquième branche montée en miroir de courant avec la quatrième branche, la quatrième branche comportant en outre un neuvième transistor (T9) monté en diode en direct et du même type de conductivité que le premier transistor (T1).

40

6. Générateur de référence, selon l'une quelconques des revendications précédentes, caractérisé en ce que les rapports de géométrie du troisième et du cinquième transistor sont utilisés pour modifier le niveau de la tension de sortie.

45

Générateur de référence, selon l'une quelconque des revendications précédentes, caractérisé en ce qu'il est réalisé en technologie CMOS, le premier transistor ayant une conductivité du type P et le deuxième transistor ayant une conductivité du type N.

50

55

# RAPPORT DE RECHERCHE EUROPEENNE Numero de la demande

EP 96 40 1646

| Catégorie                       | Citation du document avec in<br>des parties pert                                                                                                                                      |                                                                                    | Revendication concernée | CLASSEMENT DE LA<br>DEMANDE (Int.Cl.6)       |  |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-------------------------|----------------------------------------------|--|

| A                               | US-A-4 978 905 (HOFF DAVID ET AL) 18<br>Décembre 1990<br>* colonne 1, ligne 43 - colonne 2, ligne<br>12 *<br>* colonne 4, ligne 19 - ligne 28 *<br>* colonne 3, ligne 22 - ligne 28 * |                                                                                    | 1-7                     | G05F3/24                                     |  |

| Α                               | 19 Février 1991                                                                                                                                                                       | 47 - ligne 49 *<br>8 - ligne 10 *                                                  |                         |                                              |  |

| Α                               | EP-A-0 356 020 (IBM<br>* page 2, ligne 1 -                                                                                                                                            |                                                                                    | 1-7                     |                                              |  |

| A                               | EP-A-0 397 408 (ADV<br>INC) 14 Novembre 19<br>* colonne 1, ligne                                                                                                                      |                                                                                    | 1-7                     | DOMAINES TECHNIQUES<br>RECHERCHES (Int.Cl.6) |  |

| Α                               | 13 Novembre 1990                                                                                                                                                                      | ZPATRICK MARK E ET A<br>64 - colonne 4, ligne<br>3 - ligne 21 *                    |                         |                                              |  |

| Α                               | EP-A-0 310 743 (IBM) 12 Avril 1989<br>* page 4, ligne 16 - page 5, ligne 1 *                                                                                                          |                                                                                    | 1-7                     |                                              |  |

| A                               | US-A-5 124 632 (GRE<br>1992<br>* abrégé *                                                                                                                                             | AVES CARLOS A) 23 Jui                                                              | n 1-7                   |                                              |  |

| Le pi                           | résent rapport a été établi pour tou                                                                                                                                                  | ites les revendications                                                            |                         |                                              |  |

| Lieu de la recherche<br>LA HAYE |                                                                                                                                                                                       | Date d'achèvement de la recherche<br>28 Octobre 199                                | 6 Sch                   | Examinateur<br>obert, D                      |  |

| Y: par                          | CATEGORIE DES DOCUMENTS C<br>rticulièrement pertinent à lui seul<br>rticulièrement pertinent en combinaison<br>tre document de la même catégorie<br>ière-plan technologique           | E : document de<br>date de dépõ<br>n avec un D : cité dans la<br>L : cité pour d'a | utres raisons           |                                              |  |

## RAPPORT DE RECHERCHE EUROPEENNE

EP 96 40 1646

| tégorie |                                                                                                                                                                              |                                                                                        |                            |                                           |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|----------------------------|-------------------------------------------|

| negorie | des parties perti                                                                                                                                                            | dication, en cas de besoin,<br>nentes                                                  | Revendication<br>concernée | CLASSEMENT DE LA<br>DEMANDE (Int.Cl.6)    |

| А       | EP-A-0 564 225 (TEXA<br>Octobre 1993<br>* abrégé *                                                                                                                           | 1-7                                                                                    |                            |                                           |

|         |                                                                                                                                                                              |                                                                                        |                            |                                           |

|         |                                                                                                                                                                              |                                                                                        |                            |                                           |

|         |                                                                                                                                                                              |                                                                                        |                            |                                           |

|         |                                                                                                                                                                              |                                                                                        |                            |                                           |

|         |                                                                                                                                                                              |                                                                                        |                            |                                           |

|         |                                                                                                                                                                              |                                                                                        |                            |                                           |

|         |                                                                                                                                                                              |                                                                                        |                            |                                           |

|         |                                                                                                                                                                              |                                                                                        |                            | DOMAINES TECHNIQUES RECHERCHES (Int.Cl.6) |

|         |                                                                                                                                                                              |                                                                                        |                            |                                           |

|         |                                                                                                                                                                              |                                                                                        |                            |                                           |

|         |                                                                                                                                                                              |                                                                                        |                            |                                           |

|         |                                                                                                                                                                              |                                                                                        |                            |                                           |

|         |                                                                                                                                                                              |                                                                                        |                            |                                           |

|         |                                                                                                                                                                              |                                                                                        |                            |                                           |

|         |                                                                                                                                                                              |                                                                                        |                            |                                           |

|         |                                                                                                                                                                              |                                                                                        |                            |                                           |

|         | résent rapport a été établi pour tou                                                                                                                                         | tac lac revendinations                                                                 |                            |                                           |

| Le p    | Lieu de la recherche                                                                                                                                                         | Date d'achèvement de la recherche                                                      |                            | Examinateur                               |

|         | LA HAYE                                                                                                                                                                      | 28 Octobre 1996                                                                        | Sch                        | obert, D                                  |

| Y: pa   | CATEGORIE DES DOCUMENTS C<br>rticulièrement pertinent à lui seul<br>rticulièrement pertinent en combinaison<br>tre document de la même catégorie<br>rière-plan technologique | E : document de l<br>date de dépôt<br>avec un D : cité dans la d<br>L : cité pour d'au | tres raisons               |                                           |