**Europäisches Patentamt European Patent Office** Office européen des brevets

EP 0 768 760 A1

(12)

## **EUROPEAN PATENT APPLICATION**

(43) Date of publication:

16.04.1997 Bulletin 1997/16

(21) Application number: 95830420.6

(22) Date of filing: 09.10.1995

(51) Int. Cl.6: **H03K 5/24**, G05F 3/26, H03F 3/345

(11)

(84) Designated Contracting States: DE FR GB IT

(71) Applicant: SGS-THOMSON MICROELECTRONICS S.r.I. 20041 Agrate Brianza (Milano) (IT)

(72) Inventors:

· Tomasini, Alfredo I-15011 Acqui Terme (IT) · Colli, Gianluca I-27039 Sannazzaro dè Burgondi (IT)

· Chioffi, Ernestina I-27100 Pavia (IT)

(74) Representative: Pellegri, Alberto et al c/o Società Italiana Brevetti S.p.A. Via Puccini, 7 21100 Varese (IT)

#### (54)**Current comparator**

The absorption of current from the supply rails by a current comparator circuit producing a logic configuration of two complementary nodes of a first branch and of a second branch, respectively, in function of the comparison between a first current forced through the first branch and a second current forced through the second branch is limited by discriminating the lowest between the two compared currents and by mirroring the discriminated lowest current on the circuit branch through which the highest current is being forced. The comparator circuit comprises means that are responsive to the logic configuration of the two complementary nodes of the comparator circuit so as to assume a state capable of configuring the circuit to function as a current mirror that forces the lowest current on the other branch of the current comparator circuit.

### Description

5

10

15

25

30

35

The present invention relates to integrated circuits of signal processing and in particular to current comparators. Current comparator circuits are ubiquitous components of many analog systems including data converters and similar front-end signal processing applications. The smallest size of devices, high speed and low consumption constitute the basic requisites of any new project of this type.

The articles:

- "Novel approach to high speed CMOS current comparators", by H. Träff, Electronics Letters, January 30, 1992, Vol. 28, No. 3;

- "Fast CMOS multilevel current comparator", by H. Gustat, Electronics Letters, April 1, 1993, Vol. 29, No. 7; and

- "High performance CMOS current comparator", by A.T.K. Tang and C. Toumazou, Electronics Letters, January 6, 1994, Vol. 30, No. 1,

describe as many current comparators circuits employing a CMOS technology.

The comparison between two currents is made by forcing the currents to be compared through the two branches of a differential (unbalance) stage circuit so as to be able to discriminate the highest (or lowest) input current by monitoring the respective voltage levels of two nodes, respectively of one and the other branch of the unbalance circuit. Usually, while one of the nodes swings to voltage close to the supply voltage, the other node drops down to a potential close to the common ground potential of the circuit. A dedicated buffer stage or several stages in cascode provide a logic signal that is representative of the result of the comparison between the two input currents, forced through the respective branches of the comparator circuit.

Forcing the currents to be compared through the respective branches of the comparator circuit implies an absorption of these currents from a supply rail and therefore an attendant consumption which will be more or less high depending on the level of the input currents to be compared.

In many instances, the absorption and therefore the consumption depends substantially from the level of the highest current being compared which may indeed be a preestablished reference current with which to compare a certain current signal.

It has now been found and constitutes the object of the present invention, a method and a respective circuit arrangement capable of markedly limiting the absorption of current by a current comparator circuit. The invention consists in limiting the absorption of current through the branch of the comparator circuit along which is forced the highest current to the value of the lowest current which is in turn forced through the other branch of the comparator circuit. This condition is obtained without interfering in any way on other characteristics of switching speed and sensitivity of the comparator circuit.

This twofold function of the circuit: that is of comparing and at the same time limiting the current absorption, is implemented with an extremely simple circuit that requires an exceptionally reduced number of components, basically only three transistors, thus offering advantages also in terms of the overall economy of integration.

Fundamentally the invention consists in discriminating the level of two currents while limiting the current in the branch of the unbalanced circuit through which is being forced the highest of the two currents to the value of the other (lowest) current which flows in the other branch of the unbalanced circuit. In practice, the circuit of the invention is able to accomplish the required comparison through operating at a current level that is limited to the value of the lowest current, without requiring the use of any switch or other digitally controlled device.

The output or sensing node of the branch through which is forced the "lowest" current assumes a relatively "low" potential, whereas the other output or sensing node, that is the "output" node of the branch through which is forced the "highest" current assumes a relatively "high" potential. In other words, the logic configuration provided by the comparator circuit is coherent with the relative level of the compared currents.

An important aspect of the circuit of this invention is the fact that it is composed of a particularly reduced number of components, if compared to the number of components required for realizing known current comparator circuits with similar performances.

The circuit of the invention can be designed in CMOS technology by either employing exclusively p-channel devices or by employing cascoded n-channel or p-channel devices, or in a complementary form employing devices of both types of conductivity.

Essentially, the circuit of the invention uses a source-follower stage that can, for example, be constituted of by a single MOS transistor, whose state or electrical behavior is determined by the logic configuration assumed by the two complementary output nodes of the respective branches of the current comparator circuit. Such a stage or device is capable of assuming an operating state that effectively limits the current in the branch of the circuit through which the highest current is being forced to a value equivalent to the value of the lowest current that is being forced through the other

branch of the comparator circuit.

In the case of a stage realized with a single MOS transistor, it is advantageously exploited the capacity of such device of assuming different operating states (in a so-called linear zone or in a saturation zone) in function of the difference of potential of the two (complementary) output nodes of the comparator circuit. This mechanism eventually produces a configuration of a current mirror circuit that mirrors the lowest current on the branch through which the highest current is being forced, while ensuring a stable switching of the comparator circuit.

The various aspects, relative advantages and operating features of the circuit of this invention will be even more easily understood through the following description of some important embodiments and by referring to the enclosed figures, wherein:

10

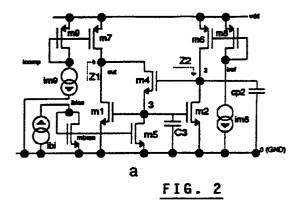

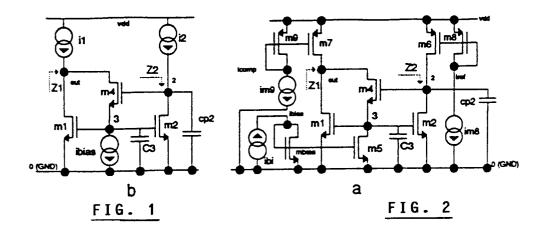

- Figure 1 is a basic scheme of a current comparator circuit realized according to the present invention;

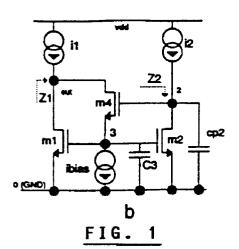

- Figure 2 shows an alternative embodiment of the comparator circuit of the present invention;

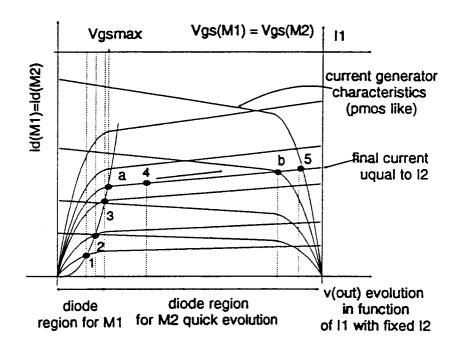

- 15 Figure 3 shows the functioning diagrams of the basic circuit of the invention;

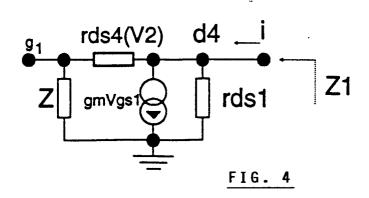

- Figure 4 shows an equivalent electric scheme for small signals of the pair of transistors M4 and M1 of the basic circuit of this invention;

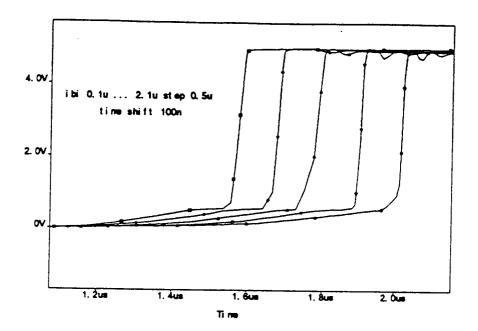

- 20 Figure 5 shows diagrams of the response characteristic for different current levels obtained by simulation;

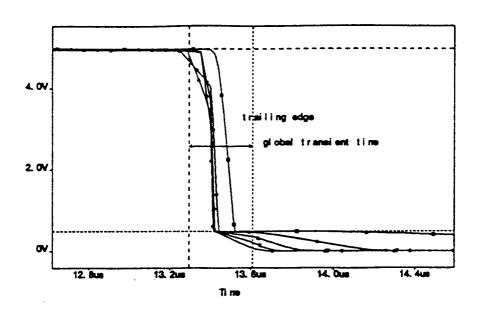

- Figure 6 shows the trailing fronts for different current levels obtained by simulation;

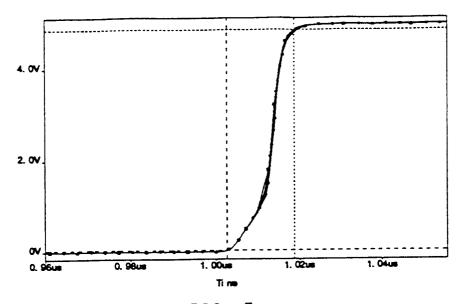

- Figure 7 shows the switchings rise-time;

25

30

35

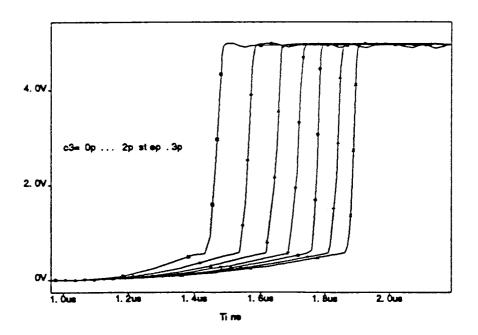

- Figure 8 shows the effect of the capacitance C3;

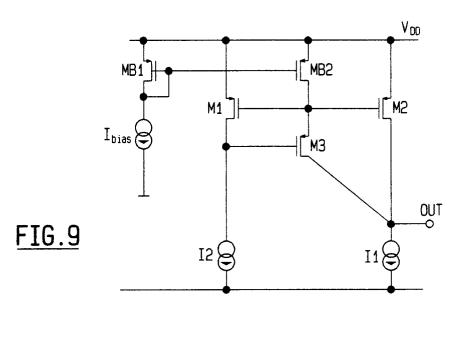

- Figure 9 depicts a circuit of the invention realized with p-channel devices;

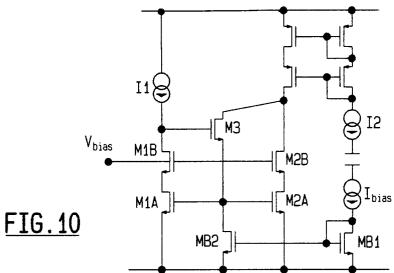

- Figure 10 is a circuit of the invention realized with cascoded p-channel devices;

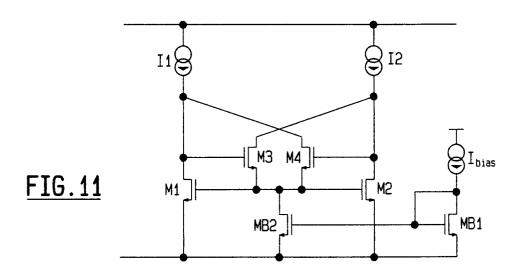

- Figure 11 shows an embodiment of the circuit of the invention according to a complementary architecture.

- Fig. 1 shows a basic circuit of a current comparator circuit realized according to the present invention using exclusively n-channel devices.

- The primary function of the circuit is that of discriminating which of the two currents I1 and I2 is the highest. The two currents I1 and I2 are, respectively, forced through the two branches of the circuit where one branch comprises the transistor M1 and the other branch comprises the transistor M2. The two complementary output nodes, designated "out" and 2, respectively, alternatively assume a "high" voltage level and a "low" voltage level in function of the result of a comparison between the two currents I1 and I2.

- A fundamental aspect of the circuit of this invention is the use of a stage that is substantially of the "source-follower" type, which in the example shown in Fig. 5, is constituted by the third transistor M4 and by the respective bias current generator lbias.

- In practice, depending on the result of the comparison between the two currents I1 and I2 and of the consequent eventual circuit switching, one or the other of the two transistors M1 and M2 is configured as a diode by the state assumed by the transistor M4. In this way a current mirror is realized in practice, which actually "copies" the lowest of the two currents on the branch through which the highest current is being forced.

- In the case of the circuit shown in Fig. 1, this behavior is obtained by exploiting the output characteristics of the MOS transistor M4, in a linear zone and in a saturation zone, respectively.

50

### DC ANALYSIS

It is well known that the output current of an MOS device follows the following physical laws:

$$I_{d} = k \frac{W}{L} (V_{gs} - V_{th})^2$$

(saturation) eq. (1)

$$I_{d}=k\frac{W}{L}(2(V_{gs}-V_{th})V_{ds}-V_{ds}^{2})$$

(linear) eq (2)

where

5

10

15

20

25

30

35

40

55

$k = \frac{\mu C_{ox}}{2}.$

By fixing the drain current value, it is possible to verify how the respective voltages Vgs and Vds behave. In a linear zone of the operating characteristics, these voltages have a mutual influence on each other whereas in a saturation zone of the operating characteristics, the current is controlled by the voltage Vgs and only secondarily by the voltage Vds. Equation 1 highlights that for a certain drain current, the voltage Vgs must become very high when the voltage Vds approaches zero, while according to equation 2, the voltage Vds may assume whichever value for a fixed value of the Vgs voltage.

By referring to the basic scheme of Fig. 1, the circuit is capable of exploiting these correlations for attaining in practice only two stable conditions, as shown by way of an example by the following relationships:

a)

$$11 > 12$$

$V(out) \approx 5V$   $V(2) \approx 0V$

b) 11 < 12  $V(out) \approx 0V$   $V(2) \approx 5V$

c) I1 = I2 unstable.

During a phase a) the transistor M2 is practically diode-configured, thus causing the mirroring of the current I2 on the transistor M1 (in fact, during this phase the transistor M4 behaves as source-follower). During a phase b) it is the transistor M1 that is diode-configured by the transistor M4 and therefore it causes the mirroring of the current I1 on the transistor M2.

In order to enable a complete scan of the working characteristics of the basic circuit of the invention, a test circuit whose electric scheme is depicted in Fig. 2 has been formulated.

A complete evolution of the output DC characteristic of MOS transistors is shown in Fig. 3. By starting a test run of the circuit of Fig. 2 from a condition whereby I1<I2, the transistor M2 is originally configured as a diode and the voltage (Vout) on the node "out" evolves through the points 1, 2 and 3 indicated on the characteristics up to a point where the increasing of the current I1 brings the system to the operating point indicated by the letter <u>a</u>.

By assuming that the two MOS transistors M1 and M2 are of the same size, the operating point <u>a</u> will be reached when the current I1 equals the current I2 (I1=I2). In this condition, the voltage Vgs of the transistors M1 and M2 cannot increase further.

As a consequence, the output voltage (Vout) must shift along the output characteristic of the transistor M1 in the order to verify the condition  $Vgs_{M1}=Vgs_{MAX}$ , without any increment of the drain current, thus passing through point 4 for reaching the new point of stability indicated by the letter  $\underline{b}$ .

If the current I1 continues to increase, the output voltage Vout on the node "out" will also increase evolving along the linear region of the output characteristics of the MOS transistor M7, accompanied by a further increase of the Vgs voltage.

The potential of the complementary node 2 of the circuit evolves in an exactly opposite way, only the end voltages reached by the nodes "out" and 2 are slightly different. More exactly, the final voltage on node 2 will be given by the Vgs voltage of the transistor M2 plus the  $Vgs_{M2}$  voltage.

### AC ANALYSIS

It is possible to evaluate the transfer function, that is the relationship between the input current I1 and the output voltage on the node 2, of the circuit of Fig. 2, through an analysis for small signals, bearing in mind that this simplification does not exactly reflect the real operating conditions of the circuit. The analysis anyway capable of identifying the necessary elements for trimming the circuit toward the required speed and resolution characteristics.

Firstly, it is important to establish the impedance Z1 of the output node "out". The equivalent circuit for small signals

of the transistor pair M4 and M1, is shown in Fig. 4, wherein Z represents the complex impedance between the common gate of transistors M1 and M2 and ground.

Once a given input current  $\underline{i}$  through the drain d of the transistor M4 is fixed, by calculating the derivative of the relation between said current i and the drain voltage  $V_{d4}$ , the impedance Z1 of the output node "out" may be calculated, according to the equations 3 and 4 below, where the resistance  $r_{ds4}$  represents the drain-source resistance of the transistor M4 and therefore the feedback resistance of the transistor M1 which is a function of the voltage V2 of node 2.

$$i = V_{gs1}g_{m1} + \frac{V_{dA}}{r_{ds1}} \quad \text{but:} \quad V_{gs1} = \frac{V_{dA}Z}{r_{ds4} + Z} \quad eq (3)$$

$$i = \frac{V_{dA}Z}{r_{ds4} + Z} g_{m1} + \frac{V_{dA}}{r_{ds1}} = V_{d4} \left( \frac{Z g_{m1}}{r_{ds4} + Z} + \frac{1}{r_{ds1}} \right) = V_{d4} \left( \frac{Z (1 + rds1 g_{m1}) + r_{ds4}}{r_{ds1} (r_{ds4} + Z)} \right)$$

$$Z1 = \frac{V_{dA}}{i} = \left( \frac{r_{ds1} (r_{ds4} + Z)}{Z (1 + r_{ds1} g_{m1}) + r_{ds4}} \right) eq (4)$$

A simpler model for the impedance Z may be obtained by closely observing the diagram of Fig. 2. The capacitance C3 can be considered representative of the impedance Z, consequently

$$Z = \frac{1}{sC3}.$$

By substituting this expression into equation 4, we obtain the following explicit solution for Z1:

$$Z1 = \left(\frac{r_{ds1}\left(r_{ds4} + \frac{1}{sC3}\right)}{\frac{1}{sC3}\left(1 + r_{ds1} g_{m1}\right) + r_{ds4}}\right) eq (5)$$

Obviously, a more significant mathematical relation is the link between the input current I1 and the voltage  $V_2$  of the circuit node 2. Indeed, this relation links the value of the resistance  $r_{ds4}$  with I1 through the voltage  $V_2$ . By referring to the circuit schemes of Fig. 2 and Fig. 4, the following relations may be derived.

$$V_{2} = V_{g1} g_{m2} Z_{2} \qquad \text{but:} \qquad V_{g1} = V_{1} \frac{Z}{r_{ds4} + Z} = I_{1} Z_{1} \frac{Z}{r_{ds4} + Z} = I_{1} Z_{1} \frac{\frac{1}{sC3}}{r_{ds4} + \frac{1}{sC3}}$$

$$V_{2} = I_{1} \left( \frac{r_{ds1} \left( r_{ds4} + \frac{1}{sC3} \right)}{r_{ds4} + \frac{1}{sC3}} \right) \frac{1}{sC3} q_{m2} Z_{2}$$

$$V2 = I1 \left( \frac{r_{ds1} \left( r_{ds4} + \frac{1}{sC3} \right)}{\frac{1}{sC3} \left( 1 + r_{ds1} g_{m1} \right) + r_{ds4}} \right) \frac{\frac{1}{sC3}}{r_{ds4} + \frac{1}{sC3}} g_{m2} Z_2$$

$$= 11 \left( \frac{r_{ds1}}{(1 + r_{ds1} g_{m1}) + sC3r_{ds4}} \right) g_{m2} Z_{2}$$

$$= 11 \left( \frac{r_{ds1}}{1 + \frac{sC3r_{ds4}}{T + r_{ds1} g_{m1}}} \right) \frac{g_{m2} Z_{2}}{T + r_{ds1} g_{m1}} \quad eq (6)$$

Observing the diagram of Fig. 2, a more significant expression for Z2 can be written as in the following equation 7:

25

45

50

55

35 Substituting equation 7 into equation 6, we obtain the following expression for V2/I1:

$$\frac{V2}{11} = \left(\frac{r_{ds1}}{1 + \frac{sC3r_{ds4}}{1 + r_{ds1} g_{m1}}}\right) \frac{g_{m2}}{1 + r_{ds1} g_{m1}} \frac{\frac{r_{ds2} r_{ds6}}{r_{sd2} + r_{ds6}}}{1 + sC_{p2} \frac{r_{ds2} r_{ds6}}{r_{sd2} + r_{ds6}}} eq (8)$$

where C<sub>p</sub> represents the parasitic capacitance of the node 2 of the circuits depicted in Figures 1 and 2. Equation 8 shows the existence of two poles, the dominant pole has a time constant given by:

$$\tau 1 = C_{p2} \frac{r_{ds2} r_{ds6}}{r_{sd2} + r_{ds6}}.$$

A second pole is determined by the parasitic capacitance C3, with a time constant given by:

$$\tau 2 = \frac{\text{C3r}_{\text{ds4}}}{1 + \text{r}_{\text{ds1}} \text{g}_{\text{m1}}}$$

It is important to consider that both these time constants are strongly dependent on the bias conditions of the circuit, because the drain-source impedance of MOS transistors varies drastically during the circuit switching transients. For instance, when I1<I2, the transistor M4 exhibits a very low  $r_{ds4}$  by virtue of its high Vgs. Conversely, the resist-

ance  $\rm r_{ds6}$  is low because the transistor M6 is functioning in a linear region.

During a transition I1=I2, the drain-source resistance of all the MOS transistors involved is high and the speed of the circuit is controlled by the time constant  $\tau 2$  because it becomes more and more independent of the Vgs of the transistor M4. The time constant  $\tau 2$  assumes a constant value when the voltage V1 reaches the saturation value  $V_{dsat}$ , as shown in Fig. 3 by the intersection point a.

Another significant verification is the evolution of the output node "out".

The equation that ties I1 with V1 is equation 5, this equation is rewritten below as equation 9.

$$V1 = I1 \left( \frac{r_{ds1} \left( r_{ds4} + \frac{1}{sC3} \right)}{\frac{1}{sC3} (1 + r_{ds1} g_{m1}) + r_{ds4}} \right) = I1 \frac{r_{ds1}}{(1 + r_{ds1} g_{m1})} \left( \frac{(1 + sC3r_{ds4})}{\left( 1 + \frac{sC3r_{ds4}}{1 + r_{ds1} g_{m1}} \right)} \right) = I1 \frac{1}{g_{m1}} \left( \frac{(1 + sC3r_{ds4})}{\left( 1 + \frac{sC3r_{ds4}}{1 + r_{ds1} g_{m1}} \right)} \right) = eq (9)$$

This expression contains a pole and a zero. The zero's frequency is rather low whereas the frequency of the pole is by two to three decades higher. The drain-source resistance of the transistor M4 maintains an important role. It controls the transfer function and is dependent on the voltage Vgs<sub>M4</sub>. In other words, it is strongly nonlinear.

### **SIMULATIONS**

The following simulations refer to the test circuit scheme of Fig. 2. The following table shows the parameters used for this evaluation:

30

5

10

15

20

25

35

40

45

50

Netlist: (summary)

5

10

15

20

25

30

35

40

50

ibi 0 ib .5u im8 ir 0 1u im9 ic 0 pulse(0u 40u 1u 10u 0.4u 2u 60u) vdd 30 0 5

xclc1 30 ir ic out ib clc params: cpl=0.01p

.param c3=0.4p .step im8 1u 2.6u .5u

icomp out ibias params: col = 2p subckt dc vdd iref gate \*dev. source bulk model and size drain nmodlow w=16u l=5u 0 0 m1 out 3 3 0 0 nmodlow w=40u l=3u m2 2 0 nmodlow w=3u l=3u 3 out 2 m4 0 0 nmodlow w=6u l=3u **m**5 3 ibias pmod w=10u l=3u 2 vdd vdd m6 iref vdd pmod w=10u l=3u m8 iref iref vdd vdd pmod w=6u l=4u vdd m7 icomp out vdd pmod w=6u l=4u m9 icomp icomp vdd nmodlow w=6u l=3u ibias 0 mbias ibias passive devices {c3} c3 3 0 2 0 cp2 {cpi}

<u>.ends</u>

Effects of the bias current "ibi" on the circuit precision and speed.

Scope of a first simulation is that of testing equation 9 and particularly the effect of the parameter  $r_{ds4}$  on the speed and precision characteristics.

Fig. 5 shows the transient diagrams for different values of the bias current "ibi". The rise-time remains within the interval of 30 to 40 nanoseconds (n). Of course, the maximum speed of 30n is obtained with the highest value of "ibi".

The circuit has an intrinsic slew-rate determined by the capacitance of the output node "out" which does not appear in equation 9 and depends from the input ramp.

The separation between the different curves is of about 100ns, in agreement with the theoretical value of 125µs. This value is obtained by employing a ramp generator having a gradient of 4A/s and the current value of "ibi".

Fig. 6 depicts the diagrams of the trailing front transient analysis. The delays in this case are more pronounced because the current is lower than during the leading front transient. It is however important to note that no problem of switching-back is manifested. Such a problem is practically inexistent because even if the current I1 became zero, the output voltage can assume only the same null value.

### Maximum speed

Of course, there exists a limit for the response speed of the circuit, at which the circuit becomes incapable of discriminating the currents. With the aim of determining such a limit, a simulation was carried out according to the following parameters and conditions:

ibi 0 ib .5u im8 ir 0 1u im9 ic 0 pulse(0u 40u 1u 5n 1u 2u 60u) vcid 30 0 5 xcic1 30 ir ic out ib cic params: cpi=0.01p .param c3=0.4p .step param c3 0.1p 2.2p .5p

| <u>subckt</u> | dc      | vdd               | iref  | icomp        | out | bias       | peramet col = 2p |                    |

|---------------|---------|-------------------|-------|--------------|-----|------------|------------------|--------------------|

|               | *dev.   |                   | drain | gate         |     | source     | bulk             | model and size     |

|               | m1      |                   | out   | 3            |     | 0          | 0                | nmodlow w=16u ≒5u  |

|               | m2      |                   | 2     | 3            |     | 0          | 0                | nmodlow w=40u i=3u |

|               | m4      |                   | out   | 2            |     | 3          | 0                | nmodow w=3u i=3u   |

|               | rm5     |                   | 3     | <b>Ibias</b> |     | 0          | 0                | nmodlow w=6u l=3u  |

|               | m6      |                   | 2     | iref         |     | cell       | cell             | pmod w=10u l=3u    |

|               | m8      |                   | iref  | iref         |     | cell       | cell             | pmod w=10u i=3u    |

|               | m7      |                   | out   | icomp        |     | vdd        | vdd              | pmod w=6u i=4u     |

|               | m9      |                   | icomp | icomp        |     | vdd        | vdd              | pmod w=6u l=4u     |

|               | mbias   |                   | bias  | ibias        |     | 0          | 0                | nmodlow w=6u i=3u  |

|               | passive | device and supply |       |              |     |            |                  |                    |

|               | c3      |                   | 3     | 0            |     | {c3}       |                  |                    |

|               | cp2     |                   | 2     | 0            |     | (cpi)      |                  |                    |

|               | vcell   |                   | ceil  | 0            |     | 2 <b>v</b> |                  |                    |

| .ends         |         |                   |       |              |     |            |                  |                    |

25

30

40

5

10

15

20

The impulse rise-time was reduced to 5ns with drain voltages of the transistor M6 and M8 reduced to 2V in order to simulate the worst case.

The result of this simulation is shown in the diagram of Fig. 7 wherefrom it can be observed that the maximum transient speed for a current variation  $\Delta I_{M9}$ =40 $\mu$ A is 16ns.

### Effects of the parasitic capacitance C3

As demonstrated by the AC analysis, the parasitic capacitance C2 has an important role in determining the response characteristics of the circuit. This capacitance does not have a major effect during switching, because the value of the drain source  $r_{ds4}$  resistance is so high that the output node "out" is completely isolated from the capacitance C3. The evolution of the voltage Vout of the "out" node is controlled by the slew-rate characteristics and not by the time constant. For this reason, the effect on the capacitance C3 should manifest itself during the first part of the transient, before the turning point of the switching.

This is confirmed by the simulation results shown in Fig. 8. The effect of the capacitance C3 can be considered as a delay factor in switching, because the voltage on the node 3 cannot any longer follow the ramp speed for ever increasing values of the capacitance C3. A further simple and intuitive interpretation can be made by considering the overall current balance on the output node "out".

The simulations demonstrate that the characteristics of the leading transient tend to get closer to each other for relatively high values of C3; the limit being given by missing the transition for C3 tending to infinity.

### Capacitance CP2

The capacitive load on the node 2 slows-down the functioning of the circuit.

A lower "ibi", current has the effect of impelling the transistors M4, M1 and M2 toward an OFF-state. Indeed, the coupling capacitance between the drain and the gate of M1 injects current into the node 3 and switches off the transistor M4, thus precluding the mirroring of the current of M2 on M1. The following equations define the OFF-state condition for the transistor M4:

55

$$Cds2\frac{dV_2}{dt} + Cds1\frac{dV_{out}}{dt} > ibi$$

$M4 = off$

$$Cds2\frac{dV_2}{dt} + Cds1\frac{dV_{out}}{dt} < ibi$$

$M4 = on$

Due to the fact that the switching of the complementary nodes "out" and 2, in the absence of a capacitance CP2, have similar time constants, the two drain-gate capacitances of the transistors M2 and M1 share the charge injected into node 3 thus preventing the switching off of the transistor M4.

In conclusion, the load capacitance of the node 2 (CP2) slows down the evolution of the voltage on the node 2, according to equation 8, and, in the limit, the above mentioned compensation becomes insufficient leading to the consequent switching off of the transistor M4. In this case, the circuit requires a period of time relatively long for regaining its functionality.

Of course, the higher is the bias current ibi, the lower is the likelihood that such an effect has to take place, ensuring a conduction state of all the circuit transistors. An alternative way of compensating such a current injection could be that of adding a capacitance of an appropriate value between the nodes 2 and 3 of the circuit.

Of course, the circuit of the invention can be realized in different ways. Fig. 9 shows an embodiment of the circuit with p-channel MOS transistors rather than with n-channel transistors as in the example analyzed.

Fig. 10 shows an alternative embodiment of the circuit of the invention with cascoded p-channel transistors. Of course, a similar complementary scheme would employ cascoded n-channel transistors.

Finally Fig. 11 shows a configuration of the circuit of the invention according to a complementary architecture, using both p-channel and n-channel transistors.

### **Claims**

10

15

20

25

30

35

50

55

Current comparator circuit capable of producing a logic configuration of two complementary nodes, respectively of a first and of a second branch of the circuit, in function of the comparison between a first current forced through said first branch and a second current forced through said second branch of the circuit, characterized in that it comprises

means responsive to the logic configuration of said complementary nodes and assuming a state capable of limiting the current in the branch through which is forced the highest current to the value of the current forced through the other branch of the circuit.

- 2. The current comparator circuit as defined in claim 1, characterized in that said means consist of at least a transistor having a control terminal coupled to one of said nodes and current terminals coupled to the other of said nodes and to a common control node, respectively, of a pair of transistors of said first and of said second branch, respectively, of the circuit and a bias current generator connected between a common supply node of the circuit and said common control node.

- 3. The current comparator circuit according to claim 2, characterized in that said means comprise a pair of transistors cross-coupled to the two circuit branches.

- 4. The current comparator circuit according to any of the claims 1 and 2, characterized in that it is realized with p-channel MOS transistors.

- 45 5. The current comparator circuit according to any of the claims 1 and 2, characterized in that it is realized with n-channel MOS transistors.

- 6. The current comparator circuit according to any of the claims 1 and 2, characterized in that it is realized with cascoded p-channel MOS transistors.

- 7. The current comparator circuit according to any of the claims 1 and 2, characterized in that it is realized with cascoded n-channel MOS transistors.

- 8. A method for limiting the absorption of current of a current comparator circuit capable of producing a logic configuration of two complementary nodes of a first branch and of a second branch, respectively, of the circuit in function of the comparison between a first current forced through said first branch and a second current forced through said second branch, characterized in that it comprises

discriminating the lowest between said two currents;

|    | mirroring said discriminated lowest current on the circuit branch into which the highest current is being forced. |

|----|-------------------------------------------------------------------------------------------------------------------|

|    |                                                                                                                   |

|    |                                                                                                                   |

| 5  |                                                                                                                   |

|    |                                                                                                                   |

|    |                                                                                                                   |

| 10 |                                                                                                                   |

|    |                                                                                                                   |

|    |                                                                                                                   |

| 15 |                                                                                                                   |

| 15 |                                                                                                                   |

|    |                                                                                                                   |

|    |                                                                                                                   |

| 20 |                                                                                                                   |

|    |                                                                                                                   |

|    |                                                                                                                   |

| 25 |                                                                                                                   |

|    |                                                                                                                   |

|    |                                                                                                                   |

| 30 |                                                                                                                   |

|    |                                                                                                                   |

|    |                                                                                                                   |

|    |                                                                                                                   |

| 35 |                                                                                                                   |

|    |                                                                                                                   |

|    |                                                                                                                   |

| 40 |                                                                                                                   |

|    |                                                                                                                   |

|    |                                                                                                                   |

| 45 |                                                                                                                   |

|    |                                                                                                                   |

|    |                                                                                                                   |

| 50 |                                                                                                                   |

|    |                                                                                                                   |

|    |                                                                                                                   |

|    |                                                                                                                   |

FIG. 3

FIG. 5

FIG. 6

FIG. 8

# **EUROPEAN SEARCH REPORT**

Application Number EP 95 83 0420

| Category                  | Citation of document with in of relevant pa                                                                                                                        | dication, where appropriate,<br>ssages                                                | Relevant<br>to claim                                                   | CLASSIFICATION OF THI<br>APPLICATION (Int.Cl.6) |  |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------|-------------------------------------------------|--|

| X<br>Y                    | GB-A-2 058 504 (RCA<br>* page 3, line 56 -                                                                                                                         | CORP) 8 April 1981<br>line 79 *                                                       | 1-5,8<br>6,7                                                           | H03K5/24<br>G05F3/26<br>H03F3/345               |  |

| X                         | DE-A-30 35 471 (PIO<br>April 1981<br>* page 25, line 16<br>figure 3 *                                                                                              | NEER ELECTRONIC CORP) - page 26, line 12;                                             | 9 1-5,8                                                                | 110313/343                                      |  |

| X                         | EP-A-0 349 954 (MOT<br>1990<br>* abstract; figure                                                                                                                  | OROLA INC) 10 January                                                                 | 1,2,8                                                                  |                                                 |  |

| Υ                         | US-A-5 142 696 (KOS<br>25 August 1992<br>* figure 6 *                                                                                                              | IEC JEANNIE H ET AL)                                                                  | 6,7                                                                    |                                                 |  |

| A                         | US-A-5 136 184 (DEE<br>1992                                                                                                                                        | VY KENNETH) 4 August                                                                  |                                                                        |                                                 |  |

|                           |                                                                                                                                                                    |                                                                                       |                                                                        | TECHNICAL FIELDS<br>SEARCHED (Int.Cl.6)         |  |

|                           |                                                                                                                                                                    |                                                                                       |                                                                        | H03K<br>G05F<br>H03F                            |  |

|                           |                                                                                                                                                                    |                                                                                       |                                                                        |                                                 |  |

|                           |                                                                                                                                                                    |                                                                                       |                                                                        |                                                 |  |

|                           |                                                                                                                                                                    |                                                                                       |                                                                        |                                                 |  |

|                           |                                                                                                                                                                    |                                                                                       |                                                                        |                                                 |  |

|                           |                                                                                                                                                                    |                                                                                       |                                                                        |                                                 |  |

|                           | The present search report has b                                                                                                                                    | een drawn up for all claims                                                           | .,                                                                     |                                                 |  |

| Place of search THE HAGUE |                                                                                                                                                                    | Date of completion of the search 15 March 1996                                        | Seg                                                                    | Segaert, P                                      |  |

| X : par<br>Y : par<br>doc | CATEGORY OF CITED DOCUMENT<br>ticularly relevant if taken alone<br>ticularly relevant if combined with and<br>cument of the same category<br>thological background | E : earlier patent<br>after the filing<br>ther D : document cite<br>L : document cite | document, but pub<br>date<br>d in the application<br>for other reasons | lished on, or<br>n                              |  |