# Europäisches Patentamt **European Patent Office**

Office européen des brevets

EP 0 806 719 A2 (11)

(12)

# EUROPÄISCHE PATENTANMELDUNG

(43) Veröffentlichungstag: 12.11.1997 Patentblatt 1997/46 (51) Int. Cl.<sup>6</sup>: **G05F 3/26**, G05F 3/30

(21) Anmeldenummer: 97106833.3

(22) Anmeldetag: 24.04.1997

(84) Benannte Vertragsstaaten: CH DE DK FR GB IT LI

(30) Priorität: 10.05.1996 DE 19618914

(71) Anmelder: SIEMENS AKTIENGESELLSCHAFT 80333 München (DE)

(72) Erfinder: Weber, Stephan, Dr. 81739 München (DE)

#### (54)Schaltungsanordnung zur Erzeugung eines Referenz-potentials

(57)Schaltungsanordnung zur Erzeugung eines Referenzpotentials mit einem ersten Transistor (T1), dessen Emitter mit einem Bezugspotential (M) verbunden ist und dessen Basis und Kollektor miteinander verschaltet sind,

mit einem zweiten Transistor (T2), dessen Basis mit der Basis des ersten Transistors (T1) verbunden ist,

mit einem ersten Widerstand (R1), der zwischen den Kollektor des ersten Transistors (T1) und einem Ausgangsanschluß (U) zum Abgreifen des Referenzpotentials geschaltet ist,

mit einem zweiten Widerstand (R2), der zwischen den Kollektor des zweiten Transistors (T2) und den Ausgangsanschluß (U) geschaltet ist,

mit einem dritten Widerstand (R3), der zwischen den Emitter des zweiten Transistors (T2) und das Bezugspotential (M) geschaltet ist,

mit einem dritten Transistor (T3), dessen Basis mit dem Kollektor des zweiten Transistors (T2) und dessen Emitter mit dem Bezugspotential (M) verbunden ist, und mit einer gesteuerten Stromquelle (T3, T4), die zwischen ein Versorgungspotential (V) und den Ausgangsanschluß (U) geschaltet ist und die eingangsseitig mit dem Kollektor des dritten Transistors (T3) gekoppelt ist und mit einer Kapazität (C1), die dem zweiten Widerstand (R2) parallel geschaltet ist.

20

25

35

## **Beschreibung**

Die Erfindung betrifft eine Schaltungsanordnung zur Erzeugung eines Referenzpotentials mit einem ersten Transistor, dessen Emitter mit einem Bezugspotential verbunden ist und dessen Basis und Kollektor miteinander verschaltet sind, mit einem zweiten Transistor, dessen Basis mit der Basis des ersten Transistors verbunden ist, mit einem ersten Widerstand, der zwischen den Kollektor des ersten Transistors und einem Ausgangsanschluß zum Abgreifen des Referenzpotentials geschaltet ist, mit einem zweiten Widerstand, der zwischen den Kollektor des zweiten Transistors und den Ausgangsanschluß geschaltet ist, mit einem dritten Widerstand, der zwischen den Emitter des zweiten Transistors und das Bezugspotentials geschaltet ist, mit einem dritten Transistor, dessen Basis mit dem Kollektor des zweiten Transistors und dessen Emitter mit dem Bezugspotential verbunden ist, und mit einer gesteuerten Stromquelle, die zwischen ein Versorgungspotential und den Ausgangsanschluß geschaltet ist und die eingangsseitig mit dem Kollektor des dritten Transistors gekoppelt ist.

Eine derartige, auch Bandgap-Referenz bezeichnete Schaltungsanordnung ist beispielsweise aus Paul R. Gray, Robert G. Meyer, Analysis and Design of Analog Integrated Circuits, Second Edition, John Wiley and Sons, 1984, S.293-296 und der EP 0 411 657 A1 bekannt und wird häufig bei integrierten Schaltkreisen als interne Referenzspannungsquelle verwendet. Eine frequenzkompensierte Bandgap-Referenz ist zudem in der GB 2 256 949 A beschrieben.

In Zukunft wird es bei integrierten Schaltkreisen zunehmend wichtiger, daß die Schaltkreise sich zum Zwecke der Stromersparnis über einen externen Anschluß ein- und ausschalten lassen. Das Ausschalten sollte dabei möglichst schnell erfolgen, um effektiv die Stromaufnahme und damit die Verlustleistung senken zu können. Ebenso sollte auch die Einschaltzeit möglichst klein gehalten werden, um den Schaltkreis binnen kürzester Zeit in den Arbeitszustand zu bringen. Ein weiteres wichtiges Kriterium von Schaltungsanordnungen zur Erzeugung eines Referenzpotentials ist das Rauschverhalten. Dies kann durch Kondensatoren zur Bandbegrenzung, die das Rauschen bei hohen Frequenzen wegfiltern, günstig beeinflußt werden. Jedoch steigen durch diese Maßnahmen die Ein- und Ausschaltzeiten des jeweiligen Schaltkreises an.

Aufgabe der Erfindung ist es, eine Schaltungsanordnung der eingangs genannten Art anzugeben, die trotz guten Rauschverhaltens kurze Ein- und Ausschaltzeiten aufweist.

Die Aufgabe wird durch eine Schaltungsanordnung gemäß Patentanspruch 1 gelöst. Ausgestaltungen und Weiterbildungen des Erfindungsgedankens sind Gegenstand von Unteransprüchen.

Vorteilhaft ist, daß die günstigen Ein- und Ausschaltzeiten sowie das güngstige Rauschverhalten mit geringstem technischen Aufwand erreicht wird. Zu die-

sem Zweck wird eine Kapazität dem zweiten Widerstand parallel geschaltet. Gegenüber einer Kapazität, die beispielsweise zwischen Basis und Emitter des dritten Transistors geschaltet ist, kann der als Emitterfolger betriebene vierte Transistor mehr Strom liefern und verkürzt dadurch die Einschaltzeit. Der zur Kapazität parallel liegende zweite Widerstand trägt hingegen zur Verkürzung der Ausschaltzeit bei. Stabilität und Rauschverhalten bleiben dabei praktisch unverändert. Schließlich wird die Betriebsspannungsunterdrückung bei hohen Frequenzen verbessert.

Bei einer bevorzugten Ausgestaltung der erfindungsgemäßen Schaltungsanordnung weist die gesteuerte Stromquelle einen vierten Transistor auf, dessen Kollektor mit dem Versorgungspotential, dessen Emitter mit dem Ausgangsanschluß und dessen Basis mit dem Kollektor des dritten Transistors verbunden ist. Zwischen Basis und Kollektor des vierten Transistors ist dabei eine weitere Stromquelle geschaltet.

Weiterhin kann die weitere Stromquelle einen fünften Transistor aufweisen, dessen Basis mit dem Ausdessen Emitter gangsanschluß und unter Zwischenschaltung eines vierten Widerstandes mit dem Bezugspotential verbunden ist. Des weiteren sind ein sechster Transistor, dessen Emitter unter Zwischenschaltung eines fünften Widerstandes mit dem Versoraunaspotential verbunden ist, dessen Kollektor mit der Basis des vierten Transistors verschaltet ist und dessen Basis mit dem Kollektor des fünften Transistors gekoppelt ist, sowie ein siebter Transistor, dessen Basis und Kollektor miteinander sowie mit dem Kollektor des fünften Transistors gekoppelt sind und dessen Emitter unter Zwischenschaltung eines sechsten Widerstandes mit dem Versorgungspotential verbunden ist, vorgesehen.

Bei einer Weiterbildung der Erfindung ist in die Kollektorleitung des sechsten Transistors in Reihe zur weiteren Stromquelle ein achter Widerstand geschaltet. Dies hat den Vorteil, daß das Rauschen der erfindungsgemäßen Schaltungsanordnung weiter herabgesetzt wird. Das Rauschen der weiteren Stromquelle hat insbesondere bei hohen Frequenzen einen Einfluß auf das Rauschverhalten der gesamten Schaltungsanordnung. Dies stört vor allem auch dann, wenn bei der weiteren Stromquelle pnp-Transistoren verwendet werden, da diese hinsichtlich des Rauschens und der Größe der parasitären Kapazitäten weit von einem idealen Transistor entfernt sind. Der eingefügte achte Widerstand isoliert insbesondere bei hohen Frequenzen die nicht ideal arbeitende weitere Stromquelle und verbessert so das Rauschverhalten sowie den Ausgangswiderstand. Darüber hinaus wird die Stabilität verbessert, da die effektive Kapazität am Ausgang der weiteren Stromguelle nun nicht mehr in so starkem Maße die Phasenreserve der gesamten Schaltungsanordnung beeinflußt. Das Einfügen eines Serienwiderstandes empfiehlt sich insbesondere bei Realisierung von sechstem und siebtem Transistor als pnp-Transistoren an einem Stromausgang der Schaltungsanordnung.

Die Erfindung wird nachfolgend anhand des in der

55

15

einzigen Figur der Zeichnung dargestellten Ausführungsbeispiels näher erläutert.

3

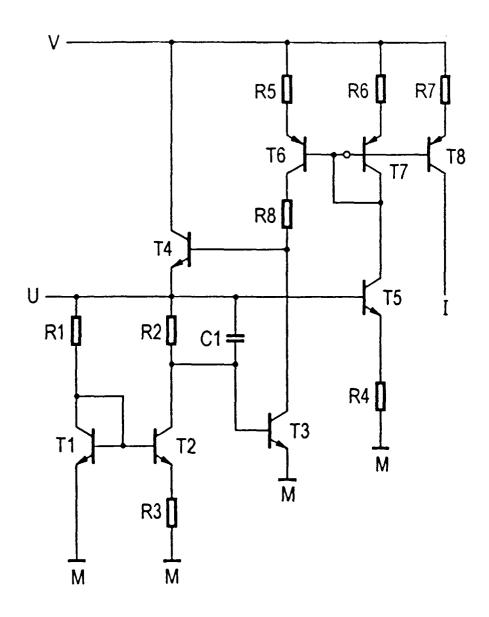

Bei der als Ausführungsbeispiel gezeigten erfindungsgemäßen Schaltungsanordnung ist ein npn-Transistor T1 vorgesehen, dessen Emitter mit einem 5 Bezugspotential M verbunden ist und dessen Basis und Kollektor sowohl miteinander verschaltet als auch über einen gemeinsamen Widerstand R1 mit einem ein Referenzpotential führenden Ausgangsanschluß U gekoppelt sind. An Basis und Kollektor des Transistors T1 ist die Basis eines npn-Transistors T2 angeschlossen, dessen Emitter über einen Widerstand R3 mit dem Bezugspotential M und dessen Kollektor über einen Widerstand R2 mit dem Ausgangsanschluß U gekop-

An dem Ausgangsanschluß U ist darüber hinaus der Emitter eines non-Transistors T4 angeschlossen, dessen Kollektor mit einem Versorgungspotential V verbunden ist. Die Basis des Transistors T4 ist mit dem Kollektor eines npn-Transistors T3 verbunden, dessen Emitter an das Bezugspotential M und dessen Basis an den Kollektor des Transistors T2 angeschlossen ist. Dem Widerstand R2 ist eine Kapazität C1 parallel geschaltet.

Die Basis des Transistors T4 ist darüber hinaus über einen Widerstand R8 sowie eine Stromguellenschaltung an das Versorgungspotential V angeschlos-

Die Stromquellenschaltung weist einen pnp-Transistor T6 auf, dessen Emitter über einen Widerstand R5 mit dem Versorgungspotential V und dessen Kollektor über den Widerstand R8 mit der Basis des Transistors T4 bzw. dem Kollektor des Transistors T3 verbunden ist. Die Basis des Transistors T6 ist mit Basis und Kollektor eines pnp-Transistors T7 verschaltet, dessen Emitter über einen Widerstand R6 mit dem Versorgungspotential V gekoppelt ist. Basis und Kollektor des Transistors T7 sowie die Basis des Transistors T6 sind darüber hinaus mit dem Kollektor eines npn-Transistors T5 verbunden, dessen Emitter über einen Widerstand R4 an das Bezugspotential M angeschlossen ist und dessen Basis mit dem Ausgangsanschluß U verbunden ist.

Neben dem Ausgangsanschluß U, an dem das Referenzpotential abgreifbar ist, kann darüber hinaus ein Ausgangsanschluß I vorgesehen werden, der einen Referenzstrom führt. Dazu ist der Ausgangsanschluß I mit dem Kollektor eines pnp-Transistors T8 verbunden, dessen Emitter über einen Widerstand R7 mit dem Versorgungspotential V verbunden ist und dessen Basis mit den Basen der Transistoren T6 und T7 verschaltet

Die Bemessung des Kondensators C1 hängt vom jeweiligen Anwendungsfall ab, wobei auch hier bei höheren Kapazitäten das Rauschverhalten und bei niedrigeren Kapazitäten das Einschaltverhalten günstiger wird. Der Widerstand R8 wird so groß wie möglich gewählt, um eine möglichst hohe Isolation zu gewahrleisten.

## Patentansprüche

Schaltungsanordnung zur Erzeugung eines Referenzpotentials mit einem ersten Transistor (T1), dessen Emitter mit einem Bezugspotential (M) verbunden ist und dessen Basis und Kollektor miteinander verschaltet sind. mit einem zweiten Transistor (T2), dessen Basis mit

der Basis des ersten Transistors (T1) verbunden ist, mit einem ersten Widerstand (R1), der zwischen den Kollektor des ersten Transistors (T1) und einem Ausgangsanschluß (U) zum Abgreifen des Referenzpotentials geschaltet ist,

mit einem zweiten Widerstand (R2), der zwischen den Kollektor des zweiten Transistors (T2) und den Ausgangsanschluß (U) geschaltet ist,

mit einem dritten Widerstand (R3), der zwischen den Emitter des zweiten Transistors (T2) und das Bezugspotential (M) geschaltet ist,

mit einem dritten Transistor (T3), dessen Basis mit dem Kollektor des zweiten Transistors (T2) und dessen Emitter mit dem Bezugspotential (M) verbunden ist, und mit einer gesteuerten Stromquelle (T4), die zwischen ein Versorgungspotential (V) und den Ausgangsanschluß (U) geschaltet ist und die eingangsseitig mit dem Kollektor des dritten Transistors (T3) gekoppelt ist, wobei

eine Kapazität (C1) vorgesehen ist, die dem zweiten Widerstand (R2) parallel geschaltet ist,

die gesteuerte Stromquelle (T3, T4) einen vierten Transistor (T4) aufweist, dessen Kollektor mit dem Versorgungspotential (V), dessen Emitter mit dem Ausgangsanschluß (U) und dessen Basis mit dem Kollektor des dritten Transistors (T3) verbunden ist, zwischen Basis und Kollektor des vierten Transistors (T4) eine weitere Stromquelle (T5, T6, T7, R4, R5, R6) geschaltet ist und

die weitere Stromquelle (T5, T6, T7, R4, R5, R6) aufweist:

Einen fünften Transistor (T5), dessen Basis mit dem Ausgangsanschluß (U) und dessen Emitter unter Zwischenschaltung eines vierten Widerstandes (R4) mit dem Bezugspotential (M) verbunden ist;

einen sechsten Transistor (T6), dessen Emitter (T6) unter Zwischenschaltung eines fünften Widerstandes (R5) mit dem Versorgungspotential (V) verbunden ist, dessen Kollektor mit der Basis des vierten Transistors (T4) verschaltet ist und dessen Basis mit dem Kollektor des fünften Transistors (T5) gekoppelt ist;

einen siebten Transistor (T7), dessen Basis und Kollektor miteinander sowie mit dem Kollektor des fünften Transistors (T5) gekoppelt sind und dessen Emitter unter Zwischenschaltung eines sechsten Widerstandes (R6) mit dem Versorgungspotential (V) verbunden ist.

2. Schaltungsanordnung nach Anspruch 1, dadurch gekennzeichnet, daß in Reihe zur weiteren Stromquelle (T6, T7) ein achter Widerstand (R8) geschaltet ist.