(19) Europäisches Patentamt

European Patent Office

Office européen des brevets

(11) EP 0 816 965 A1

(12)

## DEMANDE DE BREVET EUROPEEN

(43) Date de publication:

07.01.1998 Bulletin 1998/02

(51) Int. Cl.<sup>6</sup>: G05F 3/30

(21) Numéro de dépôt: 97201850.1

(22) Date de dépôt: 17.06.1997

(84) Etats contractants désignés:

AT BE CH DE DK ES FI FR GB GR IE IT LI LU MC

NL PT SE

(30) Priorité: 26.06.1996 FR 9607941

(71) Demandeur:

PHILIPS ELECTRONICS N.V.

5621 BA Eindhoven (NL)

(72) Inventeur: Perraud, Jean-Claude

75008 Paris (FR)

(74) Mandataire: Caron, Jean

Société Civile S.P.I.D.

156, Boulevard Haussmann

75008 Paris (FR)

### (54) Générateur de tension de référence régulée en fonction de la température

(57) La présente invention concerne un générateur de tension de référence fournissant une tension de sortie  $V_{bg}$  régulée, comprenant deux transistors (T1, T2), deux sources de courant (I1, I2), deux résistances (R1, R2) et un troisième transistor T3 débitant dans une résistance de charge RL.

Selon l'invention, un tel générateur est caractérisé en ce qu'il comporte en outre, insérés entre les premier et deuxième transistors (T1, T2) et les sources de courant (I1, I2), un quatrième et un cinquième transistors (T4, T5), dont les bases sont reliées ensemble à la base du troisième transistor T3.

Un tel générateur de tension possède une structure simple tout en assurant une régulation optimale de la tension de sortie  $V_{bg}$  en fonction de la température.

Applications : Elaboration d'une tension de référence dans un lecteur de cartes à puces.

FIG.1

## Description

La présente invention concerne un générateur de tension de référence fournissant sur une borne de sortie une tension de sortie régulée, comprenant :

- . un premier et un deuxième transistors, dont les bases sont reliées ensemble et forment la borne de sortie du générateur, l'émetteur du premier transistor étant relié via une première résistance A l'émetteur du deuxième transistor, lequel est en outre relié via une deuxième résistance à une première borne d'alimentation, les collecteurs des premier et deuxième transistors étant reliés à deux sources de courant de valeurs nominales égales,

- . un troisième transistor dont la base est reliée à l'une des sources de courant, le collecteur à une deuxième borne d'alimentation et l'émetteur aux bases des premier et deuxième transistors, ainsi qu'à la borne négative d'alimentation via une résistance de charge.

Un tel générateur est décrit dans le brevet européen ayant pour numéro d'enregistrement 94 203 440.6. Ce générateur a notamment pour fonction de fournir sur les bases des premier et deuxième transistors une tension dont la valeur ne varie pas en fonction de la température. La théorie décrivant ce type de systèmes est connue de l'homme de l'art. Elle repose sur le fait que la tension base-émetteur d'un transistor diminue linéairement en fonction de la température. Une chute de tension créée grâce à la première résistance, notée VR1, permet d'augmenter le potentiel de l'émetteur de manière linéaire en fonction de la température. En effet, si le premier transistor est N fois plus grand que le deuxième, la tension VR1 est égale à  $Vt \ln(N)$ , avec  $Vt = K \cdot T/q$ , où K est la constante de Boltzmann, q la charge de l'électron et T la température absolue. On a donc  $VR1 = T \cdot (\ln(N) \cdot K/q)$ . La diminution linéaire en fonction de la température de la tension base-émetteur, appelée Vbe, du premier transistor peut ainsi être compensée grâce à un bon dimensionnement des composants constituant le générateur. Celui-ci fonctionne de manière optimale lorsque les courants traversant les premier et deuxième transistors sont rigoureusement égaux. De plus, afin que l'effet d'Early ne crée pas de déséquilibre entre les dits transistors, leurs tensions de collecteur doivent également être identiques, ce qui n'est pas le cas dans le générateur décrit dans le document cité ci-dessus, dans lequel les collecteurs présentent une différence de potentiel due à la tension base-émetteur du troisième transistor à laquelle s'ajoute une chute de tension aux bornes d'une résistance additionnelle. Cette différence de potentiel crée un déséquilibre ayant pour effet d'altérer la qualité de la compensation en température de la tension base-émetteur du premier transistor.

La présente invention a pour but de remédier à cet

inconvénient en proposant un générateur de tension dans lequel les tensions de collecteur des premier et deuxième transistors sont rendues égales, sans pour autant recourir à une structure complexe.

En effet, un générateur de tension de référence selon la présente invention est caractérisé en ce qu'il comporte, insérés entre les premier et deuxième transistors et les sources de courant, un quatrième et un cinquième transistors dont les bases sont reliées ensemble à la base du troisième transistor, dont les émetteurs sont reliés respectivement aux collecteurs des premier et deuxième transistors et dont les collecteurs sont reliés chacun à une des sources de courant.

Dans un tel générateur, chacun des collecteurs des premier et deuxième transistor est à un potentiel inférieur d'un Vbe à la tension de base du troisième transistor. De plus, chacune des bases des premier et deuxième transistors est également à un potentiel inférieur d'un Vbe à la tension de base du troisième transistor. Il en ressort que les premier et deuxième transistors fonctionnent tous deux sous une tension collecteur-émetteur nulle, ce qui est un point de fonctionnement particulièrement stable.

Une variante de l'invention présente un générateur de tension de référence tel que décrit ci-dessus, caractérisé en ce qu'il comporte un premier, un deuxième et un troisième miroirs de courant, chacun d'eux présentant une première et une deuxième branches et un point d'alimentation, les premières branches des premier et deuxième miroir de courant étant reliées respectivement aux collecteurs des quatrième et cinquième transistors, les points d'alimentation des premier et deuxième miroir de courant étant reliés à la deuxième borne d'alimentation, les deuxièmes branches des premier et deuxième miroirs de courant étant respectivement reliées aux première et deuxième branches du troisième miroir de courant dont le point d'alimentation est relié à la première borne d'alimentation, les bases des premier, deuxième et troisième transistors étant reliées ensemble à l'une des branches du troisième miroir de courant.

Une telle structure assure l'égalité des courants traversant les premier et deuxième transistors qui est nécessaire à une bonne régulation de la tension de sortie en fonction de la température. De plus, cette structure étant très simple, la tension d'alimentation d'un tel générateur peut prendre des valeurs faibles, de l'ordre de 2 Volts.

Une autre variante de l'invention présente un générateur de tension de référence tel que décrit ci-dessus, caractérisé en ce qu'il comporte, inséré entre celle des branches du premier ou deuxième miroir de courant qui n'est pas reliée à la base du troisième transistor, et celle des branches du troisième miroir de courant qui n'est pas reliée à la base du troisième transistor, un sixième transistor dont la base est reliée à l'émetteur du troisième transistor.

Grâce à ce transistor additionnel, les potentiels des

deuxièmes branches de courant des premier et deuxième miroirs de courant sont identiques, étant tous deux égaux à la tension de sortie à laquelle s'ajoute un  $V_{be}$ , ce qui améliore encore l'identicité des courants parcourant les premier et deuxième transistors.

Une autre variante de l'invention présente un générateur de tension de référence tel que décrit ci-dessus, caractérisé en ce que le troisième miroir de courant comporte un septième, un huitième, un neuvième et un dixième transistor, les bases des septième et huitième transistors étant reliées à leurs collecteurs respectifs et aux bases des neuvième et dixième transistors, les émetteurs des septième et neuvième transistors étant reliés respectivement aux collecteurs des huitième et dixième transistors, dont les émetteurs sont reliés ensemble et forment le point d'alimentation du troisième miroir de courant, les collecteurs des septième et neuvième transistors formant respectivement les première et deuxième branches du troisième miroir de courant, la deuxième branche du troisième miroir de courant étant reliée à la base du troisième transistor.

Cette structure du troisième miroir de courant permet de compenser en partie les courants prélevés sur sa deuxième branche.

Une autre variante de l'invention présente un générateur tel que décrit plus haut, caractérisé en ce qu'il comprend un module de démarrage lui permettant d'évoluer rapidement vers un régime stabilisé après sa mise sous tension, module comportant un onzième et un douzième transistors montés en paire différentielle, le collecteur du onzième transistor étant relié à la borne positive d'alimentation, la base du onzième transistor étant reliée aux bases des troisième, quatrième et cinquième transistors, le collecteur du douzième transistor étant relié à la première branche de celui des premier ou deuxième miroir de courant dont la deuxième branche est reliée à la base du troisième transistor, la base du douzième transistor recevant une tension de valeur nominale fixée inférieure à la tension qui est présente aux bases des troisième, quatrième et cinquième transistors lorsque le générateur fonctionne en régime établi.

Un tel module de démarrage assure une stabilisation rapide du générateur après sa mise sous tension.

L'invention sera mieux comprise à l'aide de la description suivante de quelques modes de réalisation, faite à titre d'exemple et en regard des dessins annexés dans lesquels :

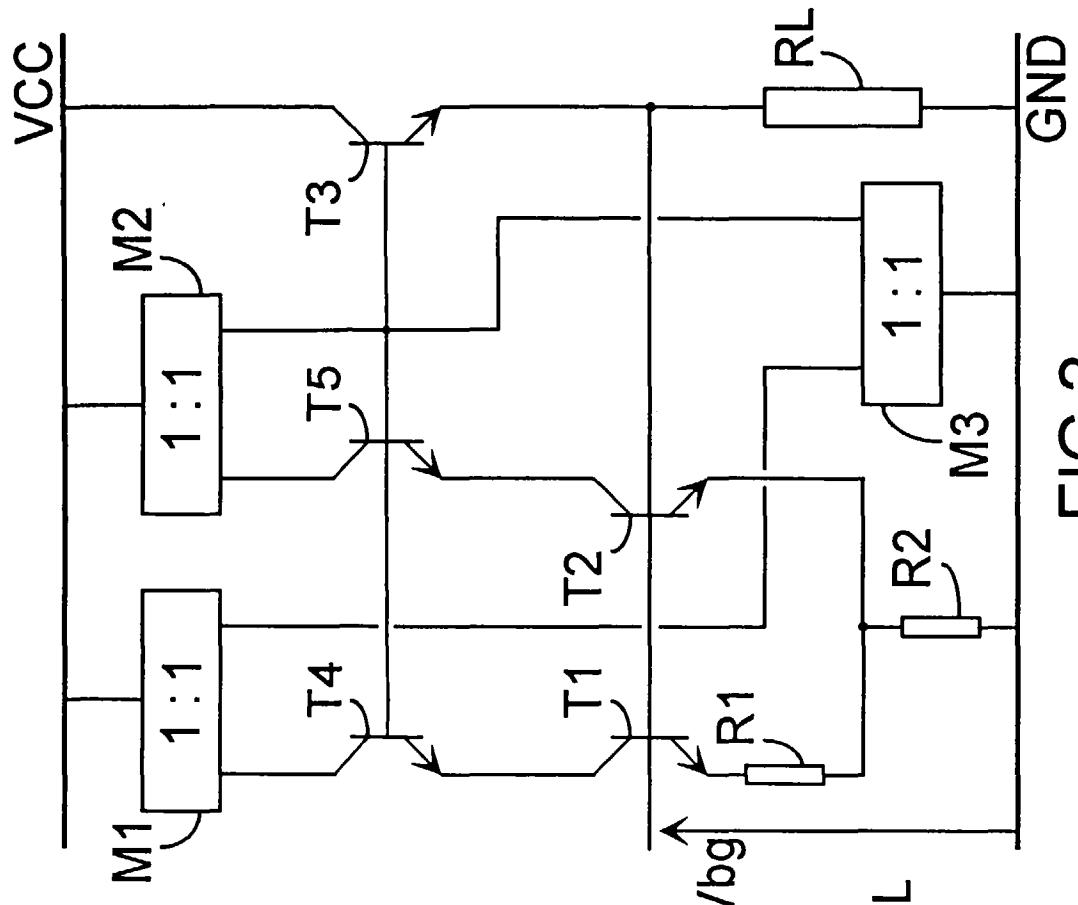

- la figure 1 présente un schéma fonctionnel décrivant un générateur de tension selon l'invention,

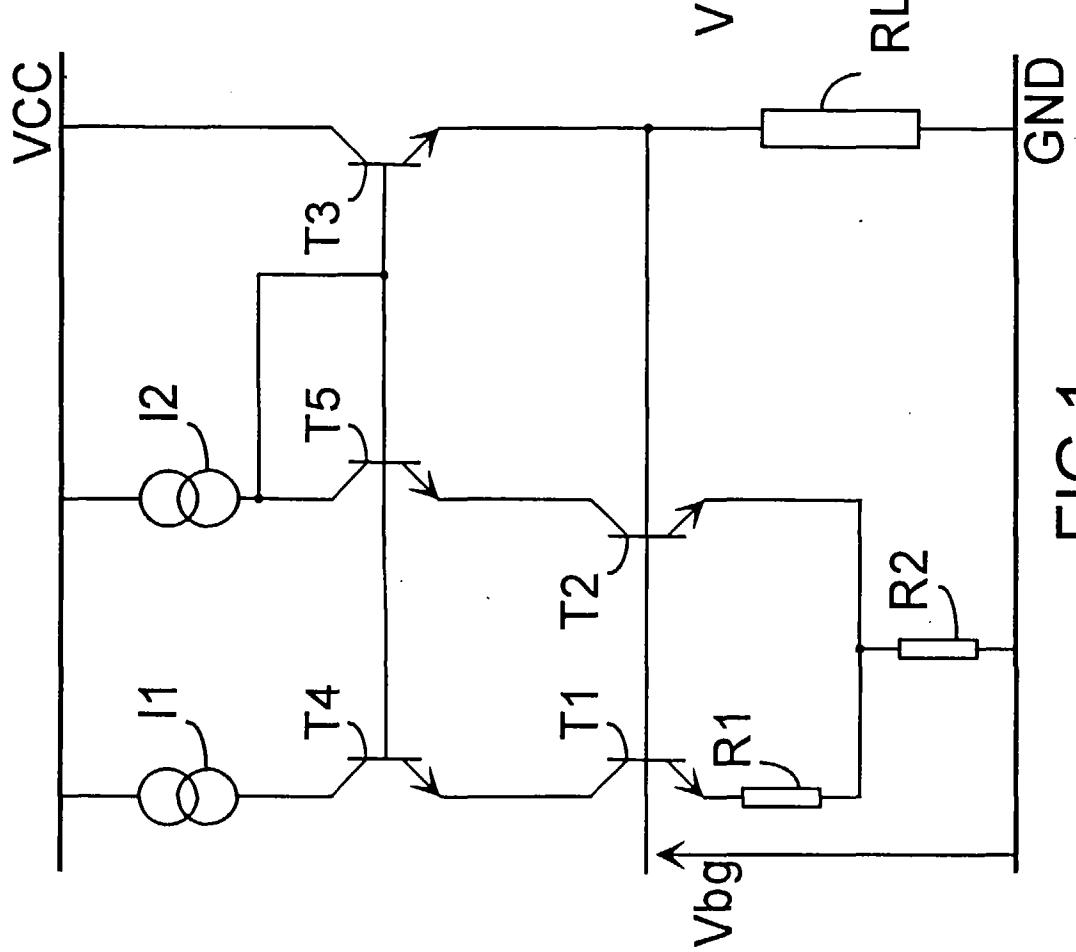

- la figure 2 présente un schéma fonctionnel décrivant un générateur de tension selon une variante de l'invention, et

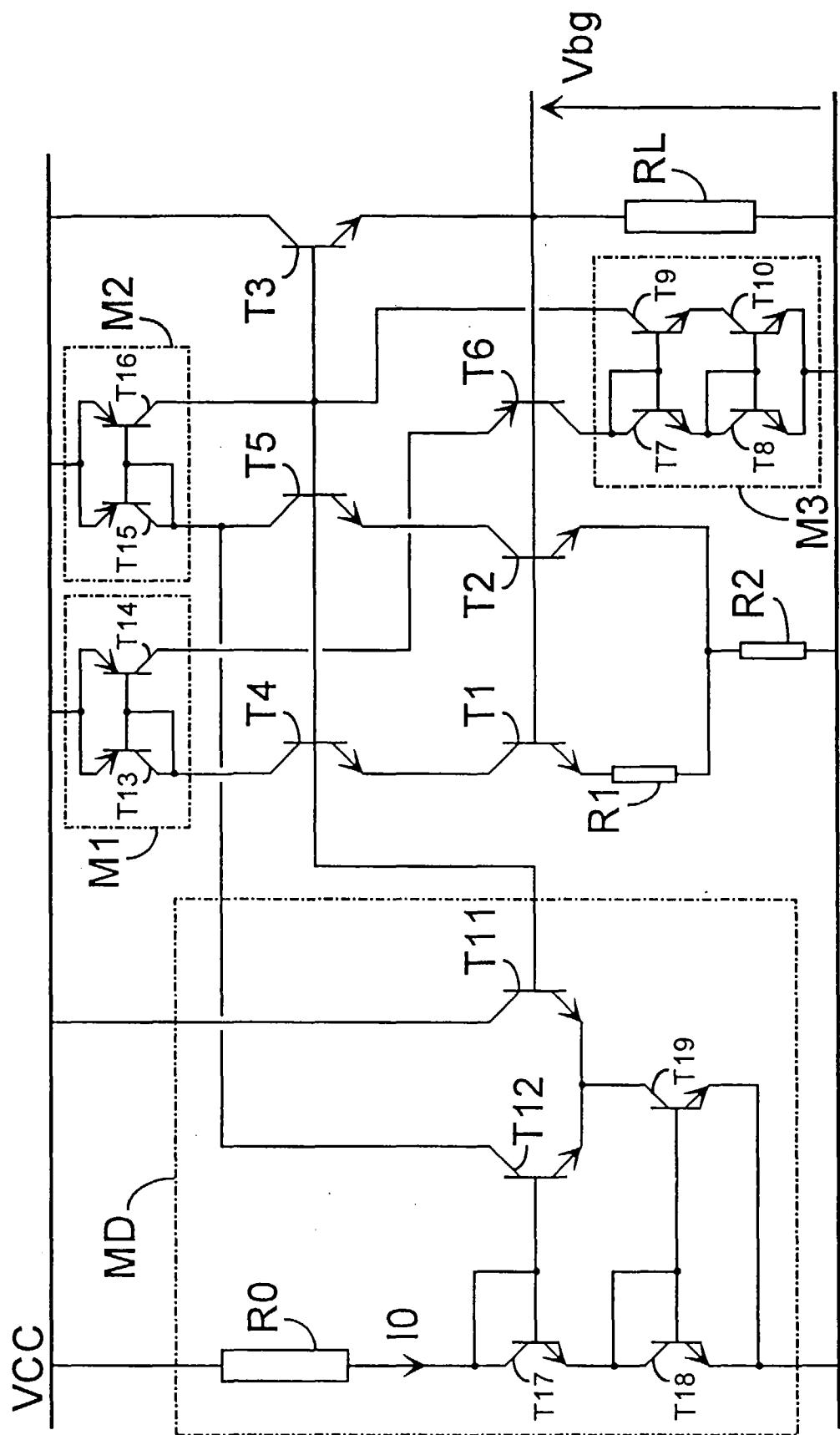

- la figure 3 présente un schéma fonctionnel décrivant un générateur de tension selon un mode de réalisation préféré de l'invention.

Selon la figure 1, un générateur de tension de référence selon l'invention, fournissant sur une borne de sortie une tension de sortie régulée  $V_{bg}$ , comprend :

- 5 . un premier et un deuxième transistors (T1, T2), tous deux de type NPN, dont les bases sont reliées ensemble et forment la borne de sortie du générateur, l'émetteur du premier transistor T1 étant relié via une première résistance R1 à l'émetteur du deuxième transistor T2, lequel est en outre relié via une deuxième résistance R2 à une première borne d'alimentation GND, les collecteurs des premier et deuxième transistors (T1, T2) étant reliés à deux sources de courant de valeurs nominales égales (I1, I2),

- 10 . un troisième transistor T3, de type NPN, dont la base est reliée à la source de courant I2, le collecteur à une deuxième borne d'alimentation VCC et l'émetteur aux bases des premier et deuxième transistors (T1, T2), ainsi qu'à la borne négative d'alimentation GND via une résistance de charge RL. Ce générateur comporte en outre, insérés entre les premier et deuxième transistors (T1, T2) et les sources de courant (I1, I2), un quatrième et un cinquième transistors (T4, T5), tous deux de type NPN, dont les bases sont reliées ensemble à la base du troisième transistor T3. Leurs émetteurs sont reliés respectivement aux collecteurs des premier et deuxième transistors (T1, T2). Leurs collecteurs sont reliés chacun à une des sources de courant (I1, I2).

- 15 .

- 20 .

- 25 .

- 30 .

Dans un tel générateur, la tension de collecteur de T1, notée  $V_c(T1)$ , est égale à la tension de base de T3, notée  $V_b(T3)$ , moins la tension base-émetteur de T4, notée  $V_{be}(T4)$  :  $V_c(T1)=V_b(T3)-V_{be}(T4)$ . De même, on a pour T2 :  $V_c(T2)=V_b(T3)-V_{be}(T5)$ . Si T4 et T5 sont identiques,  $V_c(T1)=V_c(T2)$ . De plus, les tensions collecteur-base de T1 et T2, notées respectivement  $V_{cb}(T1)$  et  $V_{cb}(T2)$ , sont nulles, puisque  $V_b(T1)=V_b(T2)=V_b(T3)-V_{be}(T3)$ . Les transistors T1 et T2 sont donc tous deux polarisés en un point de fonctionnement particulièrement stable.

La figure 2 présente un schéma fonctionnel décrivant un générateur de tension selon une variante de l'invention, qui comporte un premier, un deuxième et un troisième miroirs de courant (M1, M2, et M3), chacun d'eux présentant une première et une deuxième branches et un point d'alimentation. Les premières branches des premier et deuxième miroir de courant (M1, M2) sont reliées respectivement aux collecteurs des quatrième et cinquième transistors (T4, T5). Les points d'alimentation des premier et deuxième miroirs de courant (M1, M2) sont reliés à la deuxième borne d'alimentation VCC. Les deuxièmes branches des premier et deuxième miroirs de courant (M1, M2) sont reliées respectivement aux première et deuxième branches du troisième miroir de courant M3 dont le point d'alimentation

tion est relié à la première borne d'alimentation GND. Les bases des premier, deuxième et troisième transistors (T1, T2 et T3) sont reliées ensemble à la deuxième branche du troisième miroir de courant M3.

Une telle structure assure l'égalité des courants traversant les premier et deuxième transistors (T1, T2) qui est nécessaire à une bonne régulation de la tension de sortie Vbg en fonction de la température.

La figure 3 présente un schéma fonctionnel décrivant un générateur de tension selon un mode de réalisation préféré de l'invention, qui comporte, inséré entre la deuxième branche du premier miroir de courant M1 et la première branche du troisième miroir de courant M3, un sixième transistor T6 de type PNP dont la base est reliée à l'émetteur du troisième transistor T3.

Le potentiel de la deuxième branche du premier miroir de courant M1 est égal à  $V_{bg} + V_{be}(T6)$ , tandis que le potentiel de la deuxième branche du deuxième miroir de courant M2 est égal à  $V_{bg} + V_{be}(T3)$ . Dans un tel circuit, les valeurs des tensions  $V_{be}$  des différents transistors sont très proches les unes des autres. Grâce à ce transistor additionnel T6, les potentiels des deuxièmes branches de courant des premier et deuxième miroirs de courant (M1, M2) sont donc identiques, ce qui améliore encore l'identicité des courants parcourant les premier et deuxième transistors (T1, T2).

Dans le générateur de tension représenté sur la figure 3, le troisième miroir de courant M3 comporte un septième, un huitième, un neuvième et un dixième transistor (T7, T8, T9 et T10). Les bases des septième et huitième transistors (T7, T8) sont reliées à leurs collecteurs respectifs et aux bases des neuvième et dixième transistors (T9, T10). Les émetteurs des septième et neuvième transistors (T7, T9) sont reliés respectivement aux collecteurs des huitième et dixième transistors (T8, T10), dont les émetteurs sont reliés ensemble et forment le point d'alimentation du troisième miroir de courant M3. Les collecteurs des septième et neuvième transistors (T7, T9) forment respectivement la première et la deuxième branche du troisième miroir de courant M3. La deuxième branche du troisième miroir de courant est reliée à la base du troisième transistor T3.

Le courant entrant dans la deuxième branche du miroir de courant M3 est amputé des courants de base des troisième, quatrième et cinquième transistors. La structure dissymétrique du miroir de courant M3 décrite ci-dessus permet de compenser ces pertes, car les courants de base des transistors qui contient le miroir de courant M3 sont prélevés sur le courant entrant dans la première branche, rétablissant ainsi la symétrie entre les deux courants entrants, et améliorant l'identicité des courants parcourant les premier et deuxième transistors qui résultent des réflexions des courants entrant dans le miroir de courant M3 en provenance des miroirs M1 et M2. Les miroirs de courant M1 et M2 sont constitués ici respectivement par les transistors T13, T14 et T15, T16, tous quatre de type PNP.

Si la tension de sortie Vbg d'un tel générateur est

de 1,2V, la tension minimale d'alimentation VCC, qui est par exemple égale à  $V_{bg} + V_{be}(T4) - V_{ce\ sat}(T13)$ , avec  $V_{be}(T4)$  et  $V_{ce\ sat}(T13)$  respectivement de l'ordre de 0,6V et 0,2V sera donc voisine de 2V, ce qui permet au générateur de consommer peu d'énergie, et le rend particulièrement adapté pour des utilisations dans des appareils portables, comme des téléphones sans fil.

Le générateur de tension représenté sur la figure 3 comprend de plus un module de démarrage MD lui permettant d'évoluer rapidement vers un régime stabilisé après sa mise sous tension. Ce module MD comporte un onzième et un douzième transistors (T11, T12), tous deux de type NPN, montés en paire différentielle. Le collecteur du onzième transistor T11 est relié à la deuxième borne d'alimentation VCC, sa base étant reliée aux basés des troisième, quatrième et cinquième transistors (T3, T4, T5). Le collecteur du douzième transistor T12 est relié à la première branche du deuxième miroir de courant M2, sa base étant reliée, par l'intermédiaire d'une résistance R0 à la deuxième borne d'alimentation VCC. La base du douzième transistor T12 est en outre reliée à la base d'un dix-septième transistor T17, de type NPN, monté en diode, dont l'émetteur est relié par l'intermédiaire d'un dix-huitième transistor T18, de type NPN, à la première borne d'alimentation GND. Le dix-huitième transistor T18 est monté en miroir de courant avec un dix-neuvième transistor T19, de type NPN, dont le collecteur est relié aux émetteurs des onzième et douzième transistors (T11, T12). La résistance R0 débite un courant fixe I0, dont la valeur est  $(V_{CC} - 2 \cdot V_{be}) / R_0$ . Ce courant est reproduit par le miroir de courant (T18, T19) et polarise ainsi la paire différentielle (T11, T12). La base du troisième transistor est en permanence à un potentiel égal à  $2 \cdot V_{be}$ . Au démarrage, la tension de sortie Vbg du générateur est nulle. La tension appliquée à la base du onzième transistor T11 est donc très inférieure à  $2 \cdot V_{be}$ , et le douzième transistor T12 conduit le courant I0. Ce courant est reproduit par le miroir M2, et permet la mise en conduction du troisième transistor T3, lequel conduit alors un courant vers la résistance de charge RL, faisant ainsi augmenter la tension de sortie Vbg. Le courant I0 reproduit par le miroir M2 permet aussi la mise en conduction des quatrième et cinquième transistors (T4, T5) pendant que le courant I0, successivement réfléchi par les miroirs M3 et M2 est envoyé vers le premier transistor T1. Lorsque la tension de sortie Vbg du générateur est stabilisée, la base du onzième transistor T11 est à un potentiel dont la valeur est de l'ordre de  $V_{bg} + V_{be}$ . La tension régulée Vbg étant elle-même de l'ordre de  $2 \cdot V_{be}$ , le potentiel appliqué à la base du onzième transistor T11 est alors supérieur à  $2 \cdot V_{be}$ , qui est le potentiel appliqué à la base du douzième transistor T12. Celui-ci se bloque, désolidarisant donc le module de démarrage MD du reste du générateur.

## Revendications

1. Générateur de tension de référence fournissant sur une borne de sortie une tension de sortie régulée, comprenant :

- un premier et un deuxième transistors, dont les bases sont reliées ensemble et forment la borne de sortie du générateur, l'émetteur du premier transistor étant relié via une première résistance à l'émetteur du deuxième transistor, lequel est en outre relié via une deuxième résistance à une première borne d'alimentation, les collecteurs des premier et deuxième transistors étant reliés à deux sources de courant de valeurs nominales égales,

- un troisième transistor dont la base est reliée à l'une des sources de courant, le collecteur à une deuxième borne d'alimentation et l'émetteur aux bases des premier et deuxième transistors, ainsi qu'à la borne négative d'alimentation via une résistance de charge, générateur caractérisé en ce qu'il comporte, insérés entre les premier et deuxième transistors et les sources de courant, un quatrième et un cinquième transistors dont les bases sont reliées ensemble à la base du troisième transistor, dont les émetteurs sont reliés respectivement aux collecteurs des premier et deuxième transistors et dont les collecteurs sont reliés chacun à une des sources de courant.

2. Générateur de tension de référence selon la revendication 1, caractérisé en ce qu'il comporte un premier, un deuxième et un troisième miroirs de courant, chacun d'eux présentant une première et une deuxième branches et un point d'alimentation, les premières branches des premier et deuxième miroir de courant étant reliées respectivement aux collecteurs des quatrième et cinquième transistors, les points d'alimentation des premier et deuxième miroir de courant étant reliés à la deuxième borne d'alimentation, les deuxièmes branches des premier et deuxième miroirs de courant étant respectivement reliées aux première et deuxième branches du troisième miroir de courant dont le point d'alimentation est relié à la première borne d'alimentation, les bases des premier, deuxième et troisième transistors étant reliées ensemble à l'une des branches du troisième miroir de courant.

3. Générateur de tension de référence selon la revendication 2, caractérisé en ce qu'il comporte, inséré entre celle des branches du premier ou deuxième miroir de courant qui n'est pas reliée à la base du troisième transistor, et celle des branches du troisième miroir de courant qui n'est pas reliée à la

base du troisième transistor, un sixième transistor dont la base est reliée à l'émetteur du troisième transistor.

- 5 4. Générateur de tension de référence selon l'une des revendications 2 ou 3, caractérisé en ce que le troisième miroir de courant comporte un septième, un huitième, un neuvième et un dixième transistor, les bases des septième et huitième transistors étant reliées à leurs collecteurs respectifs et aux bases des neuvième et dixième transistors, les émetteurs des septième et neuvième transistors étant reliés respectivement aux collecteurs des huitième et dixième transistors, dont les émetteurs sont reliés ensemble et forment le point d'alimentation du troisième miroir de courant, les collecteurs des septième et neuvième transistors formant respectivement les première et deuxième branches du troisième miroir de courant, la deuxième branche du troisième miroir de courant étant reliée à la base du troisième transistor.

- 10 5. Générateur selon l'une des revendications 2 à 4, caractérisé en ce qu'il comprend un module de démarrage lui permettant d'évoluer rapidement vers un régime stabilisé après sa mise sous tension, module comportant un onzième et un douzième transistors montés en paire différentielle, le collecteur du onzième transistor étant relié à la deuxième borne d'alimentation, la base du onzième transistor étant reliée aux bases des troisième, quatrième et cinquième transistors, le collecteur du douzième transistor étant relié à la première branche de celui des premier ou deuxième miroir de courant dont la deuxième branche est reliée à la base du troisième transistor, la base du douzième transistor recevant une tension de valeur nominale fixée inférieure à la tension qui est présente aux bases des troisième, quatrième et cinquième transistors lorsque le générateur fonctionne en régime établi.

- 15 35 40 45 50 55

FIG.2

FIG.1

FIG.3

GND

Office européen

des brevets

## RAPPORT DE RECHERCHE EUROPEENNE

Numéro de la demande

EP 97 20 1850

| DOCUMENTS CONSIDERES COMME PERTINENTS                                                                                                                                                                                               |                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                          |                                              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| Catégorie                                                                                                                                                                                                                           | Citation du document avec indication, en cas de besoin,<br>des parties pertinentes                                                                                                                                               | Revendication<br>concernée                                                                                                                                                                                                                                               | CLASSEMENT DE LA<br>DEMANDE (Int.Cl.6)       |

| A                                                                                                                                                                                                                                   | ANONYMOUS: "Line Voltage Rejection in a Bandgap Voltage Reference"<br>IBM TECHNICAL DISCLOSURE BULLETIN,<br>vol. 30, no. 4, septembre 1987, NEW YORK,<br>US,<br>pages 1424-1425, XP002028263<br>* le document en entier *<br>--- | 1-5                                                                                                                                                                                                                                                                      | G05F3/30                                     |

| A                                                                                                                                                                                                                                   | ANISIMOV V I ET AL: "CIRCUIT DESIGN OF LOW-POWER REFERENCE VOLTAGE SOURCES"<br>TELECOMMUNICATIONS AND RADIO ENGINEERING,<br>vol. 48, no. 1, 1 janvier 1993,<br>pages 11-17, XP000447126<br>* le document en entier *             | 1-5                                                                                                                                                                                                                                                                      |                                              |

| D,A                                                                                                                                                                                                                                 | EP 0 656 575 A (PHILIPS ELECTRONICS NV) 7 juin 1995<br>* le document en entier *<br>---                                                                                                                                          | 1-5                                                                                                                                                                                                                                                                      |                                              |

| A                                                                                                                                                                                                                                   | GB 2 218 544 A (PLESSEY CO PLC) 15 novembre 1989<br>* le document en entier *                                                                                                                                                    | 2-5                                                                                                                                                                                                                                                                      | DOMAINES TECHNIQUES<br>RECHERCHES (Int.Cl.6) |

| A                                                                                                                                                                                                                                   | EP 0 419 819 A (MOTOROLA INC) 3 avril 1991<br>* le document en entier *<br>-----                                                                                                                                                 | 5                                                                                                                                                                                                                                                                        | G05F                                         |

| Le présent rapport a été établi pour toutes les revendications                                                                                                                                                                      |                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                          |                                              |

| Lieu de la recherche                                                                                                                                                                                                                | Date d'achèvement de la recherche                                                                                                                                                                                                | Examinateur                                                                                                                                                                                                                                                              |                                              |

| LA HAYE                                                                                                                                                                                                                             | 24 septembre 1997                                                                                                                                                                                                                | Lampe, S                                                                                                                                                                                                                                                                 |                                              |

| CATEGORIE DES DOCUMENTS CITES                                                                                                                                                                                                       |                                                                                                                                                                                                                                  | T : théorie ou principe à la base de l'invention<br>E : document de brevet antérieur, mais publié à la date de dépôt ou après cette date<br>D : cité dans la demande<br>L : cité pour d'autres raisons<br>.....<br>& : membre de la même famille, document correspondant |                                              |

| X : particulièrement pertinent à lui seul<br>Y : particulièrement pertinent en combinaison avec un autre document de la même catégorie<br>A : arrière-plan technologique<br>O : divulgation non-écrite<br>P : document intercalaire |                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                          |                                              |